Изобретение относится к электроизмерительной и вычислительной технике и может быть использовано для преобразования аналогового напряжения в код.

Известен аналого-цифровой преобразователь (АЦП) последовательного приближения, содержащий схему сравнения, регистр последовательной аппроксимации, цифроаналоговый преобразователь (ЦАП), элемент И, генератор тактовых импульсов (Чернов В.Г. Устройства ввода-вывода аналоговой информации для цифровых систем сбора и обработки данных. - М.: Машиностроение, 1988. - С.85, рис.57). Аналого-цифровой преобразователь последовательного приближения характеризуется следующими особенностями. В процессе подбора кода используется метод половинного деления, и процесс преобразования всегда длится N тактов, где N - разрядность аналого-цифрового преобразователя.

Недостатком устройства является его низкое быстродействие.

Наиболее близким по технической сущности к предлагаемому устройству является аналого-цифровой преобразователь на N разрядов, содержащий делитель опорного напряжения, входы которого являются соответственно первым и вторым входами устройства и предназначены для подключения опорного напряжения, М (М<2N) компараторов напряжения, первые входы которых объединены и являются третьим входом устройства, предназначенный для подачи входного преобразуемого напряжения, регистр, М мультиплексоров, триггер, генератор тактовых импульсов, и формирователь кодов, выходы делителя опорного напряжения подключены к соответствующим входам мультиплексоров, выходы которых подключены ко вторым входам соответствующих компараторов напряжения, выходы которых соединены с первыми входами формирователя кодов, первая группа выходов которого является первыми выходами устройства и подключены к первой группе информационных входов регистра, остальные группы выходов формирователя кодов соединены с соответствующими группами информационных входов регистра, первый вход триггера является четвертым входом устройства, выход триггера, являющийся вторым выходом устройства, подключен к первому управляющему входу регистра и управляющему входу генератора импульсов, выход которого соединен со стробирующими входами компараторов напряжения и вторым управляющим входом регистра, первая группа выходов которого соединена с адресными входами первого мультиплексора и вторыми входами формирователя кодов, остальные группы выходов подключены к адресным входам соответствующих мультиплексоров, последний выход формирователя кодов подключен ко второму входу триггера (Патент 2183381 России, МКИ Н 03 М 1/26. Аналого-цифровой преобразователь/ Н.Н.Хрисанов. Опубл. 20.08.2002, БИ №23, прототип).

Недостатком устройства является значительная сложность, т.к. для построения N-разрядного аналого-цифрового преобразователя требуются мультиплексоры с 2N входами.

Технический результат - упрощение устройства за счет применения в качестве делителя опорного напряжения резисторной матрицы R-2R, при этом вместо мультиплексоров с 2N входами, содержащими соответственно 2 коммутирующих элементов, используются блоки ключей, содержащих N коммутирующих элементов.

Поставленный технический результат достигается тем, что в N-разрядный аналого-цифровой преобразователь, содержащий делитель опорного напряжения, входы которого являются соответственно первым и вторым входами устройства и предназначены для подключения опорного напряжения, М {М<2N) компараторов напряжения, первые входы которых объединены и являются третьим входом устройства, предназначенный для подачи входного преобразуемого напряжения, регистр, триггер, генератор тактовых импульсов, и формирователь кодов, выходы компараторов напряжения соединены с первыми входами формирователя кодов, первая группа выходов которого является первыми выходами устройства и подключены к первой группе информационных входов регистра, остальные группы выходов формирователя кодов соединены с соответствующими группами информационных входов регистра, первый вход триггера является четвертым входом устройства, выход триггера, являющийся вторым выходом устройства, подключен к первому управляющему входу регистра и управляющему входу генератора тактовых импульсов, выход которого соединен с стробирующими входами компараторов напряжения и вторым управляющим входом регистра, первая группа выходов которого соединена с вторыми входами формирователя кодов, последний выход которого подключен ко второму входу триггера, введены М аналоговых сумматоров, М блоков ключей, одноименные входы которых объединены и подключены к соответствующим выходам делителя опорного напряжения, а выходы соединены с входами соответствующих аналоговых сумматоров, выходы которых соединены с вторыми входами соответствующих компараторов напряжения, управляющие входы блоков ключей соединены с соответствующими группами выходов регистра.

Структурная схема предлагаемого устройства отличается от известного тем, что в него введены М (М<2N) блоков ключей и М аналоговых сумматоров, которые являются стандартными узлами аналого-цифровой техники. Кроме того, в качестве делителя опорного напряжения используется резисторная матрица R-2R (содержащей 2N резистора), вместо делителя, содержащего 2N одинаковых резистора. Аналоговые сумматоры могут быть реализованы на операционных усилителях (Фолкенберри Л. Применение операционных усилителей и линейных ИС. - М.: Мир, 1985, с.107-123). Однако, несмотря на то, что введенные блоки являются стандартными узлами аналого-цифровой техники, их введение, а также появление новых функциональных связей между ними и существующими блоками дает возможность проявиться в устройстве новому свойству. А именно: аналого-цифровой преобразователь более прост в реализации, за счет применения вместо мультиплексоров с 2N входами, и содержащими 2N коммутирующих элементов, блоков ключей, содержащими N коммутирующих элементов. Делитель опорного напряжения содержит 2N резистора вместо 2N в прототипе. Таким образом, предлагаемое устройство более просто в реализации.

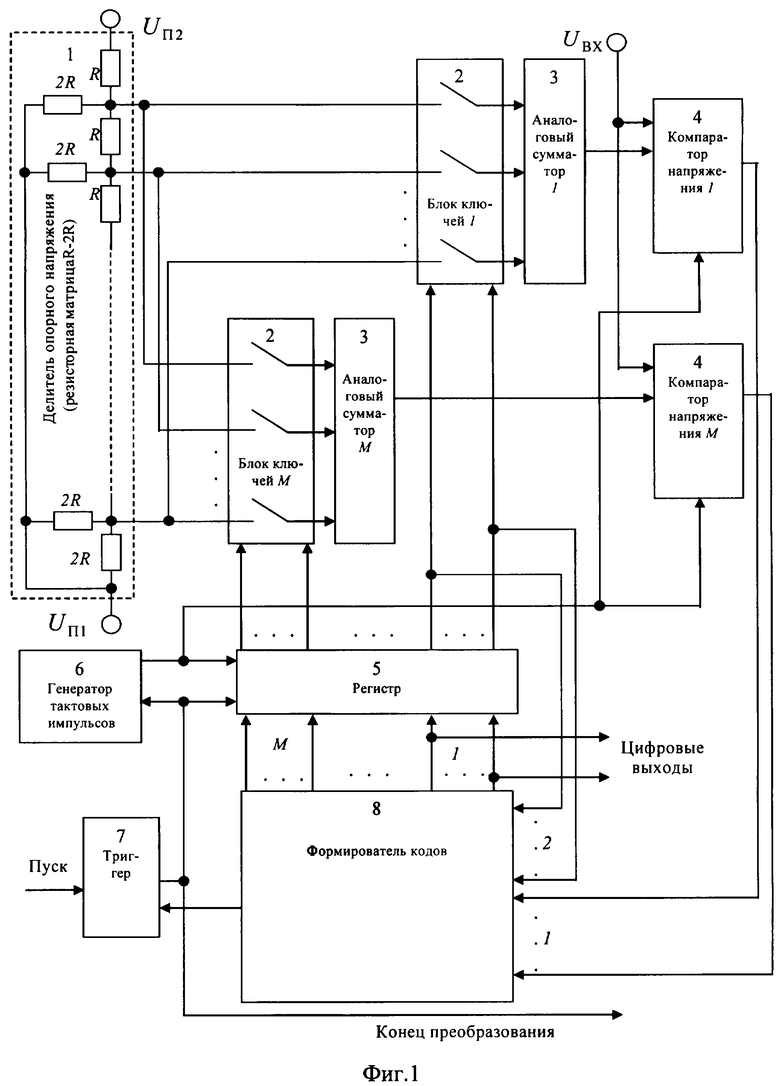

Структурная схема аналого-цифрового преобразователя (АЦП) приведена на фиг.1, где 1 - делитель опорного напряжения на основе резисторной матрицы R-2R; 2 - блок ключей; 3 - аналоговый сумматор; 4 - компаратор напряжения; 5 - регистр; 6 - генератор тактовых импульсов; 7 - триггер; 8 - формирователь кодов.

Делитель опорного напряжения на основе резисторной матрицы R-2R 1 предназначен для получения опорных напряжений, пропорциональных степени двойки. Так, например, если напряжение питания резисторной матрицы R-2R, входящей в делитель опорного напряжения 1, UП=10 В и разрядность аналого-цифрового преобразователя N=4, то с помощью резисторной матрицы R-2R должны быть сформированы 4 опорных напряжения U3=5,0 В, U2=2,5 В, U1=1,25 В, U0=0,625 В.

Блок ключей 2 содержит N коммутирующих элементов, которые замыкаются или размыкаются при подаче на соответствующий управляющий вход сигнала логической единицы или нуля, и предназначен для подачи на входы аналогового сумматора 3 одного и или нескольких опорных напряжений с делителя опорного напряжения на основе резисторной матрицы R-2R 1.

Аналоговый сумматор 3 предназначен для формирования напряжения U∑i, где i - номер аналогового сумматора 3, равного сумме подключенных к нему опорных напряжений. Например, если к входам первого аналогового сумматора (верхнего по схеме) будут подключены с помощью блока ключей 2 опорные напряжения U3 и U2, то на выходе первого сумматора будет напряжение U∑1=5,0+2,5=7,5 В.

Компаратор напряжения 4 предназначен для сравнения напряжения, поступающего с выхода соответствующего аналогового сумматора 3 с входным преобразуемым напряжением. Регистр 5 предназначен для запоминания текущих кодов, поступающих с выхода формирователя кодов 8, в процессе подбора выходного кода. Генератор тактовых импульсов 6 предназначен для синхронизации работы устройства. По переднему фронту импульсов, поступающих с генератора тактовых импульсов 6, происходит фиксация состояния компараторов напряжения 4, по заднему фронту происходит запись в регистр 5 кодов с выходов формирователя кодов 8. Триггер 7 предназначен для фиксации начала процесса преобразования и его окончания. При подаче на его первый вход сигнала "Пуск", триггер 7 устанавливается в единичное состояние и начинается процесс преобразования. При появлении сигнала логической единицы на последнем выходе формирователя кодов 8, триггер 7 устанавливается в нулевое состояние и процесс преобразования заканчивается.

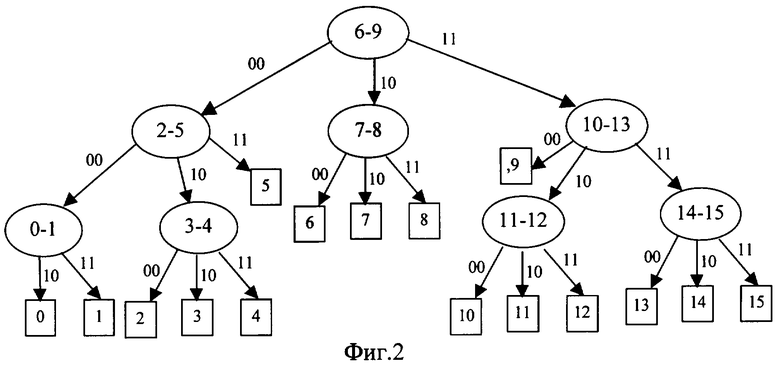

Формирователь кодов 8 предназначен для реализации процесса подбора кода в процессе преобразования. Рассмотрим процесс подбора кода на одном частном примере. Пусть разрядность аналого-цифрового преобразователя АЦП равна четырем, и аналого-цифровой преобразователь содержит два блока ключей 2 и два аналоговых сумматора 3 и соответственно два компаратора напряжения 4 (М=2). Каждый блок ключей содержит соответственно 4 коммутирующих элемента. Процесс подбора кода можно изобразить в виде графа, изображенного на фиг.2. В соответствии с фиг.2 первоначально на управляющих входах первого блока ключей 3 (верхнего по схеме) устанавливается код числа 9 или в двоичном виде 1001 (младший разряд соответствует опорному напряжению U0). Это означает, что к входам первого аналогового сумматора 3 будут подключены опорные напряжения U3 и U0, и напряжение на выходе первого аналогового сумматора будет равным U∑1=5,0+0,625=5,625 В. На управляющие входы второго блока ключей 2 (нижнего по схеме) подается код числа 6 (верхняя корневая вершина), или в двоичном виде 0110. К входам второго аналогового сумматора 3 будут подключены опорные напряжения U2 и U1, и напряжение на выходе второго аналогового сумматора 3 будет равным U∑2=2,5+1,25=3,75 В.

На выходах компараторов напряжения 4 при этом в зависимости от входного напряжения возможны три комбинации: 00 - когда входное напряжение UВХ меньше напряжения, поступающее как с первого, так и второго аналоговых сумматоров 3 {UВХ<U∑1 и UВХ<U∑2); 10 - когда входное напряжение больше напряжения, поступающего со второго аналогового сумматора 3, но меньше напряжения, поступающего с первого аналогового сумматора 3 (UВХ<U∑1 и UВХ>U∑2); 11 - когда входное напряжение больше напряжения, поступающего как с первого так и второго аналоговых сумматоров 3 (UВХ>U∑1 и UВХ>U∑2). Далее в зависимости от значения кодов на выходе компараторов напряжения 4 происходит переход по соответствующей дуге графа. Например, при коде 00 происходит переход к вершине 2-5, и соответственно на управляющих входах блоков ключей 2 должны быть установлены коды 2 (нижний блок ключей 2) и 5 (верхний блок ключей 2). Процесс подбора кода прекращается по достижении висячей вершины. В качестве выходного кода, соответствующего входному напряжению UВХ, берется код, указанный на фиг.2 в прямоугольниках.

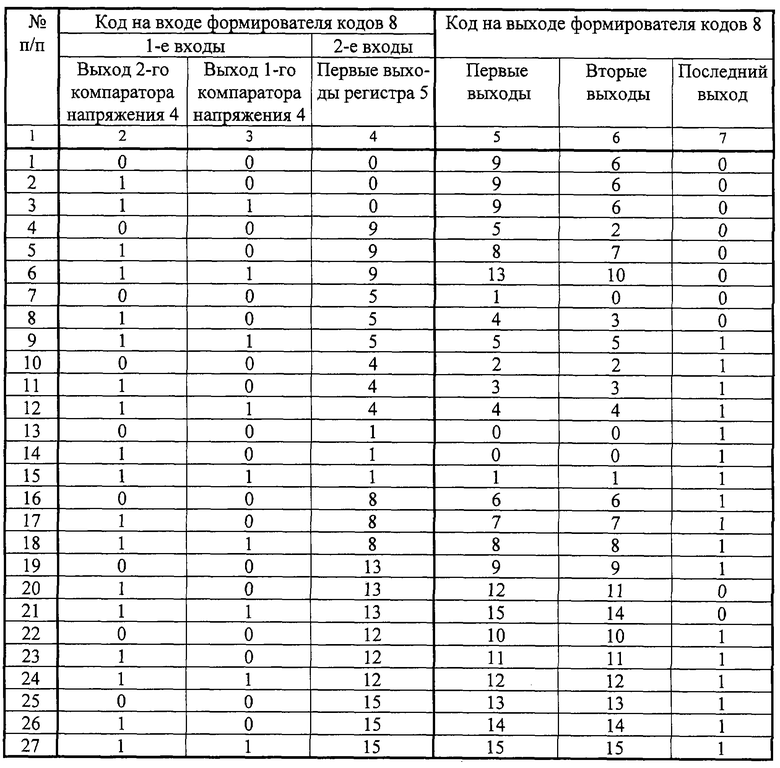

В табл. 1 показано, каким образом формирователь кодов 8 должен преобразовывать коды, поступающие на его входы.

Для примера рассмотрим 4, 5, 6 строки табл.1. В 4-м столбце табл.1 везде стоит цифра 9. Это означает, что на первых выходах регистра 5, которые поступают на вторые входы формирователя кодов 8 установлен код, соответствующий цифре 9. При этом, если на выходе 1-го и 2-го компараторов напряжения 4 будут нули (4-я строка таблицы), то на первых выходах формирователя кодов 8 установится код, соответствующий числу 5 (4-я строка, 5-й столбец таблицы), а на вторых выходах установится код, соответствующий числу 2 (4-я строка, 6-й столбец таблицы). Т.е. организуется переход от вершины 6-9 к вершине 2-5 по дуге 00 (фиг.2). В последнем столбце 4-й строки (соответствующей значению сигнала на последнем выходе формирователя кодов 8) в данном случае стоит ноль, что указывает, что висячая вершина не достигнута и процесс преобразования должен быть продолжен.

Формирователь кодов 8 может быть реализован с помощью постоянного запоминающего устройства или на программируемых логических матрицах. Если в качестве формирователя кодов 8 использовать разделяемое (с компьютером) оперативное запоминающее устройство, то это позволит оперативно изменять процедуру подбора кода.

Рассмотрим работу устройства при выполнении процедуры подбора кода в соответствии с фиг.2 для следующего конкретного случая. Разрядность аналого-цифрового преобразователя - N=4. Устройство содержит два блока ключей 2, два аналоговых сумматора 3 и два компаратора напряжения 4 (М=2). Напряжение питания, подключенное к делителю опорного напряжения на основе резисторной матрицы R-2R 1, равно UП=10В. С помощью делителя опорного напряжения 1 будут сформированы четыре дополнительных опорных напряжения: U3=5,0 В, U2=2,5 В, U1=l,25 В, U0=0,625 В.

Пусть на вход аналого-цифрового преобразователя подано напряжение UВХ=3,2 В.

Работа устройства, и, следовательно, процесс преобразования входного напряжения в код, начинается с подачи на четвертый вход устройства "Пуск" и соответственно на первый вход триггера 7, импульса (в исходном состоянии триггер 7 находится в нулевом состоянии). Триггер 7 переходит в единичное состояние и на его выходе появляется уровень, соответствующий логической единице. При поступлении переднего фронта перепада напряжения с выхода триггера 7 на первый управляющий вход (вход обнуления) регистра 5, он установится в нулевое состояние. На первой группе выходов регистра 5 установится код нуля, который поступит на вторые входы формирователя кодов 8. Согласно таблице (строки 1-3), независимо от кода на выходе компараторов напряжения 4, на первой группе выходов формирователя кодов 8 появится код числа 9 (строки 1-3, столбец 5 табл.1), а на второй группе выходов - код числа 6 (строки 1-3, столбец 6 таблицы).

После перехода триггера 7 в единичное состояние, уровень логической единицы с его выхода поступает также на управляющий вход генератора тактовых импульсов 6, и с его выхода начинают поступать импульсы на второй управляющий вход (вход записи) регистра 5. В регистр 5 по заднему фронту первого импульса с генератора импульсов 6 по первой группе входов будет записан код числа 9, а по второй группе входов - код числа 6. Это соответствует корневой вершине 6-9 графа на фиг.2.

Код числа 9 с первых выходов регистра 5 поступит на управляющие входы первого блока ключей 2 (верхнего по схеме) и к входам первого аналогового сумматора 3 будут подключены опорные напряжения U3 и U0, и напряжение на выходе первого аналогового сумматора будет равным U∑1=5,0+0,625=5,625 В.

Со вторых выходов регистра 5 на управляющие входы второго блока ключей 2 (нижнего по схеме) поступит код числа 6 и к входам второго аналогового сумматора 3 будут подключены опорные напряжения U2 и U1, и напряжение на выходе второго аналогового сумматора 3 будет равным U∑2=2,5+1,25-3,75 В.

С помощью компараторов напряжения 4 производится сравнение напряжений, поступающих с выходов соответствующих аналоговых сумматоров 3 с входным напряжением UВХ=3,2 В. С приходом следующего импульса с генератора тактовых импульсов 6 на стробирующие входы компараторов напряжения 4, по переднему фронту этого импульса производится фиксация результатов сравнения. В данном случае входное напряжение меньше напряжения на выходе и первого и второго аналоговых сумматоров 3 и на выходе компараторов напряжения 4 установится уровень логического нуля.

Итак, на первых входах формирователя кодов 8 установится комбинация 00, а на вторых выходах - код числа 9 (с первой группы выходов регистра 5). В соответствии с таблицей (строка 4) после этого на первых выходах формирователя кодов 8 установится код числа 5 (строка 4, столбец 5 таблицы), а на вторых выходах - код числа 2 (строка 4, столбец 6 таблицы). На фиг.2 это соответствует переходу из вершины 6-9 в вершину 2-5 по условию 00. По заднему фронту второго импульса с генератора тактовых импульсов 6 коды чисел 2 (двоичный код 0010) и 5 (двоичный код 0101) будут записаны в соответствующие разряды регистра 5, которые в дальнейшем поступят на управляющие входы соответствующих блоков ключей 2. На выходе первого аналогового сумматора 3 (верхнего по схеме) появится напряжение U∑1=U2+U0=2,5+0,625=3,125 В, а на выходе второго аналогового сумматора 3 (нижнего по схеме) появится напряжение U∑2=U1=1,25 В. В данном случае имеем UВХ>UM1 и UВХ>UM2. Следовательно, на выходе компараторов напряжения 4 будет комбинация 11. Учитывая, что на вторых входах формирователя кодов 8 установлен код числа 5, то на первых выходах формирователя кодов 8 появится код числа 5 (строка 9 таблицы). При этом на последнем выходе формирователя кодов 8 установится уровень, соответствующий логической единице (строка 9, столбец 7 таблицы). Этот сигнал поступит на второй вход триггера 7 и установит его в нулевое состояние. На выходе триггера установится уровень, соответствующий логическому нулю, который выключит генератор тактовых импульсов 6. Процесс преобразования входного напряжения в код на этом закончится. На выход устройства с первых выходов формирователя кодов 8 поступит результат преобразования, т.е. код числа 6.

Из предыдущего описания следует, что процесс преобразования закончился через два такта работы устройства. Два такта также потребуется при преобразовании напряжения, соответствующего кодам чисел 6, 7, 8, 9. Для других кодов время преобразования составит три такта (фиг.2).

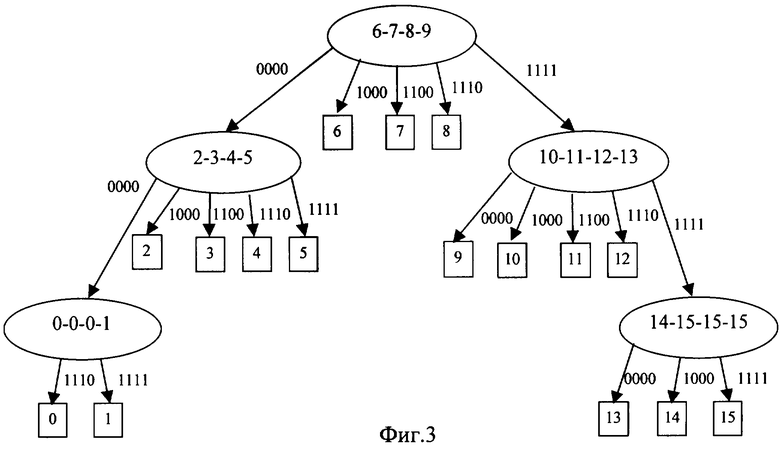

Увеличивая количество блоков ключей 2 и аналоговых сумматоров 3, можно повысить быстродействие устройства. На фиг.3 в виде графа показан процесс подбора кода для АЦП, содержащего 4 блока ключей, 4 аналоговых сумматора и 4 стробируемых компаратора напряжения. В этом случае коды 6, 7, 8 могут быть получены в течение одного такта работы устройства, коды 2, 3, 4, 5, 9, 10, 11, 12 за два такта, и коды 0, 1, 13, 14, 15 за три такта устройства.

Таким образом при том же быстродействии что и в прототипе (используется тот же алгоритм подбора кода), реализация предложенного аналого-цифрового преобразователя требует меньших аппаратных затрат, поскольку вместо мультиплексоров с 2N входами, и содержащими 2N коммутирующих элементов, используются блоки ключей, содержащими N коммутирующих элементов. Делитель опорного напряжения содержит 2N резистора вместо 2N в прототипе. Таким образом, предлагаемое устройство более просто в реализации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 2017 |

|

RU2646356C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2001 |

|

RU2187885C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2001 |

|

RU2183381C1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| ФУНКЦИОНАЛЬНЫЙ АНАЛОГОВО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2013 |

|

RU2549114C2 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1297224A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2007 |

|

RU2359403C1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

Изобретение относится к электроизмерительной и вычислительной технике и может быть использовано для преобразования аналогового напряжения в код. Техническим результатом является упрощение устройства. Устройство содержит делитель опорного напряжения на основе резисторной матрицы R-2R, блок ключей, аналоговый сумматор, компаратор напряжения, регистр, генератор тактовых импульсов, триггер, формирователь кодов. 3 ил., 1 табл.

Аналого-цифровой преобразователь, содержащий делитель опорного напряжения, входы которого являются соответственно первым и вторым входами устройства и предназначены для подключения опорного напряжения, М (М<2N, где N - разрядность аналого-цифрового преобразователя) компараторов напряжения, первые входы которых объединены и являются третьим входом устройства, предназначенный для подачи входного преобразуемого напряжения, регистр, триггер, генератор тактовых импульсов, и формирователь кодов, выходы компараторов напряжения соединены с первыми входами формирователя кодов, первая группа выходов которого является первыми выходами устройства, и подключены к первой группе информационных входов регистра, остальные группы выходов формирователя кодов соединены с соответствующими группами информационных входов регистра, первый вход триггера является четвертым входом устройства, выход триггера, являющийся вторым выходом устройства, подключен к первому управляющему входу регистра и управляющему входу генератора тактовых импульсов, выход которого соединен со стробирующими входами компараторов напряжения и вторым управляющим входом регистра, первая группа выходов которого соединена со вторыми входами формирователя кодов, последний выход которого подключен ко второму входу триггера, отличающийся тем, что в него введены М аналоговых сумматоров, М блоков ключей, одноименные входы которых объединены и подключены к соответствующим выходам делителя опорного напряжения, а выходы соединены с входами соответствующих аналоговых сумматоров, выходы которых соединены со вторыми входами соответствующих компараторов напряжения, управляющие входы блоков ключей соединены с соответствующими группами выходов регистра.

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2001 |

|

RU2183381C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2001 |

|

RU2187885C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО СРАВНЕНИЯ | 1992 |

|

RU2066923C1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1231609A1 |

| US 4829302 А, 09.05.1989 | |||

| US 5870052 А, 09.02.1999. | |||

Авторы

Даты

2004-11-20—Публикация

2002-12-10—Подача