Устройство относится к области цифровой техники, в частности к устройствам преобразования аналогового напряжения в цифровой код.

В процессе цифровой обработки различного рода сигналов самой первой является задача преобразования аналогового сигнала, например напряжения, в цифровую форму.

Известно большое количество различных схем (см., например, 1-8) аналого-цифровых преобразователей (АЦП). Основными их характеристиками являются быстродействие (скорость преобразования) и разрядность преобразования (достижимое количество разрядов в выходном цифровом коде) при разумных экономических критериях.

Известны АЦП прямого преобразования [6-7], в которых входной аналоговый сигнал сравнивается в (2N-1) компараторах с таким же количеством опорных напряжений, различающихся на целое число шагов, равных цене младшего разряда выходного кода. Они обладают самым высоким быстродействием. Их недостаток - сложность и высокая стоимость изготовления, быстро растущие с увеличением числа разрядов. Их разрядность не превышает 8 ([3], стр. 3, 9).

Известны интегрирующие АЦП ([3], стр. 4, 9, [5]), в которых входной сигнал интегрируется в течение фиксированного промежутка времени, а затем дезинтегрируется эталонным напряжением; результат получается как отношение интервала дезинтегрирования к интервалу интегрирования. Они могут обеспечить достаточно высокую разрядность интегрирования и хорошую экономическую эффективность, но их основной недостаток - низкое быстродействие.

Известны сигма-дельта АЦП ([3], стр. 5, 9, [4]), в которых на основе сигма-дельта модуляторов и счета тактовых импульсов, следующих с очень высокой частотой, с последующей цифровой фильтрацией и прореживанием (децимацией) отсчетов получаются требуемые цифровые выборки. Эти АЦП обеспечивают самую высокую разрядность преобразования (24 и более разрядов); их недостатки - низкое быстродействие, лишь немного превышающее быстродействие интегрирующих АЦП, и сложность архитектуры, влекущая за собой высокие требования к технологии производства и соответственно - высокую стоимость.

Известны АЦП с поразрядным взвешиванием, известные также как АЦП последовательного приближения ([3], стр. 3, 9, [2]), содержащие регистр последовательных приближений (РПП), цифроаналоговый преобразователь (ЦАП), компаратор и схему управления, в которых формируемый последовательно в старших разрядах РПП код с помощью ЦАП преобразуется в аналоговую величину, которая в компараторе сравнивается с входным сигналом и по знаку выходного напряжения компаратора схема управления вырабатывает сигнал (лог. 1 или 0) для записи в следующий разряд РПП. Эти АЦП обеспечивают разрядность преобразования 10-12 разрядов и достаточно высокое быстродействие при хороших экономических показателях. Однако дальнейшее повышение разрядности и быстродействия в АЦП этого типа связано с очень большими производственными сложностями, приводящими к резкому возрастанию их стоимости.

Известны конвейерные (pipeline) АЦП ([3], стр. 5, 9), содержащие несколько последовательно соединенных каскадов, причем последний каскад нагружен на точный АЦП. Каждый каскад содержит 4-разрядный АЦП, кодовый выход которого подается на логическую схему коррекции и калибровки и на ЦАП, преобразующий этот код в аналоговый сигнал, который вычитается из входного аналогового сигнала, а остаток поступает на усилитель с фиксированным усилением, выход которого соединен со входом следующего каскада. Выход точного ЦАП также подается на схему коррекции и калибровки, в которой производится корректировка кодов из предыдущих каскадов по кодам из последующих и точного АЦП. Выход этой логической схемы через драйверы дает полную кодовую выборку. Согласно [3], этот АЦП имеет быстродействие, превышающее быстродействие АЦП последовательного приближения, и разрядность выходного кода от 12 до 16 разрядов. Недостатком этого АЦП является сложность архитектуры и вытекающие отсюда проблемы изготовления.

Известный АЦП [1], принятый за прототип, относится к цепочечным (конвейерным) АЦП, и содержит N последовательно соединенных однотипных каскадов по числу разрядов выходного кода и источник эталонного (опорного) напряжения U0 (ИЭН), знак которого совпадает со знаком входного напряжения. Каждый из N каскадов содержит дифференциальный (операционный) усилитель (ДУ) с коэффициентом усиления 2, компаратор (КОМ) и два ключа, вход ДУ первого каскада является входом АЦП, выход ДУ N-го каскада является аналоговым выходом АЦП, служащим для наращивания цепочки аналого-цифрового преобразования, причем прямой вход ДУ соединен с прямым входом КОМ, инвертирующий вход КОМ соединен с ИЭН, выход КОМ, являющийся одновременно цифровым выходом АЦП, соединен с управляющим входом первого ключа и через инвертор - с управляющим входом второго ключа. Вход первого ключа соединен с ИЭН, вход второго ключа соединен с общей шиной (землей), а выходы ключей соединены между собой и подключены к инвертирующему входу ДУ. Этот АЦП имеет высокое быстродействие, но его главный недостаток - высокие требования к технологическому процессу (очень высокая точность подгонки компонент), приводящая к снижению экономических показателей.

Сущность предлагаемого устройства заключается в создании адекватного современной технологии АЦП, обеспечивающего наивысшее достижение потенциально возможного показателя критерия “сложность - стоимость - эффективность”, т.е. обеспечивающего максимальную эффективность при минимальных стоимости и сложности производства. Основной технический результат предлагаемого устройства - повышение разрядности аналого-цифрового преобразования при сохранении достаточно высокого быстродействия и упрощение его архитектуры за счет устранения из прототипа цепочки однотипных каскадов (оставлен только один) и введения аналоговых запоминающих устройств (АЗУ), усилителя постоянного тока (УПТ), устройства управления (УУ), преобразователя последовательного кода в параллельный (ППКП) и счетчика по модулю М (СМ), где М - число разрядов преобразования; введен также входной каскад определения знака входного сигнала и инвертирования последнего в случае, когда он отрицательный.

Технический результат достигается следующим образом.

АЦП последовательного действия (ПД) содержит один каскад цепочечного АЦП, включающий дифференциальный (операционный) усилитель (ДУ) с коэффициентом усиления 2, компаратор (КОМ), два ключа и ИЭН, прямой вход ДУ, являющийся входом АЦП, соединен с прямым входом КОМ, инвертирующий вход КОМ соединен со входом первого ключа и с ИЭН, выход КОМ, являющийся одновременно цифровым (разрядным) выходом АЦП, соединен с управляющим выводом первого ключа и через инвертор - с управляющим выводом второго ключа, вход которого подключен к общей шине (земле), выходы ключей соединены с инвертирующим входом ДУ. С целью обеспечения работоспособности АЦП при устранении цепочки однотипных каскадов в него введены дополнительно три ключа, два коммутируемых АЗУ, УУ, ППКП, СМ и УПТ с коэффициентом усиления по напряжению равным единице, причем прямые входы ДУ и КОМ соединены с входом первого АЗУ и через третий и четвертый ключи - с источником входного сигнала и выходом УПТ соответственно, выход ДУ соединен через пятый ключ со входом второго АЗУ и входом УПТ, информационный вход ППКП соединен с выходом КОМ, первый выход УУ соединен с управляющим выводом третьего ключа, второй выход УУ соединен с управляющим выводом четвертого ключа, третий выход УУ соединен с управляющим выводом пятого ключа, тактовым входом ППКП и со счетным входом СМ, четвертый выход УУ соединен со входом обнуления СМ, а выход переполнения СМ соединен с управляющим входом УУ.

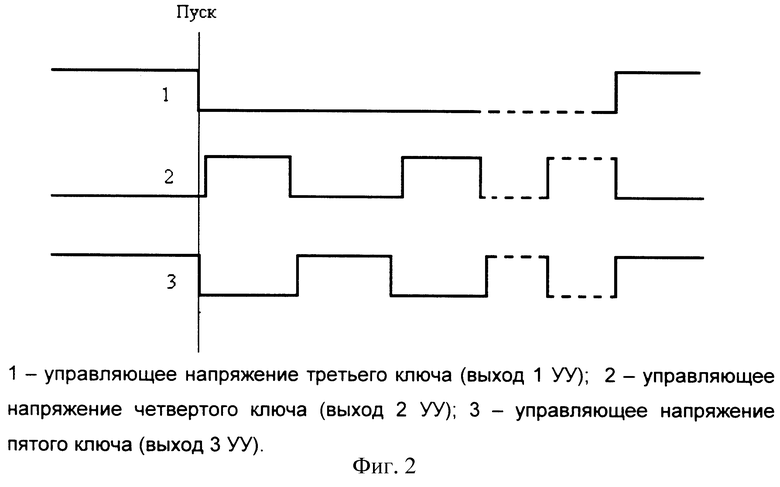

Общая блок-схема АЦП ПД приведена на фиг.1, фиг.2 иллюстрирует его работу.

АЦП ПД содержит: 1, 2, 3, 4, 5 - ключи; 6 - дифференциальный усилитель (ДУ) с коэффициентом усиления 2; 7 - компаратор (КОМ); 8 - усилитель постоянного тока (УПТ) с коэффициентом усиления 1; 9 - инвертор; 10, 11 - аналоговые запоминающие устройства (АЗУ); 12 - устройство управления (УУ); 13 - преобразователь последовательного кода в параллельный (ППКП); 14 - счетчик по модулю М (СМ); входной каскад определения знака и инвертирования отрицательных напряжений.

Работа устройства поясняется диаграммами выходных сигналов УУ.

Устройство работает следующим образом (фиг.2).

В исходном состоянии УУ 12 не работает, потенциалы на его выходах неизменны, причем на первом и третьем выходах они равны единице, на втором нулю. Под действием этих потенциалов третий 3 и пятый 5 будут постоянно замкнуты (открыты), а четвертый 4 - разомкнут (закрыт). Входной аналоговый сигнал поступает на вход первого АЗУ 10, в котором он запоминается, и на прямые входы ДУ 6 и КОМ 7, в которых производится сравнение напряжения этого сигнала с опорным напряжением U0; величина последнего выбирается равной цене старшего разряда (например, половине максимального значения входного напряжения). Если напряжение на входе превысит U0, на выходе КОМ 7 появится логическая (лог.) 1, которая откроет ключ 1 и (через инвертор 9) закроет ключ 2; таким образом, на инвертирующий вход ДУ 6 будет подано опорное напряжение U0. Если же напряжение на входе будет меньше U0, на выходе КОМ 7 появится лог. 0, который закроет ключ 1 и откроет ключ 2: на инвертирующий вход ДУ 6 в этом случае будет подано напряжение, равное 0. Таким образом, на выходе КОМ 7 появится значение первого (старшего) разряда выходного кода, а ДУ 6 произведет вычитание поданного на его инверсный вход напряжения (U0 или 0) из входного и усилит в 2 раза разность напряжений на прямом и инверсном входе; в любом случае эта разность по величине окажется меньше цены разряда (в предельном случае - равна). Выходное напряжение ДУ 6 подается через открытый ключ 5 на вход второго АЗУ 11, где оно запоминается и поступает на вход УПТ 8.

Таким образом, заявляемый АЦП отличает исключительная простота архитектуры. Его структура не зависит от числа разрядов выходного кода и содержит наименьшее по сравнению с известными АЦП количество регулируемых элементов. В нем происходит последовательная (поразрядная) обработка входного сигнала, как в АЦП с поразрядным взвешиванием, следовательно заявляемый АЦП будет иметь такое же быстродействие. Очевидно, что в качестве АЗУ целесообразно применять конденсаторы подходящей емкости. Дополнительным преимуществом заявляемого АЦП является то, что он не требует дополнительного внешнего устройства выборки-хранения.

ИСТОЧНИКИ ИНФОРМАЦИИ

I. Прототип и аналоги:

1. Свидетельство на полезную модель №18330, МПК Н 03 М 1/00, опубл. 10.06.2001: БИПМ, 2001, №16, с.418 (прототип).

2. А.С. СССР №1677872, МПК Н 03 М 1/18, опубл. 20.08.99: БИ №23, 1999, с.338-339 (аналог).

II. Дополнительные источники по уровню техники:

3. Pipeline ADCs come of age. Maxim Engineering Journal, 1999, vol. 33.

4. Заявка РФ №98101746 МПК Н 03 М 3/00, 3/04, опубл. 20.11.99: БИ, 1999, №32, с.63.

5. Пат. РФ №2101859 МПК Н 03 М 1/48, опубл. 10.01.98: БИ, 1998, №1, с.428.

6. Пат. РФ №2110886 МПК Н 03 М 1/34, опубл. 10.05.98: БИ, 1998, №13, с.398.

7. Пат. РФ №2107388 МПК Н 03 М 1/10, опубл. 20.03.98: БИ, 1998, №8, с.504.

8. Заявка РФ №96101790 МПК Н 03 М 1/34, опубл. 20.03.98: БИ, 1998, №8, с.176-177.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь для цифрового радиопередатчика | 2020 |

|

RU2761554C2 |

| СОСТАВНОЙ БЫСТРОДЕЙСТВУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2006 |

|

RU2311731C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ ЕГО КАЛИБРОВКИ | 2006 |

|

RU2341017C2 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1986 |

|

SU1383500A1 |

| Аналого-цифровой преобразователь | 2017 |

|

RU2656989C1 |

| Аналого-цифровой преобразователь | 2017 |

|

RU2646356C1 |

| Способ сбора телеметрической информации и устройство для его осуществления | 1985 |

|

SU1249560A1 |

| Аналого-цифровой преобразователь последовательного приближения | 1981 |

|

SU1018228A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1695499A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЭЛЕКТРИЧЕСКОЙ ЕМКОСТИ ХИМИЧЕСКИХ ИСТОЧНИКОВ ТОКА | 2007 |

|

RU2354985C2 |

Изобретение относится к области цифровой техники, в частности к устройствам преобразования аналогового напряжения в цифровой код. Техническим результатом является повышение разрядности аналого-цифрового преобразователя при сохранении высокого быстродействия и упрощение его архитектуры. Устройство содержит дифференциальные усилители, компаратор, усилитель постоянного тока, аналоговые запоминающие устройства, устройство управления, преобразователь последовательного кода в параллельный, счетчик по модулю М, ключи, инвертор, входной каскад определения знака и инвертирования отрицательных напряжений. 2 ил.

Аналого-цифровой преобразователь (АЦП) последовательного действия (ПД), содержащий дифференциальный усилитель (ДУ), компаратор (КОМ), два ключа, инвертор, источник эталонного напряжения (ИЭН), прямые входы КОМ и ДУ подключены к источнику входного сигнала, выход КОМ, являющийся разрядным выходом АЦП, соединен с управляющим выводом первого ключа и через инвертор - с управляющим выводом второго ключа, вход первого ключа и инвертирующий вход КОМ подключены к ИЭН, вход второго ключа соединен с общим проводом (землей), выходы ключей соединены с инвертирующим входом ДУ, отличающийся тем, что в него дополнительно введены три ключа, усилитель постоянного тока (УПТ) с коэффициентом усиления 1, два аналоговых запоминающих устройства (АЗУ), устройство управления (УУ), счетчик разрядов по модулю М (СМ), где М - число разрядов преобразования, и преобразователь последовательного кода в параллельный (ППКП), причем третий ключ включен между источником входного сигнала и прямыми входами ДУ и КОМ, к которым подключен вход первого АЗУ и выход четвертого ключа, выход ДУ, коэффициент усиления которого равен 2, соединен со входом пятого ключа, выход которого соединен со входом второго АЗУ и со входом УПТ, выход последнего соединен со входом четвертого ключа, первый и второй выходы УУ соединены соответственно с управляющими выводами третьего и четвертого ключей, третий выход УУ соединен с управляющим выводом пятого ключа, со счетным входом СМ и с тактовым входом ППКП, информационный вход которого соединен с выходом КОМ, четвертый выход УУ соединен со входом обнуления СМ, а выход переполнения последнего подключен к управляющему входу УУ.

| Бетон с искусственно-приготовленным пористым наполнительным материалом | 1929 |

|

SU18330A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1993 |

|

RU2110886C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2000 |

|

RU2171543C1 |

| Устройство для выбора многокритериальных решений | 1990 |

|

SU1765834A1 |

| US 4897658 А, 30.01.1990. | |||

Авторы

Даты

2005-01-20—Публикация

2003-02-11—Подача