Изобротенне относится к игзмери- п льной технике и может быть исполь- ;Ювано при построении быстродействую Dp-ix преобразователей информации в системах обработки широкополосных сигналов,.

Целью изобретения является повышение точности и быстродействия преобразования за счет реализации ампли- |удной свертки сигигшов в моменты Оавенства напряжений на входе коммутирующих элементов.

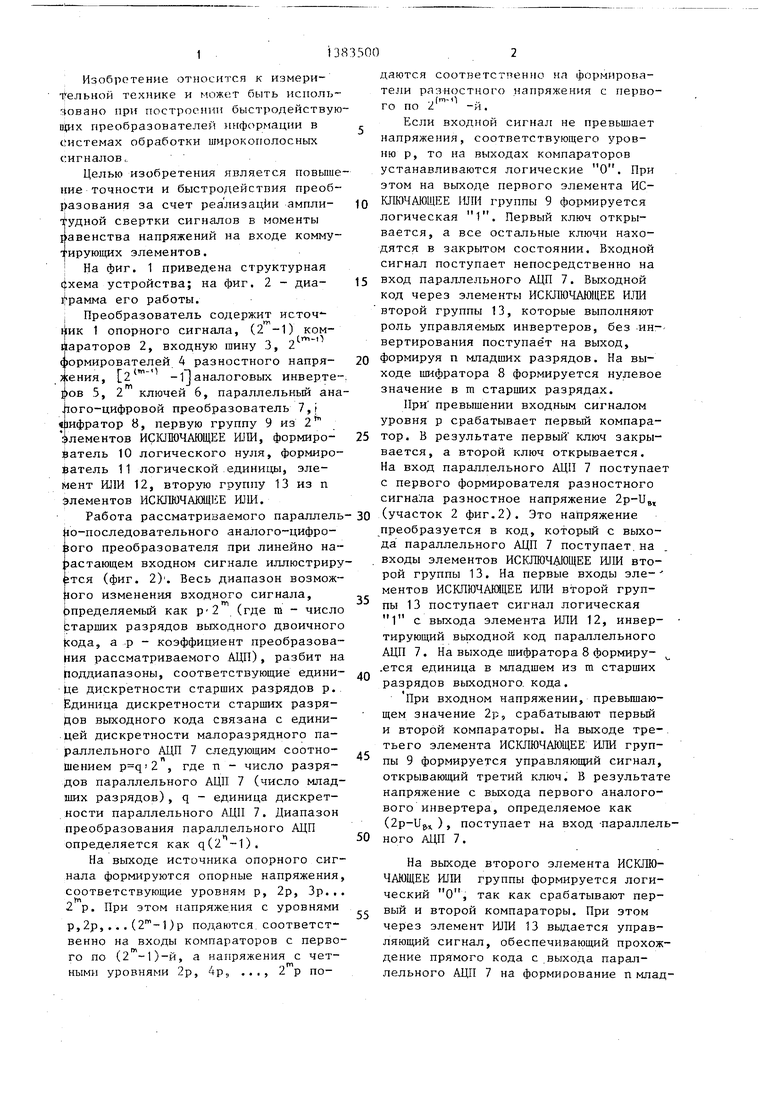

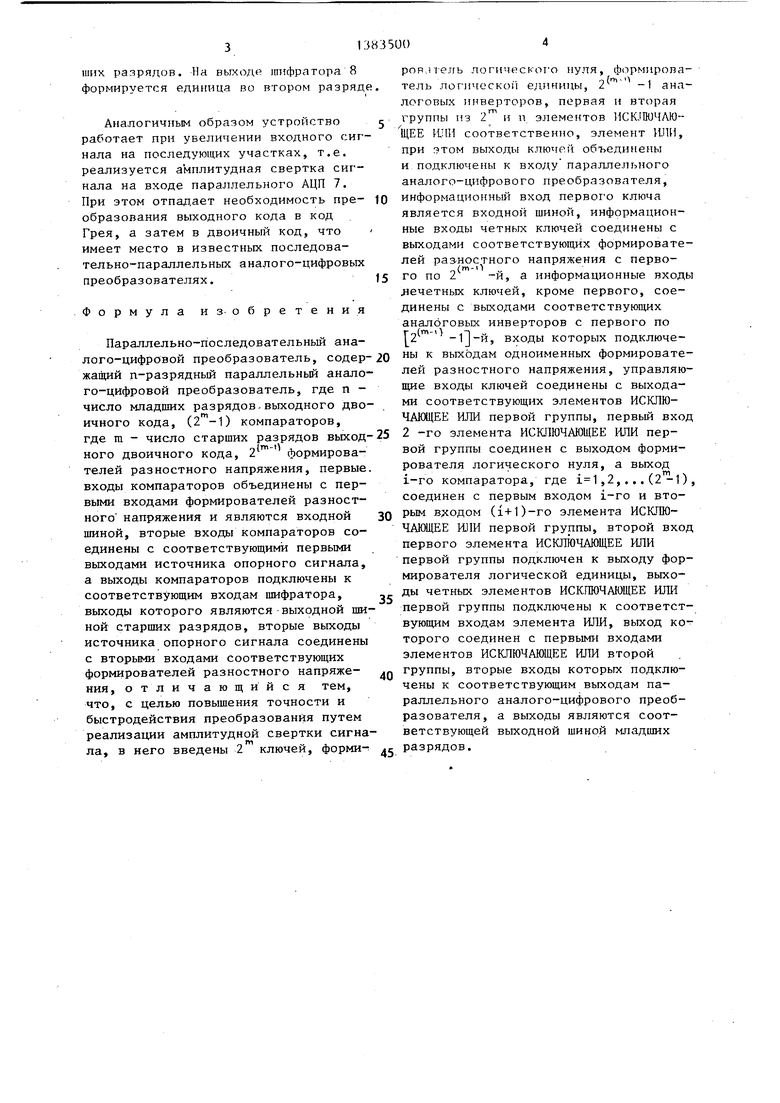

1На фиг. 1 приведена структурная 4хема устройства; на фиг. 2 - диа- li paMMa его работы.

: Преобразователь содержит источ - 1 опорного сигнсша, (2 -1) ком- ijiapaTopoB 2, входную шину 3, 2 формирователей 4 разностного напря- ;ения, -1 аналоговых инвертеров 5, 2 ключей 6, параллельньш аналого-цифровой преобразователь 1, «шфратор 8, первую группу 9 из 2 Элементов ИСКЛЮЧАЮЩЕЕ ШШ, формирователь 10 логического нуля, формирователь 11 логической единицы, элемент ШШ 12, вторую группу 13 из п Элементов ИСКЛЮЧАЮЩЕЕ ШШ.

Работа рассматриваемого параллельно-последовательного аналого-цифро- 13ОГО преобразователя при линейно на- ;застаю1цем входном сигнале иллюстриру 15ТСЯ (фиг. 2). Весь диапазон возмож- jioro изменения входного сигнала, |эпределяемьш как р 2 (где га - число Ьтарших разрядов выходного двоичного Кода, а р - коэффициент преобразования рассматриваемого .АЦП), разбит на loддиaпaзoны, соответствующие единице дискретности старших разрядов р.. Единица дискретности старших разрядов выходного кода связана с единицей дискретности малоразрядного параллельного АЦП 7 следующим соотношением , где п - число разрядов параллельного АЦП 7 (число младших разрядов), q - единица дискретности параллельного АЦП 7. Диапазон преобразования параллельного АЦП определяется как q(2 -1).

На выходе источника опорного сигнала формируются опорные напряжения, соответствующие уровням р, 2р, 3р..

2р. При этом напряжения с уровнями р,2р, .. . ( )р подаются соответственно на входы компараторов с первого по (2 -О-й, а напряжения с четными уровнями

,

2 р подаются соответстпенно на формирователи разностного напряжения с перво.i( го по 2 -и.

Если входной сигнал не превышает напряжения, соответствующего уровню р, то на выходах компараторов устанавли1заются логические О. При этом на выходе первого элемента ИСКЛЮЧАЮЩЕЕ ШШ группы 9 формируется логическая 1. Первый ключ открывается, а все остальные ключи находятся в закрытом состоянии. Входной сигнал поступает непосредственно на

вход параллельного АЦП 7. Выходной код через элементы ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы 13, которые выполняют роль управляемых инвертеров, без -ин-- вертирования поступае т на выход,

формируя п младших разрядов. На выходе шифратора 8 формируется нулевое значение в m старших разрядах.

При превышении входным сигналом уровня р срабатывает первый компаратор. В результате первый ключ закрывается, а второй ключ открывается. На вход параллельного АЦП 7 поступает с первого формирователя разностного сигнала разностное напряжение 2р-ив,

(участок 2 фиг,2). Это напряжение преобразуется в код, который с выхода параллельного АЦП 7 поступает.на . входы элементов ИСКЛЮЧАЮЩЕЕ ШШ второй группы 13. На первые входы эле- ментов ИСКПЮЧАКМЦЕЕ ИЛИ второй группы 13 поступает сигнал логическая 1 с выхода элемента ИЛИ 12, инвертирующий вьрсодной код параллельного АЦП 7. На выходе шифратора 8 формиру- .ется единица в младшем из m старших разрядов выходного, кода.

При входном напряжении, превьш аю- щем значение 2р, срабатывают первый и второй компараторы. На выходе тре-. тьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы 9 формируется управляющий сигнал, открывающий третий ключ. В результате напряжение с выхода первого аналогового инвертера, определяемое как (2p-Ug. ) , поступает на вход -параллельного АЦП 7.

На выходе второго элемента ИСКЛЮЧАЮЩЕЕ ШШ группы формируется логический О, так как срабатывают пер- вый и второй компараторы. При этом через элемент ШШ 13 вьщается управляющий сигнал, обеспечивающий прохождение прямого кода с выхода параллельного АЦП 7 на формирование п млад

ших разрядов. На выходе шифратора 8 формируется единица во втором разряд

Аналогичным образом устройство работает при увеличении входного сигнала на последующих участках, т.е. реализуется амплитудная свертка сигнала на входе параллельного АЦП 7. При этом отпал,ает необходимость пре- образования выходного кода в код Грея, а затем в двоичный код, что имеет место в известных последовательно-параллельных аналого-цифровых преобразователях.

Формула из- обретения

Параллельно-последовательньш аналого-цифровой преобразователь, содержащий п-разрядный параллельньш аналого-цифровой преобразователь, где п - число младших разрядов-выходного двоичного кода, (2 -1) компараторов, где га - число старших разрядов выходного двоичного кода, 2 формирователей разностного напряжения, первые входы компараторов объединены с первыми входами формирователей разностного напряжения и являются входной шиной, вторые входы компараторов соединены с соответствующими первыми выходами источника опорного сигнала, а выходы компараторов подключены к соответствующим входам шифратора, выходы которого являются выходной шиной старших разрядов, вторые выходы источника опорного сигнала соединены с вторыми входами соответствующих формирователей разностного напряже- НИН, отличающийся тем, что, с целью повышения точности и быстродействия преобразования путем реализации амплитудной свертки сигнала, в него введены 2 ключей, форми

poRjrejfb логическот о нуля, формиропа- тель логической единицы, -1 аналоговых инверторов, первая и вторая группы из 2 и II элементов ИСКЛЮЧАЮ-- ЩЕЕ Ш1И соответственно, элемент И.ПИ, при этом выходы ключей объединень и подключены к входу параллельного аналого-цифрового преобразователя, информационный вход первого ключа является входной шиной, информационные входы четных ключей соединены с выходами соответствующих формирователей разностного напряжения с первого по 2 -и, а информационные входы лечетных ключей, кроме первого, соединены с выходами соответствующих аналоговых инверторов с первого по -lj-й, входы которых подключены к выходам одноименных формирователей разностного напряжения, управляющие входы ключей соединены с выходами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, первый вход 2 -го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы соединен с выходом формирователя логического нуля, а выход i-ro компаратора, где ,2, ... (2-1) соединен с первым входом i-ro и вторым входом (1+1)-го элемента ИСКЛЮЧАЮЩЕЕ ШШ первой группы, второй вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы подключен к выходу формирователя логической единицы, выходы четных элементов ИСКПЮЧАЮЩЕЕ ИШ1 первой группы подключены к соответствующим входам элемента ИЛИ, выход которого соединен с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, вторые входы которых подключены к соответствующим выходам параллельного аналого-цифрового преобразователя, а выходы являются соответствующей выходной шиной младших разрядов.

я/Т) P

P

P

X rtopqA ЛЦ/7

Участие,

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельно-последовательный аналого-цифровой преобразователь | 1984 |

|

SU1282326A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1981 |

|

SU1039025A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1982 |

|

SU1069156A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1181144A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU980276A1 |

| Устройство для контроля ресурса коммутационных аппаратов | 1987 |

|

SU1446637A1 |

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ВАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2017156C1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1193808A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1983 |

|

SU1211881A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1152088A1 |

Изобретение относится к области измерительной техники и может быть использовано при построении быстродействующих преобразователей информа«h ции в системах обработки широкополосных сигналов. В устройство, содержащее п-разрядный параллельный аналого- цифровой преобразователь 7, компараторы 2, формирователи 4 разностного напряжения, источник 1 ойорного сигнала и шифратор 8, с целью повышения точности и быстродействия преобразования за счет реализации и амплитудной свертки сигнала и комьгутации сигналов в моменты равенства напряжений на входе и выходе коммутирующих элементов, введены аналоговые инверторы 5, ключи 6, первая и вторая группы 9 и 13 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, формирователи 10 и 11 логических единицы и нуля соответственно и элемент ИЛИ 12. 2 ил. (Л с со 00 00 ел

| Электронная лампа с подогревным катодом | 1941 |

|

SU77470A3 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1982 |

|

SU1069156A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-03-23—Публикация

1986-05-06—Подача