Изобретение относится к области вычислительной техники и может быть использовано при построении универсальных и специализированных управляющих устройств, а также в устройствах диагностирования.

Известны регистры сдвига, например:

Реверсивный регистр сдвига (авторское свидетельство СССР №830577, кл. G 11 С 19/00, 1981). Он содержит ячейки памяти (разряды), каждая из которых выполнена на D-триггере и элементе “И-ИЛИ-НЕ”, два элемента задержки, два элемента “ИЛИ” и элемент “И-ИЛИ”.

Недостатком данного устройства является ограниченная область применения и низкая надежность.

Известен также регистр сдвига (авторское свидетельство РФ №2186428, кл. 7 G 11 С 19/00, 2000). Он содержит установочный блок, входной элемент регистра “ИЛИ”, N-1 блокирующих элементов “ИЛИ”, N разрядов, где N≥3, каждый разряд включает триггер, установочный элемент “И”, управляющий элемент “ИЛИ”, входной элемент триггера “ИЛИ”, все разряды, кроме N-го, содержат разрешающий элемент “И-НЕ” и двухвходовый элемент “И”, а (N-1)-й разряд, кроме того, содержит одновибратор и элемент развязки “ИЛИ”.

Недостатком данного устройства является низкая надежность.

Наиболее близким по технической сущности к предлагаемому регистру сдвига является универсальный регистр сдвига (Справочник по интегральным МС под редакцией Б.В.Тарабрина. М.: Энергия. 1980, с.638), содержащий N-разрядов, где N≥3, N блоков распределения, N-1 элементов “И”, причем информационный выход j-го блока распределения, где j=1,2,...,N, подключен к первому информационному входу j-го разряда, информационный выход i-го разряда, где i=2,3...,N, подключен к информационному входу (i-1)-го элемента “И”, информационный выход которого подключен ко второму информационному входу (i-1)-го блока распределения, информационный выход (i-1)-го разряда соединен с первым информационным входом i-го блока распределения, тактовые входы всех разрядов объединены и являются тактовым входом регистра сдвига, информационные выходы N разрядов являются соответствующими N информационными выходами регистра. Универсальный регистр сдвига выполняет функции сдвига в обоих направлениях и хранения информации.

Однако устройство-прототип имеет недостаток - ограниченную область применения и недостаточно высокую надежность работы. Это связано с тем, что данный регистр сдвига работает как регистр с фиксированным количеством разрядов и не имеет возможности резервирования разрядов за счет отключения отказавших и подключения работоспособных.

Целью изобретения является разработка регистра сдвига, обладающего более широкой областью применения за счет возможности формирования сигнала как в прямом, так и в обратном (реверсивном) направлениях и изменения его длины, а также более высокой надежностью работы за счет определения отказа разрядов в регистре, исключая их из схемы формирования сигнала.

Поставленная цель достигается тем, что в известный универсальный регистр сдвига, содержащий N разрядов, где N≥3, N блоков распределения, N-1 элементов “И”, причем информационный выход j-го блока распределения, где j=1,2,...,N, подключен к первому информационному входу j-го разряда, информационный выход i-го разряда, где i=2,3...,N, подключен к информационному входу (i-1)-го элемента “И”, информационный выход которого подключен ко второму информационному входу (i-1)-го блока распределения, информационный выход (i-1)-го разряда соединен с первым информационным входом i-го блока распределения, тактовые входы всех разрядов объединены и являются тактовым входом регистра сдвига, информационные выходы N разрядов являются соответствующими N информационными выходами регистра, дополнительно введены N блоков переключения, N блоков диагностики, блок установки начального состояния, блок управления регистром. Управляющий и информационный входы блока управления регистром являются, соответственно, управляющим и информационным входами регистра. Управляющие входы блоков распределения с номерами от второго до N-го подключены к первому управляющему выходу блока управления регистром, второй управляющий выход которого подключен к управляющим входам всех элементов “И”.

Первый информационный выход блока управления регистром подключен ко второму информационному входу N-го блока распределения. Второй информационный и третий управляющий выходы блока управления регистром подключены соответственно к первому информационному и управляющему входам первого блока распределения. Информационный выход j-го блока распределения подключен к информационному входу j-го блока переключения, разрешающий вход которого подключен к разрешающему выходу j-го разряда. Информационный выход j-го блока переключения подключен ко второму информационному входу j-го разряда. Первый и второй установочные выходы блока установки начального состояния подключены соответственно к первым и вторым установочным входам всех разрядов. Разрешающий выход j-го блока диагностики подключен к разрешающему входу j-го разряда, первый и второй проверочные выходы которого подключены соответственно к первому и второму проверочным входам j-го блока диагностики. Отключающие входы N блоков диагностики являются соответствующими N отключающими входами регистра.

Разряд состоит из DV-триггера, двухвходового элемента “И” и двухвходового элемента “ИЛИ”, второй вход двухвходового элемента “И” подключен к разрешающему V-входу триггера и является разрешающим выходом разряда. Выход двухвходового элемента “И” подключен к первому установочному  -входу триггера, прямой выход которого подключен ко второму входу двухвходового элемента “ИЛИ”, выход которого является информационным выходом разряда. Первый вход двухвходового элемента “ИЛИ” является вторым информационным входом разряда, причем прямой и инверсный выходы триггера являются, соответственно, вторым и первым проверочными выходами разряда. Второй установочный

-входу триггера, прямой выход которого подключен ко второму входу двухвходового элемента “ИЛИ”, выход которого является информационным выходом разряда. Первый вход двухвходового элемента “ИЛИ” является вторым информационным входом разряда, причем прямой и инверсный выходы триггера являются, соответственно, вторым и первым проверочными выходами разряда. Второй установочный  -вход и С тактовый вход триггера являются, соответственно, вторым установочным и тактовым входами разряда, разрешающий V-вход и информационный D-вход триггера являются, соответственно, разрешающим и информационным входами разряда, а первый вход двухвходового элемента “И” является первым установочным входом разряда.

-вход и С тактовый вход триггера являются, соответственно, вторым установочным и тактовым входами разряда, разрешающий V-вход и информационный D-вход триггера являются, соответственно, разрешающим и информационным входами разряда, а первый вход двухвходового элемента “И” является первым установочным входом разряда.

Блок переключения состоит из одновходового элемента “И-НЕ” и двухвходового элемента “И”, инверсный выход одновходового элемента “И-НЕ” подключен ко второму входу двухвходового элемента “И”, первый вход которого является информационным входом блока переключения, причем вход одновходового элемента “И-НЕ” является разрешающим входом блока переключения, а выход двухвходового элемента “И” является информационным выходом блока переключения.

Блок распределения состоит из двухвходового элемента “ИЛИ” и двухвходового элемента “И”, первый и второй входы которого являются, соответственно, управляющим и первым информационным входами блока распределения, выход двухвходового элемента “И” соединен со вторым входом двухвходового элемента “ИЛИ”, выход которого является информационным выходом блока распределения, первый вход двухвходового элемента “ИЛИ” соединен со вторым информационным входом блока распределения.

Блок диагностики состоит из двухвходового элемента “И” и сумматора по модулю два “М2”, первый и второй входы которого, соответственно, подключены к первому и второму проверочным входам блока диагностики, выход сумматора по модулю два “М2” подключен ко второму входу двухвходового элемента “И”, первый вход которого является отключающим входом блока диагностики, выход двухвходового элемента “И” является разрешающим выходом блока диагностики.

Блок управления регистром состоит из двух одновходовых элементов “ИЛИ-НЕ” и двухвходового элемента “И”, выход которого является первым информационным выходом блока управления регистром, вход первого одновходового элемента “ИЛИ-НЕ” является управляющим входом блока управления регистром, а его инверсный выход соединен со входом второго одновходового элемента “ИЛИ-НЕ”, причем инверсный выход первого одновходового элемента “ИЛИ-НЕ” является первым и третьим управляющими выходами блока управления регистром, а инверсный выход второго одновходового элемента “ИЛИ-НЕ” подключен ко второму управляющему выходу блока управления регистром и соединен с первым входом двухвходового элемента “И”, второй вход которого является информационным входом блока управления регистром и соединен с его вторым информационным выходом.

Блок установки начального состояния представляет собой источник постоянного тока и цепочку элементов из резистора R и конденсатора С. Первый отвод резистора R подключен к первой обкладке конденсатора С и является первым установочным выходом блока установки начального состояния. Второй отвод сопротивления R подключен к положительной клемме источника постоянного тока и является вторым установочным выходом блока установки начального состояния. Вторая обкладка конденсатора С и отрицательная клемма источника постоянного тока подключены к корпусу.

Благодаря новой совокупности существенных признаков и введению дополнительно N блоков переключения 2, N блоков диагностики 4, блока установки начального состояния 6, блока управления регистром 5 со связями между ними обеспечивается возможность работы регистра сдвига при изменяемом количестве информационных разрядов, а также исключения в формировании выходной последовательности сигнала отказавших разрядов за счет их самодиагностики, что расширяет область применения и повышает надежность функционирования заявленного устройства.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественными всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного изобретения условию патентоспособности "новизна".

Результаты поиска известных решений в данной и смежной областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность выявления предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности "изобретательский уровень".

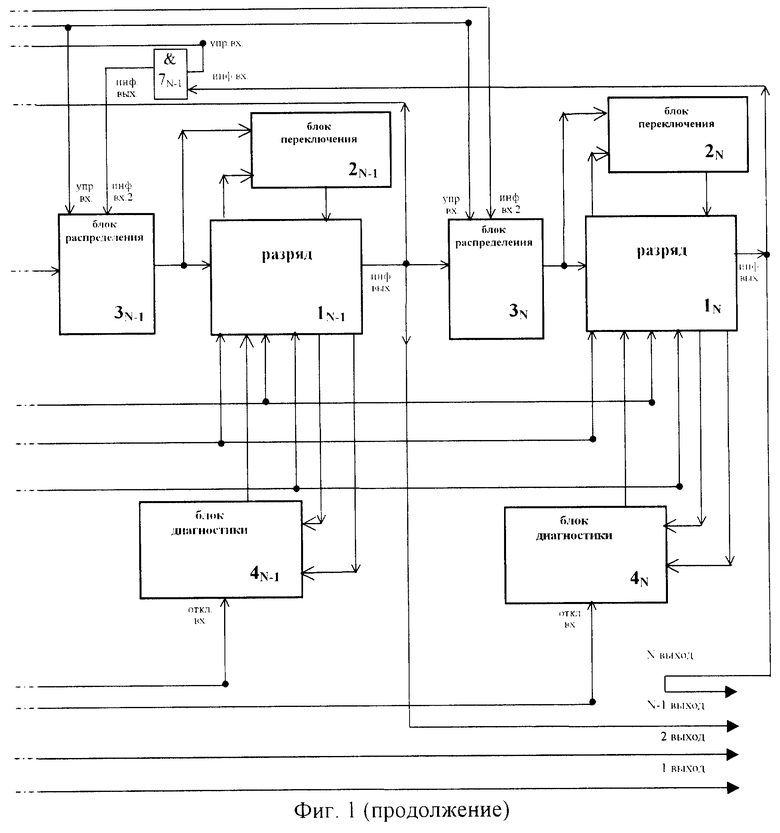

Заявленное устройство поясняется схемами:

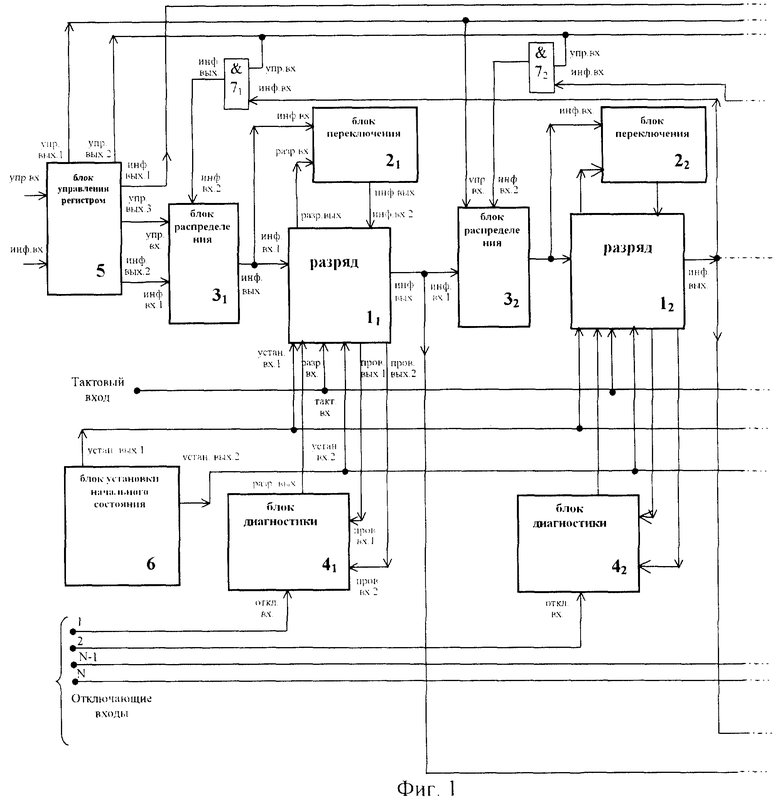

фиг.1 - схема регистра сдвига;

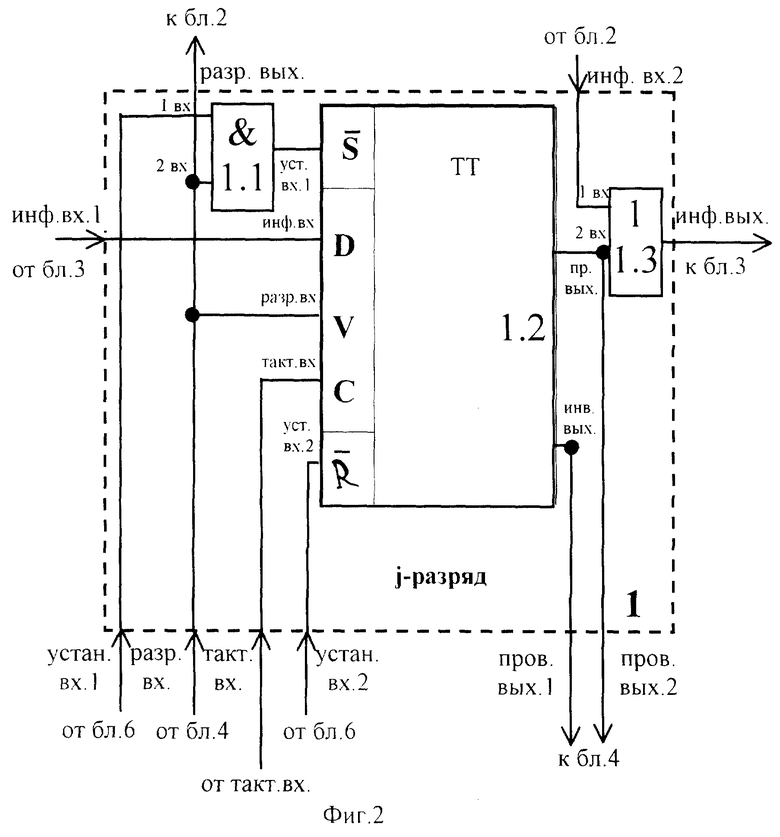

фиг.2 - схема разряда;

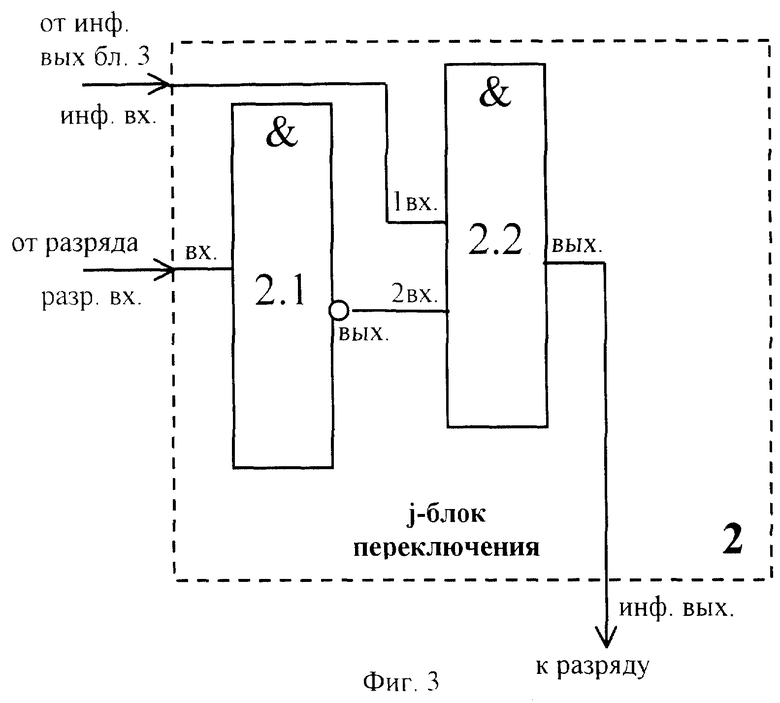

фиг.3 - схема блока переключения;

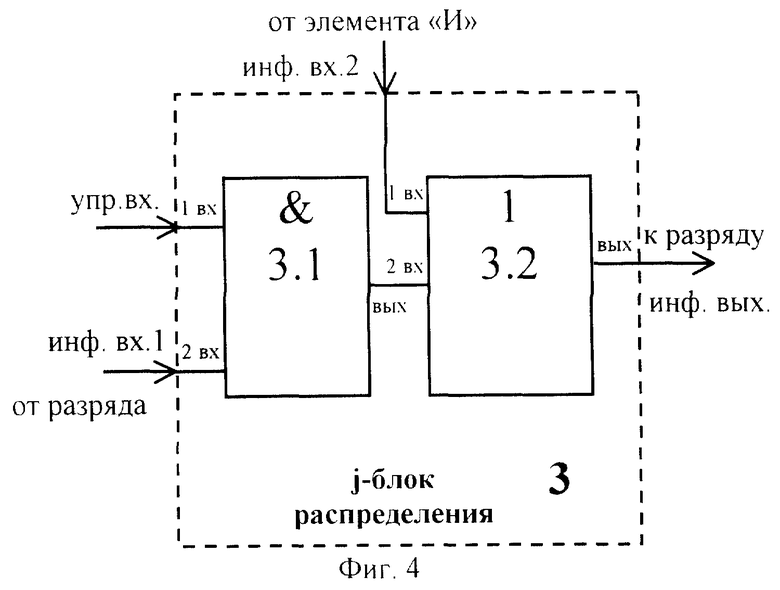

фиг.4 - схема блока распределения;

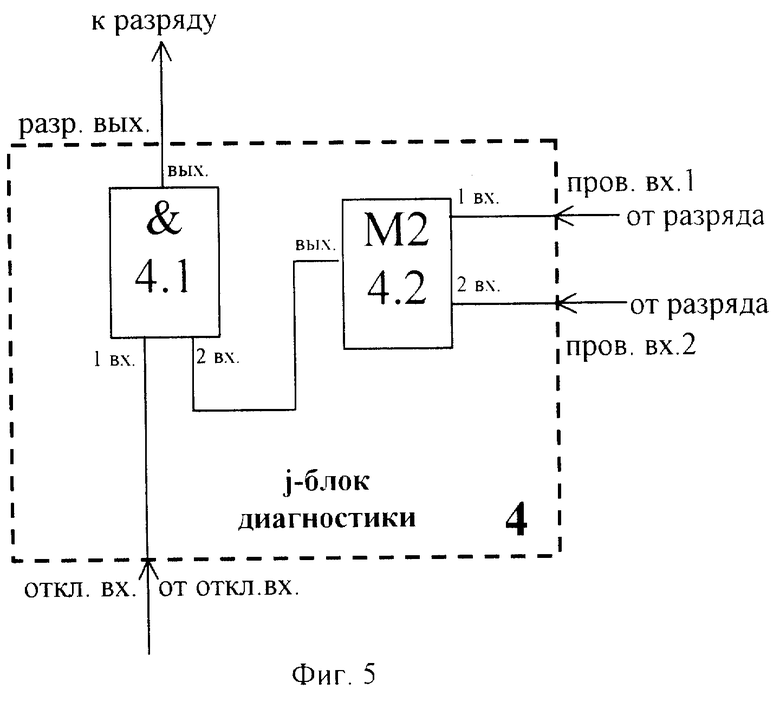

фиг.5 - схема блока диагностики;

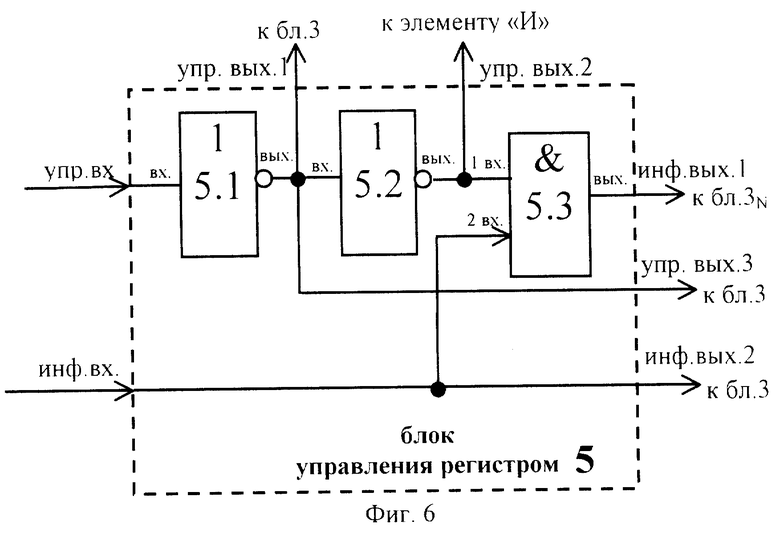

фиг.6 - схема блока управления регистром;

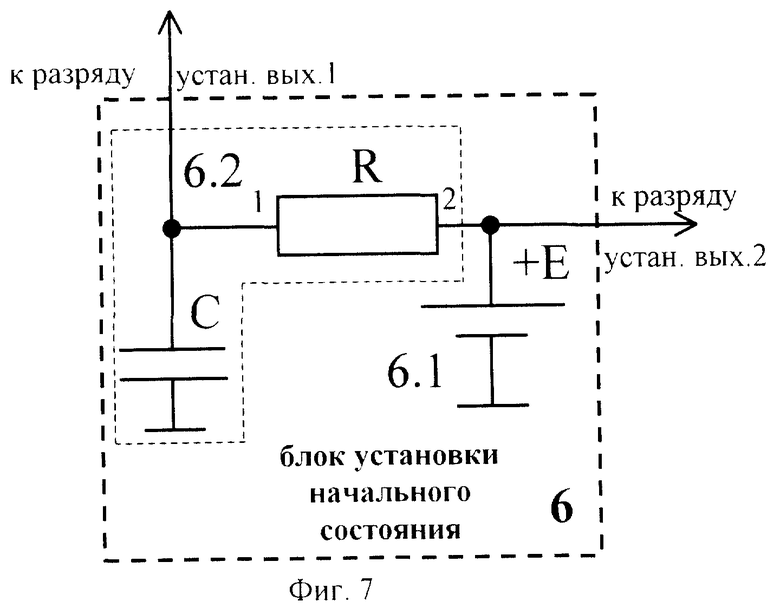

фиг.7 - схема блока установки начального состояния.

Регистр сдвига, показанный на Фиг.1, состоит из N разрядов 11,12,...1N, где N≥3, N блоков переключения 21,22,...2N, N блоков распределения 31,32,...3N, N блоков диагностики 41,42,...4N, блока управления регистром 5, блока установки начального состояния 6 и N-1 элементов “И” 71,72,...7N-1.

Информационный выход j-го блока распределения 3, где j=1,2,...,N, подключен к первому информационному входу j-го разряда 1. Информационный выход i-го разряда 1, где i=2,3...,N, подключен к информационному входу (i-1)-го элемента “И” 7, информационный выход которого подключен ко второму информационному входу (i-1)-го блока распределения 3. Информационный выход (i-1)-го разряда 1 соединен с первым информационным входом i-го блока распределения 3. Тактовые входы всех разрядов объединены и являются тактовым входом регистра сдвига, а информационные выходы N разрядов 1 являются соответствующими N информационными выходами регистра. Управляющий и информационный входы блока управления регистром 5 являются, соответственно, управляющим и информационным входами регистра. Управляющие входы блоков распределения 3 с номерами от второго до N-го подключены к первому управляющему выходу блока управления регистром 5, второй управляющий выход которого подключен к управляющим входам всех элементов “И” 7. Первый информационный выход блока управления регистром 5 подключен ко второму информационному входу N-го блока распределения 3. Второй информационный и третий управляющий выходы блока управления регистром 5 подключены соответственно к первому информационному и управляющему входам первого блока распределения 3. Информационный выход j-го блока распределения 3 подключен к информационному входу j-го блока переключения 2, разрешающий вход которого подключен к разрешающему выходу j-го разряда 1. Информационный выход j-го блока переключения 2 подключен ко второму информационному входу j-го разряда 1. Первый и второй установочные выходы блока установки начального состояния 6 подключены, соответственно, к первым и вторым установочным входам всех разрядов 1.

Разрешающий выход j-го блока диагностики 4 подключен к разрешающему входу j-го разряда 1, первый и второй проверочные выходы которого подключены, соответственно, к первому и второму проверочным входам j-го блока диагностики 4. Отключающие входы N блоков диагностики 4 являются соответствующими N отключающими входами регистра.

Каждый разряд 1 регистра сдвига предназначен для записи и хранения информации. Он может быть реализован в виде схемы, показанной на Фиг.2. Разряд 1 состоит из DV-триггера 1.2, двухвходового элемента “И” 1.1 и двухвходового элемента “ИЛИ” 1.3. Второй вход двухвходового элемента “И” 1.1 подключен к разрешающему V-входу триггера 1.2 и является разрешающим выходом разряда 1. Выход двухвходового элемента “И” 1.1 подключен к первому установочному  -входу триггера 1.2, прямой выход которого подключен ко второму входу двухвходового элемента “ИЛИ” 1.3. Выход двухвходового элемента “ИЛИ” 1.3 является информационным выходом разряда 1. Первый вход двухвходового элемента “ИЛИ” 1.3 является вторым информационным входом разряда 1. Прямой и инверсный выходы триггера 1.2 являются, соответственно, вторым и первым проверочными выходами разряда 1. Второй установочный

-входу триггера 1.2, прямой выход которого подключен ко второму входу двухвходового элемента “ИЛИ” 1.3. Выход двухвходового элемента “ИЛИ” 1.3 является информационным выходом разряда 1. Первый вход двухвходового элемента “ИЛИ” 1.3 является вторым информационным входом разряда 1. Прямой и инверсный выходы триггера 1.2 являются, соответственно, вторым и первым проверочными выходами разряда 1. Второй установочный  -вход и тактовый С-вход триггера 1.2 являются, соответственно, вторым установочным и тактовым входами разряда 1. Разрешающий V-вход и информационный D-вход триггера 1.2 являются, соответственно, разрешающим и первым информационным входами разряда 1. Первый вход двухвходового элемента “И” 1.1 является первым установочным входом разряда 1.

-вход и тактовый С-вход триггера 1.2 являются, соответственно, вторым установочным и тактовым входами разряда 1. Разрешающий V-вход и информационный D-вход триггера 1.2 являются, соответственно, разрешающим и первым информационным входами разряда 1. Первый вход двухвходового элемента “И” 1.1 является первым установочным входом разряда 1.

Блок переключения 2 предназначен для передачи сигналов в обход разряда 1, исключаемого из формируемой последовательности сигналов. Он может быть реализован в виде схемы, показанной на Фиг.3. Блок переключения 2 состоит из одновходового элемента “И-НЕ” 2.1 и двухвходового элемента “И” 2.2. Инверсный выход одновходового элемента “И-НЕ” 2.1 подключен ко второму входу двухвходового элемента “И” 2.2. Первый вход двухвходового элемента “И” 2.2 является информационным входом блока переключения 2. Вход одновходового элемента “И-НЕ” 2.1 является разрешающим входом блока переключения 2. Выход двухвходового элемента “И” 2.2 является информационным выходом блока переключения 2.

Блок распределения 3 предназначен для выбора сигналов в различных режимах работы регистра. Он может быть реализован в виде схемы, показанной на Фиг.4. Блок распределения 3 состоит из двухвходового элемента “ИЛИ” 3.2 и двухвходового элемента “И” 3.1. Первый и второй входы двухвходового элемента “И” 3.1 являются, соответственно, управляющим и первым информационным входами блока распределения 3. Выход двухвходового элемента “И” 3.1 соединен со вторым входом двухвходового элемента “ИЛИ” 3.2. Выход двухвходового элемента “ИЛИ” 3.2 является информационным выходом блока распределения 3. Первый вход двухвходового элемента “ИЛИ” 3.2 соединен со вторым информационным входом блока распределения 3.

Блок диагностики 4 предназначен для управления отключением разряда 1. Он может быть реализован в виде схемы, показанной на Фиг.5. Блок диагностики 4 состоит из сумматора по модулю два “М2” 4.2 и двухвходового элемента “И” 4.1. Первый и второй входы сумматора по модулю два “М2” 4.2, соответственно, подключены к первому и второму проверочным входам блока диагностики 4. Выход сумматора по модулю два “М2” 4.2 подключен ко второму входу двухвходового элемента “И” 4.1. Первый вход двухвходового элемента “И” 4.1 является отключающим входом блока диагностики 4. Выход двухвходового элемента “И” 4.1 является разрешающим выходом блока диагностики 4.

Блок управления регистром 5 предназначен для формирования сигналов управления режимами работы регистра. Он может быть реализован в виде схемы, показанной на Фиг.6. Блок управления 5 состоит из двухвходового элемента “И” 5.3, первого одновходового элемента “ИЛИ-НЕ” 5.1, второго одновходового элемента “ИЛИ-НЕ” 5.2. Выход двухвходового элемента “И” 5.3 является первым информационным выходом блока управления регистром 5. Вход первого одновходового элемента “ИЛИ-НЕ” 5.1 является управляющим входом блока управления регистром 5. Инверсный выход одновходового элемента “ИЛИ-НЕ” 5.1 соединен со входом второго одновходового элемента “ИЛИ-НЕ” 5.2. Инверсный выход первого одновходового элемента “ИЛИ-НЕ” 5.1 является первым и третьим управляющими выходами блока управления регистром 5. Инверсный выход второго одновходового элемента “ИЛИ-НЕ” 5.2 подключен ко второму управляющему выходу блока управления регистром 5 и соединен с первым входом двухвходового элемента “И” 5.3. Второй вход двухвходового элемента “И” 5.3 является информационным входом блока управления регистром 5 и соединен с его вторым информационным выходом.

Блок установки начального состояния 6 предназначен для установки начального состояния регистра. Он может быть реализован в виде схемы, показанной на Фиг.5. Блок установки начального состояния 6 представляет собой источник постоянного тока 6.1 и цепочку элементов 6.2 из резистора R и конденсатора С. Первый отвод резистора R подключен к первой обкладке конденсатора С и является первым установочным выходом блока установки начального состояния 6. Второй отвод сопротивления R подключен к положительной клемме источника постоянного тока 6.1 и является вторым установочным выходом блока установки начального состояния 6. Вторая обкладка конденсатора С и отрицательная клемма источника постоянного тока 6.1 подключены к корпусу.

Входящие в общую структуру регистра сдвига элементы являются типовыми и могут быть технически реализованы в настоящее время при использовании имеющейся элементной базы.

DV-триггеры (1,2,...N) могут быть реализованы на интегральных микросхемах, описанных в книге: В.А.Батушев, В.Н.Вениаминов, В.Г.Ковалева и др. Микросхемы и их применение. - М.: Энергия, 1978, с.164-168.

Сумматор по модулю два “М2” может быть реализован на интегральных микросхемах, описанных в книге: Цифровые интегральные микросхемы: Справочник /П.П.Мальцев, П.С.Долидзе, М.И.Критенко и др. - М.: Радио и связь, 1994, c.109.

Входящие в рассмотренные блоки элементы “И”, “ИЛИ”, “И-НЕ”, “ИЛИ-НЕ”, могут быть реализованы на интегральных микросхемах, описанных в книге: Справочник / П.П.Мальцев, Н.С.Долидзе, М.И.Критенко и др. - М.: Радио и связь, 1994, с.234-237.

RC-цепь выполняет функцию фильтра нижних частот. Номиналы сопротивления и емкости выбираются исходя из допустимого времени переходных процессов.

Регистр сдвига работает следующим образом.

При включении питания 1.21,1.22,...1.2N-1 1.2N триггеры (Фиг.2) устанавливаются в исходное состояние благодаря кратковременной подаче на установочные входы  всех триггеров низкого уровня сигнала (“0”) через конденсатор С блока установки начального состояния 6 (Фиг.7), а на

всех триггеров низкого уровня сигнала (“0”) через конденсатор С блока установки начального состояния 6 (Фиг.7), а на  входы всех триггеров высокого уровня сигнала (“1”). По мере заряда конденсатора С блока установки начального состояния 6 через резистор R на первых входах элементов “И” 1.11, 1.12,...1.1N-1 1.1N триггеров 1.2 (Фиг.2) устанавливается высокий уровень сигнала. Разряды подготовлены к работе по управляющим входам.

входы всех триггеров высокого уровня сигнала (“1”). По мере заряда конденсатора С блока установки начального состояния 6 через резистор R на первых входах элементов “И” 1.11, 1.12,...1.1N-1 1.1N триггеров 1.2 (Фиг.2) устанавливается высокий уровень сигнала. Разряды подготовлены к работе по управляющим входам.

В зависимости от наличия и вида сигналов на управляющем входе блока управления регистром 5 и на отключающих N-входах устройства (Фиг.1) регистр может работать в следующих режимах:

1. Режим прямого прохождения сигнала при фиксированной длине регистра.

2. Режим реверсивного (обратного) прохождения сигнала при фиксированной длине регистра.

3. Режим работы регистра сдвига при автоматическом отключении разрядов.

4. Режим работы регистра сдвига при принудительном отключении разрядов.

Работа регистра сдвига при прямом прохождении сигнала с фиксированной длиной происходит при подаче на управляющий вход регистра низкого уровня сигнала “0”, а на отключающие 1,2,…,N входы регистра логической “1” (Фиг.1).

При подаче на управляющий вход регистра логического “0” (Фиг.1) на входе элемента “ИЛИ-НЕ” 5.1 блока управления регистром 5 появляется логический “0” (Фиг.6). С инверсного выхода элемента “ИЛИ-НЕ” 5.1 сигнал логической “1” через первый и третий управляющие выходы блока управления регистром 5 поступает, соответственно, на управляющий вход 2,...,N и первого блоков распределения 3, далее на первый вход двухвходового элемента “И” 3.1 (Фиг.4). В результате сигнал на выходе двухвходового элемента “И” 3.1 1,2,...,N блоков распределения 3 будет зависеть от сигнала на втором входе, то есть от информационного. Логическая “1” также поступает на вход одновходового элемента “ИЛИ-НЕ” 5.2 (Фиг.6), с инверсного выхода которого логический “0” через второй управляющий выход блока управления регистром 5 поступает на управляющий вход 71, 72,...7N-1 элементов “И”, исключая их из работы в этом режиме (Фиг.1), и на первый вход двухвходового элемента “И” 5.3 блока управления регистром 5 (Фиг.6), с выхода которого сигнал логического “0” поступает через первый информационный выход блока управления регистром 5 на второй информационный вход N-го блока распределения 3 (Фиг.1) и далее на первый вход двухвходового элемента “ИЛИ” 3.2 (Фиг.4). Таким образом из схемы исключается обратная связь (элементы 71, 72,...7N-1 “И”) и сигнал на выходе элементов “ИЛИ” 3.2 N-го блока распределения 3 будет зависеть от сигнала на втором его входе, то есть от информационного сигнала с (N-1)-го разряда. При подаче на 1,2,...,N отключающие входы регистра сдвига высокого уровня сигнала логическая “1” поступает на соответствующие отключающие входы 41, 42,...4N-1 4N блоков диагностики (Фиг.1). С отключающего входа блока диагностики 4 сигнал логической “1” поступает на первый вход двухвходового элемента “И” 4.1 (Фиг.5) и далее через разрешающий выход блока диагностики 4 на разрешающий вход разряда 1 (Фиг.1), на установочный вход  и разрешающий V-вход триггера 1.2 (Фиг.2).

и разрешающий V-вход триггера 1.2 (Фиг.2).

В этом случае триггеры 1.21, 1.22,...1.2N-1 1.2N всех разрядов подготовлены к работе по информационному D-входу (на установочных входах

и на разрешающем V-входе 1.21,1.22,...1.2N-1 1.2N триггеров имеется “1”). При этом на прямых выходах всех триггеров 1.2 будет логический “0” (Фиг.2). Регистр сдвига готов к работе при прямом прохождении сигнала.

и на разрешающем V-входе 1.21,1.22,...1.2N-1 1.2N триггеров имеется “1”). При этом на прямых выходах всех триггеров 1.2 будет логический “0” (Фиг.2). Регистр сдвига готов к работе при прямом прохождении сигнала.

При подаче на 1,2,...,N тактовые С входы (Фиг.1) 1.21,1.22,...1.2N-1 1.2N триггеров сдвигающего синхросигнала, а на информационный вход регистра логической “1” (Фиг.1), “1” записывается в триггер 1.2 первого разряда 11. С приходом следующего сдвигающего синхросигнала логическая “1” из триггера 1.21 будет перезаписываться в триггер 1.22 следующего, второго разряда 12. Считывание информации осуществляется на 1,2,...,N выходах регистра сдвига (Фиг.1).

Работа регистра сдвига с фиксированной длиной (количеством разрядов) при реверсивном (обратном) прохождении сигнала происходит при подаче на управляющий вход и на отключающие 1,2,...N входы регистра высокого уровня сигнала “1” (Фиг.1).

При подаче на управляющий вход регистра логической “1” на входе элемента “ИЛИ-НЕ” 5.1 блока управления регистром 5 появляется логическая “1” (Фиг.6). С инверсного выхода элемента “ИЛИ-НЕ” 5.1 сигнал логического “0” через первый и третий управляющие выходы блока управления регистром 5 поступает, соответственно, на управляющий вход 2,...N и первого блоков распределения 3 (Фиг.1) и далее на первый вход двухвходового элемента “И” 3.1 (Фиг.4), исключающий его из работы, и на вход одновходового элемента “ИЛИ-НЕ” 5.2 блока управления регистром 5 (Фиг.6). С инверсного выхода элемента “ИЛИ-НЕ” 5.2 сигнал логической “1” через второй управляющий выход блока управления регистром 5 поступает на управляющий вход 71, 72,...7N-1 элементов “И”, включая тем самым их в работу (Фиг.1), и на первый вход двухвходового элемента “И” 5.3 блока управления регистром 5 (Фиг.6), с выхода которого сигнал, в зависимости от сигнала на информационном входе регистра, поступает через первый информационный выход блока управления регистром 5 на второй информационный вход N-го блока распределения 3 (Фиг.1) и далее на первый вход двухвходового элемента “ИЛИ” 3.2 (Фиг.4). В результате, исключая из работы двухвходового элемента “И” 3.1 1,2,...N блоков распределения 3 и включая обратную связь (элементы 71, 72,...7N-1 “И”), обеспечивается работа регистра при реверсивном (обратном) прохождении сигнала. При подаче сигнала логической “1” на 1,2,…N отключающие входы регистра сдвига его работа аналогична описанному выше.

При подаче на 1,2,...N тактовые входы С триггера 1.21,1.22,...1.2N-1 1.2N сдвигающего синхросигнала, а на информационный вход регистра логической “1” (Фиг.1) логическая “1” записывается через второй информационный вход N-го блока распределения 3 в триггер 1.2 N-го разряда, а логический “0” через прямой выход триггера 1.2 N-го разряда и элемент “ИЛИ” 1.3 (Фиг.2) с информационных выходов 2,3,...N разрядов, поступая на информационные входы соответствующих 71, 72,...7N-1 элементов “И”, перезаписывается в предыдущие разряды 1 регистра сдвига (Фиг.1). С приходом следующего сдвигающего синхросигнала логическая “1” из триггера 1.2 N-го разряда через 7N-1 элемент “И” перезаписывается в триггер 1.2 N-1 разряда. Считывание информации осуществляется на 1,2,...N выходах регистра сдвига (Фиг.1).

Работа регистра сдвига при автоматическом отключении элементов (разрядов) происходит при возникновении на прямом и инверсном выходах триггера 1.2 любого из 1,2,...N разрядов 1 запрещенной комбинации 00 или 11 (сбоя) (Фиг.2). При этом с первого и второго проверочных выходов соответствующего разряда 1 (Фиг.1) через первый и второй проверочные входы соответствующего блока диагностики 4 на первый и второй входы сумматора по модулю два “М2” 4.2 (Фиг.5) поступают одинаковые сигналы. В этом случае с выхода сумматора по модулю два “М2” 4.2 блока диагностики 4 на второй вход двухвходового элемента “И” 4.1 поступает сигнал логического “0”. В результате, независимо от сигнала на первом входе двухвходового элемента “И” 4.1 блока диагностики 4, с его выхода и разрешающего выхода соответствующего блока диагностики 4 сигнал логического “0” будет подан на установочный вход  на разрешающий V-вход триггера 1.2 соответствующего разряда (Фиг.2) и на разрешающий вход блока переключения 2 (Фиг.1). Разрешающий V-вход триггера 1.2 опрокинет данный триггер в “0” состояние, запретит его работу по информационному D-входу (Фиг.2) и через схему “И-НЕ” 2.1 и двухвходовый элемент “И” 2.2 соответствующего блока переключения 2 (Фиг.3) разрешит передачу сигналов на элемент “ИЛИ” 1.3 разряда 1 (Фиг.2) и далее на следующий разряд 1. Таким образом, данный разряд 1 будет исключен из схемы формирования сигнала как при прохождении сигнала в прямом, так и обратном направлении (в режиме реверса).

на разрешающий V-вход триггера 1.2 соответствующего разряда (Фиг.2) и на разрешающий вход блока переключения 2 (Фиг.1). Разрешающий V-вход триггера 1.2 опрокинет данный триггер в “0” состояние, запретит его работу по информационному D-входу (Фиг.2) и через схему “И-НЕ” 2.1 и двухвходовый элемент “И” 2.2 соответствующего блока переключения 2 (Фиг.3) разрешит передачу сигналов на элемент “ИЛИ” 1.3 разряда 1 (Фиг.2) и далее на следующий разряд 1. Таким образом, данный разряд 1 будет исключен из схемы формирования сигнала как при прохождении сигнала в прямом, так и обратном направлении (в режиме реверса).

Работа регистра сдвига при принудительном отключении разрядов происходит при подаче на любой из 1,2,...N отключающие входы регистра “0” (Фиг.1). Сигнал логического “0” поступает через отключающий вход соответствующего блока диагностики 4 (Фиг.5) на первый вход двухвходового элемента “И” 4.1, а с его выхода “0” будет подан на разрешающий вход соответствующего разряда 1. Дальнейшая работа регистра сдвига аналогична описанному выше. Длина регистра сдвига изменяется на количество разрядов, на разрешающие входы которых подан “0”.

Таким образом, по сравнению с известным предлагаемый регистр имеет более широкую областью применения за счет возможности формирования сигнала как в прямом, так и в обратном (реверсивном) направлениях и изменения его длины, а также более высокую надежность работы за счет определения отказа разрядов в регистре, исключая их из схемы формирования сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СИГНАЛИЗАЦИИ | 1989 |

|

RU2024064C1 |

| РЕГИСТР СДВИГА | 2000 |

|

RU2186428C1 |

| ГЕНЕРАТОР СЛУЧАЙНЫХ ЧИСЕЛ | 2001 |

|

RU2211481C2 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1995 |

|

RU2110089C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2014 |

|

RU2553093C1 |

| Биометрическое устройство верификации субъекта доступа | 2016 |

|

RU2637987C1 |

| АССОЦИАТИВНЫЙ ВЫЧИСЛИТЕЛЬ СМЕЩЕНИЯ ЦЕНТРА ТЕКУЩЕГО ИЗОБРАЖЕНИЯ ОТ ЦЕНТРА ЭТАЛОННОГО | 1991 |

|

RU2029358C1 |

| РЕГИСТР СДВИГА | 1998 |

|

RU2143140C1 |

| Генератор псевдослучайных последовательностей | 1981 |

|

SU1023325A1 |

| УСТРОЙСТВО ДЛЯ ПНЕВМОМАССАЖА | 1993 |

|

RU2061456C1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении универсальных и специализированных управляющих устройств, а также в устройствах диагностирования. Техническим результатом является разработка регистра сдвига, формирующего сигнал как в прямом, так и в обратном направлениях с изменяемой длиной, а также с определением состояния разрядов и исключением их при отказе из общей схемы формирования сигнала. Устройство содержит N разрядов, состоящих из DV-триггера, элементов “И” и “ИЛИ”, N блоков переключения, N блоков распределения, N блоков диагностики, блок установки начального состояния, N-1 элементов “И”. 5 з.п. ф-лы, 7 ил.

-входу триггера, прямой выход которого подключен ко второму входу двухвходового элемента ИЛИ, выход которого является информационным выходом разряда, первый вход двухвходового элемента ИЛИ является вторым информационным входом разряда, причем прямой и инверсный выходы триггера являются соответственно вторым и первым проверочными выходами разряда, второй установочный

-входу триггера, прямой выход которого подключен ко второму входу двухвходового элемента ИЛИ, выход которого является информационным выходом разряда, первый вход двухвходового элемента ИЛИ является вторым информационным входом разряда, причем прямой и инверсный выходы триггера являются соответственно вторым и первым проверочными выходами разряда, второй установочный  -вход и тактовый С-вход триггера являются соответственно вторым установочным и тактовым входами разряда, разрешающий V-вход и информационный D-вход триггера являются соответственно разрешающим и первым информационным входами разряда, а первый вход двухвходового элемента И является первым установочным входом разряда.

-вход и тактовый С-вход триггера являются соответственно вторым установочным и тактовым входами разряда, разрешающий V-вход и информационный D-вход триггера являются соответственно разрешающим и первым информационным входами разряда, а первый вход двухвходового элемента И является первым установочным входом разряда.

| РЕГИСТР СДВИГА | 2000 |

|

RU2186428C1 |

| РЕГИСТР СДВИГА | 1998 |

|

RU2143140C1 |

| Регистр сдвига | 1984 |

|

SU1179435A2 |

| Регистр | 1987 |

|

SU1425785A1 |

| Реверсивный регистр сдвига | 1979 |

|

SU830577A1 |

| US 4850000 A, 18.07.1989 | |||

| 0 |

|

SU383490A1 | |

Авторы

Даты

2005-02-27—Публикация

2003-03-12—Подача