Настоящее изобретение относится к схемному устройству для детектирования несанкционированного вмешательства в интегральную схему, содержащему сигнальную шину, нагруженную тактовым сигналом, и, по меньшей мере, одну пару шин, служащую для кодирования одного бита, причем сигнальная шина и, по меньшей мере, одна пара шин включены между первым и вторым блоками интегральной схемы.

Многие схемы, используемые, например, в микропроцессорах, сетях с эстафетным доступом или других блоках обработки данных, требуют защищенной от физических вмешательств и от прослушивания обработки данных с высоким уровнем защиты. Подобное вмешательство возможно за счет анализа интегральной схемы методом "Reverse Engineering". Этим методом можно проанализировать как принцип работы интегральной схемы, так и повлиять на принцип работы с целью манипулирования содержимым данных или процессом функционирования.

На практике уже существуют различные методы, с помощью которых можно, по меньшей мере, затруднить подобный анализ.

Например, известно закрывание интегральной схемы так называемым "экраном". Экран состоит при этом, по меньшей мере, из двух проходящих над интегральной схемой, как правило, меандровых проводящих дорожек. Прерывание или короткое замыкание этих проводящих дорожек детектируют с помощью схемы обработки, которая приводит тогда интегральную схему в защищенное состояние. Это может быть, например, срабатывание сброса или стирание содержимого памяти.

Далее известны методы, с помощью которых можно обнаружить удаление состоящего из пресс-массы пластикового корпуса. При этом обнаруживают изменение емкости между двумя проводящими дорожками при удалении корпуса. Для этой цели в пластиковом корпусе предусмотрены датчики.

Далее существуют методы, позволяющие обнаружить удаление пассивирующего слоя на поверхности чипа.

Для отражения крипто-аналитических вмешательств интегральные схемы в важных для защиты областях применения часто реализуют с помощью технологии, известной как "Dual Rail with Precharge". Бит кодируют при этом посредством комплементарных шин. На первой тактовой фазе, так называемой "Precharge Phase", обе комплементарные шины предварительно заряжают (логическая 1 или High), за счет чего предварительно накопленная информация стирается. На второй тактовой фазе, так называемой "Evaluation Phase", одну из обеих шин разряжают (логический 0 или Low), а на следующем фронте тактового импульса обрабатывают.

Все вышеперечисленные методы детектирования служат для того, чтобы предотвратить доступ к проводящим дорожкам интегральной схемы. После преодоления этих барьеров посылаемые по проводящим дорожкам интегральной схемы данные можно анализировать и манипулировать ими. Последнее может происходить, например, за счет приложения напряжения или разрезания шин.

Задача настоящего изобретения состоит поэтому в том, чтобы разработать схемное устройство и способ детектирования несанционированного вмешательства в интегральную схему, которые обеспечивали бы более надежную защиту.

Эта задача решается посредством признаков п.1 формулы, в котором приведено схемное устройство, а также признаков п.4 формулы, в котором приведен способ. Предпочтительные выполнения приведены в зависимых пунктах.

Интегральная схема использует при этом названную выше технологию "Dual Rail with Precharge", т.е. для кодирования одного бита используют пару шин. Интегральная схема может при этом иметь множество пар шин. Согласно изобретению предусмотрено, что одна сигнальная шина, нагруженная тактовым сигналом, и, по меньшей мере, одна пара шин соединены с детекторной схемой, которая в зависимости от сигналов сигнальной шины и, по меньшей мере, одной пары шин изменяет процесс функционирования интегральной схемы.

В одном варианте каждая шина, по меньшей мере, одной пары шин непосредственно соединена с детекторной схемой. В качестве альтернативы пары шин могут быть соединены у мультиплексора с детекторной схемой. Сигнальная шина, нагруженная тактовым сигналом, в каждом из обоих вариантов соединена с детекторной схемой.

Схемное устройство согласно изобретению использует при этом то обстоятельство, что из действующих состояний в технологии "Dual Rail with Precharge" действующим логическим состояниям противостоят пять запрещенных состояний. Их определяют с помощью детекторной схемы, за счет чего в случае необходимости можно изменить процесс функционирования интегральной схемы.

Помимо детектирования запрещенных состояний при работе защищенной схемы, указывающих на физическое вмешательство (например, посредством игл, методом FIB "Focused Ion Beam", манипулированием светом, температурой, напряжением), схемное устройство согласно изобретению может быть активировано уже при производственном тестировании, т.е. самотестировании схемы. За счет этого можно обнаруживать производственные дефекты, например дефекты "Stuck-At-One" или "Stuck-At-Zero". Поскольку при производстве интегральных схем можно исходить из того, что вмешательства отсутствуют, недействительные значения в парах шин указывают на сбой, например на короткое замыкание.

Схемное устройство согласно изобретению выполнено крайне просто, поскольку оно дополнительно требует только детекторной схемы, которая соединена с парами шин и сигнальной шиной, нагруженной тактовым сигналом.

Принцип работы схемного устройства согласно изобретению становится понятным из описываемого ниже способа.

При первом значении сигнала сигнальной шины две шины одной пары шин детектируют на одинаковый уровень сигнала. При втором значении сигнала сигнальной шины две шины одной пары шин детектируют на разный уровень сигнала, причем при отклонении от ожидаемых результатов изменяют процесс функционирования интегральной схемы.

Другими словами, это означает, что в одном из пяти запрещенных состояний, более подробно поясняемых ниже, вызывается процесс функционирования интегральной схемы. Способ согласно изобретению использует при этом проверку зарядового состояния (уровень сигнала) обеих шин одной пары, причем проверка запрещенных состояний может быть изображена с помощью таблицы состояний или достоверности. Схемная реализация таблицы достоверности представляет собой стандартную задачу и здесь поэтому более подробно не поясняется.

Фазу "Precharge Phase" можно, в принципе, установить при первом значении сигнала логическая 1 или логический 0.

Предпочтительным образом первым значением сигнала сигнальной шины является логический 0. В этом случае таблица состояний соответствует обычным действиям в технологии "Dual Rail with Precharge".

В то время как на сигнальной шине имеется первое значение сигнала, уровень сигнала вторых шин пары в одном выполнении является соответственно логическим 0 или логической 1. За счет одного из этих обоих состояний устанавливают, таким образом, достоверный "Precharge". Соответственно три других оставшихся состояния определяют запрещенные состояния.

Соответственно вторым значением сигнала сигнальной шины является логическая 1 или логический 0. Второе значение сигнала, таким образом, в принципе, комплементарно первому значению сигнала сигнальной шины.

В то время как на сигнальной шине имеется второе значение сигнала, значением сигнала первой шины одной пары является логический 0 или 1, тогда как уровень сигнала второй шины является логической 1 или 0, т.е. комплементарным.

Запрещенное состояние имеет место, следовательно, тогда, когда в течение второго значения сигнала сигнальной шины на обеих шинах одной пары имеет идентичное значение. В целом, возникают, тем самым, пять запрещенных состояний.

Способ согласно изобретению более подробно поясняется ниже с помощью фигур, которые изображают:

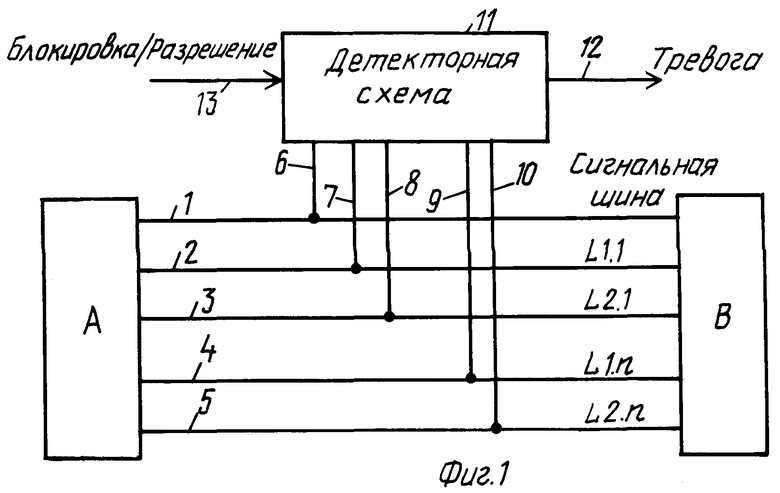

- фиг.1: первый пример выполнения схемного устройства согласно изобретению;

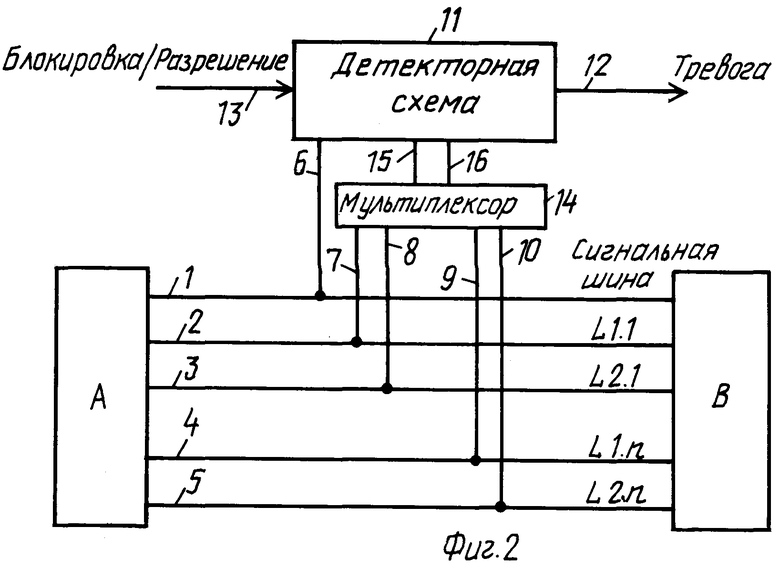

- фиг.2: второй пример выполнения схемного устройства согласно изобретению;

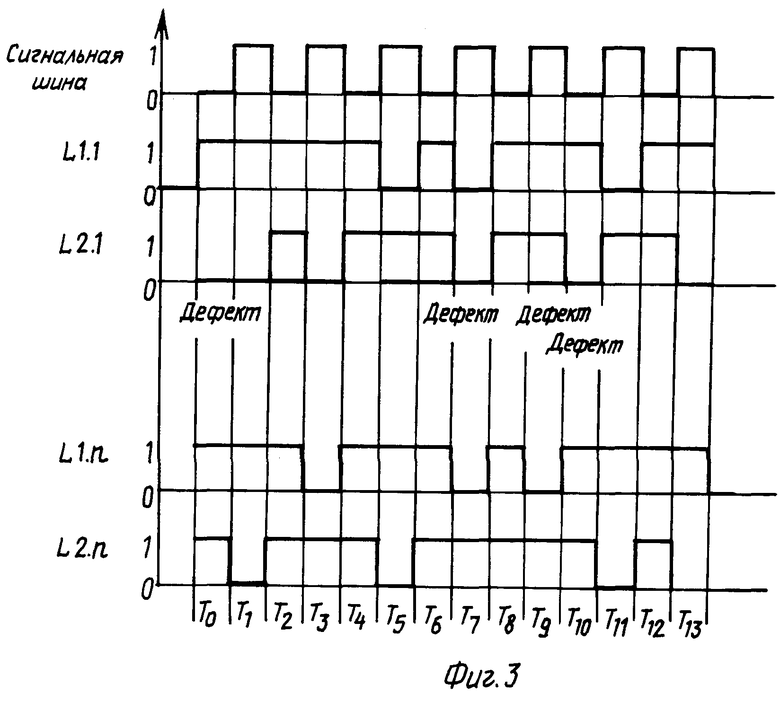

- фиг.3: примерную характеристику сигнала сигнальной шины, а также двух пар шин;

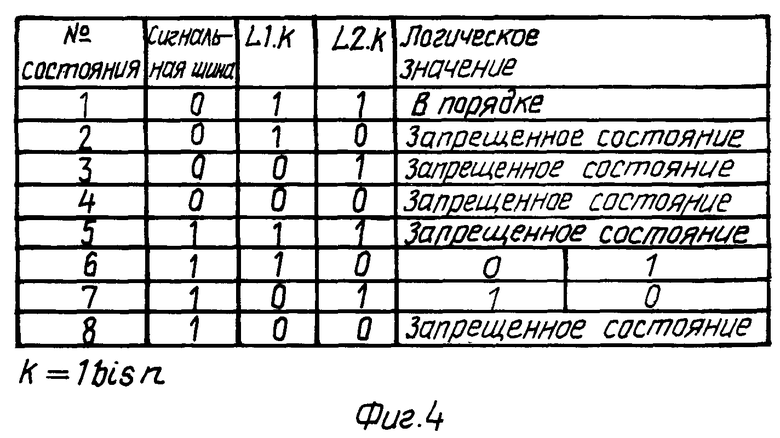

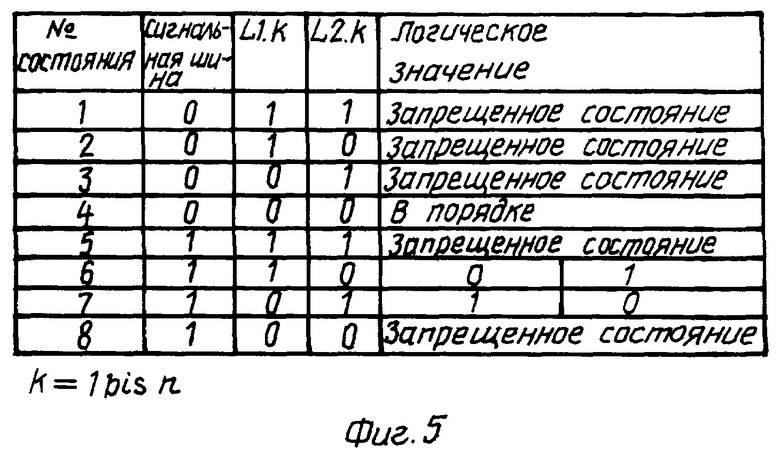

- фиг.4-7: четыре таблицы состояний.

На фиг.1 изображен первый пример выполнения схемного устройства согласно изобретению для детектирования несанкционированного вмешательства в интегральную схему. Интегральная схема изображена на фиг.1 в качестве примера блоками А, В, между которыми находятся проводящие дорожки 1-5. Дорожка 1 представляет собой при этом сигнальную шину "Clock", нагруженную тактовым сигналом. Далее в качестве примера изображены две пары шин L1.1, L2.1 и L1.n, L2.n. Между блоками А, В могут, таким образом, передаваться в данном примере два бита. В принципе, между блоками А, В может быть включено, конечно, произвольное число пар шин.

Согласно изобретению для проверки проводящих дорожек предусмотрена детекторная схема 11. Каждая из сигнальных шин 1-5, включенная между блоками А, В, соединена с детекторной схемой 11. Это изображено проводящими дорожками 6-10. В случае запрещенного состояния детекторная схема 11 может через шину 12 вызвать тревогу, в результате чего интегральная схема может быть запущена заново или могут быть стерты важные для защиты данные.

Далее можно активировать или дезактивировать детекторную схему 11 выборочно посредством сигнальной шины 13.

В первом примере выполнения на фиг.1 каждая из сигнальных шин 1-5 соединена непосредственно с детекторной схемой 11. В примере выполнения на фиг.2 только сигнальная шина 1, на которой имеется тактовый сигнал, соединена непосредственно с детекторной схемой 11 через сигнальную шину 6. Пары шин L1.1, L2.1 и L1.n, L2.n, напротив, соединены с детекторной схемой 11 через мультиплексор 14.

В то время как на фиг.1 может происходить проверка всех пар шин одновременно, пары шин на фиг.2 проверяют на запрещенное состояние последовательно. Поскольку принцип работы мультиплексора достаточно известен из уровня техники, здесь подробное описание принципа работы опущено.

С помощью таблиц состояний на фиг.4-7 можно понять принцип работы схемного устройства согласно изобретению. В первой колонке проставлен номер возможного состояния. Колонки 2-4 обозначают возможные состояния сигнальной шины "Clock", а также двух шин одной пары, обозначенных в данном случае L1.k, L2.k. Индекс k обозначает при этом пары шин 1-n. В последней колонке указано логическое значение, контролируемое детекторной схемой 11.

В течение первого из четырех состояний (номера состояний 1-4) сигнальная шина "Clock" находится на так называемой фазе "Precharge Phase". На этой фазе зарядовые состояния двух шин L1.k, L2.k одной пары должны иметь одинаковые значения. На фиг.4 и 6 это тот случай, когда L1.k и L2.k имеют значение логическая 1, тогда как на фиг.5 и 7 этот случай при значении логический 0.

На так называемой фазе "Evaluation Phase" (номера состояний 5-8) шины L1.k, L2.k не должны иметь одинаковое зарядовое состояние. В этом случае имеет место дефект или вмешательство. Выборочно можно присвоить номеру 6 состояния логическое значение 0 или 1. В соответствии с этим логическим значением при номере 7 состояния является 1 или 0, т.е. оно комплементарно логическому значению номера 6 состояния.

Использование изображенных на фиг.4 и 5 таблиц состояний в способе детектирования согласно изобретению предпочтительно, поскольку фазу "Precharge Phase" осуществляют при логическом значении 0 сигнальной шины "Clock". В качестве альтернативы можно также осуществлять фазу "Precharge Phase" при значении логическая 1, а фазу "Evaluation Phase" - при значении логический 0. Это изображено в таблицах состояний 6 и 7.

На фиг.3 в качестве примера изображена характеристика сигнала сигнальной шины "Clock", а также двух пар шин L1.1, L2.1 и L1.n, L2.n. Для проверки наличия запрещенного состояния, например дефекта или вмешательства, необходимо, в принципе, сравнить между собой сигналы шин одной пары. Изображенную на фиг.3 характеристику сигнала оценивают по таблице состояний на фиг.4. Таким образом, в первой паре шин уже при первом значении сигнала сигнальной шины "Clock" (тактовая фаза То) уже имеется дефект, поскольку вторая шина L2.1 на фазе "Precharge Phase" не принимает идентичного значения сигнала. В течение тактовых фаз Т7 и Т9 на фазе "Evaluation Phase" имеет место дефект, поскольку там состояния сигналов обеих шин пары 1 имеют одинаковое зарядовое состояние, что согласно таблице состояний на фиг.4 запрещено. Другой дефект возникает на тактовой фазе Т10.

Характеристика сигнала n-й пары шин, напротив, в порядке, как показывает сравнение с таблицей состояний на фиг.4.

Перечень ссылочных позиций

1-5 - проводящая дорожка

6-10 - проводящая дорожка

11 - детекторная схема

12 - сигнальная шина

13 - сигнальная шина

14 - мультиплексор

15 - проводящая дорожка

16 - проводящая дорожка

А, В - схемный блок

Изобретение относится к схемному устройству для детектирования несанкционированного вмешательства в интегральную схему. Техническим результатом является повышение надежности защиты. Устройство содержит сигнальную шину, нагруженную тактовым сигналом, по меньшей мере одну пару шин, служащую для кодирования одного бита, детекторную схему, мультиплексор. Согласно способу при первом значении сигнала сигнальной шины две шины одной пары детектируют на одинаковый уровень сигнала, при втором значении сигнала сигнальной шины две шины одной пары детектируют на разный уровень сигнала, обнаруживают запрещенные состояния при работе схемы, изменяют процесс функционирования схемы, тем самым вызывая тревогу. 2 н. и 6 з.п. ф-лы, 7 ил.

а) при первом значении сигнала сигнальной шины (1) две шины одной пары шин (2, 3; 4, 5) детектируют на одинаковый уровень сигнала;

б) при втором значении сигнала сигнальной шины (1) две шины одной пары шин (2, 3; 4, 5) детектируют на разный уровень сигнала, причем процесс функционирования интегральной схемы изменяют таким образом, что вызывается тревога, если две шины одной пары шин (2, 3; 4, 5) при первом значении сигнала сигнальной шины (1) имеют разный уровень сигнала или при втором значении сигнала сигнальной шины (1) имеют одинаковый уровень сигнала.

| СПОСОБ ЗАЩИТЫ ОТ ОБРАЩЕНИЙ К ПАМЯТИ ЭВМ ПОСТОРОННИХ ПОЛЬЗОВАТЕЛЕЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1993 |

|

RU2106686C1 |

| СПОСОБ ПОЛУЧЕНИЯ АНИОПИТА | 1972 |

|

SU417447A1 |

| Способ разделения дробленого материала | 1978 |

|

SU860882A1 |

| US 4933898 А, 12.06.1990. | |||

Авторы

Даты

2005-05-10—Публикация

2001-08-30—Подача