Изобретение относится к области вычислительной техники и может быть использовано в сверхбольших интегральных схемах (СБИС) при реализации арифметических устройств.

Известна реализация многоразрядного сумматора на основе парафазных динамических КМДП схем с предзарядом (Патент США №5491653, G 06 F 7/50, НКИ 364-784 от 13.02.1996). Особенностью данного технического решения является реализация функций сложения в каждом разряде в виде схемных КМДП макроэлементов, логическая часть которых выполняется только на транзисторах n-типа. Это сокращает число простейших последовательно включенных логических элементов, необходимых для выполнения функций суммирования. Недостатком данного устройства является невысокое быстродействие, что обусловлено необходимостью противофазного трехтактного тактирования соседних разрядов. Поэтому каждый последующий разряд функционирует только после полного срабатывания предыдущего, что увеличивает длительность тактов и снижает быстродействие.

Наиболее близким техническим решением к предлагаемому является многоразрядный сумматор на КМДП транзисторах (Патент РФ №2185655, G 06 F 7/50 от 19.02.2001). Это устройство, принятое за прототип, содержит разряды сумматора, работающие под общим однофазным тактированием с асинхронной последовательной передачей сигнала переноса и поразрядным суммированием при наличии парафазных входных и выходных сигналов. Логическая часть реализована на транзисторах только n-типа. Недостаток этого устройства - относительная сложность и ограниченное быстродействие, что обусловлено наличием двух инвертирующих элементов в каждом из разрядов в цепях последовательного распространения переноса. В результате функция переноса реализуется через два логических перехода с соответствующими временными задержками в логической части и в инвертирующем элементе, что увеличивает время распространения сигнала переноса в каждом из разрядов и снижет быстродействие устройства.

Технической задачей, решаемой в изобретении, является упрощение устройства при повышении его быстродействия.

Поставленная цель достигается тем, что многоразрядный сумматор на КМДП транзисторах, содержащий инвертор, тактовый транзистор p-типа и в каждом разряде - триггер-фиксатор, четыре предзарядовых транзистора и двадцать логических транзисторов, из которых соединены последовательно парами первый и второй, третий и четвертый, пятый и шестой, седьмой и восьмой, девятый и десятый, одиннадцатый и двенадцатый, тринадцатый и четырнадцатый, пятнадцатый и шестнадцатый, образуя соответствующие восемь ключевых цепей, средние точки первой и четвертой, второй и третьей ключевых цепей попарно объединены, средние точки шестой и восьмой ключевых цепей соответственно через семнадцатый и восемнадцатый транзисторы соединены с общим выводом разряда, первые выводы первой и второй ключевых цепей стоками соответственно первого и третьего логических транзисторов подключены к первому выходу разряда, первые выводы третьей и четвертой ключевых цепей стоками соответственно пятого и седьмого транзисторов подключены к второму выходу разряда, первые выводы пятой и шестой ключевых цепей стоками соответственно девятого и одиннадцатого транзисторов подключены к третьему выходу разряда, первые выводы седьмой и восьмой ключевых цепей стоками соответственно тринадцатого и пятнадцатого транзисторов подключены к четвертому выходу разряда, первая, вторая, пятая и шестая ключевые цепи вторыми выводами соединены через девятнадцатый транзистор с общим выводом разряда, третья, четвертая, седьмая и восьмая ключевые цепи вторыми выводами соединены через двадцатый транзистор с общим выводом разряда, первый, второй, третий и четвертый предзарядовые транзисторы, затворы которых объединены, включены между шиной питания разряда и одноименным выходом разряда, в каждом разряде первый и второй выходы разряда подключены к соответствующему входу триггера-фиксатора, выходы которого являются выводами результата суммирования в данном разряде, а третий и четвертый выходы разряда являются выходами результата переноса в разряде, затворы первого, пятого, одиннадцатого и тринадцатого логических транзисторов подключены к прямому входу, а затворы третьего, седьмого, девятого и пятнадцатого логических транзисторов - к дополняющему входу, на которые подаются парафазные сигналы первой переменной разряда, затворы второго, шестого, десятого, шестнадцатого и семнадцатого логических транзисторов подключены к прямому входу, а затворы четвертого, восьмого, двенадцатого и четырнадцатого логических транзисторов - к дополняющему входу, на которые подаются парафазные сигналы второй переменной разряда, затворы девятнадцатого и двадцатого транзисторов являются прямым и дополняющим входами переноса, вход инвертора, который включен между клеммой питания устройства и шиной земли, соединен с тактовой клеммой устройства, а выход - с затвором тактового транзистора p-типа, исток которого подключен к клемме питания устройства, в нечетных разрядах логические транзисторы являются транзисторами n-типа, а предзарядовые транзисторы, затворы которых соединены с тактовой клеммой устройства, являются транзисторами p-типа, шина питания разряда соединена с клеммой питания устройства, а триггер-фиксатор выполнен на элементах 2И-НЕ, третий и четвертый выходы каждого разряда подключены соответственно к дополняющему и прямому входам переноса последующего разряда, в нечетных разрядах общий вывод разряда соединен с выходом инвертора, в четных разрядах логические транзисторы выполнены как транзисторы p-типа, а предзарядовые транзисторы, затворы которых подключены к выходу инвертора, выполнены как транзисторы n-типа, причем в четных разрядах шина питания разряда соединена с шиной земли, общий вывод разряда соединен со стоком тактового транзистора p-типа, а триггер-фиксатор выполнен на элементах 2ИЛИ-НЕ.

Наличие в предлагаемом устройстве перечисленных выше существенных признаков обеспечивает решение поставленной технической задачи - упрощение устройства при повышении его быстродействия.

Действительно, благодаря выполнению соседних разрядов сумматора на соответствующих транзисторах взаимодополняющего типа отпадает необходимость в инвертирующих элементах на выходах логической части переноса, что ведет к уменьшению числа транзисторов в каждом из разрядов (на 4) и упрощению связей между разрядами. Тактирование устройства осуществляется посредством всего 3 общих для всех разрядов сумматора транзисторов - одного тактового и двух в инверторе (вместо 4 с теми же функциями тактирования). Одновременно в каждом разряде с двух до одного сокращается число логических переходов в цепи распространения переноса, что ведет к уменьшению числа переключаемых нагрузок и снижению средней задержки на один разряд в 1,4-1,5 раза, что обуславливает повышение быстродействия устройства.

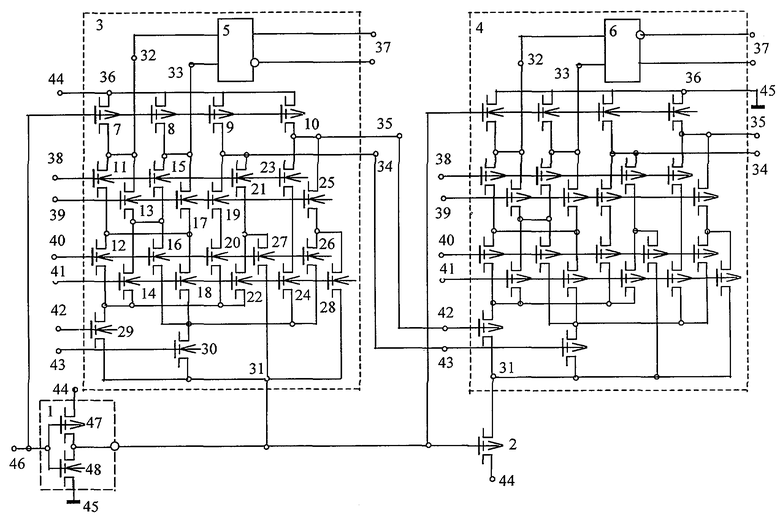

На чертеже приведена принципиальная схема заявляемого многоразрядного сумматора на КМДП транзисторах на примере двух разрядов.

Устройство содержит инвертор 1, тактовый транзистор 2 p-типа, нечетные 3 и четные 4 разряды. В нечетных разрядах триггер-фиксатор 5 выполнен на элементах 2И-НЕ, в четных разрядах триггер-фиксатор 6 выполнен на элементах 2ИЛИ-НЕ.

Каждый разряд 3 и 4 сумматора содержит четыре предзарядовых транзистора 7-10 и двадцать логических транзисторов 11-30. В нечетных разрядах 3 предзарядовые транзисторы 7-10 являются транзисторами p-типа, а логические 11-30 - транзисторами n-типа, в четных разрядах 4 - предзарядовые транзисторы n-типа, а логические - p-типа.

С первого 11 по шестнадцатый 26 логические транзисторы соединены последовательно парами - первый и второй, третий и четвертый, пятый и шестой, седьмой и восьмой, девятый и десятый, одиннадцатый и двенадцатый, тринадцатый и четырнадцатый и пятнадцатый и шестнадцатый, образуя соответствующие восемь ключевых цепей. Средние точки первой и четвертой, второй и третьей ключевых цепей попарно объединены.

Средние точки шестой и восьмой ключевых цепей подсоединены соответственно через семнадцатый 27 и восемнадцатый 28 транзисторы к общему выводу 31 разряда.

Первые выводы первой и второй ключевых цепей стоками соответственно первого 11 и третьего 13 логических транзисторов подключены к первому выходу 32 разряда, первые выводы третьей и четвертой ключевых цепей стоками соответственно пятого 15 и седьмого 17 транзисторов подключены к второму выходу 33 разряда, первые выводы пятой и шестой ключевых цепей стоками соответственно девятого 19 и одиннадцатого 21 транзисторов подключены к третьему выходу 34 разряда, первые выводы седьмой и восьмой ключевых цепей стоками соответственно тринадцатого 23 и пятнадцатого 25 транзисторов подключены к четвертому выходу 35 разряда.

Первая, вторая, пятая и шестая ключевые цепи вторыми выводами соединены через девятнадцатый транзистор 29 с общим выводом 31 разряда, а третья, четвертая, седьмая и восьмая ключевые цепи вторыми выводами соединены через двадцатый 30 транзистор также с общим выводом 31 разряда. Первый 7, второй 8, третий 9 и четвертый 10 предзарядовые транзисторы, затворы которых объединены, включены между шиной питания 36 разряда и одноименным выходом разряда.

В каждом разряде первый 32 и второй 33 выходы разряда подключены к входам соответствующего триггера-фиксатора 5 или 6. Выходы триггеров-фиксаторов 5 и 6 являются выходами 37 результата суммирования в соответствующем разряде. Третий 34 и четвертый 35 выходы разряда являются выходами результата переноса в последующий разряд устройства.

Затворы первого 11, пятого 15, одиннадцатого 21 и тринадцатого 23 логических транзисторов подключены к прямому входу 38, а затворы третьего 13, седьмого 17, девятого 19 и пятнадцатого 25 логических транзисторов - к дополняющему входу 39, на которые подаются парафазные сигналы первой переменной разряда. Затворы второго 12, шестого 16, десятого 20, шестнадцатого 26 и семнадцатого 27 логических транзисторов подключены к прямому входу 40, а затворы четвертого 14, восьмого 18, двенадцатого 22 и четырнадцатого 24 логических транзисторов - к дополняющему входу 41, на которые подаются парафазные сигналы второй переменной разряда. Затворы девятнадцатого 29 и двадцатого 30 транзисторов являются прямым 42 и дополняющим 43 входами переноса.

Вход инвертора 1, который включен между клеммой 44 питания устройства и шиной земли 45, соединен с тактовой клеммой 46 устройства, а выход - с затвором тактового транзистора 2 p-типа, исток которого подключен к клемме 44 питания устройства. Инвертор содержит последовательно включенные транзистор 47 p-типа и транзистор 48 n-типа.

В нечетных разрядах 3 затворы предзарядовых транзисторов 7-10 соединены с тактовой клеммой 46 устройства, а шина питания 36 разряда соединена с клеммой 44 питания устройства и общий вывод 31 разряда соединен с выходом инвертора 1.

В четных разрядах 4 затворы предзарядовых транзисторов 7-10 подключены к выходу инвертора 1, причем шина питания 36 разряда соединена с шиной земли 45, а общий вывод 31 разряда соединен со стоком тактового транзистора 2 p-типа.

Третий 34 и четвертый 35 выходы каждого разряда подключены соответственно к дополняющему 43 и прямому 42 входам переноса последующего разряда.

Триггеры-фиксаторы 5 и 6 включены также между клеммой питания устройства и шиной земли и выполнены на двух двухвходовых элементах с инверсией, первые входы которых являются симметричными входами триггера-фиксатора, а вторые - входами обратной связи с выхода парного элемента.

Устройство работает следующим образом. В исходном состоянии - на первом полутакте предзарядовые транзисторы 7-10 p-типа в нечетных разрядах 3 открыты нулевым сигналом на тактовой клемме 46, а предзарядовые транзисторы 7-10 n-типа в четных разрядах 4 открыты положительным сигналом на выходе инвертора 1. Клеммы 44 питания устройства (положительной полярности) изолированы от шины земли 45 и токи через логические транзисторы не протекают, т.к. тактовый транзистор 2 p-типа и транзистор 47 n-типа инвертора 1 закрыты. Узловые емкости, связанные с выходами 32-35 нечетных разрядов 3 от клеммы 44 через предзарядовые транзисторы 7-10, заряжаются до уровня "логической 1", а те же выходы в четных разрядах 4 через предзарядовые транзисторы 7-10 разряжены на шину земли 45 до уровня "логического 0".

Триггеры-фиксаторы 5 и 6 находятся при этом в режиме хранения результата предыдущего такта суммирования, поскольку на их входах 32-33 в нечетных разрядах присутствуют сигналы "логической 1", а на тех же входах в четных разрядах присутствуют сигналы "логического 0".

На первом полутакте на прямые 38, 40 и дополняющие 39, 41 входы первой и второй переменных всех разрядов от внешнего устройства подаются соответствующие сигналы в прямом и логически дополняющем виде (парафазные сигналы). Двоичному значению "логической 1" соответствует высокий уровень напряжения клеммы питания устройства, а значению "логического 0" - низкий уровень напряжения шины земли. Открытому или замкнутому состоянию транзистора n-типа соответствует сигнал "логической 1", поданный на затвор транзистора, а транзистора p-типа - сигнал "логического 0".

Например, когда суммируются числа А=1 и В=0, на входы 38 и 41 подаются сигналы "логической 1", а на входы 39 и 40 - сигналы "логического 0". На входы 42 и 43 переноса первого разряда от того же внешнего устройства одновременно поданы сигналы отложенного переноса С, например, при С=1 - соответственно "логической 1" и "логического 0". На выходах переноса 34 и 35 нечетных разрядов присутствуют сигналы "логической 1", а на выходах переноса 34 и 35 четных разрядов присутствуют сигналы "логического 0". Входные сигналы, соответствующие суммируемым переменным по входам А и В в каждом разряде удерживаются в течение всего второго рабочего полутакта.

После подачи положительного сигнала на тактовую клемму 46 сумматора в нечетных разрядах 3 предзарядовые транзисторы 7-10 закрываются, на выходе инвертора 1 формируется сигнал "логического 0" и тактовый транзистор 2 p-типа открывается, а в четных разрядах 4 предзарядовые транзисторы 7-10 также закрываются. Открытые транзистор 48 n-типа инвертора 1 и тактовый транзистор 2 обеспечивают протекание токов в соответствующих ключевых цепях разрядов для формирование парафазных сигналов на выходах 32-35 каждого из разрядов. При любом наборе взаимно дополняющих сигналов на входах 38-43 в каждом из разрядов проводящими могут быть только одна ключевая цепь логических транзисторов, связанная с первым 32 или вторым 33 выходами разряда (сумма) и одна ключевая цепь логических транзисторов, связанная с третьим 34 или четвертым 35 выходами разряда (перенос).

Например, пусть в первом разряде суммируются переменные А=1 и В=1 при С=0, а во втором А=1, В=0. Наличие проводящей ключевой цепи, состоящей из транзисторов 11, 16 и 30, ведет в первом разряде к разряду узловой емкости, связанной с первым выходом 32 до уровня "логического 0". Появление нулевого сигнала на одном из входов триггера-фиксатора 7 ведет к его переключению либо подтверждению предыдущего состояния, соответствующего сумме, равной 0. Одновременно в первом разряде благодаря проводящей ключевой цепи, состоящей из транзисторов 21 и 27 до уровня "логического 0" разряжается узловая емкость, связанная с третьим выходом 34 разряда, что соответствует логическому значению переноса, равному 1. С учетом того, что в случае равенства переменных 1 входам 38, 40, 42 соответствуют положительные значения сигналов, третий выход 34 разряда соединен с дополняющим входом 43 переноса последующего разряда.

Во втором (четном) разряде проводящей оказывается ключевая цепь, состоящая из пятнадцатого 25, шестнадцатого 26 и двадцатого 30 логических транзисторов, т.к. на 39, 40 и 43 входы данного разряда поданы нулевые сигналы, которые являются открывающими для транзисторов p-типа. От клеммы 44 питания через тактовый транзистор 2 p-типа и указанную цепь логических транзисторов узловая емкость, связанная с четвертым 35 выходом второго разряда, заряжается до уровня "логической 1" и в таком виде (значение переноса соответствует 1) подается на прямой 42 вход переноса последующего нечетного разряда. Одновременно благодаря проводящей ключевой цепи, состоящей из третьего 13, шестого 16 и двадцатого 30 логических транзисторов p-типа, на первом 32 выходе второго разряда формируется сигнал "логической 1", в результате чего триггер-фиксатор, выполненный на элементах 2ИЛИ-НЕ, устанавливается в состояние, соответствующее сумме, равной значению "логического 0".

По окончании действия тактового сигнала на клемме 46 предзарядовые транзисторы 7-10 p-типа нечетных разрядов открываются, на выходе инвертора 1 через транзистор 47 p-типа формируется положительный сигнал, который закрывает тактовый транзистор 2 p-типа, открывает предзарядовые транзисторы 7-10 четных разрядов 4 и ускоряет процесс перезаряда узловых емкостей, связанных с логическими транзисторами n-типа, в том числе процесс перехода выходов 32-35 в исходное состояние.

Данное устройство является более простым и содержит в каждом из разрядов на два инвертора или на 4 транзистора меньше, чем известное, и обладает более простой организацией тактирования (3 транзистора вместо 4). Повышенное быстродействие сумматора обусловлено минимальным числом логических переходов и величины нагрузок в цепях распространения сигнала переноса. Это позволяет реализовать разряд сумматора на транзисторах минимальных технологических размеров с быстродействием 1,4-1,5 раз выше, чем в известном устройстве.

| название | год | авторы | номер документа |

|---|---|---|---|

| СУММАТОР НА КМДП ТРАНЗИСТОРАХ | 2001 |

|

RU2185655C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ | 1995 |

|

RU2107387C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КМДП ТРАНЗИСТОРАХ | 2007 |

|

RU2355104C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2009 |

|

RU2393631C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КМДП ТРАНЗИСТОРАХ | 2003 |

|

RU2258303C1 |

| ТАКТИРУЕМЫЙ ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2009 |

|

RU2382490C1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КМДП ТРАНЗИСТОРАХ | 2004 |

|

RU2275737C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ПЕРЕНОСА В СУММАТОРЕ | 2013 |

|

RU2525111C1 |

| ТАКТИРУЕМЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2010 |

|

RU2427073C1 |

| МНОГОРАЗРЯДНОЕ УСТРОЙСТВО ЛОГИЧЕСКОГО СРАВНЕНИЯ | 2007 |

|

RU2328026C1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в КМДП интегральных схемах при реализации арифметических устройств. Техническим результатом является упрощение устройства и повышение его быстродействия. Устройство содержит инвертор, тактовый транзистор p-типа, нечетные и четные разряды, при этом нечетные разряды состоят из триггера-фиксатора, выполненного на элементах 2И-НЕ, четырех предзарядовых транзисторах p-типа и двадцати логических транзисторов n-типа, четные разряды состоят из триггера-фиксатора, выполненного на элементах 2ИЛИ-НЕ, четырех предзарядовых транзисторов n-типа и двадцати логических транзисторов p-типа. 1 ил.

Многоразрядный сумматор на КМДП-транзисторах, содержащий инвертор, тактовый транзистор p-типа и в каждом разряде триггер-фиксатор, четыре предзарядовых транзистора и двадцать логических транзисторов, из которых соединены последовательно парами первый и второй, третий и четвертый, пятый и шестой, седьмой и восьмой, девятый и десятый, одиннадцатый и двенадцатый, тринадцатый и четырнадцатый, пятнадцатый и шестнадцатый, образуя соответствующие восемь ключевых цепей, средние точки первой и четвертой, второй и третьей ключевых цепей попарно объединены, средние точки шестой и восьмой ключевых цепей соответственно через семнадцатый и восемнадцатый транзисторы соединены с общим выводом разряда, первые выводы первой и второй ключевых цепей стоками соответственно первого и третьего логических транзисторов подключены к первому выходу разряда, первые выводы третьей и четвертой ключевых цепей стоками соответственно пятого и седьмого транзисторов подключены к второму выходу разряда, первые выводы пятой и шестой ключевых цепей стоками соответственно девятого и одиннадцатого транзисторов подключены к третьему выходу разряда, первые выводы седьмой и восьмой ключевых цепей стоками соответственно тринадцатого и пятнадцатого транзисторов подключены к четвертому выходу разряда, первая, вторая, пятая и шестая ключевые цепи вторыми выводами соединены через девятнадцатый транзистор с общим выводом разряда, третья, четвертая, седьмая и восьмая ключевые цепи вторыми выводами соединены через двадцатый транзистор с общим выводом разряда, первый, второй, третий и четвертый предзарядовые транзисторы, затворы которых объединены, включены между шиной питания разряда и одноименным выходом разряда, в каждом разряде первый и второй выходы разряда подключены к соответствующему входу триггера-фиксатора, выходы которого являются выводами результата суммирования в данном разряде, а третий и четвертый выходы разряда являются выходами результата переноса в разряде, затворы первого, пятого, одиннадцатого и тринадцатого логических транзисторов подключены к прямому входу, а затворы третьего, седьмого, девятого и пятнадцатого логических транзисторов - к дополняющему входу, на которые подаются парафазные сигналы первой переменной разряда, затворы второго, шестого, десятого, шестнадцатого и семнадцатого логических транзисторов подключены к прямому входу, а затворы четвертого, восьмого, двенадцатого и четырнадцатого логических транзисторов - к дополняющему входу, на которые подаются парафазные сигналы второй переменной разряда, затворы девятнадцатого и двадцатого транзисторов являются прямым и дополняющим входами переноса, вход инвертора, который включен между клеммой питания устройства и шиной земли, соединен с тактовой клеммой устройства, а выход - с затвором тактового транзистора p-типа, исток которого подключен к клемме питания устройства, в нечетных разрядах логические транзисторы являются транзисторами n-типа, а предзарядовые транзисторы, затворы которых соединены с тактовой клеммой устройства, являются транзисторами p-типа, шина питания разряда соединена с клеммой питания устройства, а триггер-фиксатор выполнен на элементах 2И-НЕ, отличающийся тем, что третий и четвертый выходы каждого разряда подключены соответственно к дополняющему и прямому входам переноса последующего разряда, в нечетных разрядах общий вывод разряда соединен с выходом инвертора, в четных разрядах логические транзисторы выполнены как транзисторы p-типа, а предзарядовые транзисторы, затворы которых подключены к выходу инвертора, выполнены как транзисторы n-типа, причем в четных разрядах шина питания разряда соединена с шиной земли, общий вывод разряда соединен со стоком тактового транзистора p-типа, а триггер-фиксатор выполнен на элементах 2ИЛИ-НЕ.

| СУММАТОР НА КМДП ТРАНЗИСТОРАХ | 2001 |

|

RU2185655C1 |

| СУММАТОР | 1994 |

|

RU2049346C1 |

| ОДНОРАЗРЯДНЫЙ СУММАТОР | 1996 |

|

RU2164036C2 |

| Сумматор | 1986 |

|

SU1406591A1 |

| US 5491653 А1, 13.02.1996 | |||

| МЕХАНИЗМ КАЛЕНДАРЯ К НАСТОЛЬНЫМ И НАСТЕННЫМ ЧАСАМ | 0 |

|

SU332415A1 |

Авторы

Даты

2004-10-27—Публикация

2003-04-11—Подача