Изобретение относится к технике связи, например технологии и практике измерений в коммутируемых каналах сетей передачи информации.

Многочастотный широкополосный сигнал, проходя по коммутируемым каналам связи, искажается, так как различные частотные составляющие запаздывают на разное время. Существенным недостатком известных схем цифровых фазометров [1. Метрология, стандартизация и измерения в технике связи. Под редакцией Б.П. Хромого. Москва, Радио и связь, 1986 г.] является большое время измерения, зависящее от частоты исследуемого сигнала, переходного процесса тестируемого канала связи и ограниченная точность при наличии индустриальных помех.

Известно устройство [2. Авт. свид-во СССР №1609328 (НП), G 06 G 7/19, G 01 R 25/00, опубл. 23.12.1988 г.], которое определяет сдвиг по фазе двух гармонических сигналов, например сигналов тональной частоты в телефонии с произвольным шагом дискретизации и частотой. Повышение точности измерения фазовых характеристик сложных, в общем случае нелинейных компонентов техники связи достигается тем, что нет необходимости масштабировать шаг дискретизации сигналов на выходе двух аналого-цифровых преобразователей (АЦП), определять угловую частоту ω исследуемых гармонических сигналов. Точность измерения сдвига фаз повышается за счет исключения арифметических блоков вычисления и запоминания синусов, косинусов и масштабирования, а также соответствующим выбором интервала измерения, который может быть адаптивным, что повышает помехоустойчивость. К недостаткам подобного устройства можно отнести ограничения на форму тест-сигнала. Кроме того, его нельзя применить при других видах модуляции.

Наиболее близко к предлагаемому устройство для адаптивной коррекции параметров динамических характеристик сложных нелинейных и нестационарных радиотехнических систем, содержащих радиокомпоненты как с аналоговыми, так и с цифровыми сигналами [3. Пат. России №2187140, G 05 B 13/00, H 03 D 3/02, опубл. 10.08.2002 г.], содержащее генератор гармонических сигналов эталонной опорной частоты, формирователь импульсов синхронизации, счетчик, генератор прямоугольных импульсов, цифровой блок регулирования фазы синхронизации, выход которого соединен с входом задания фазы генератора прямоугольных импульсов, выход которого через ключ подключен к сигнальному информационному входу квадратурного демодулятора, первый выход генератора гармонических сигналов опорной частоты соединен с первым синфазным входом квадратурного демодулятора и формирователем импульсов, соединенным с входом счетчика, при этом второй выход генератора гармонических сигналов опорной частоты соединен со вторым входом квадратурного демодулятора, информационные входы первого и второго буферных регистров являются измерительными входами для подключения к выходам соответственно первого и второго АЦП, первый и второй цифровые БИХ-фильтры подключены к выходам первого и второго буферных регистров соответственно, входы первого и второго мультиплексора подключены к первому, второму и третьему выходам соответствующих цифровых БИХ-фильтров, а выходы первого и второго мультиплексора - к входам арифметических сумматоров-вычитателей, первый управляющий выход микропроцессорного комплекта соединен с входом сброса в начальное состояние цифрового блока регулирования фазы синхронизации, второй вход которого подключен к второму управляющему выходу микропроцессорного комплекта, выход формирователя импульсов соединен с входом синхронизации микропроцессорного комплекта, выход общей синхронизации которого соединен с соответствующими входами синхронизации буферных регистров, БИХ-фильтров, мультиплексоров и арифметических сумматоров-вычитателей, третий, четвертый и пятый управляющие выходы микропроцессорного комплекта соединены с корректирующими входами первого цифрового БИХ-фильтра, шестой, седьмой и восьмой управляющие выходы микропроцессорного комплекта соединены с соответствующими корректирующими входами второго цифрового БИХ-фильтра, девятый управляющий выход микропроцессорного комплекта подключен к управляющему входу блока индикации.

К недостаткам этого устройства можно отнести случайную погрешность измерения транспортного запаздывания e-τTS сигналов на ограниченном интервале наблюдения, например, в оперативном режиме диагностики и наладки сложных радиотехнических комплексов, в режиме нормальной эксплуатации при воздействии индустриальных помех общего вида, в том числе импульсных; нестационарных на интервале наблюдения и т.д. Эта погрешность в известном устройстве, выбранном в качестве прототипа, уменьшается оптимальным выбором и коррекцией цифровых БИХ-фильтров, однако при уменьшении отношения полезный сигнал / шум становится заметной для инженерной практики.

Настоящее изобретение направлено на повышение точности измерения транспортного запаздывания сигналов в технологии и технике связи. Технический результат, достигаемый при решении этой задачи, состоит в полной компенсации случайной погрешности измерения знака и величины ±τT *, например, для сигналов тональных частот, а также сигналов с другими видами модуляции, например ИКМ.

Это достигается тем, что в известное устройство, содержащее генератор гармонических сигналов эталонной опорной частоты, формирователь импульсов синхронизации, счетчик, генератор прямоугольных импульсов, цифровой блок регулирования фазы синхронизации, выход которого соединен с входом задания фазы генератора прямоугольных импульсов, выход которого через ключ подключен к сигнальному информационному входу квадратурного демодулятора, первый выход генератора гармонических сигналов опорной частоты соединен с первым синфазным входом квадратурного демодулятора и формирователем импульсов, соединенным с входом счетчика, при этом второй выход генератора гармонических сигналов опорной частоты соединен со вторым входом квадратурного демодулятора, информационные входы первого и второго буферных регистров являются измерительными входами для подключения к выходам соответственно первого и второго АЦП, первый и второй цифровые БИХ-фильтры подключены к выходам первого и второго буферных регистров соответственно, входы первого и второго мультиплексора подключены к первому, второму и третьему выходам соответствующих цифровых БИХ-фильтров, а выходы первого и второго мультиплексора - к входам арифметических сумматоров-вычитателей, первый управляющий выход микропроцессорного комплекта соединен с входом сброса в начальное состояние цифрового блока регулирования фазы синхронизации, второй вход которого подключен к второму управляющему выходу микропроцессорного комплекта, выход формирователя импульсов соединен с входом синхронизации микропроцессорного комплекта, выход общей синхронизации которого соединен с соответствующими входами синхронизации буферных регистров, БИХ-фильтров, мультиплексоров и арифметических сумматоров-вычитателей, третий, четвертый и пятый управляющие выходы микропроцессорного комплекта соединены с корректирующими входами первого цифрового БИХ-фильтра, шестой, седьмой и восьмой управляющие выходы микропроцессорного комплекта соединены с соответствующими корректирующими входами второго цифрового БИХ-фильтра, девятый управляющий выход микропроцессорного комплекта подключен к управляющему входу блока индикации, введены цифроаналоговый генератор сигналов тональных частот, первый вход которого соединен со вторым выходом ключа, второй с первым управляющим выходом микропроцессорного комплекта, а третий вход - со вторым управляющим выходом микропроцессорного комплекта, третий мультиплексор, два входа которого соединены с выходами квадратурного демодулятора, а два других - с выходами цифроаналогового генератора сигналов тональных частот, первый выход третьего мультиплексора подключен к входу исследуемого канала связи и к входу первого АЦП, а второй выход - к входу второго АЦП, к выходу исследуемого канала связи подключена последовательная цепь из третьего АЦП, третьего буферного регистра, третьего цифрового БИХ-фильтра, корректирующие входы которого соединены с десятым, одиннадцатым и двенадцатым управляющими выходами микропроцессорного комплекта, и четвертого мультиплексора, три входа которого присоединены к трем соответствующим выходам третьего цифрового БИХ-фильтра, а девять выходов второго, третьего и четвертого мультиплексора попарно подключены на соответствующие входы шести арифметических сумматоров-вычитателей, выход первого арифметического сумматора-вычитателя соединен с первым входом первого арифметического блока умножения с накоплением, выход второго арифметического сумматора-вычитателя соединен со вторым входом первого арифметического блока умножения с накоплением, первым и вторым входами второго арифметического блока умножения с накоплением и первым входом третьего арифметического блока умножения с накоплением, выход третьего арифметического сумматора-вычитателя соединен со вторым входом третьего арифметического блока умножения с накоплением, выход четвертого арифметического сумматора-вычитателя соединен с первым входом четвертого арифметического блока умножения с накоплением, выход пятого арифметического сумматора-вычитателя соединен со вторым входом четвертого арифметического блока умножения с накоплением, первым и вторым входами пятого арифметического блока умножения с накоплением и первым входом шестого арифметического блока умножения с накоплением, а выход шестого арифметического сумматора-вычитателя соединен со вторым входом шестого арифметического блока умножения с накоплением, выходы первого, второго и третьего арифметических блоков умножения с накоплением соединены с соответствующими входами пятого мультиплексора, выход которого соединен с первым информационным входом микропроцессорного комплекта, а выходы четвертого, пятого и шестого арифметических блоков умножения с накоплением подключены соответственно к входам шестого мультиплексора, выход которого соединен со вторым информационным входом микропроцессорного комплекта, причем выход общей синхронизации микропроцессорного комплекта соединен с соответствующими входами синхронизации всех мультиплексоров, цифровых БИХ-фильтров, арифметических сумматоров-вычитателей, арифметических блоков умножения с накоплением, а вход и выход исследуемого канала связи являются входом и выходом устройства.

На чертеже представлена структурная схема устройства.

Цифровое устройство для измерения транспортного запаздывания сигнала содержит генератор 1 гармонических сигналов (термостабилизированный, кварцевый, опорной частоты, сдвинутых на 90° (эталонный генератор), формирователь импульсов синхронизации 2, счетчик 3, генератор прямоугольных импульсов 4, ключ 5, блок квадратурного демодулятора 6, цифровой блок 7 регулирования фазы синхронизации, два аналого-цифровых преобразователя (АЦП) 8, 9, первый и второй буферные регистры 10, 11, информационные входы которых являются измерительными входами для подключения соответствующих выходов АЦП, первый и второй мультиплексоры 12 и 13 с временным разделением коммутируемых каналов, первый и второй цифровые БИХ-фильтры 14 и 15, первый и второй арифметические сумматоры-вычитатели 16, 17, подключенные первыми входами на первый и второй выход мультиплексора 12 соответственно, цифроаналоговый генератор 18 сигналов тональных частот, первый вход которого соединен со вторым выходом ключа 5, третий мультиплексор 19, два входа которого соединены с выходами квадратурного демодулятора 6, а два других - с выходами цифроаналогового генератора 18 сигналов тональных частот, первый выход третьего мультиплексора 19 подключен к входу исследуемого канала связи 20 и к входу первого АЦП 8, а второй выход - к входу второго АЦП 9, к выходу исследуемого канала связи 20 подключена последовательная цепь из третьего АЦП 21, третьего буферного регистра 22, третьего цифрового БИХ-фильтра 23 и четвертого мультиплексора 24, три входа которого присоединены к трем соответствующим выходам третьего цифрового БИХ-фильтра 23, а девять выходов второго, третьего и четвертого мультиплексора 12, 13, 24 попарно подключены на соответствующие входы шести арифметических сумматоров-вычитателей 16, 17, 25, 26, 27, 28, выход первого арифметического сумматора-вычитателя 16 соединен с первым входом первого арифметического блока умножения с накоплением 29, выход второго арифметического сумматора-вычитателя 17 соединен со вторым входом первого арифметического блока умножения с накоплением 29, первым и вторым входами второго арифметического блока умножения с накоплением 30 и первым входом третьего арифметического блока умножения с накоплением 31, выход третьего арифметического сумматора-вычитателя 25 соединен со вторым входом третьего арифметического блока умножения с накоплением 31, выход четвертого арифметического сумматора-вычитателя 26 соединен с первым входом четвертого арифметического блока умножения с накоплением 32, выход пятого арифметического сумматора-вычитателя 27 соединен со вторым входом четвертого арифметического блока умножения с накоплением 32, первым и вторым входами пятого арифметического блока умножения с накоплением 33 и первым входом шестого арифметического блока умножения с накоплением 34, а выход шестого арифметического сумматора-вычитателя 28 соединен со вторым входом шестого арифметического блока умножения с накоплением 34, выходы первого, второго и третьего арифметических блоков умножения с накоплением 29, 30, 31 соединены с соответствующими входами пятого мультиплексора 35, а выходы четвертого, пятого и шестого арифметических блоков умножения с накоплением 26, 27, 28 подключены соответственно к входам шестого мультиплексора 36, выходы пятого и шестого мультиплексоров 35, 36 соединены с первым и вторым информационными входами микропроцессорного комплекта 37, причем выход общей синхронизации микропроцессорного комплекта соединен с соответствующими входами синхронизации всех мультиплексоров 12, 13, 19, 24, 35, 36, цифровых БИХ-фильтров 14, 15, 23, арифметических сумматоров-вычитателей 16, 17, 25, 26, 27, 28, арифметических блоков умножения с накоплением 29, 30, 31, 32, 33, 34, микропроцессорный комплект 37, содержащий входные и выходные регистры данных, блок обработки данных (БОД), блок микропрограммного управления (МПУ) и генератор синхроимпульсов (ГСИ), который синхронизирует работу МПУ, БОД, регистров, пятого и шестого мультиплексоров с временным разделением, и блок индикации 38. Устройство микропрограммного управления работает в конвейерном режиме, что позволяет повысить быстродействие за счет параллельной организации работы буферных регистров, цифровых БИХ-фильтров, мультиплексоров, арифметических сумматоров-вычитателей, арифметических блоков умножения с накоплением и микропроцессорного комплекта 37. Вход и выход исследуемого канала связи 20 являются измерительными входами устройства.

Измерение транспортного запаздывания сигналов τТ в технологии и технике связи, например в телефонии (от 100 Гц до 10 кГц) в режиме нормальной эксплуатации, сопровождается распределенными дистанционно индустриальными помехами ni(t), которые в общем случае на ограниченном интервале наблюдения имеют нестационарный характер. На вход исследуемого объекта 20 с первого выхода цифроаналогового генератора 18 сигналов тональных частот через третий мультиплексор 19 когерентно с сигналом общей синхронизации подается тест-сигнал Х1(nT). Одновременно этот сигнал поступает на вход первого АЦП 8. Со второго выхода цифроаналогового генератора 18 сигналов тональных частот через третий мультиплексор 19 на вход второго АЦП 9 подается когерентно копия тест-сигнала Х2(nT), сдвинутая во времени на эталонную задержку τМ, которая может программно управляться микропроцессорным комплектом 37. С выхода объекта исследования 20 сигнал Y*(t)=Y(t)+N(t), где Y(t) - полезный сигнал, a N(t) - обобщенная помеха, подается на вход третьего АЦП 21. Сигналы с выходов первого, второго и третьего АЦП 8, 9 и 21 в параллельном коде через первый, второй и третий буферные регистры 10, 11 и 22 поступают на соответствующие входы первого, второго и третьего цифровых БИХ-фильтров 14, 15 и 23.

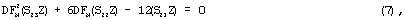

В соответствии с алгоритмом аппроксимации оператора транспортного запаздывания сигналов тональных частот e-τs рядом Паде и ограничиваясь для инженерной практики вторым порядком, на соответствующих выходах трех цифровых БИХ-фильтров 14, 15 и 23 непрерывно в конвейерном режиме формируются сигналы Сji(nT), где Т - шаг квантования во времени, единый для АЦП, буферных регистров и цифровых БИХ-фильтров, работающих в конвейерном режиме, а n=1, 2, 3, 4,...

Сигналы Сji(nT) снимаются с первых, вторых и третьих выходов соответствующих цифровых БИХ-фильтров, причем

Cj3(nT)=d Сj2(nT)/dt=d2 Сj1(nT)/dt,

где j=1, 2, 3.

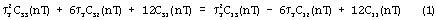

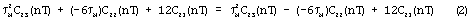

В отличие от прототипа непрерывно формируются параллельно во времени два алгебраических уравнения вида:

При этом эталонный сдвиг копии тест-сигнала Тэ на втором выходе цифроаналогового генератора 18 сигналов тональных частот выбран таким образом:

Для этого достаточно, чтобы |τэ|>|τт|.

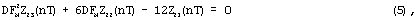

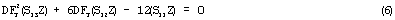

От уравнений (1) и (2) можно перейти к уравнениям вида:

где DFТ - неизвестный параметр, характеризующий знак и величину транспортного запаздывания сигнала тональных частот в линейном тракте исследуемого канала связи, включая АЦП и цифровые БИХ-фильтры, DFM - второй дополнительный параметр, позволяющий установить случайную погрешность измерения, вызванную в общем случае нестационарной помехой на интервале наблюдения. Этот параметр характеризует транспортное запаздывание сигнала на втором выходе генератора 18 относительно сигнала тональных частот на выходе исследуемого объекта 20.

Переменные Zij(nT) в дискретных точках (nT) формируются на соответствующих выходах арифметических сумматоров-вычитателей 16, 17, 25, 26, 27 и 28. Сигналы с выходов шести арифметических сумматоров-вычитателей попарно синхронно поступают на соответствующие входы шести арифметических блоков умножения с накоплением 29, 30, 31, 32, 33, 34.

Точность оценки транспортного запаздывания сигналов тональных частот в линейных трактах каналов связи с различными видами модуляции повышается при статистическом накоплении информации на арифметических блоках умножения с накоплением в результате синхронного управления цифроаналоговым генератором 18 сигналов тональных частот. Интегрирование сигналов, входящих в уравнения (4) и (5), на специально формируемых отрезках времени от niT до (ni+ki)T заменили численным интегрированием методом прямоугольников. Объем выборки контролируется микропрограммным управлением МПУ микропроцессорного комплекта 37, который решает затем в БОД два алгебраических квадратных уравнения, сформированных параллельно во времени:

где

j=1, 2; m=1, 2, 3.

Микропроцессорный комплект 37 в отличие от прототипа вычисляет два значения: DFT* и DFM*. Знаки и величины DFi* выводятся на блок индикации 38.

Используя тождество (3), при стационарном транспортном запаздывании сигналов тональных частот (что характерно для неподвижного расположения "абонент - узел связи") можно полностью устранить погрешность измерения транспортного запаздывания сигналов тональных частот, вызванную индустриальными помехами. Как показали экспериментальные исследования, в диапазоне от 50 Гц до 10 кГц точность измерения τТ* приближается к разрешающей способности микропроцессорного комплекта. При этом сохраняется возможность оперативной технической диагностики каналов связи в реальном масштабе времени. Перспективно применение данного цифрового устройства в задачах позиционирования мобильных абонентов в комбинированной сети передачи данных, включающей как проводные средства связи, так и радиоканалы. Повышенная точность измерения транспортного запаздывания сигналов в режиме нормальной эксплуатации повысит скорость диагностики и наладки сложных радиотехнических комплексов.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИНДЕНТИФИКАЦИИ ТОНАЛЬНЫХ СИГНАЛОВ В СЕТЯХ СВЯЗИ И ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2004 |

|

RU2291405C2 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ АДАПТИВНОЙ КОРРЕКЦИИ КВАДРАТУРНЫХ ДЕМОДУЛЯТОРОВ | 2000 |

|

RU2187140C2 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ЗАЩИТЫ ИНФОРМАЦИИ В СЕТЯХ СВЯЗИ | 2005 |

|

RU2295195C1 |

| ЦИФРОВОЙ КОГЕРЕНТНЫЙ ДЕМОДУЛЯТОР ЧЕТЫРЕХПОЗИЦИОННОГО СИГНАЛА С ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2017 |

|

RU2656577C1 |

| НЕКОГЕРЕНТНЫЙ ЦИФРОВОЙ ДЕМОДУЛЯТОР "В ЦЕЛОМ" КОДИРОВАННЫХ СИГНАЛОВ С ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2014 |

|

RU2556429C1 |

| ЦИФРОВОЕ КВАДРАТУРНОЕ УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ И ДЕМОДУЛЯЦИИ | 2015 |

|

RU2591032C1 |

| УСТРОЙСТВО УСКОРЕННОЙ СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2011 |

|

RU2446560C1 |

| Цифровой демодулятор сигналов с квадратурной амплитудной манипуляцией | 2015 |

|

RU2628427C2 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1992 |

|

RU2042269C1 |

| ЦИФРОВОЙ ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2011 |

|

RU2505922C2 |

Изобретение относится к измерительной технике и может быть использовано при измерениях в коммутируемых каналах сетей передачи информации, содержащих радиокомпоненты с аналоговыми и цифровыми сигналами. Техническим результатом является повышение точности измерения транспортного запаздывания сигналов, позволяющее полностью скомпенсировать случайные погрешности измерения. Устройство содержит генератор гармонических сигналов, формирователь импульсов синхронизации, счетчик, генератор прямоугольных импульсов, ключ, блок квадратурного демодулятора, цифровой блок регулирования фазы синхронизации, цифроаналоговый генератор сигналов тональных частот, три АЦП, три буферных регистра, три цифровых БИХ-фильтра, пять мультиплексоров временного разделения, шесть арифметических сумматоров-вычитателей, шесть арифметических блоков умножения с накоплением, микропроцессорный комплект с входными и выходными регистрами данных, блоком обработки данных, блоком микропрограммного управления и генератором синхроимпульсов и блок индикации. 1 ил.

Цифровое устройство для измерения транспортного запаздывания сигнала в технологии и технике связи, содержащее генератор гармонических сигналов эталонной опорной частоты, формирователь импульсов синхронизации, счетчик, генератор прямоугольных импульсов, цифровой блок регулирования фазы синхронизации, выход которого соединен с входом задания фазы генератора прямоугольных импульсов, выход которого через ключ подключен к сигнальному информационному входу квадратурного демодулятора, первый выход генератора гармонических сигналов опорной частоты соединен с первым синфазным входом квадратурного демодулятора и формирователем импульсов, соединенным с входом счетчика, при этом второй выход генератора гармонических сигналов опорной частоты соединен со вторым входом квадратурного демодулятора, информационные входы первого и второго буферных регистров являются измерительными входами для подключения к выходам соответственно первого и второго АЦП, первый и второй цифровые БИХ-фильтры подключены к выходам первого и второго буферных регистров соответственно, входы первого и второго мультиплексоров подключены к первому, второму и третьему выходам соответствующих цифровых БИХ-фильтров, первый управляющий выход микропроцессорного комплекта соединен с входом сброса в начальное состояние цифрового блока регулирования фазы синхронизации, второй вход которого подключен к второму управляющему выходу микропроцессорного комплекта, выход формирователя импульсов соединен с входом синхронизации микропроцессорного комплекта, выход общей синхронизации которого соединен с соответствующими входами синхронизации буферных регистров, БИХ-фильтров, мультиплексоров и арифметических сумматоров-вычитателей, третий, четвертый и пятый управляющие выходы микропроцессорного комплекта соединены с корректирующими входами первого цифрового БИХ-фильтра, шестой, седьмой и восьмой управляющие выходы микропроцессорного комплекта соединены с соответствующими корректирующими входами второго цифрового БИХ-фильтра, девятый управляющий выход микропроцессорного комплекта подключен к управляющему входу блока индикации, отличающееся тем, что в него введены цифроаналоговый генератор сигналов тональных частот, первый вход которого соединен со вторым выходом ключа, второй - с первым управляющим выходом микропроцессорного комплекта, а третий вход - со вторым управляющим выходом микропроцессорного комплекта, третий мультиплексор, два входа которого соединены с выходами квадратурного демодулятора, а два других - с выходами цифроаналогового генератора сигналов тональных частот, первый выход третьего мультиплексора подключен к входу исследуемого канала связи и к входу первого АЦП, а второй выход - к входу второго АЦП, к выходу исследуемого канала связи подключена последовательная цепь из третьего АЦП, третьего буферного регистра, третьего цифрового БИХ-фильтра, корректирующие входы которого соединены с десятым, одиннадцатым и двенадцатым управляющими выходами микропроцессорного комплекта, и четвертого мультиплексора, три входа которого присоединены к трем соответствующим выходам третьего цифрового БИХ-фильтра, а девять выходов первого, второго и четвертого мультиплексоров попарно подключены на соответствующие входы шести арифметических сумматоров-вычитателей, выход первого арифметического сумматора-вычитателя соединен с первым входом первого арифметического блока умножения с накоплением, выход второго арифметического сумматора-вычитателя соединен со вторым входом первого арифметического блока умножения с накоплением, первым и вторым входами второго арифметического блока умножения с накоплением и первым входом третьего арифметического блока умножения с накоплением, выход третьего арифметического сумматора-вычитателя соединен со вторым входом третьего арифметического блока умножения с накоплением, выход четвертого арифметического сумматора-вычитателя соединен с первым входом четвертого арифметического блока умножения с накоплением, выход пятого арифметического сумматора-вычитателя соединен со вторым входом четвертого арифметического блока умножения с накоплением, первым и вторым входами пятого арифметического блока умножения с накоплением и первым входом шестого арифметического блока умножения с накоплением, а выход шестого арифметического сумматора-вычитателя соединен со вторым входом шестого арифметического блока умножения с накоплением, выходы первого, второго и третьего арифметических блоков умножения с накоплением соединены с соответствующими входами пятого мультиплексора, выход которого соединен с первым информационным входом микропроцессорного комплекта, а выходы четвертого, пятого и шестого арифметических блоков умножения с накоплением подключены соответственно к входам шестого мультиплексора, выход которого соединен со вторым информационным входом микропроцессорного комплекта, причем выход общей синхронизации микропроцессорного комплекта соединен с соответствующими входами синхронизации всех мультиплексоров, цифровых БИХ-фильтров, арифметических сумматоров-вычитателей, арифметических блоков умножения с накоплением.

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ АДАПТИВНОЙ КОРРЕКЦИИ КВАДРАТУРНЫХ ДЕМОДУЛЯТОРОВ | 2000 |

|

RU2187140C2 |

| ИЗМЕРИТЕЛЬ ВРЕМЕННОЙ ЗАДЕРЖКИ СИГНАЛОВ В ДИНАМИЧЕСКИХ СИСТЕМАХ | 1992 |

|

RU2118847C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ И РЕГУЛИРОВАНИЯ ВРЕМЕНИ ЗАПАЗДЫВАНИЯ СИГНАЛОВ В ТРАКТАХ ПЕРЕДАЧИ КАНАЛА ТОНАЛЬНОЙ ЧАСТОТЫ | 1992 |

|

RU2040116C1 |

| АРОМАТИЧЕСКИЕ ДИКЕТОПРОИЗВОДНЫЕ, СПОСОБЫ ПОЛУЧЕНИЯ И ПРИМЕНЕНИЕ ДАННЫХ СОЕДИНЕНИЙ В КАЧЕСТВЕ ФАРМАЦЕВТИЧЕСКИХ СРЕДСТВ | 2000 |

|

RU2252211C2 |

Авторы

Даты

2005-08-20—Публикация

2003-09-19—Подача