Изобретение относится к области радиотехники и может использоваться в приемниках шумоподобных сигналов с минимальной частотной манипуляцией.

Известно устройство синхронизации цифрового приемника [патент RU №2138907, МПК H03L 7/12, H04L 7/033, опубл. 27.09.1999], содержащее цифровой фазовый детектор, аналоговый сумматор, двухвходовый мультиплексор, фильтр низких частот, вход которого соединен с выходом аналогового сумматора, а выход - с входом генератора, управляемого напряжением (ГУН), решающее устройство и блок определения состояния синхронизации, выполненное на триггерах. В устройстве обеспечивается непрерывное сравнение в блоке определения состояния синхронизации времени появления задних фронтов входных данных и сигнала генератора, управляемого напряжением. При потере синхронизации указанный блок формирует сигналы, индицирующие отсутствие синхронизации и опережение/отставание путем определения соотношения частот и фаз сигнала выходных данных и сигнала генератора, управляемого напряжением. Уровень сигнала индикации опережения/отставания устанавливается таким, чтобы он соответствовал уровню сигнала на выходе фазового детектора. При наличии помехи в линии в описанном выше устройстве синхронизации возможно ложное срабатывание, приводящее к нежелательному сканированию частоты ГУН. Для устранения этого в устройство синхронизации может быть введен цифровой интегратор на основе регистра сдвига с параллельными выходами и логической схемы И.

Недостатком выявленного аналога является значительное время установления фазовой синхронизации.

Наиболее близким техническим решением к заявляемому является устройство синхронизации приемника шумоподобных сигналов с минимальной частотной манипуляцией [патент RU №2357359, МПК Н04В 1/00, опубл. 27.05.2009], включающее аналого-цифровой преобразователь, вход которого является входом устройства, блок фазовой синхронизации и блок кодовой синхронизации. Блок фазовой синхронизации содержит фазовый дискриминатор, включающий первый и второй перемножители, сигнальные входы которых объединены и подключены к выходу аналого-цифрового преобразователя, а опорные входы соединены соответственно с квадратурными выходами синтезатора отсчетов несущей частоты, третий, четвертый, пятый, шестой и седьмой перемножители, вычитатель и первый сумматор, первый и второй интеграторы, решающий блок, выход которого является выходом демодулятора, а также первый петлевой фильтр, вход которого подключен к выходу третьего перемножителя, а выход соединен со входом синтезатора отсчетов несущей частоты. При этом сигнальные входы четвертого и шестого, пятого и седьмого перемножителей попарно объединены и подключены соответственно к выходу первого и второго перемножителей, опорные входы четвертого и пятого, шестого и седьмого перемножителей попарно объединены и подключены соответственно к квадратурным выходам блока кодовой синхронизации. Выходы четвертого и седьмого, пятого и шестого перемножителей объединены соответственно через вычитатель и первый сумматор, к выходам которых подключены первый и второй интеграторы соответственно. Сигнальный вход третьего перемножителя подключен к выходу второго интегратора. Опорный вход третьего перемножителя подключен к выходу решающего блока, вход которого соединен с выходом первого интегратора. Блок кодовой синхронизации содержит временной дискриминатор, включающий восьмой и девятый перемножители, сигнальные входы которых соединены соответственно с выходами первого и второго перемножителей, а опорные входы восьмого и девятого перемножителей соединены с попарно объединенными опорными входами шестого и седьмого, четвертого и пятого перемножителей соответственно и подключены к квадратурным выходам синтезатора отсчетов опорных квадратурных сигналов, второй сумматор, десятый и одиннадцатый перемножители, третий интегратор, а также последовательно соединенные второй петлевой фильтр, управляемый генератор тактовой частоты и генератор кода, к дополнительным выходам которого подключен дешифратор. При этом выходы восьмого и девятого перемножителей объединены через второй сумматор, к выходу которого подключен сигнальный вход десятого перемножителя, опорный вход которого подключен к инверсному выходу генератора кода, а выход одиннадцатого перемножителя соединен с входом третьего интегратора. Один вход одиннадцатого перемножителя подключен к выходу третьего интегратора, другой вход подключен к выходу решающего блока, а выход одиннадцатого перемножителя соединен с входом второго петлевого фильтра. Прямой выход генератора кода соединен со входом синтезатора отсчетов опорных квадратурных сигналов, а выход дешифратора соединен с синхронизирующими входами первого, второго и третьего интеграторов.

Известное устройство работает следующим образом.

Входной шумоподобный сигнал (ШПС) после дискретизации и оцифровки в аналого-цифровом преобразователе поступает на первый и второй перемножители, где он перемножается с отсчетами опорных сигналов cos(ω0t) и sin(ω0t) частоты ω0, равной средней частоте ШПС, которые вырабатываются синтезатором отсчетов несущей частоты. Отсчеты квадратурных составляющих комплексной огибающей ШПС с выходов первого и второго перемножителей на входы четвертого, шестого и пятого, седьмого перемножителей соответственно, где перемножаются с отсчетами опорных квадратурных сигналов, формируемых блоком кодовой синхронизации. При идеальной кодовой синхронизации опорные квадратурные сигналы являются точными копиями квадратурных компонентов I(t) и Q(t) комплексной огибающей принимаемого ШПС. Результаты перемножения отсчетов квадратурных составляющих входного и опорных сигналов объединяются в вычитателе и первом сумматоре, образуя соответственно «косинусную» и «синусную» квадратурные составляющие (составляющие удвоенной частоты ω0 подавляются при последующей обработке). Первый и второй интеграторы в квадратурных каналах фазового дискриминатора осуществляют когерентное накопление на интервале, равном периоду Tп повторения ШПС, поступающих на их входы отсчетов квадратурных составляющих, формируя соответственно корреляции z1 и z2. Сброс первого и второго интеграторов осуществляется с шагом Tп синхроимпульсами, вырабатываемыми блоком кодовой синхронизации.

Результаты z1 и z2 интегрирования в квадратурных каналах фазового дискриминатора поступают на третий перемножитель, формирующий сигнал ошибки, пропорциональный фазовому рассогласованию принимаемого ШПС и опорных сигналов частоты ω0. При этом корреляция z2 поступает на сигнальный вход третьего перемножителя непосредственно, а корреляция z1 поступает на опорный вход третьего перемножителя через решающий блок, осуществляющий преобразование вида sign(z1) (sign(x) - знаковая функция), благодаря чему исключается влияние цифровой модуляции ШПС на формирование сигнала ошибки. Выходной сигнал петлевого фильтра, сглаживающего флуктуации сигнала ошибки, используется для управления частотой и фазой опорных сигналов, формируемых синтезатором отсчетов несущей частоты.

Блок кодовой синхронизации работает следующим образом. Отсчеты квадратурных составляющих комплексной огибающей входного ШПС с выходов первого и второго перемножителей поступают соответственно на сигнальные входы восьмого и девятого перемножителей временного дискриминатора. На опорные входы восьмого и девятого перемножителей подаются отсчеты опорных квадратурных сигналов соответственно Q(t) и I(t), формируемых синтезатором отсчетов опорных квадратурных сигналов. Сигналы с выходов восьмого и девятого перемножителей объединяются во втором сумматоре, умножаются на отсчеты инверсной кодовой последовательности, формируемой генератором кода, и далее поступают на третий интегратор, который осуществляет когерентное накопление отсчетов на интервале Тп, формируя сигнал ошибки. С помощью одиннадцатого перемножителя исключается влияние цифровой модуляции ШПС на формирование сигнала ошибки, пропорционального временнóму рассогласованию входного ШПС и опорных квадратурных сигналов I(t) и Q(t). Второй петлевой фильтр сглаживает флуктуации сигнала ошибки, формируя управляющий сигнал для управляемого генератора тактовой частоты. Меандровый сигнал тактовой частоты fт=1/Т, вырабатываемый управляемым генератором тактовой частоты, поступает на вход генератора кода. Формируемая генератором кода кодовая последовательность поступает на вход синтезатора отсчетов опорных квадратурных сигналов, определяя знак приращения фазы р/2 на интервалах, равных длительности T элемента кодовой последовательности.

С выходов синтезатора отсчетов опорные квадратурные сигналы поступают на четвертый, пятый, шестой и седьмой перемножители фазового дискриминатора блока фазовой синхронизации, а также на восьмой и девятый перемножители временного дискриминатора. Дешифратор, подключенный к дополнительным выходам генератора кода, формирует синхронизирующий сигнал (синхроимпульсы с частотой повторения Fп=1/Tп) для первого, второго и третьего интеграторов соответственно фазового и временнóго дискриминаторов.

Недостатком выявленного прототипа является длительное время установления фазовой синхронизации при приеме шумоподобных сигналов с минимальной частотной манипуляцией на фоне флуктуационной помехи при отношении сигнал/шум, равном «минус» 40 дБ.

Задачей предлагаемого технического решения является сокращение времени установления фазовой синхронизации приемников шумоподобных сигналов с минимальной частотной манипуляцией.

Поставленная задача решается тем, что в устройстве ускоренной синхронизации приемника шумоподобных сигналов с минимальной частотной манипуляцией, включающем аналого-цифровой преобразователь, вход которого является входом устройства, блок фазовой синхронизации с фазовым дискриминатором, содержащим первый и второй перемножители, сигнальные входы которых объединены и подключены к выходу аналого-цифрового преобразователя, а опорные входы соответственно соединены с квадратурными выходами синтезатора отсчетов несущей частоты, третий, четвертый, пятый, шестой и седьмой перемножители, вычитатель и первый сумматор, первый и второй интеграторы, решающий блок, выход которого является выходом демодулятора, а также первый петлевой фильтр, вход которого подключен к выходу третьего перемножителя, сигнальный вход которого подключен к выходу второго интегратора, а опорный вход третьего перемножителя подключен к выходу решающего блока, вход которого соединен с выходом первого интегратора, при этом сигнальные входы четвертого и шестого, пятого и седьмого перемножителей попарно объединены и подключены к выходам соответственно первого и второго перемножителей, выходы четвертого и седьмого, пятого и шестого перемножителей объединены соответственно через вычитатель и первый сумматор, к выходам которых подключены первый и второй интеграторы, блок кодовой синхронизации, содержащий временной дискриминатор, включающий восьмой и девятый перемножители, сигнальные входы которых соединены соответственно с выходами первого и второго перемножителей, а опорные входы восьмого и девятого перемножителей соединены с попарно объединенными опорными входами шестого и седьмого, четвертого и пятого перемножителей соответственно и подключены к квадратурным выходам синтезатора отсчетов опорных квадратурных сигналов, второй сумматор, десятый и одиннадцатый перемножители, третий интегратор, а также последовательно соединенные второй петлевой фильтр, управляемый генератор тактовой частоты и генератор кода, к дополнительным выходам которого подключен дешифратор, при этом выходы восьмого и девятого перемножителей объединены через второй сумматор, к выходу которого подключен сигнальный вход десятого перемножителя, опорный вход которого подключен к инверсному выходу генератора кода, а выход перемножителя соединен со входом третьего интегратора, один вход одиннадцатого перемножителя подключен к выходу третьего интегратора, другой вход подключен к выходу решающего блока, а выход одиннадцатого перемножителя соединен со входом второго петлевого фильтра, прямой выход генератора кода соединен со входом синтезатора отсчетов опорных квадратурных сигналов, а выход дешифратора соединен с синхронизирующими входами первого, второго и третьего интеграторов, согласно изобретению в блок фазовой синхронизации дополнительно введен блок управления шумовой полосой устройства, вход которого соединен с выходом первого петлевого фильтра, а выход - со входом синтезатора отсчетов несущей частоты, блок управления шумовой полосой устройства содержит третий петлевой фильтр, первый вход которого является входом блока управления шумовой полосой устройства, второй вход подключен к выходу мультиплексора, а выход третьего петлевого фильтра является выходом блока управления шумовой полосой устройства, адресный вход мультиплексора соединен с выходом компаратора, разрешающий вход которого соединен с выходом инвертора, а вход инвертора подключен к выходу компаратора, при этом первый и второй сигнальные входы мультиплексора объединены соответственно с первым и вторым сигнальными входами компаратора и подключены к выходам первого и второго программируемых постоянных запоминающих устройств соответственно, причем разрешающие входы первого и второго программируемых постоянных запоминающих устройств объединены и подключены к выходу источника ЭДС, суммирующий асинхронный счетчик, выходы которого соединены с адресными входами первого программируемого постоянного запоминающего устройства, а разрешающий вход суммирующего асинхронного счетчика подключен к выходу источника ЭДС, и преобразователь кода, выходы которого соединены с адресными входами второго программируемого постоянного запоминающего устройства, а вход преобразователя кода подключен к выходу источника ЭДС.

Изобретение поясняется прилагаемыми чертежами, на которых представлено следующее:

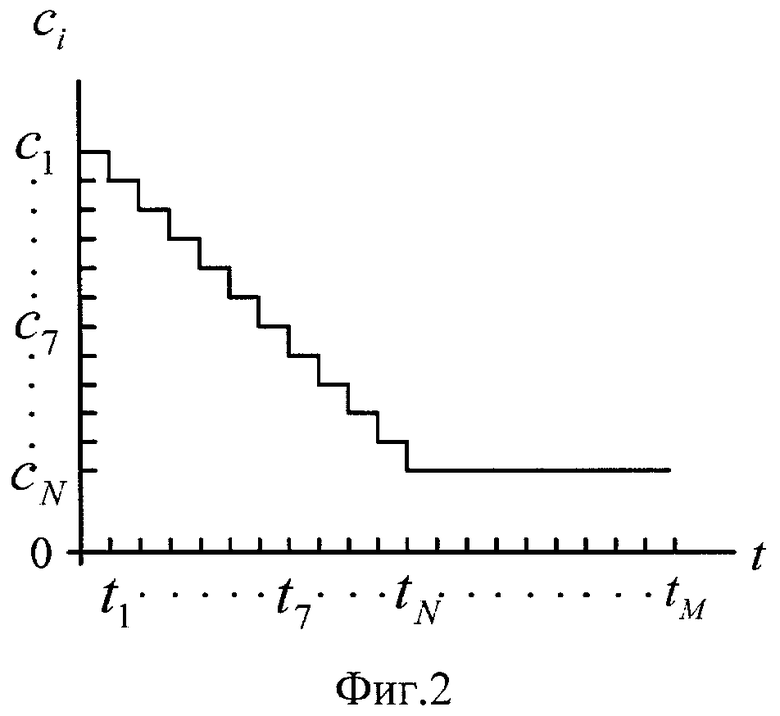

фиг.1 - функциональная схема устройства ускоренной синхронизации приемника шумоподобных сигналов с минимальной частотной манипуляцией;

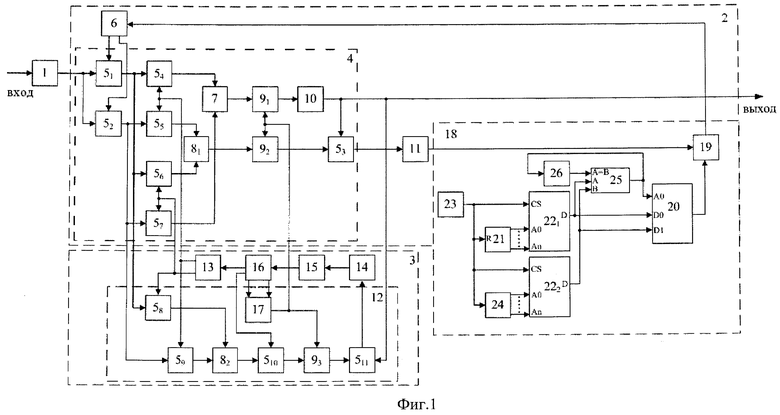

фиг.2 - зависимость величины коэффициента ci от времени t.

Устройство ускоренной синхронизации приемника шумоподобных сигналов с минимальной частотной манипуляцией (фиг.1) содержит аналого-цифровой преобразователь 1, вход которого является входом устройства, блок 2 фазовой синхронизации и блок 3 кодовой синхронизации. Блок 2 фазовой синхронизации содержит фазовый дискриминатор 4, включающий первый 51, второй 52, третий 53, четвертый 54, пятый 55, шестой 56 и седьмой 57 перемножители, вычитатель 7 и первый сумматор 81, первый и второй интеграторы 91 и 92, решающий блок 10, выход которого является выходом демодулятора, а также первый петлевой фильтр 11, выход которого соединен со входом блока 18 управления шумовой полосой устройства, а выход блока 18 управления шумовой полосой устройства соединен со входом синтезатора 6 отсчетов несущей частоты. Остальные связи между перечисленными элементами в блоке 2 фазовой синхронизации аналогичны описанным связям в блоке фазовой синхронизации по прототипу. Блок 3 кодовой синхронизации содержит временной дискриминатор 12, включающий восьмой 58, девятый 59, десятый 510 и одиннадцатый 511 перемножители, второй сумматор 82, третий интегратор 93, а также последовательно соединенные второй петлевой фильтр 14, управляемый генератор 15 тактовой частоты и генератор 16 кода, к дополнительным выходам которого подключен дешифратор 17, а прямой выход генератора 16 кода соединен со входом синтезатора 13 отсчетов опорных квадратурных сигналов. Остальные связи между перечисленными элементами в блоке 3 кодовой синхронизации аналогичны описанным связям в блоке кодовой синхронизации по прототипу. Связи между блоком 2 фазовой синхронизации и блоком 3 кодовой синхронизации аналогичны описанным связям между данными блоками по прототипу. Блок 18 управления шумовой полосой устройства содержит третий петлевой фильтр 19, мультиплексор 20, компаратор 25, инвертор 26, первое 221 и второе 222 программируемые постоянные запоминающие устройства (ППЗУ), источник ЭДС 23, суммирующий асинхронный счетчик 21 и преобразователь кода 24. Первый вход третьего петлевого фильтра 19, который является входом блока 18 управления шумовой полосой устройства, соединен с выходом первого петлевого фильтра 11. Выход третьего петлевого фильтра 19, который является выходом блока 18 управления шумовой полосой устройства, соединен с входом синтезатора 6 отсчетов несущей частоты. Второй вход третьего петлевого фильтра 19 подключен к выходу мультиплексора 20, адресный (А0) вход которого соединен с выходом компаратора 25. Разрешающий (А=В) вход компаратора 25 соединен с выходом инвертора 26, а вход инвертора 26 подключен к выходу компаратора 25. При этом первый (D0) и второй (D1) сигнальные входы мультиплексора 20 объединены соответственно с первым (А) и вторым (В) сигнальными входами компаратора 25 и подключены к выходам (D) первого 221 и второго 222 ППЗУ соответственно. Причем разрешающие (CS) входы первого 221 и второго 222 ППЗУ объединены и подключены к выходу источника ЭДС 23. Выходы суммирующего асинхронного счетчика 21 соединены с адресными (A0…AN) входами первого 221 ППЗУ, а разрешающий (R) вход суммирующего асинхронного счетчика 21 подключен к выходу источника ЭДС 23. Выходы преобразователя кода 24 соединены с адресными (A0…AN) входами второго 222 ППЗУ, а вход преобразователя кода 24 подключен к выходу источника ЭДС 23.

В зависимости от специфики решаемой задачи передаточная функция блока фазовой синхронизации (БФС) должна обеспечивать нужный порядок астатизма устройства синхронизации для минимизации ошибки синхронизации [Первачев С.В., Валуев А.А., Чиликин В.М. и др. Статистическая динамика радиотехнических следящих систем. - М.: Сов. радио, 1973. - 487 с.]. Для решения задачи ускоренной синхронизации приемника шумоподобных сигналов с минимальной частотной манипуляцией при пороговом отношении сигнал/шум, равном «минус» 40 дБ, целесообразно использовать БФС, включающий фазовый дискриминатор (ФД) 4, петлевой фильтр 11 и блок управления шумовой полосой 18 (БУШП), содержащий петлевой фильтр 19 с описанными связями. Передаточная функция БФС имеет вид:

K(p,t)=КД4·КПФ11(p)·КПФ19(p,t),

где КД4 - крутизна дискриминационной характеристики фазового дискриминатора;

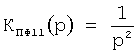

- передаточная функция петлевого фильтра 11;

- передаточная функция петлевого фильтра 11;

КПФ19(p,t)=ci(t)·(1+Tp) - передаточная функция петлевого фильтра 19 БУШП;

р - оператор Лапласа; t - время; Т - постоянная времени петлевого фильтра 19 БУШП;

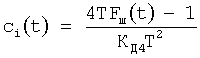

- текущее значение коэффициента передачи петлевого фильтра 19 БУШП;

- текущее значение коэффициента передачи петлевого фильтра 19 БУШП;

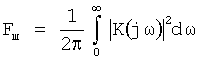

- шумовая полоса БФС;

- шумовая полоса БФС;

К(jω) - комплексный коэффициент передачи БФС.

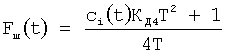

Тогда текущее значение шумовой полосы БФС рассчитывают по формуле:  .

.

Передаточная функция петлевого фильтра 19 БУШП КПФ19(p,t) регулируется путем задания текущего значения коэффициента передачи ci(t) петлевого фильтра 19 БУШП, что позволяет изменять текущее значение шумовой полосы БФС Fш(t) пропорционально текущим значениям коэффициента передачи ci(t) петлевого фильтра 19 БУШП.

На временном интервале t∈[0;tN] (см. фиг.2) текущее значение коэффициента передачи петлевого фильтра 19 БУШП ступенчато уменьшается от максимального значения с1 до минимального cN, а на временном интервале t∈[tN;tM] значение коэффициента передачи петлевого фильтра БУШП, равное cN, остается постоянным. При такой зависимости изменения коэффициента передачи сi петлевого фильтра 19 БУШП от времени t на временном интервале t∈[0;tN] значение шумовой полосы БФС Fш ступенчато уменьшается от максимального значения к минимальному, а на временном интервале t∈[tN;tM] значение шумовой полосы БФС Fш, равное минимальному, остается постоянным. Таким образом, сокращение времени установления фазовой синхронизации происходит вследствие уменьшения во времени значения шумовой полосы БФС.

Устройство ускоренной синхронизации приемника шумоподобных сигналов с минимальной частотной манипуляцией работает следующим образом.

Блок 3 кодовой синхронизации работает аналогично работе блока кодовой синхронизации по прототипу.

В фазовом дискриминаторе 4 блока 2 фазовой синхронизации сигнал ошибки, пропорциональный фазовому рассогласованию принимаемого ШПС и опорных сигналов частоты ω0, формируют аналогичным образом формирования данного сигнала по прототипу. Выходной сигнал петлевого фильтра 11 поступает на вход петлевого фильтра 19 блока 18 управления шумовой полосой устройства.

Блок 18 управления шумовой полосой устройства работает следующим образом.

После момента подачи питания сигнал с уровнем логической единицы '1', поступающий с выхода источника ЭДС 23 на разрешающие (CS) входы первого 221 и второго 222 ППЗУ, разрешает режим чтения с первого 221 и второго 222 ППЗУ. Одновременно сигнал с уровнем логической единицы '1', поступающий с выхода источника ЭДС 23 на разрешающий (R) вход суммирующего асинхронного счетчика 21, запускает работу счетчика 21 с периодом счета, равным 2 сек, и модулем счета, равным 11. В преобразователе кода 24 сигнал с уровнем логической единицы '1', приходящий от источника ЭДС, преобразуется в двоичный код, равный 0001.

В ячейки памяти первого 221 ППЗУ с адресами A0, A1…AN последовательно записаны значения коэффициента передачи петлевого фильтра БУШП с1, с2, …, cN, а в ячейку памяти второго 222 ППЗУ с адресом A1=(0001) записано значение коэффициента cN.

На временном интервале t∈[0;tN] (см. фиг.2) через каждые 2 сек суммирующий асинхронный счетчик 21 последовательно обращается к ячейкам памяти первого 221 ППЗУ с адресами от А0=0000 до AN=1011, в которых записаны значения коэффициента петлевого фильтра БУШП от с1 до cN.

Так как на всем временном интервале t∈[0;tM] сигнал с уровнем логической единицы '1' на входе преобразователя кода 24 остается постоянным, то на данном временном интервале преобразователь кода 24 постоянно обращается к ячейке памяти второго 222 ППЗУ с адресом A1=(0001), в которой записано значение коэффициента cN.

На всем временном интервале t∈[0;tM] с выхода (D) первого 221 ППЗУ значение коэффициента ci, записанное в ячейку памяти первого 221 ППЗУ с адресом Ai, который формирует счетчик 21, одновременно поступает на первый (D0) сигнальный вход мультиплексора 20 и первый (А) сигнальный вход компаратора 25. Также на всем временном интервале t∈[0;tM] с выхода (D) второго 222 ППЗУ значение коэффициента cN, записанное в ячейку памяти второго 222 ППЗУ с адресом A1=(0001), постоянно поступает на второй (D1) сигнальный вход мультиплексора 20, а также на второй (В) сигнальный вход компаратора 25. Компаратор 25 осуществляет сравнение значения коэффициента ci на первом (А) сигнальном входе со значением коэффициента cN на втором (В) сигнальном входе. При неравенстве значений коэффициентов ci и cN на первом (А) и втором (В) сигнальных входах компаратора 25 результатом сравнения является сигнал с уровнем логического нуля '0', а при равенстве - сигнал с логической единицы '1'. Постоянно в течение времени t∈[0;tN] на выходе компаратора формируется сигнал с уровнем логического нуля '0', который поступает на адресный (А0) вход мультиплексора 20. При этом на выход мультиплексора 20 поступает текущее значение коэффициента ci. Одновременно сигнал с уровнем логического нуля '0' через инвертор 26 поступает на разрешающий (А=В) вход компаратора 25, разрешая компаратору 25 дальнейшее сравнение значений коэффициентов на его сигнальных входах.

В момент времени tN на выходе компаратора 25 формируется сигнал с уровнем логической единицы '1', который поступает на адресный (А0) вход мультиплексора 20. Одновременно сигнал с уровнем логической единицы '1' через инвертор 26 поступает на разрешающий (А=В) вход компаратора 25, запрещая компаратору 25 дальнейшее сравнение значений коэффициентов на его сигнальных входах. С момента времени установления фиксированного значения коэффициента передачи петлевого фильтра 19 (tN) до окончания работы устройства (tM) на выход мультиплексора 20 поступает значение коэффициента cN.

Выходной сигнал мультиплексора 20, представленный на фиг.2, определяет передаточную функцию КПФ19(p,t) третьего петлевого фильтра 19 таким образом, чтобы текущее значение шумовой полосы Fш(t) блока фазовой синхронизации 18 изменялось пропорционально текущему значению коэффициента ci от максимального до минимального, что обеспечивает быстрый захват сигнала по частоте и фазе. Затем текущее значение шумовой полосы Fш(t) блока фазовой синхронизации 18 поддерживается постоянным, что приводит к высокой точности слежения в установившемся режиме. Выходной сигнал блока управления шумовой полосой устройства 18 используется для управления частотой и фазой опорных сигналов, формируемых синтезатором 6 отсчетов несущей частоты.

Пример реализации синтезатора отсчетов квадратурных сигналов с использованием накапливающего сумматора (аккумулятора фазы) и постоянного запоминающего устройства для хранения отсчетов квадратурных сигналов приведен в монографии [Цифровые системы фазовой синхронизации / М.И.Жодзишский, С.Ю.Сила-Новицкий, В.А.Прасолов и др. Под ред. М.И.Жодзишского. - М.: Сов. радио, 1980. - С.55-57].

На фоне флуктуационной помехи при отношении сигнал/шум, равном «минус» 40 дБ, заявляемое устройство обеспечивает сокращение времени установления фазовой синхронизации приемников шумоподобных сигналов с минимальной частотной манипуляцией не менее чем в 10 раз по сравнению с прототипом.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2007 |

|

RU2357359C2 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2008 |

|

RU2374776C2 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МОДУЛЯЦИЕЙ | 2014 |

|

RU2548010C1 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ | 2010 |

|

RU2431919C1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ СТРУКТУРНЫХ ПОМЕХ | 2010 |

|

RU2450445C2 |

| УСТРОЙСТВО КОМПЕНСАЦИИ СТРУКТУРНЫХ ПОМЕХ | 2013 |

|

RU2534221C1 |

| УСТРОЙСТВО СЛЕЖЕНИЯ ЗА ЧАСТОТОЙ ШУМОПОДОБНЫХ СИГНАЛОВ | 2007 |

|

RU2325041C1 |

| УСТРОЙСТВО СЛЕЖЕНИЯ ЗА ЗАДЕРЖКОЙ ШУМОПОДОБНЫХ ЧАСТОТНО-МАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2006 |

|

RU2313184C1 |

| СПОСОБ ПРИЕМА ШУМОПОДОБНЫХ ЧАСТОТНО-МАНИПУЛИРОВАННЫХ СИГНАЛОВ С НЕПРЕРЫВНОЙ ФАЗОЙ | 2006 |

|

RU2323536C1 |

| СПОСОБ ПРИЕМА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2006 |

|

RU2307474C1 |

Изобретение относится к области радиотехники и может использоваться в приемниках шумоподобных сигналов с минимальной частотной манипуляцией. Технический результат - сокращение времени установления фазовой синхронизации приемников шумоподобных сигналов с минимальной частотной манипуляцией. Устройство содержит аналого-цифровой преобразователь, блок фазовой синхронизации, включающий фазовый дискриминатор шумоподобных сигналов с минимальной частотной манипуляцией, петлевой фильтр, синтезатор отсчетов несущей частоты и блок управления шумовой полосой устройства с петлевым фильтром, а также блок кодовой синхронизации, включающий когерентный временной дискриминатор шумоподобных сигналов с минимальной частотной манипуляцией, петлевой фильтр, управляемый генератор тактовой частоты, генератор кода, дешифратор и синтезатор отсчетов опорных квадратурных сигналов. 2 ил.

Устройство ускоренной синхронизации приемника шумоподобных сигналов с минимальной частотной манипуляцией, включающее аналого-цифровой преобразователь, вход которого является входом устройства, блок фазовой синхронизации с фазовым дискриминатором, содержащим первый и второй перемножители, сигнальные входы которых объединены и подключены к выходу аналого-цифрового преобразователя, а опорные входы соответственно соединены с квадратурными выходами синтезатора отсчетов несущей частоты, третий, четвертый, пятый, шестой и седьмой перемножители, вычитатель и первый сумматор, первый и второй интеграторы, решающий блок, выход которого является выходом демодулятора, а также первый петлевой фильтр, вход которого подключен к выходу третьего перемножителя, сигнальный вход которого подключен к выходу второго интегратора, а опорный вход третьего перемножителя подключен к выходу решающего блока, вход которого соединен с выходом первого интегратора, при этом сигнальные входы четвертого и шестого, пятого и седьмого перемножителей попарно объединены и подключены к выходам соответственно первого и второго перемножителей, выходы четвертого и седьмого, пятого и шестого перемножителей объединены соответственно через вычитатель и первый сумматор, к выходам которых подключены первый и второй интеграторы соответственно, блок кодовой синхронизации, содержащий временной дискриминатор, включающий восьмой и девятый перемножители, сигнальные входы которых соединены соответственно с выходами первого и второго перемножителей, а опорные входы восьмого и девятого перемножителей соединены с попарно объединенными опорными входами шестого и седьмого, четвертого и пятого перемножителей соответственно и подключены к квадратурным выходам синтезатора отсчетов опорных квадратурных сигналов, второй сумматор, десятый и одиннадцатый перемножители, третий интегратор, а также последовательно соединенные второй петлевой фильтр, управляемый генератор тактовой частоты и генератор кода, к дополнительным выходам которого подключен дешифратор, при этом выходы восьмого и девятого перемножителей объединены через второй сумматор, к выходу которого подключен сигнальный вход десятого перемножителя, опорный вход которого подключен к инверсному выходу генератора кода, а выход десятого перемножителя соединен со входом третьего интегратора, один вход одиннадцатого перемножителя подключен к выходу третьего интегратора, другой вход подключен к выходу решающего блока, а выход одиннадцатого перемножителя соединен со входом второго петлевого фильтра, прямой выход генератора кода соединен со входом синтезатора отсчетов опорных квадратурных сигналов, а выход дешифратора соединен с синхронизирующими входами первого, второго и третьего интеграторов, отличающееся тем, что в блок фазовой синхронизации дополнительно введен блок управления шумовой полосой устройства, вход которого соединен с выходом первого петлевого фильтра, а выход - со входом синтезатора отсчетов несущей частоты, блок управления шумовой полосой устройства содержит третий петлевой фильтр, первый вход которого является входом блока управления шумовой полосой устройства, второй вход подключен к выходу мультиплексора, а выход третьего петлевого фильтра является выходом блока управления шумовой полосой устройства, адресный вход мультиплексора соединен с выходом компаратора, разрешающий вход которого соединен с выходом инвертора, а вход инвертора подключен к выходу компаратора, при этом первый и второй сигнальные входы мультиплексора объединены соответственно с первым и вторым сигнальными входами компаратора и подключены к выходам первого и второго программируемых постоянных запоминающих устройств соответственно, причем разрешающие входы первого и второго программируемых постоянных запоминающих устройств объединены и подключены к выходу источника ЭДС, суммирующий асинхронный счетчик, выходы которого соединены с адресными входами первого программируемого постоянного запоминающего устройства, а разрешающий вход суммирующего асинхронного счетчика подключен к выходу источника ЭДС, и преобразователь кода, выходы которого соединены с адресными входами второго программируемого постоянного запоминающего устройства, а вход преобразователя кода подключен к выходу источника ЭДС.

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ЦИФРОВОГО ПРИЕМНИКА | 1996 |

|

RU2138907C1 |

| СПОСОБ ПРИЕМА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2006 |

|

RU2307474C1 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2008 |

|

RU2374776C2 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2007 |

|

RU2357359C2 |

| US 6140869 A, 31.10.2000 | |||

| US 4942590 A, 30.10.1987 | |||

| EP 1484855 A1, 08.12.2004. | |||

Авторы

Даты

2012-03-27—Публикация

2011-01-11—Подача