Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано для построения функциональных узлов аналоговых вычислительных машин, средств автоматического регулирования и управления, аналоговых процессоров и др.

Известны ранговые селекторы (см., например, фиг.1 в описании изобретения к патенту РФ 2192044, кл. G 06 G 7/52, 2002 г.), которые выполняют селекцию (выбор) из n(n≥2) аналоговых сигналов х1,...,хn сигнала х(r) любого ранга

К причине, препятствующей достижению указанного ниже технического результата при использовании известных ранговых селекторов, относится сложная настройка, обусловленная тем, что для ее реализации необходимо nV+V-1 управляющих сигналов, где  m=0,5(n+1) (m=0,5n)при нечетном (четном) n.

m=0,5(n+1) (m=0,5n)при нечетном (четном) n.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятый за прототип, ранговый селектор (фиг.1 в описании изобретения к патенту РФ 2172980, кл. G 06 G 7/25, 2001 г.), который содержит n замыкающих и n размыкающих ключей, 2n устройств выборки/хранения, булевый инвертор и может быть использован для выполнения селекции из n(n≥2) аналоговых сигналов сигнала любого ранга r∈{1,...,n}.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится сложная настройка, обусловленная тем, что для ее реализации необходимо два управляющих сигнала и два опорных напряжения.

Техническим результатом изобретения является упрощение настройки за счет обеспечения ее реализации с помощью двух управляющих сигналов.

Указанный технический результат при осуществлении изобретения достигается тем, что в ранговом селекторе, содержащем булевый инвертор, n(n≥2) замыкающих и n размыкающих ключей и 2n устройств выборки/хранения, особенность заключается в том, что в него введены логические ячейки, каждая из которых содержит элемент «MIN», подсоединенный первым, вторым входами и выходом соответственно к ее первому, второму входам и первому выходу, и элемент «МАХ», подсоединенный первым, вторым входами и выходом соответственно к ее первому, второму входам и второму выходу, выход и вход i-го  размыкающего ключа соединены соответственно с объединенными выходом i-го замыкающего ключа, информационным входом i-го устройства выборки/хранения и объединенными i-ым выходом рангового селектора, выходом (n+i)-го устройства выборки/хранения, подсоединенного входом записи к выходу булевого инвертора, вход которого соединен с входом записи i-го устройства выборки/хранения и вторым настроечным входом рангового селектора, подсоединенного первым настроечным и i-ым информационным входами соответственно к управляющему входу всех ключей и входу i-го замыкающего ключа, все логические ячейки сгруппированы в две группы так, что первая и вторая группы содержат соответственно g и k логических ячеек, первый и второй входы b-й

размыкающего ключа соединены соответственно с объединенными выходом i-го замыкающего ключа, информационным входом i-го устройства выборки/хранения и объединенными i-ым выходом рангового селектора, выходом (n+i)-го устройства выборки/хранения, подсоединенного входом записи к выходу булевого инвертора, вход которого соединен с входом записи i-го устройства выборки/хранения и вторым настроечным входом рангового селектора, подсоединенного первым настроечным и i-ым информационным входами соответственно к управляющему входу всех ключей и входу i-го замыкающего ключа, все логические ячейки сгруппированы в две группы так, что первая и вторая группы содержат соответственно g и k логических ячеек, первый и второй входы b-й  логической ячейки первой группы соединены соответственно с выходами (2b-1)-го и (2b)-го устройств выборки/хранения, первый и второй выходы с-й

логической ячейки первой группы соединены соответственно с выходами (2b-1)-го и (2b)-го устройств выборки/хранения, первый и второй выходы с-й  логической ячейки второй группы подключены соответственно к информационным входам (n+2с)-го и (n+2с +1)-го устройств выборки/хранения, второй выход b-й

логической ячейки второй группы подключены соответственно к информационным входам (n+2с)-го и (n+2с +1)-го устройств выборки/хранения, второй выход b-й  предыдущей и первый выход (b+1)-й логических ячеек первой группы соединены соответственно с первым и вторым входами b-й логической ячейки второй группы, а первый выход первой логической ячейки первой группы подключен к информационному входу (n+1)-го устройства выборки/хранения, кроме того при четном n k=0,5n-1 и второй выход g-й (g=0,5n) логической ячейки первой группы соединен с информационным входом (2n)-го устройства выборки/хранения, а при нечетном n первый и второй входы k-й (k=0,5(n-1)) логической ячейки второй группы соединены соответственно с вторым выходом g-й (g=0,5(n-1)) логической ячейки первой группы и выходом n-го устройства выборки/хранения.

предыдущей и первый выход (b+1)-й логических ячеек первой группы соединены соответственно с первым и вторым входами b-й логической ячейки второй группы, а первый выход первой логической ячейки первой группы подключен к информационному входу (n+1)-го устройства выборки/хранения, кроме того при четном n k=0,5n-1 и второй выход g-й (g=0,5n) логической ячейки первой группы соединен с информационным входом (2n)-го устройства выборки/хранения, а при нечетном n первый и второй входы k-й (k=0,5(n-1)) логической ячейки второй группы соединены соответственно с вторым выходом g-й (g=0,5(n-1)) логической ячейки первой группы и выходом n-го устройства выборки/хранения.

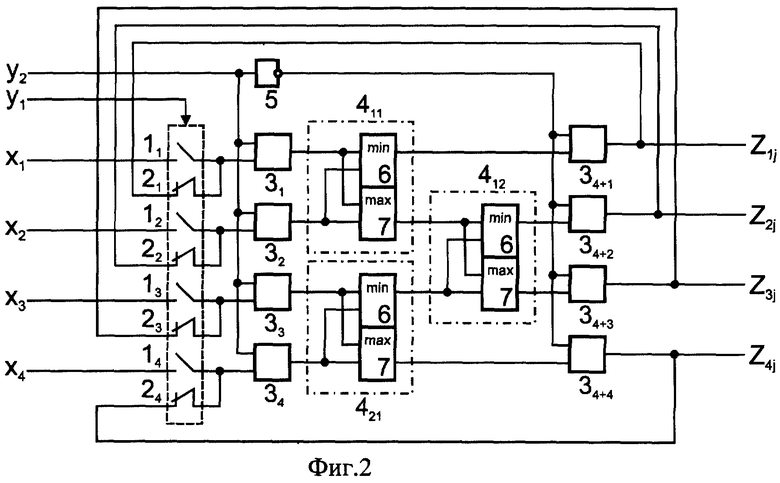

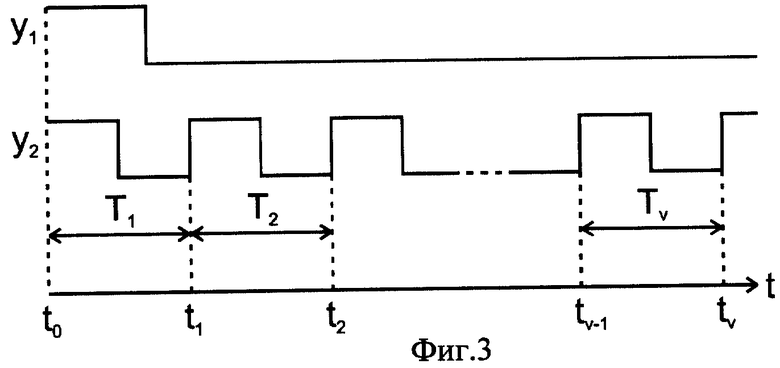

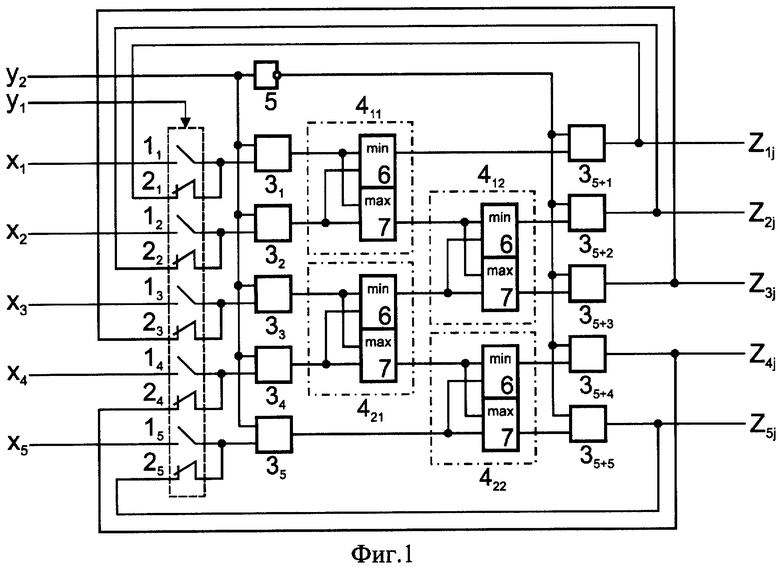

На фиг.1 и 2 представлены схемы предлагаемого рангового селектора, например при n=5 и n=4 соответственно; на фиг.3 приведены временные диаграммы сигналов настройки.

Ранговый селектор содержит замыкающие и размыкающие ключи 11,...,1n и 21,...,2n; устройства выборки/хранения 31,...,3n+n; логические ячейки 411,...,4g1, 412,...4k2, где g=k=0,5(n-1) либо g=0,5n, k=0,5n-1 при нечетном либо четном n(n>2) соответственно; булевый инвертор 5. Каждая логическая ячейка содержит элемент «MIN» 6, подсоединенный первым, вторым входами и выходом соответственно к ее первому, второму входам и первому выходу, и элемент «МАХ» 7, подсоединенный первым, вторым входами и выходом соответственно к ее первому, второму входам и второму выходу. Выход и вход ключа  соединены соответственно с объединенными выходом ключа 1i, информационным входом устройства 3i и объединенными i-ым выходом рангового селектора, выходом устройства 3n+i, подсоединенного входом записи к выходу инвертора 5, вход которого соединен с входом записи устройства 3i и вторым настроечным входом рангового селектора, подсоединенного первым настроечным и i-ым информационным входами соответственно к управляющему входу всех ключей и входу ключа 1i, первый и второй входы ячейки

соединены соответственно с объединенными выходом ключа 1i, информационным входом устройства 3i и объединенными i-ым выходом рангового селектора, выходом устройства 3n+i, подсоединенного входом записи к выходу инвертора 5, вход которого соединен с входом записи устройства 3i и вторым настроечным входом рангового селектора, подсоединенного первым настроечным и i-ым информационным входами соответственно к управляющему входу всех ключей и входу ключа 1i, первый и второй входы ячейки  соединены соответственно с выходами устройств 32b-1 и 32b,, первый и второй выходы ячейки 4c2

соединены соответственно с выходами устройств 32b-1 и 32b,, первый и второй выходы ячейки 4c2 подключены соответственно к информационным входам устройств 3n+2с и 3n+2с+1, второй выход b-й

подключены соответственно к информационным входам устройств 3n+2с и 3n+2с+1, второй выход b-й  предыдущей ячейки первой группы и первый выход ячейки 4(b+1)1 соединены соответственно с первым и вторым входами ячейки 4b2, а первый выход ячейки 411 подключен к информационному входу устройства 3n+1, кроме того при четном n второй выход ячейки 4g1 соединен с информационным входом устройства 3n+n, а при нечетном n первый и второй входы ячейки 4k2 соединены соответственно с вторым выходом ячейки 4g1 и выходом устройства 3n.

предыдущей ячейки первой группы и первый выход ячейки 4(b+1)1 соединены соответственно с первым и вторым входами ячейки 4b2, а первый выход ячейки 411 подключен к информационному входу устройства 3n+1, кроме того при четном n второй выход ячейки 4g1 соединен с информационным входом устройства 3n+n, а при нечетном n первый и второй входы ячейки 4k2 соединены соответственно с вторым выходом ячейки 4g1 и выходом устройства 3n.

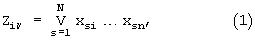

Работа предлагаемого рангового селектора осуществляется следующим образом. На его первый,..., n-й (n≥2) информационные и первый, второй настроечные входы подаются соответственно аналоговые сигналы (напряжения) х1,...,xn и управляющие двоичные сигналы у1,у2 ∈{0,1} (фиг.3). При у1=1 либо у1=0 ключ  соответственно замкнут либо разомкнут, а ключ 2i соответственно разомкнут либо замкнут. При у2=1(у2=0) устройства 3i и 3n+i работают соответственно в режимах выборки (хранения) и хранения (выборки). Элементы 6 и 7 воспроизводят базовые операции бесконечнозначной логики (БЛ): соответственно БЛ-конъюнкцию (min) и БЛ-дизъюнкцию (max), то есть осуществляют выбор соответственно наименьшего и наибольшего из двух аналоговых сигналов, действующих на их входах. Тогда напряжения на первом, произвольном четном и произвольном нечетном (кроме первого) выходах предлагаемого селектора будут определяться соответственно рекуррентными выражениями

соответственно замкнут либо разомкнут, а ключ 2i соответственно разомкнут либо замкнут. При у2=1(у2=0) устройства 3i и 3n+i работают соответственно в режимах выборки (хранения) и хранения (выборки). Элементы 6 и 7 воспроизводят базовые операции бесконечнозначной логики (БЛ): соответственно БЛ-конъюнкцию (min) и БЛ-дизъюнкцию (max), то есть осуществляют выбор соответственно наименьшего и наибольшего из двух аналоговых сигналов, действующих на их входах. Тогда напряжения на первом, произвольном четном и произвольном нечетном (кроме первого) выходах предлагаемого селектора будут определяться соответственно рекуррентными выражениями

Z1j=Z1(j-1)Z2(j-1),

Zρj=(Z(ρ-1)(j-1)∨Zρ(j-1)Z(ρ+1)(j-1)Z(ρ+2)(j-1))и

Zgj=Z(g-2)(j-1)∨Z(g-1)(j-1)∨Zg(j-1)Z(j-1)Z(g+1)(j-1),

где символами ∨ и · обозначены операции max и min;  - есть номер момента времени tj (фиг.3), здесь ν=0,5n(ν=0,5(n+1)) при четном (нечетном) n; Zi0=хi. В представленной ниже таблице приведены полученные согласно указанных рекуррентных выражений соотношения, определяющие сигналы на первом,...,n-ом выходах предлагаемого селектора при n=5.

- есть номер момента времени tj (фиг.3), здесь ν=0,5n(ν=0,5(n+1)) при четном (нечетном) n; Zi0=хi. В представленной ниже таблице приведены полученные согласно указанных рекуррентных выражений соотношения, определяющие сигналы на первом,...,n-ом выходах предлагаемого селектора при n=5.

С учетом данных, приведенных в таблице, нетрудно вывести непосредственное выражение для Ziν:

где xsi≠...≠xsn ∈{x1...xn};  - есть количество неповторяющихся БЛ-конъюнкций xsi,...хsn, определяемое как число сочетаний из n по n+1-i. При i=r выражение (1) совпадает с видом поисковой функции (функция (6.7) на стр. 117 в книге Левин В.И. Бесконечнозначная логика в задачах кибернетики. М.: Радио и связь, 1982 г.), которая реализует алгоритм поиска (селекции) элемента x(r) заданного ранга r∈{1,...,n} в множестве {x1,...,xn} (x(1) ≤...≤х(n); {x(1)}U...U{x(n)}={x1,...,xn}). Таким образом, предлагаемый селектор будет воспроизводить операцию Zrν,=x(r) селекции из n аналоговых сигналов х1,...,хn сигнала х(r) любого ранга r∈{1,...,n}.

- есть количество неповторяющихся БЛ-конъюнкций xsi,...хsn, определяемое как число сочетаний из n по n+1-i. При i=r выражение (1) совпадает с видом поисковой функции (функция (6.7) на стр. 117 в книге Левин В.И. Бесконечнозначная логика в задачах кибернетики. М.: Радио и связь, 1982 г.), которая реализует алгоритм поиска (селекции) элемента x(r) заданного ранга r∈{1,...,n} в множестве {x1,...,xn} (x(1) ≤...≤х(n); {x(1)}U...U{x(n)}={x1,...,xn}). Таким образом, предлагаемый селектор будет воспроизводить операцию Zrν,=x(r) селекции из n аналоговых сигналов х1,...,хn сигнала х(r) любого ранга r∈{1,...,n}.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый ранговый селектор обладает более простой по сравнению с прототипом настройкой, так как обеспечивает селекцию из n(n≥2) аналоговых сигналов сигнала любого ранга r∈{1,...,n} с помощью двух управляющих сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| РАНГОВЫЙ СЕЛЕКТОР | 2003 |

|

RU2240597C1 |

| РАНГОВЫЙ СЕЛЕКТОР | 2003 |

|

RU2248042C1 |

| РАНГОВЫЙ СЕЛЕКТОР | 2000 |

|

RU2172980C1 |

| РАНГОВЫЙ СЕЛЕКТОР | 2005 |

|

RU2284572C1 |

| РАНГОВЫЙ СЕЛЕКТОР | 2002 |

|

RU2227932C1 |

| РАНГОВЫЙ СЕЛЕКТОР | 2005 |

|

RU2292586C1 |

| РАНГОВЫЙ СОРТИРОВЩИК | 2005 |

|

RU2284573C1 |

| РАНГОВЫЙ СОРТИРОВЩИК | 2006 |

|

RU2324222C1 |

| РАНГОВЫЙ СОРТИРОВЩИК | 2004 |

|

RU2260845C1 |

| ЛОГИЧЕСКИЙ ПРОЦЕССОР | 2004 |

|

RU2260205C1 |

Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано для построения функциональных узлов аналоговых вычислительных машин, средств автоматического регулирования и управления, аналоговых процессоров. Техническим результатом изобретения является упрощение настройки за счет обеспечения ее реализации с помощью двух управляющих сигналов. Устройство содержит булевый инвертор, n замыкающих и n размыкающих ключей, 2n устройств выборки/хранения и 2 группы логических ячеек, каждая из которых содержит элемент «MIN» и элемент «МАХ», при этом при четном n - количество ячеек первой группы k=0,5n-1, количество ячеек второй группы g=0,5n; при нечетном n-k=0,5(n-1), g=0,5(n-1). 3 ил., 1 табл.

Ранговый селектор, содержащий булевый инвертор, n (n≥2) замыкающих и n размыкающих ключей и 2п устройств выборки/хранения, отличающийся тем, что в него введены логические ячейки, каждая из которых содержит элемент MIN, подсоединенный первым, вторым входами и выходом соответственно к ее первому, второму входам и первому выходу, и элемент МАХ, подсоединенный первым, вторым входами и выходом соответственно к ее первому, второму входам и второму выходу, выход и вход i-го  размыкающего ключа соединены соответственно с объединенными выходом i-го замыкающего ключа, информационным входом i-го устройства выборки/хранения и объединенными i-ым выходом рангового селектора, выходом (n+i)-го устройства выборки/хранения, подсоединенного входом записи к выходу булевого инвертора, вход которого соединен с входом записи i-го устройства выборки/хранения и вторым настроечным входом рангового селектора, подсоединенного первым настроечным и i-ым информационным входами соответственно к управляющему входу всех ключей и входу i-го замыкающего ключа, все логические ячейки сгруппированы в две группы так, что первая и вторая группы содержат соответственно g и k логических ячеек, первый и второй входы b-ой

размыкающего ключа соединены соответственно с объединенными выходом i-го замыкающего ключа, информационным входом i-го устройства выборки/хранения и объединенными i-ым выходом рангового селектора, выходом (n+i)-го устройства выборки/хранения, подсоединенного входом записи к выходу булевого инвертора, вход которого соединен с входом записи i-го устройства выборки/хранения и вторым настроечным входом рангового селектора, подсоединенного первым настроечным и i-ым информационным входами соответственно к управляющему входу всех ключей и входу i-го замыкающего ключа, все логические ячейки сгруппированы в две группы так, что первая и вторая группы содержат соответственно g и k логических ячеек, первый и второй входы b-ой  логической ячейки первой группы соединены соответственно с выходами (2b-1)-го и (2b)-го устройств выборки/хранения, первый и второй выходы с-ой

логической ячейки первой группы соединены соответственно с выходами (2b-1)-го и (2b)-го устройств выборки/хранения, первый и второй выходы с-ой  логической ячейки второй группы подключены соответственно к информационным входам (n+2с)-го и (n+2с+1)-го устройств выборки/хранения, второй выход b-ой

логической ячейки второй группы подключены соответственно к информационным входам (n+2с)-го и (n+2с+1)-го устройств выборки/хранения, второй выход b-ой  предыдущей и первый выход (b+1)-ой логических ячеек первой группы соединены соответственно с первым и вторым входами b-ой логической ячейки второй группы, а первый выход первой логической ячейки первой группы подключен к информационному входу (n+1)-го устройства выборки/хранения, кроме того, при четном n k=0,5n-1 и второй выход g-ой (g=0,5n) логической ячейки первой группы соединен с информационным входом (2n)-го устройства выборки/хранения, а при нечетном n первый и второй входы k-ой (k=0,5(n-1)) логической ячейки второй группы соединены соответственно с вторым выходом g-ой (g=0,5(n-1) логической ячейки первой группы и выходом n-го устройства выборки/хранения.

предыдущей и первый выход (b+1)-ой логических ячеек первой группы соединены соответственно с первым и вторым входами b-ой логической ячейки второй группы, а первый выход первой логической ячейки первой группы подключен к информационному входу (n+1)-го устройства выборки/хранения, кроме того, при четном n k=0,5n-1 и второй выход g-ой (g=0,5n) логической ячейки первой группы соединен с информационным входом (2n)-го устройства выборки/хранения, а при нечетном n первый и второй входы k-ой (k=0,5(n-1)) логической ячейки второй группы соединены соответственно с вторым выходом g-ой (g=0,5(n-1) логической ячейки первой группы и выходом n-го устройства выборки/хранения.

| РАНГОВЫЙ СЕЛЕКТОР | 2000 |

|

RU2172980C1 |

| РЕЛЯТОРНЫЙ СЕЛЕКТОР | 2001 |

|

RU2192044C1 |

| РАНГОВЫЙ ФИЛЬТР | 2000 |

|

RU2171496C1 |

| РАНГОВЫЙ ИДЕНТИФИКАТОР | 1999 |

|

RU2149454C1 |

| Многоканальный амплитудный селектор | 1985 |

|

SU1262531A1 |

| US 5586217 A, 17.12.1996. | |||

Авторы

Даты

2005-10-20—Публикация

2004-06-04—Подача