Предлагаемое изобретение относится к импульсной технике и может быть использовано, в частности, в измерительной аппаратуре. Известно устройство для формирования импульсов разностной частоты [1]. Наиболее близким по технической сущности из известных устройств является устройство формирования суммы, разности и знака разности двух частот, содержащее первый и второй формирователи, с первого по шестой триггеры, с первого по четвертый элементы "И", с первого по третий элементы "И-НЕ", первый и второй элементы задержки [2]. Основным недостатком данного устройства является неравномерность во времени периодов суммы и разности двух частот, что делает его непригодным в режиме измерения длительности периодов следования импульсов этих частот.

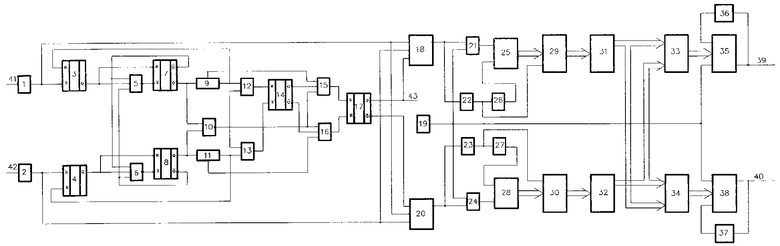

Целью изобретения является формирование суммы и разности двух частот с постоянными для каждой частоты периодами следования импульсов. Для достижения этой цели в устройство, содержащее формирователи 1 и 2 импульсов, триггеры 3, 4, 7, 8, 14, 17, элементы "И-НЕ" 5, 6, 10, элементы "И" 12, 13, 15, 16, элементы задержки 9, 11, первую шину 41, вторую шину 42 входных частот, шину знака разности двух частот 43, введены селекторы 18, 20, элементы "И" 21, 24, элементы задержки 22, 23, 26, 27, 36, 37, счетчики 25, 28, 35, 38, генератор импульсов 19, буферные регистры 29, 30, преобразователи кодов 31, 32, 33, 34, шина суммы двух частот 39, шина разности двух частот 40.

На чертеже представлена структурная схема формирователя. Формирователь содержит первый 1 и второй 2 формирователи импульсов, триггеры 3, 4, 7, 8, 14, 17, элементы "И-НЕ" 5, 6, 10, элементы "И" 12, 13, 15, 16, 21, 24, элементы задержки 9, 11, 22, 23, 26, 27, 36, 37, счетчики 25, 28, 35, 38, генератор импульсов 19, буферные регистры 29, 30, преобразователи кодов 31, 32, 33, 34, селекторы 18, 20, первую входную шину 41, вторую входную шину 42, шину суммы двух частот 39, шину разности двух частот 40 и шину знака разности двух частот 43.

На первую входную шину 41, подключенную к входу первого формирователя 1, поступает частота F1, а на вторую входную шину 42, соединенную с входом второго формирователя 2, подается частота F2. Выход первого формирователя 1 связан с установочным входом первого триггера 3 и вторыми входами первого 18 и второго 20 селекторов. Выход первого триггера 3 подключен к первому входу первого элемента "И-НЕ" 5 и входу сброса третьего триггера 7. Выход второго формирователя 2 соединен с установочным входом второго триггера 4 и третьими входами первого 18 и второго 20 селекторов. Выход второго триггера 4 связан с первым входом второго элемента "И-НЕ" 6 и входом сброса четвертого триггера 8. Установочный вход четвертого триггера 8 подключен к выходу второго элемента "И-НЕ" 6, а установочный вход третьего триггера 7 - к выходу первого элемента "И-НЕ" 5. Инверсный выход третьего триггера 7 соединен с объединенными между собой вторыми входами первого 5 и второго 6 элементов "И-НЕ", а инверсный выход четвертого триггера 8 - с объединенными между собой третьими входами первого 5 и второго 6 элементов "И-НЕ". Прямой выход третьего триггера 7 связан с входом первого элемента задержки 9 и первым входом третьего элемента "И-НЕ" 10, а прямой выход четвертого триггера 8 подключен к второму входу третьего элемента "И-НЕ" 10 и входу второго элемента задержки 11. Выход третьего элемента "И-НЕ" 10 соединен с первыми входами первого 12, второго 13, третьего 15 и четвертого 16 элементов "И". Первый выход первого элемента задержки 9 связан с вторым входом третьего элемента "И" 15, а первый выход второго элемента задержки 11 подключен к второму входу четвертого элемента "И" 16. Прямой выход пятого триггера 14 соединен с третьим входом третьего элемента "И" 15, а инверсный - с третьим входом четвертого элемента "И" 16. Второй выход первого элемента задержки 9 соединен с вторым входом первого элемента "И" 12 и входом сброса первого триггера 3, а второй выход второго элемента задержки 11 - с вторым входом второго элемента "И" 13 и входом сброса второго триггера 4. Выход первого элемента "И" 12 подключен к входу сброса пятого триггера 14, а выход второго элемента "И" 3 - к входу установки пятого триггера 14. Выход третьего элемента "И" 15 связан с входом установки шестого триггера 17, а выход четвертого элемента "И" 16 - с входом сброса того же триггера 17. Прямой выход триггера 17 подключен к первому входу селектора 18 и выходной шине 43 знака разности двух частот, а инверсный выход - к первому входу селектора 20.

Выход первого селектора 18 связан с входом третьего элемента задержки 22 и вторым входом пятого элемента "И" 21, а выход второго селектора - с входом четвертого элемента задержки 23 и вторым входом шестого элемента "И" 24. Выход генератора импульсов 19 подключен к соединенным между собой первыми входами пятого 21 и шестого 24 элементов "И", а также счетными входами третьего 35 и четвертого 38 счетчиков. Выход пятого элемента "И" 21 связан с счетным входом первого счетчика 25, а выход шестого элемента "И" 24 - с счетным входом второго счетчика 28. Установочный вход первого счетчика 25 подключен к выходу пятого элемента задержки 26, вход которого объединен с установочным входом первого буферного регистра 29 и выходом третьего элемента задержки 22. Установочный вход второго счетчика 28 соединен с выходом шестого элемента задержки 27, вход которого объединен с установочным входом второго буферного регистра 30 и выходом четвертого элемента задержки 23. Выход первого счетчика 25 связан с кодовым входом первого буферного регистра 29, а выход второго счетчика 28 - с кодовым входом второго буферного регистра 30. Выход первого буферного регистра 29 подключен к входу первого преобразователя кодов 31, а выход второго буферного регистра 30 - к входу второго преобразователя кодов 32. Выход первого преобразователя кодов 31 соединен с первым входом третьего преобразователя кодов 33 и вторым входом четвертого преобразователя кодов 34, а выход второго преобразователя кодов 32 - с первым входом четвертого преобразователя кодов 34 и вторым входом третьего преобразователя кодов 33. Выход третьего преобразователя кодов 33 связан с входом предварительной записи третьего счетчика 35, а выход четвертого преобразователя кодов 34 - с входом предварительной записи четвертого счетчика 38. Выход третьего счетчика 35 подключен к шине суммы двух частот 39 и входу седьмого элемента задержки 36, выход четвертого счетчика 38 - к шине разности двух частот 40 и входу восьмого элемента задержки 37. Установочный вход третьего счетчика 35 соединен с выходом седьмого элемента задержки 36, а установочный вход четвертого счетчика 38 - с выходом восьмого элемента задержки 37.

Формирователь работает следующим образом. На входы формирователей 1 и 2 поступает последовательность импульсов частот F1 и F2 соответственно. Формирователи 1 и 2 преобразуют входные импульсы частот F1 и F2, произвольные по длительности, в короткие импульсы, которые запоминаются на триггерах 3 и 4.

Рассмотрим случай, когда частота F1>F2. Очередной импульс частоты F1 будет преобразован формирователем 1 в короткий по длительности и запомнится на триггере 3. Установившееся "единичное" состояние триггера 3 разблокирует по первому входу элемент "И-НЕ" 5 и по входу сброса триггер 7. При наличии разрешающего потенциала на третьем входе элемента "И-НЕ" 5 (триггер 8 находится в нулевом состоянии) на выходе элемента "И-НЕ" 5 будет сформирован сигнал, который по входу установки переключит триггер 7 в состояние "1". Инверсный выход триггера 7 установит блокировочный потенциал на втором входе элемента "И-НЕ" 5, а также на втором входе элемента "И-НЕ" 6 для предотвращения установки в единичное состояние триггера 8 в случае появления импульса частоты F2 при единичном состоянии триггера 7. Единичное состояние триггера 7 и нулевое состояние триггера 8 не вызовут блокировки элементов "И" 12, 13, 15, 16, но сигнал с прямого выхода триггера 7, пройдя через элемент задержки 9, через элемент "И" 15 не пройдет, так как триггер 14, находясь в нулевом состоянии, заблокирует элемент "И" 15 по третьему входу. Сигналом с второго выхода элемента задержки 9 триггер 3, а затем триггер 7 установятся в нулевое состояние, а срезом этого сигнала триггер 14 через элемент "И" 12 - в единичное состояние. Следующим за импульсом частоты F1 импульс частоты F2 установит триггер 14 в нулевое состояние. Цикл установки триггера 14 в нулевое состояние импульсом частоты F2 аналогичен циклу установки триггера 14 импульсом частоты F1 в единичное состояние, включая элементы, участвующие в этом цикле. С выхода элемента "И" 15 с частотой, равной F1-F2, формируются импульсы, которые устанавливают триггер 17 в единичное состояние, означающее, что частота F1 больше частоты F2. Если же частота F2 будет больше частоты F1, то с выхода элемента "И" 13 на вход сброса триггера 17 будут поступать импульсы с частотой, равной F2-F1, которые установят триггер 17 в нулевое состояние, означающее, что частота F1 меньше частоты F2. На второй вход селектора 18 поступают импульсы F1, а на третий - импульсы частоты F2. Единичное состояние триггера 17 - случай, когда частота F1 больше частоты F2 - разрешает прохождение частоты F2 на выход селектора 18 и частоты и частоты F2 на выход селектора 20. Нулевое состояние триггера 17 - случай, когда частота F2 больше частоты F1 - также разрешает прохождение частоты F2 на выход селектора 18 и частоты F1 на выход селектора 20. Таким образом, наличие селектора 18, селектора 20 и триггера 17 с соответствующими связями обеспечивает прохождение на выход селектора 18 большей из двух частот F1 или F2(Fmax), а на выход селектора 20 - меньшей из двух частот F1 или F2 (Fmin). Очередной импульс частоты Fmax с выхода селектора 18 блокирует по второму входу элемент "И" 21, запрещая прохождение частоты генератора импульсов 19 (Fген) через элемент "И" 21 на счетный вход счетчика 25, а также, пройдя элемент задержки 22, записывает в буферный регистр 29 код количества импульсов Fген, подсчитанных счетчиком 25 за время между текущим и предыдущим импульсами Fmax. Далее этот же очередной импульс частоты Fmax, пройдя элемент задержки 26, подготавливает счетчик 25 к следующему подсчету количества импульсов Fген между текущим и следующим за ним импульсами частоты Fmax. С выхода буферного регистра 29 код (Аmax) подается на вход преобразователя кодов 31, который преобразует входной код Аmax в выходной код Bmax, равный А-1 max. Алгоритм подсчета количества импульсов частоты Fген между очередным и предыдущим импульсами частоты Fmin, преобразование его в выходной код Bmin, равный А-1 min, а также состав оборудования, необходимый для реализации этого алгоритма, аналогичны вышеописанному. На первый вход преобразователя кодов 33 поступает код Вmax, а на второй - Вmin. Код с выхода преобразователя 33 поступает на вход счетчика 35, который в совокупности с элементом задержки 36 и соответствующими связями представляет собой делитель частоты с переменным коэффициентом деления и устанавливает период повторения импульсов частоты F1+F2 на шине 39. Код с выхода преобразователя 34 поступает на вход счетчика 38, далее процесс формирования разностной частоты, равной /F1-F2/, на шине 40 аналогичен вышеописанному. Оба счетчика 35 и 38 работают в режиме вычитания.

Таким образом, введение в известное устройство дополнительных элементов с соответствующими связями обеспечивает формирование выходной частоты, равной сумме двух входных частот, и выходной частоты, равной разности этих же входных частот, с равными для каждой выходной частоты периодами повторения импульсов.

Источники информации

1. Устройство формирования разности двух частот. - А.с. № 523518 кл. Н 03 К 5/00 от 12.07.74.

2. Устройство формирования суммы, разности и знака разности двух частот. - А.с. № 1665506, кл. Н 03 К 5/156 от 30.12.88.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поиска зон информации на магнитном носителе | 1989 |

|

SU1712961A1 |

| Устройство для цифрового измерения разности частот электрических колебаний | 1977 |

|

SU739430A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЛИНЕЙНЫХ ПЕРЕМЕЩЕНИЙ В ЦИФРОВОЙ КОД | 2005 |

|

RU2298193C1 |

| СИСТЕМА ДЛЯ ШИФРАЦИИ И ДЕШИФРАЦИИ КОМАНД | 1991 |

|

RU2043699C1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| СПОСОБ ЦИФРОВОГО ИЗМЕРЕНИЯ ТЕМПЕРАТУРЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1990 |

|

RU2025044C1 |

| Измеритель разности фаз | 1990 |

|

SU1800382A1 |

| Многокоординатное устройство для управления | 1989 |

|

SU1777121A2 |

| Система радиосвязи | 1989 |

|

SU1660187A1 |

| Устройство для дифференцирования частотно-импульсных сигналов | 1985 |

|

SU1267411A1 |

Изобретение относится к импульсной технике и может быть использовано, в частности, в измерительной аппаратуре. Техническим результатом является возможность формирования суммы и разности двух входных частот с постоянными для каждой выходной частоты периодами следования импульсов. Указанный результат достигается за счет включения в формирователь двух формирователей импульсов, шести триггеров, шести элементов "И", восьми элементов задержки трех элементов "И-НЕ", двух селекторов, четырех счетчиков, двух буферных регистров, четырех преобразователей кода, генератора импульсов, шин суммы и разности двух частот. 1 ил.

Формирователь суммы, разности и знака разности двух частот, содержащий первый и второй формирователи импульсов, входы которых соединены с первой и второй входными шинами соответственно, с первого по шестой триггеры, с первого по четвертый элемент И, первый и второй элементы задержки, первый, второй и третий элементы И-НЕ, причем выход первого триггера подключен к первому входу первого элемента И-НЕ и входу сброса третьего триггера, выход второго триггера связан с первым входом второго элемента И-НЕ и входом сброса четвертого триггера, установочный вход которого подключен к выходу второго элемента И-НЕ, а установочный вход третьего триггера - к выходу первого элемента И-НЕ, инверсный выход третьего триггера соединен с объединенными между собой вторыми входами первого и второго элементов И-НЕ, а инверсный выход четвертого триггера - с объединенными между собой третьими входами первого и второго элементов И-НЕ, прямой выход третьего триггера связан с входом первого элемента задержки и первым входом третьего элемента И-НЕ, прямой выход четвертого триггера подключен к второму входу третьего элемента И-НЕ и входу второго элемента задержки, выход третьего элемента И-НЕ соединен с первыми входами первого, второго, третьего и четвертого элементов И, первый выход первого элемента задержки связан со вторым входом третьего элемента И, а первый выход второго элемента задержки подключен к второму входу четвертого элемента И, прямой выход пятого триггера соединен с третьим входом третьего элемента И, а инверсный - с третьим входом четвертого элемента И, второй выход первого элемента задержки соединен с вторым входом первого элемента И и входом сброса первого триггера, второй выход второго элемента задержки - с вторым входом второго элемента И и входом сброса второго триггера, выход первого элемента И подключен к входу сброса пятого триггера, а выход второго элемента И - к входу установки пятого триггера, выход третьего элемента И связан с входом установки шестого триггера, а выход четвертого элемента И - с входом сброса шестого триггера, отличающийся тем, что в него введены первый и второй селекторы, пятый и шестой элементы И, с третьего по восьмой элементы задержки, с первого по четвертый счетчики, генератор импульсов, первый и второй буферные регистры, с первого по четвертый преобразователи кодов, шина суммы и шина разности двух частот, причем шина суммы двух частот связана с выходом третьего счетчика и входом седьмого элемента задержки, выход которого подключен к установочному входу третьего счетчика, счетный вход последнего соединен с счетным входом четвертого счетчика, первыми входами пятого и шестого элементов И, и выходом генератора импульсов, шина разности двух частот связана с выходом четвертого счетчика и входом восьмого элемента задержки, выход которого подключен к установочному входу четвертого счетчика, соединенного входом предварительной записи с выходом четвертого преобразователя кодов, вход предварительной записи третьего счетчика связан с выходом третьего преобразователя кодов, первый кодовый вход которого подключен к второму кодовому входу четвертого преобразователя кодов и выходу первого преобразователя кодов, первый кодовый вход четвертого преобразователя кодов соединен с вторым кодовым входом третьего преобразователя кодов и выходом второго преобразователя кодов, связанного своим входом с выходом второго буферного регистра, кодовый вход последнего подключен к выходу второго счетчика, а установочный вход - к выходу четвертого элемента задержки и входу шестого элемента задержки, выход которого соединен с установочным входом второго счетчика, вход первого преобразователя кодов связан с выходом первого буферного регистра, кодовый вход которого подключен к выходу первого счетчика, а установочный - к выходу третьего элемента задержки, связанного с входом пятого элемента задержки, выход последнего соединен с установочным входом первого счетчика, счетный вход первого счетчика подключен к выходу пятого элемента И, второй вход пятого элемента И связан с входом третьего элемента задержки и выходом первого селектора, выход второго селектора подключен к входу четвертого элемента задержки и второму входу шестого элемента И, первый вход первого селектора связан с прямым входом шестого триггера и выходной шиной знака разности двух частот, а первый вход второго селектора - с инверсным выходом шестого триггера, вторые входы первого и второго селекторов связаны между собой и соединены с выходом первого формирователя импульсов и установочным входом первого триггера, выход второго формирователя импульсов подключен к третьим входам первого и второго селекторов и установочному входу второго триггера.

| Устройство формирования суммы, разности и знака разности двух частот | 1988 |

|

SU1665506A1 |

| Способ формирования сигналов суммарной и разностной частот | 1982 |

|

SU1100724A1 |

| Устройство для формирования импульсов разностной частоты | 1974 |

|

SU523518A1 |

| Устройство для определения знака и выделения сигналов разности и суммы частот | 1977 |

|

SU741179A1 |

Авторы

Даты

2005-10-20—Публикация

2002-11-15—Подача