ON О О

00 VJ

Изобретение относится к радиосвязи и можеТ быть использовано для связи центральной и периферийных станций по каналу с временным разделением.

Целью изобретения является повышение эффективности использования пропускной способности канала связи,

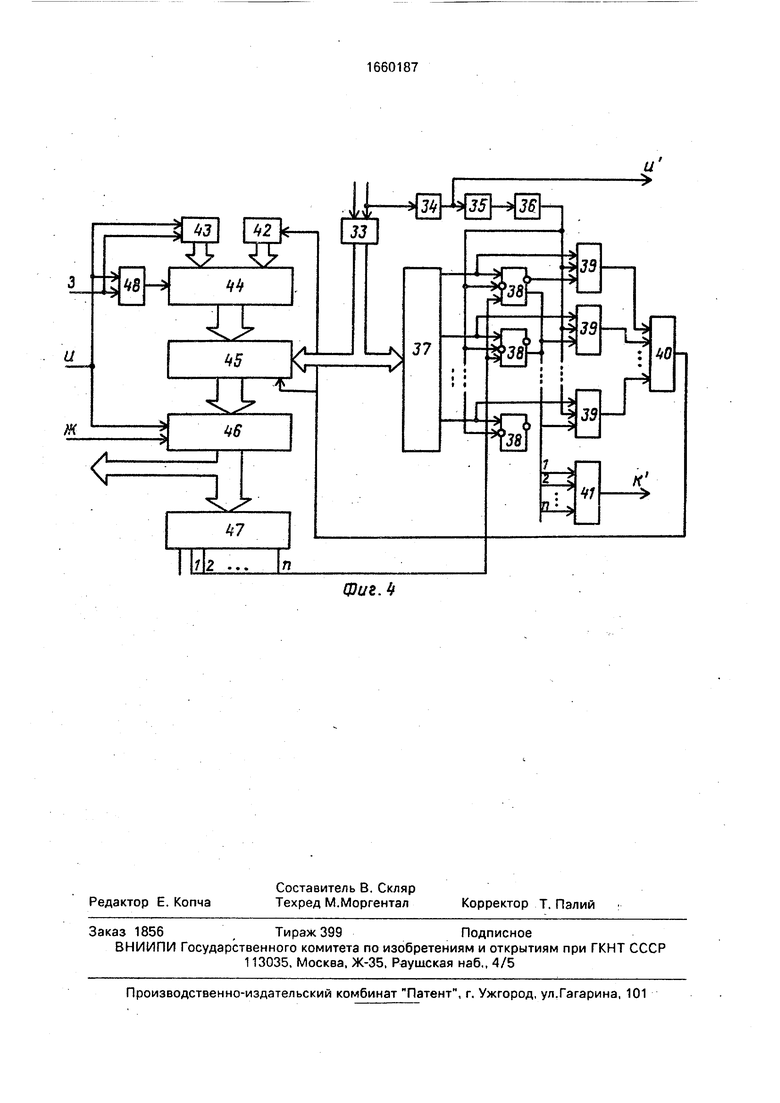

На фиг. 1 изображена структурная электрическая схема центральной станции; на фиг. 2 - структурная электрическая схема периферийной станции; на фиг, 3 - структурная электрическая схема блока управпе- ния центральной станции; на фиг, 4 - структурная электрическая схема блока памяти номеров станций на центральной станции.

Центральная станция содержит (фиг. 1) первый 1 и второй 2 приемники, блок 3 памяти номеров станций, блок 4 управления, блок 5 выделения и формирования информации, селектор 6 кода адреса, формирователь 7 синхросигнала, формирователь 8 кода адреса, передатчик 9, первый 10 и второй 11 ключи, элемент ИЛИ 12.

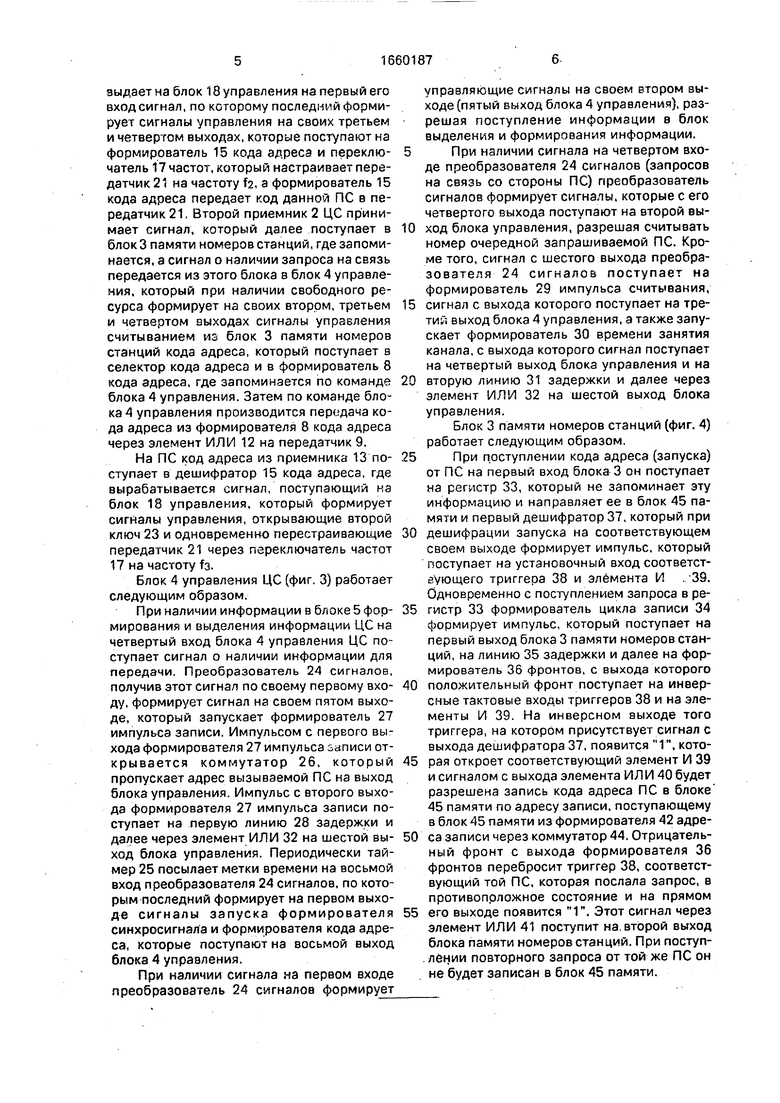

Периферийная станция содержит (фиг. 2) приемник 13, дешифратор 14 синхросигнала, дешифратор 15 кода адреса, таймер 16, переключатель 17 частот, блок 18 управления, формирователь 19 кода адреса, блок 20 выделения и формирования информации, передатчик 21, первый 22 и второй 23 ключи.

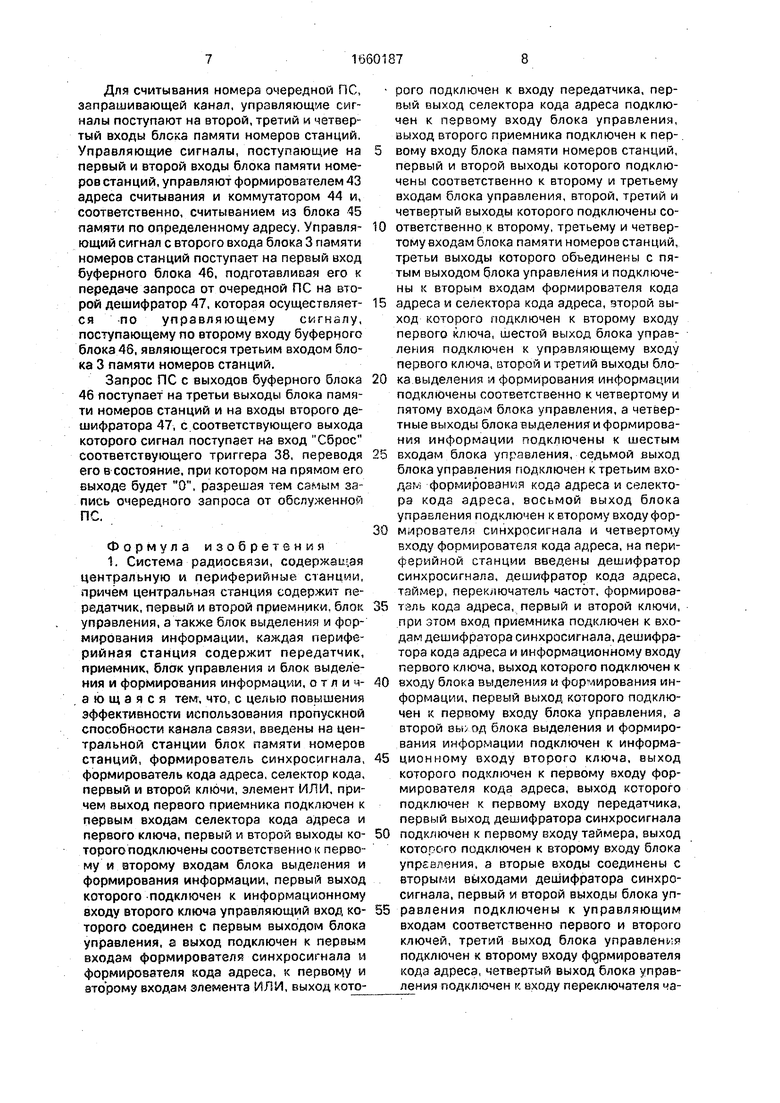

Блок 4 управления центральной станции (фиг. 3) содержит преобразователь 24 сигналов, таймер 25, коммутатор 26, формирователь 27 импульса записи, первую линию 28 задержки, формирователь 29 импульса считывания, формирователь 30 времени занятия канала, вторую линию 31 задержки, элемент ИЛИ 32.

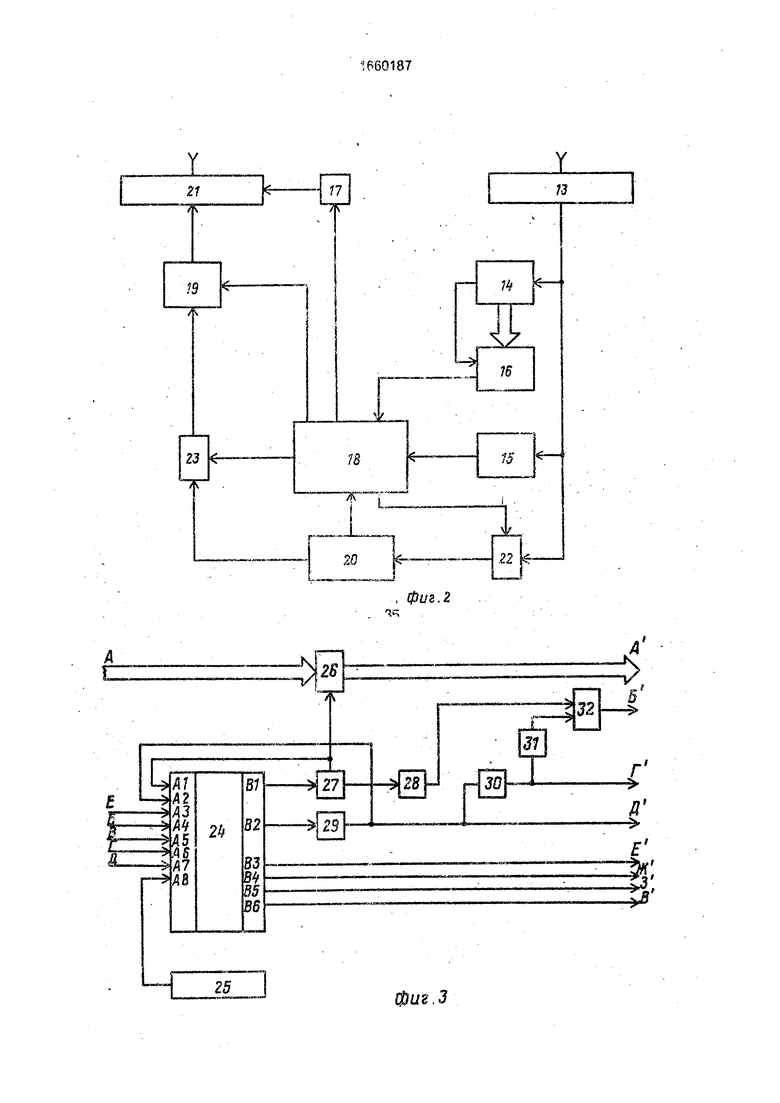

Блок 3 памяти номеров станций содержит (фиг. 4) регистр 33, формирователь 34 цикла записи, линию 35 задержки, формирователь 36 фронтов, первый дешифратор 37, N триггеров 38, N элементов И 39, первый 40 и второй 41 элементы ИЛИ, формирователь 42 адреса записи, формирователь 43 адреса считывания, коммутатор 44, блок 45 памяти, буферный блок 46, второй дешифратор 47, элемент ИЛИ-НЕ 48.

Система радиосвязи работает следующим образом.

Передача информации с центральной станции (ЦС) на периферийную производится на частоте fi, прием запроса не ЦС с периферийной станции (ПС) производится на частоте fa, а прием информации на ЦС производится на частоте Ь.

При наличии на ЦС информации для передачи на ПС блок 5 выделения и формиро вания информации на своем втором выходе формирует сигнал, который поступает на четвертый вход блока 4 управления. Одновременно блок выделения и формирования

информации на своих четвертых выходах формирует адрес вызываемой станции, который поступает на шестые входы блока 4 управления. Последний транслирует этот адрес на селектор кода адреса и на форми0 рователь кода адреса, где по сигналу с седьмого выхода блока 4 управления этот адрес запоминается и передается в канал связи.

В промежутках между передачей кода адреса вызываемой ПС по сигналу блока 4

5 управления формирователь 7 синхросигнала формирует синхросигналы и передает их «ерез элемент ИЛИ 12 на передатчик.

Таким образом, все приемники 13 ПС принимают синхросигналы и код адреса од0 ной из ПС. Синхросигналы дешифрируются на дешифраторе 14 синхросигнала каждой ПС, которые формируют сигналы для подстройки таймера 16. Код адреса дешифрируется дешифратором 15 кода адреса, сигнал

5 с которого поступаете блок 18 управления, где формируются управляющие сигналы, поступающие на входы формирователя 19 кода адреса, переключателя 17 частот, первый 22 и второй 23 ключи. При этом передат0 чик 21 ПС настраивается на частоту fa, формирователь 19 кода адреса начинает формировать и передавать в передатчик 21 код адреса данной ПС, первый 22 и второй 23 ключи открываются, давая возможность

5 блоку выделения и формирования информа- . ции 20 принимать и передавать информацию,

Приемник 1 центральной станции принимает код адреса запрашиваемой станции

0 и направляет его на первый вход первого ключа 10 и селектор 6 кода адреса, который сверяет принятый и переданный адреса и при совпадении их выдает на первый вход блока 4 управления сигнал. По этому сигна5 лу блок управления открывает второй ключ 11 и информация с блока выделения и формирования информации через формирователь 8 кода адреса и элемент ИЛИ 12 поступает на передатчик 9. Одновременно

0 селектор б кода адреса передает код адреса ПС на второй вход первого ключа 10, а блок 4 управления открывает его, пропуская информацию в блок 5 выделения и формирования информации.

5 На ПС информация ЦС с приемника 13 через открытый первый ключ 22 поступает в блок 20 выделения и формирования информации. Если периферийная станция имеет информацию для передачи на ЦС, то ее блок 20 выделения и формирования информации

выдает на блок 18 управления на первый его вход сигнал, по которому последний формирует сигналы управления на своих третьем и четвертом выходах, которые поступают на формирователь 15 кода адреса и переклю- чатель 17 частот, который настраивает передатчик 21 на частоту f2, а формирователь 15 кода адреса передает код данной ПС в передатчик 21, Второй приемник 2 ЦС принимает сигнал, который далее поступает в блок 3 памяти номеров станций, где запоминается, а сигнал о наличии запроса на связь передается из этого блока в блок 4 управления, который при наличии свободного ресурса формирует на своих втором, третьем и четвертом выходах сигналы управления считыванием из блок 3 памяти номеров станций кода адреса, который поступает в селектор кода адреса и в формирователь 8 кода адреса, где запоминается по команде блока 4 управления. Затем по команде блока 4 управления производится передача кода адреса из формирователя 8 кода адреса через элемент ИЛИ 12 на передатчик 9.

На ПС код адреса из приемника 13 по- ступает в дешифратор 15 кода адреса, где вырабатывается сигнал, поступающий на блок 18 управления, который формирует сигналы управления, открывающие второй ключ 23 и одновременно перестраивающие передатчик 21 через переключатель частот 17 на частоту fa.

Блок 4 управления ЦС (фиг. 3) работает следующим образом.

При наличии информации в блоке 5 фор- мирования и выделения информации ЦС на четвертый вход блока 4 управления ЦС поступает сигнал о наличии информации для передачи. Преобразователь 24 сигналов, получив этот сигнал по своему первому вхо- ду, формирует сигнал на своем пятом выходе, который запускает формирователь 27 импульса записи. Импульсом с первого выхода формирователя 27 импульса записи от- крывается коммутатор 26, который пропускает адрес вызываемой ПС на выход блока управления. Импульс с второго выхода формирователя 27 импульса записи поступает на первую линию 28 задержки и далее через элемент ИЛИ 32 на шестой вы- ход блока управления. Периодически таймер 25 посылает метки времени на восьмой вход преобразователя 24 сигналов, по которым последний формирует на первом выходе сигналы запуска формирователя синхросигнала и формирователя кода адреса, которые поступают на восьмой выход блока 4 управления.

При наличии сигнала на первом входе преобразователь 24 сигналов формирует

управляющие сигналы на своем втором выходе (пятый выход блока 4 управления), разрешая поступление информации в блок выделения и формирования информации.

При наличии сигнала на четвертом входе преобразователя 24 сигналов (запросов на связь со стороны ПС) преобразователь сигналов формирует сигналы, которые с его четвертого выхода поступают на второй выход блока управления, разрешая считывать номер очередной запрашиваемой ПС. Кроме того, сигнал с шестого выхода преобразователя 24 сигналов поступает на формирователь 29 импульса считывания, сигнал с выхода которого поступает на третий выход блока 4 управления, а также запускает формирователь 30 времени занятия канала, с выхода которого сигнал поступает на четвертый выход блока управления и на вторую линию 31 задержки и далее через элемент ИЛИ 32 на шестой выход блока управления.

Блок 3 памяти номеров станций (фиг. 4) работает следующим образом.

При поступлении кода адреса (запуска) от ПС на первый вход блока 3 он поступает на регистр 33, который не запоминает эту информацию и направляет ее в блок 45 памяти и первый дешифратор 37, который при дешифрации запуска на соответствующем своем выходе формирует импульс, который поступает на установочный вход соответствующего триггера 38 и элемента И 39. Одновременно с поступлением запроса в регистр 33 формирователь цикла записи 34 формирует импульс, который поступает на первый выход блока 3 памяти номеров станций, на линию 35 задержки и далее на формирователь 36 фронтов, с выхода которого положительный фронт поступает на инверсные тактовые входы триггеров 38 и на элементы И 39. На инверсном выходе того триггера, на котором присутствует сигнал с выхода дешифратора 37, появится 1, которая откроет соответствующий элемент И 39 и сигналом с выхода элемента ИЛИ 40 будет разрешена запись кода адреса ПС в блоке 45 памяти по адресу записи, поступающему в блок 45 памяти из формирователя 42 адреса записи через коммутатор 44, Отрицательный фронт с выхода формирователя 36 фронтов перебросит триггер 38, соответствующий той ПС, которая послала запрос, в противопрложное состояние и на прямом его выходе появится 1. Этот сигнал через элемент ИЛИ 41 поступит на второй выход блока памяти номеров станций. При поступлении повторного запроса от той же ПС он не будет записан в блок 45 памяти.

Для считывания номера очередной ПС, запрашивающей канал, управляющие сигналы поступают на второй, третий и четвертый входы блока памяти номеров станций. Управляющие сигналы, поступающие на первый и второй входы блока памяти номеров станций, управляют формирователем 43 адреса считывания и коммутатором 44 и, соответственно, считыванием из блока 45 памяти по определенному адресу. Управляющий сигнал с второго входа блока 3 памяти номеров станций поступает на первый вход буферного блока 46, подготавливая его к передаче запроса от очередной ПС на второй дешифратор 47, которая осуществляется по управляющему сигналу, поступающему по второму входу буферного блока 46, являющегося третьим входом блока 3 памяти номеров станций.

Запрос ПС с выходов буферного блока 46 поступает на третьи выходы блока памяти номеров станций и на входы второго дешифратора 47, с соответствующего выхода которого сигнал поступает на вход Сброс соответствующего триггера 38, переводя его в состояние, при котором на прямом его выходе будет О, разрешая тем самым запись очередного запроса от обслуженной ПС.

Формула изобретения 1. Система радиосвязи, содержащая центральную и периферийные станции, причём центральная станция содержит передатчик, первый и второй приемники, блок управления, а также блок выделения и формирования информации, каждая периферийная станция содержит передатчик, приемник, блок управления и блок выделения и формирования информации, о т л и ч- , а ю щ а я с я тем, что, с целью повышения эффективности использования пропускной способности канала связи, введены на центральной станции блок памяти номеров станций, формирователь синхросигнала, формирователь кода адреса, селектор кода, первый и второй ключи, элемент ИЛИ, причем выход первого приемника подключен к первым входам селектора кода адреса и первого ключа, первый и второй выходы которого подключены соответственно к первому и второму входам блока выделения и формирования информации, первый выход которого подключен к информационному входу второго ключа управляющий вход которого соединен с первым выходом блока управления, в выход подключен к первым входам формирователя синхросигнала и формирователя кода адреса, к первому м второму входам элемента ИЛИ, выход кото рого подключен к входу передатчика, первый выход селектора кода адреса подключен к первому входу блока управления, выход второго приемника подключен к первому входу блока памяти номеров станций, первый и второй выходы которого подключены соответственно к второму и третьему входам блока управления, второй, третий и четвертый выходы которого подключены со0 ответственно к второму, третьему и четвертому входам блока памяти номеров станций, третьи выходы которого объединены с пятым выходом блока управления и подключены к вторым входам формирователя кода

5 адреса и селектора кода адреса, второй выход которого подключен к второму входу первого ключа, шестой выход блока управления подключен к управляющему входу первого ключа, оторой и третий выходы бло0 ка выделения л формирования информации подключены соответственно к четвертому и пятому входам блока управления, а четвертные выходы блока выделения и формирования информации подключены к шестым

5 входам блока управления, седьмой выход блока управления подключен к третьим входам формирования кода адреса и селектора кода адреса, восьмой выход блока управления подключен к второму входу фор0 млрователя синхросигнала и четвертому входу формирователя кода адреса, на периферийной станции введены дешифратор синхросигнала, дешифратор кода адреса, таймер, переключатель частот, формироеа5 тзль кода адреса, первый и второй ключи, при зтом вход приемника подключен к входам дешифратора синхросигнала, дешифратора кода адреса и информационному входу первого ключа, выход которого подключен к

0 входу блока выделения и формирования информации, первый выход которого подключен к первому входу блока управления, а второй вы; од блока выделения и формирования информации подключен к информа5 ционному входу второго ключа, выход которого подключен к первому входу формирователя кода адреса, выход которого подключен к первому входу передатчика, первый выход дешифратора синхросигнала

0 подключен к первому входу таймера, выход которого подключен к второму входу блока упргвления, а вторые входы соединены с вторыми выходами дешифратора синхросигнала, первый и второй выходы блока уп5 равления подключены к управляющим входам соответственно первого и второго ключей, третий выход блока управления подключен к второму входу формирователя кода адреса, четвертый выход блока управления подключен к. входу переключателя частот, выход которого подключен к второму входу передатчика, выход дешио) -;атора кеда адреса подключен к третьему входу блока управления.

2.Система по л, 1,от л имеющаяся тем.что блок управления центральной станции содержит коммутатор, преобразователь сигналов, формирователь импульса записи, формирователь импульса считывания первую и вторую линии задержки, фор- мирователь времени занятия канала, элемент ИЛИ, таймер, причем шестые входы блока управления являются сигнальными входами коммутатора, выходы коммутатора являются пятыми выходами блока управления, пеовым, второй, третий, четвертый и пятый входы преобразователя сигналов являются соответственно первым, вторым, третьим, четвертым и пятым входами блока управления, первый, второй, третий и четвертый выходы преобразователя сигналов являются соответственно червым, вторым, шестым и восьмым выходами блока управления, пятый выход преобразователя сигналов подключен к входу формирователя импульса записи, первый ьыход которого подключен к управляющему входу коммутатора и шестому входу преобразователя сигналов, а второй выход формирователя импульса записи подключен к входу первой линии задержки, выход которой подключен к первому входу элемента ИЛИ, выход которой является седьмым выходом блока управления, шестой выход преобразователя сигналов подключен к входу формирователя импульса считывания, выход которого подключен к седьмому входу преобразователя сигналов, к входу формирователя времени занятия канала и является третьим выходом блока управления, выход формирователя времени занятия канала подключен к входу второй линии задержки и является четвертым выходом блока управления, выход второй линии задержки подключен к второму входу элемента ИЛИ, выход таймера подключен к восьмому входу преобразователя сигналов.

3.Система поп, 1,отличающаяся тем, что блок памяти номеров станций на центральной станции содержит резистор, первый и второй дешифраторы, формирователь ш/жла записи, линию задержки, формирователь фронтов, N триггеров, N

элементов И, перво й и второй элементы ИЛИ, формирователь адреса считывания, формирователь адреса записи, комм/татор, блок памяти, буферный блок, элемент ИЛ И- НЕ, причем обьединенные входы регистра и формирователя цикла записи являются первым входом блока памяти номеров станций, выход формирователя цикла записи подключен к входу линии задержки и является

первым выходом блока памяти номеров станций, выход линии задержки подключен к входу формирователя фронтов, выход которого подключен к инверсным тактируемым входам триггеров и первым входам

элементов И, N выходов первого дешифратора подключены соответственно к установочным S входам N триггеров, вторым входам N элементов И, выходы которых подключены соответственно к N входам первого элемента ИЛИ, выход которого подключен к входу формирователя адреса записи и управляющему входу блока памяти, выходы которого подключены к информационным входам буферного блока,

выходы которого являются третьими выходами блока памяти номеров станций и подключены к входам второго дешифратора, N выходов которого подкпючены соответственно к входам Сброс N триггеров, инверсные выходы которых подключены соответственно к третьим входам N элемен- пэв И, а прямые выходы триггеров подклю- 1ены соответственно к N входам второго элемент ИЛИ, выход которого является

вторым выходом блока памяти номеров станций, выходы регистра подключены к входам первого дешифратора и к информационным входам блока памяти, адресные входы которого соединены с соответствующими выходами коммутатора, выход формирователя адреса записи подключен к первому входу коммутатора, второй вход которого соединен с выходом формирователя адреса считывания, второй вход блока памяти номеров станций является первым входом формирователя адреса считывания,, первым входом элемента ИЛИ-НЕ и первым входом буферного блока, третий вход блока памяти номеров станции является

вторым входом буферного блока, а четвертый вход блока памяти номеров станций является вторым входом элемента ИЛИ-НЕ и вторым входом формирователя адреса считывания.

/81099I

Фиг. 4

| название | год | авторы | номер документа |

|---|---|---|---|

| СПУТНИКОВАЯ СИСТЕМА СВЯЗИ "КИБОЛ" | 1992 |

|

RU2033693C1 |

| Система телемеханики | 1982 |

|

SU1152015A1 |

| Способ централизованного контроля телетрафика и состояния оборудования автоматической телефонной станции и система для его осуществления | 1979 |

|

SU902307A1 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| Устройство для сопряжения каналов ввода-вывода с устройством управления оперативной памятью | 1984 |

|

SU1265788A1 |

| Устройство для приема и передачи данных | 1988 |

|

SU1596478A1 |

| УСТРОЙСТВО ПОИСКА СИГНАЛА СИНХРОНИЗАЦИИ СПУТНИКОВОЙ СИСТЕМЫ СВЯЗИ | 1995 |

|

RU2093963C1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММИРОВАНИЯ МИКРОСХЕМ ПОСТОЯННОЙ ПАМЯТИ | 1990 |

|

RU2047918C1 |

| Адаптивное устройство для обучения языкам | 1987 |

|

SU1441445A1 |

Изобретение относится к радиосвязи и может быть использовано для связи центральной и периферийной станций с временным разделением канала. Целью изобретения является повышение эффективности использования пропускной способности канала связи. Центральная станция содержит приемники 1 и 2, блок 3 памяти номеров станций, блок 4 управления, блок 5 выделения и формирования информации, селектор 6 кода адреса, формирователь 7 синхросигнала, формирователь 8 кода адреса, передатчик 9, ключи 10 и 11 и элемент ИЛИ 12. Периферийная станция содержит приемник, дешифратор синхросигнала, дешифратор кода адреса, таймер, переключатель частот, блок управления, формирователь кода адреса, блок выделения и формирования информации, передатчик и ключи. Цель изобретения достигается тем, что центральная станция, принимая запросы периферийных станций на отдельной частоте, организует в блоке 3 памяти номеров станций очередь запросов на обслуживание, которые при наличии временного ресурса обслуживаются блоком 4 управления. 2 з.п.ф-лы, 4 ил.

| Система радиосвязи | 1978 |

|

SU734886A1 |

| кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-06-30—Публикация

1989-01-18—Подача