Данное изобретение относится к ИМС с подложкой, которая имеет схемные элементы и плоскость монтажа с первыми проводящими дорожками, а также к способу изготовления ИМС.

В случае интегральных схем, особенно при их использовании в чип-картах, у потенциального злоумышленника имеется возможность провести анализ интегральной схемы так называемым «обратным проектированием» и с использованием полученной информации изменить режим работы схемы или осуществить манипулирование данными в запоминающем устройстве. Этот способ может привести к нежелательным последствиям, особенно в случае схем, для которых важна защищенность, например, с функциями платежных карт или обеспечения права доступа. При таком анализе в типовом случае удаляется материал, покрывающий чип, а также часть верхних слоев, защищающих разводку чипа. В случае открытых верхних проводящих дорожек речь идет, чаще всего, о проводниках, для которых не важна защищенность, которые можно обойти посредством так называемых «шунтирующих проводников», чтобы далее достичь более глубоких слоев и проводников. В настоящее время такой анализ может проводиться с некоторыми затратами так называемым «FIB-методом» («фокусированным пучком ионов»). Как только достигнуты расположенные глубже проводники, для которых важна защищенность и которые являются поэтому критическими проводниками, с них может быть осуществлен съем сигналов импульсов (так называемое «зондирование») или эти проводники могут быть нагружены сигналами для манипулирования данными (так называемое «подавление»).

По этой причине в прошлом ставилась цель предотвратить или, по меньшей мере, осложнить анализ интегральных схем и манипуляцию ими, которую пытались достичь, с одной стороны, посредством скрытой топологии формирования критических проводников в плоскости монтажа, а с другой стороны, нанесением специальной, прикрывающей, защитной плоскости над критическими с точки зрения защиты плоскостями монтажа. В случае этих защитных плоскостей («защитных экранов») реализуются проводники в форме меандра или решетки, например, парами в защитной плоскости, при их прерывании или коротком замыкании для случая приложения различных напряжений обнаруживающий это состояние датчик вызывает стирание памяти, сброс или неисправное состояние других частей микросхемы. Также возможно выполнение этих называемых «пассивными» проводников в виде неподключенных без напряжения. В этом случае они служат только для увеличения затрат при попытках взлома (несанкционированного доступа) или для помех.

Защищенность микросхем можно повысить, заменяя описанные «пассивные» проводники так называемыми «активными» проводниками при проектировании плоскости монтажа. В этом случае проводники экрана посредством схемы управления нагружаются сигналами, которые анализируются схемой анализа данных и, например, сравниваются с опорными сигналами. Из-за возможных вариаций сигналов защитный экран можно обойти только за счет требующей очень высоких затрат прокладки шунтирующего проводника FIB-методом.

В то время как интегральные схемы обычных логических элементов разрабатываются в основном в условиях управляемого вручную проектирования (полностью заказные конструкции), ручная обработка или воздействие в условиях интенсивно развивающейся синтезированной логики могут быть реализованы только с высокими затратами. При этом методе функции и связи объектов описываются на языке программирования высокого уровня, например VHDL, и через компилятор переводятся в готовую схему монтажа. Так как защитные свойства проводников экрана вытекают из функций, не зависимых от самой схемы, и из их пространственного положения, но они не могут быть предварительно установлены при этом способе синтеза, то в этом способе, к сожалению, только потом схема монтажа может дополняться вручную с соответствующими затратами на защитные плоскости, что противоречит желаемым преимуществам по эффективности и времени при разработке интегральной схемы.

При этом интегральные схемы, разработанные способом синтеза, могут быть особенно уязвимыми по отношению к возможным атакам, так как основной монтаж осуществляется в более глубоких слоях, в то время как в верхних слоях степень заполнения проводниками становится все меньшей. На основании этого, потенциальный злоумышленник может, не касаясь проводников, расположенных в верхних плоскостях разводки, например из точечной измерительной позиции, иглой добраться прямо до глубоколежащих проводников, критических с точки зрения защищенности.

Задача данного изобретения состоит в создании ИМС и способа ее изготовления, которые обеспечивают высокую защиту против действующего извне способа анализа при низких затратах и незначительной стоимости, особенно для случая, когда монтажная схема разработана способом синтеза.

Задача решается согласно изобретению посредством признаков, раскрытых в пунктах 1 и 6 формулы изобретения.

Этажерочная конструкция микросхемы, которая позволяет предотвратить возможность анализа за счет проводящих дорожек, известна из WO 00/67319 A1.

Согласно данному изобретению предлагается интегральная микросхема, в которой благодаря заполнению областей, свободных от проводящих дорожек, поддерживающих соответствующую назначению функцию интегральных микросхем, служащими для защиты интегральной схемы проводящими дорожками, для каждой плоскости обеспечивается максимальная степень заполнения проводящими дорожками.

Во-первых, тем самым для потенциального злоумышленника при обратном проектировании увеличивается число исследуемых дорожек, приходящееся на плоскость разводки, а во-вторых, для потенциального злоумышленника заранее невозможно установить, какие проводящие дорожки в плоскости разводки служат собственно для интегральной схемы, а какие - только для защиты этой схемы. Таким образом, возникает преимущество, состоящее в том, что заполнение и общее позиционирование обоих размещений проводящих дорожек в плоскости разводки приводит к значительно более высоким затратам при обратном проектировании.

Согласно изобретению интегральная микросхема может содержать подложку с активными элементами схемы, а также интегральные схемы, применяемые в качестве «перевернутого кристалла» без активных элементов схемы, причем последние обычно структурированной стороной приклеиваются к структурированной стороне подложки, содержащей активные элементы схемы. Совместно они составляют соответствующую изобретению микросхему.

Необходимо сослаться на то, что в этом документе согласно заявленному изобретению понятие элементов схемы охватывает также проводящие дорожки. Согласно изобретению интегральная микросхема может находить также применение, например, в упомянутых перевернутых кристаллах, содержащих лишь проводящие дорожки, которые соответственно этому могут служить в качестве расширенной защиты для кристалла, содержащего в себе активные элементы схемы.

Особенно выгодным оказывается способ изготовления устройства согласно данному изобретению для разработанных способом синтеза интегральных схем. Не перекрытые в способе синтеза проводящими дорожками в верхних плоскостях разводки и поэтому свободные и глубже лежащие критические проводящие дорожки можно накрыть после окончания способа синтеза согласно данному изобретению за счет заполнения свободных областей, расположенных над соответствующей проводящей дорожкой, служащими для защиты интегральной схемы проводящими дорожками. Возможное применение данного изобретения перед или во время способа синтеза должно учитывать сказанное выше. Преимущественно устройство и способ согласно данному изобретению реализуются посредством вычислительной программы заполнения, которая идеально сопрягается со способом синтеза. Кроме преимущества в скорости, тем самым обеспечивается возможность того, что благодаря созданию новой модульной версии с изменениями в монтажной схеме интегральной схемы, также создается совершенно новая монтажная схема защитными проводниками. Таким образом, анализ методом обратного проектирования связан не просто с исследованием малых изменений от одной модульной версии до следующей, а такой анализ должен проводиться полностью заново с высокими затратами.

Так как в предлагаемой интегральной микросхеме не предусмотрены специально предназначенные плоскости для защитных проводящих дорожек, потому что соответствующие проводящие дорожки находятся в плоскостях, в которых уже произведен электрический монтаж, не возникают дополнительные затраты на конструирование плоскостей металлизации. Это экономическое преимущество может быть получено и при проектировании специализированных интегральных схем, если соответствующие защитные проводящие дорожки заполняют свободные области составленных вручную библиотечных модулей или проводящих дорожек и проводников питания при отказе от обычно используемой защитной специально предназначенной плоскости.

Другой аспект выражает возможную многослойность областей с проводящими дорожками для защиты интегральной схемы. Кроме повышения затрат, обусловленного многослойностью, это позволяет комбинировать различные защитные механизмы, как, например, емкостные сенсорные проводники в первой плоскости с сигнальными и сенсорными проводниками, снабженными компараторами, во второй плоскости, которые предпочтительным образом существенно затрудняют последовательное удаление плоскостей и исследование проводящих дорожек.

Дальнейшие предпочтительные варианты осуществления следуют из зависимых пунктов формулы изобретения.

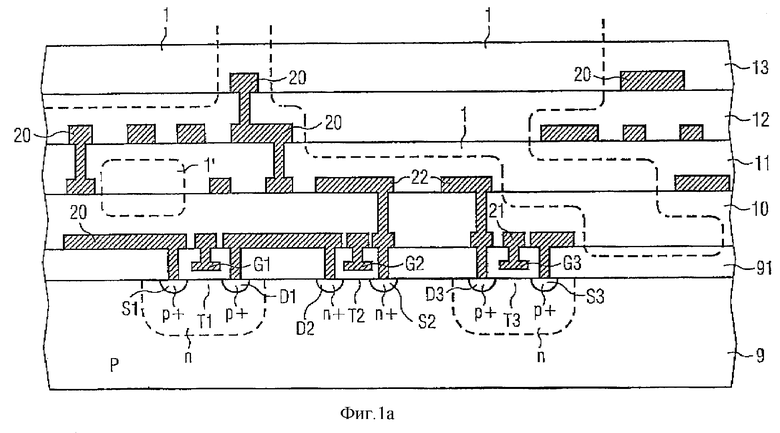

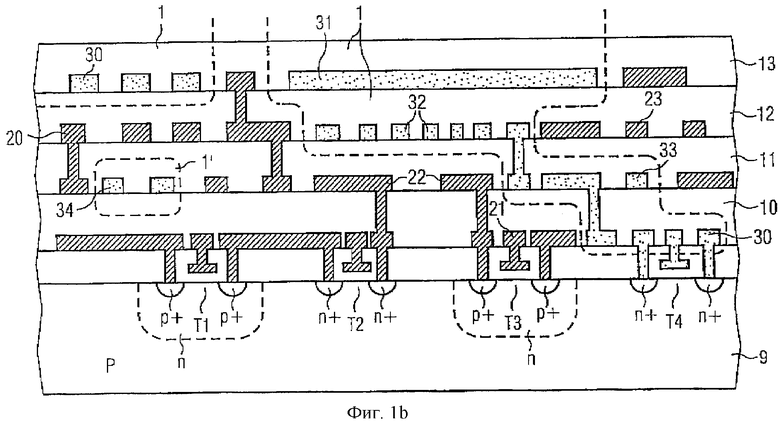

Изобретение объясняется более подробно ниже, на примере осуществления. При этом на фиг.1 представлен поперечный разрез приведенной для примера полученной способом синтеза микросхемы с транзисторами и проводящими дорожками в четырех плоскостях металлизации (а), т.е. согласно уровню техники; и (b) после заполнения, т.е. после применения соответствующего изобретению способа изготовления микросхемы.

На фиг.1а показана разработанная способом синтеза монтажная схема интегральной микросхемы, соответствующая уровню техники. В изображенном поперечном разрезе приведенного для примера устройства на подложке 9 изображены три транзистора Т1, Т2 и Т3, из них транзисторы Т1 и Т2 представляют КМОП (комплементарная структура металл-окисел-полупроводник)-инвертор. В расположенном на подложке изолированном слое 91 находятся соответствующие управляющие электроды (затворы)G1-G3, а также металлические контакты к областям истока S1-S3 и областям стока D1-D3 трех транзисторов. На этом слое находится первая плоскость 10 металлизации с расположенным на ней изолированным слоем с проводящими дорожками 20, служащими для соединений компонентов. Вследствие пересечений проводящих дорожек 20 эти проводящие дорожки должны отводиться также в вышележащие плоскости 11, 12 и 13 металлизации, разделенные посредством изоляционных слоев друг от друга, причем обычно в самых верхних слоях металлизации прокладываются шины питания. VHDL-программный код, отображающий зависимости и режимы работы соответствующих компонентов, транслируется посредством компилятора, посредством чего возникает оптимизированная монтажная схема, например, обеспечивающая максимально короткие пути монтажа. Тем самым самый нижний слой 10 металлизации сильнее всего заполняется проводящими дорожками, в то время как эта степень заполнения сильнее убывает по направлению к верхним слоям металлизации. Таким путем в монтажной схеме создаются расширяющиеся по направлению к верхним слоям металлизации свободные от проводящих дорожек области 1, 1', причем могут возникать далее не используемые компилятором свободные области 1', которые окружены проводящими дорожками.

Согласно этой микросхеме для потенциального злоумышленника было бы возможно, с целью несанкционированного доступа, после удаления изоляционных слоев между слоями 10-13 металлизации достичь, например, иглами проводящих дорожек 21 транзистора Т3, критичных с точки зрения защиты, расположенных в первом слое 10 металлизации или еще проводящих дорожек 22 транзисторов Т2, Т3, расположенных во втором слое 11 металлизации, для осуществления таких действий, как вышеупомянутое «зондирование» или «подавление».

Согласно способу, лежащему в основе данного изобретения, для изготовления интегральной микросхемы области 1, оставленные свободными, например, в способе синтеза от проводящих дорожек, заполняются другими проводящими дорожками 30, служащими защите интегральной схемы. Это можно осуществлять вручную, но в идеале должно реализовываться посредством вычислительной программы заполнения, которая обнаруживает свободные области и заполняет их проводящими дорожками при сохранении заданных защитных функций. Возможно, что еще свободные области на подложке могут также использоваться для компонентов сенсорных линий таких, как показанный на фиг.1b транзистор Т4. Проводящие дорожки 30, служащие в качестве сенсорных линий, заполняют при этом свободные области 1 по возможности плотно, чтобы уже за счет их расположения препятствовать доступу посредством игл из точечной измерительной позиции или посредством «FIB-метода» к критическим проводящим дорожкам 21, 22. За счет нагружения проводящих дорожек 30 сигналами посредством устройств управления или анализа данных, содержащих, например, транзисторы Т4, при помощи сравнения с опорным сигналом может проверяться целостность проводящих дорожек 30 в отношении короткого замыкания или шунтирования. При неравенстве сигналов устройством анализа данных обеспечивается, например, сброс или стирание памяти интегральной схемы.

Потенциальная попытка несанкционированного доступа особенно затрудняется за счет решетчатой или меандровой формы выполнения проводящих дорожек 31, 32. Если при этом ориентация проводящих дорожек 31 в слое 13 металлизации выбирается перпендикулярной проводящим дорожкам, позиционированным в нижерасположенном слое металлизации 12, то для потенциального злоумышленника становится особенно трудным достичь расположенных под ними проводников, так как в этом случае посредством создания отверстия, через которое с помощью иглы или методом FIB нужно достичь проводящей дорожки 22, должно прерываться очень много расположенных над ней проводящих дорожек 31 слоя 13 металлизации и проводящих дорожек 32 слоя 12 металлизации, которые в этом случае потенциальный злоумышленник должен отдельно исследовать или шунтировать.

Дополнительное преимущество обеспечивается благодаря проверке проводящих дорожек интегральной схемы, расположенных в верхних слоях металлизации, посредством ниже расположенных защитных проводящих дорожек. На фиг.1b это представлено посредством проводящей дорожки 23 слоя 12 металлизации, под которой параллельно проходит проводящая дорожка 33 значительной протяженности. За счет обнаружения разрыва проводящей дорожки 33 можно при этом сразу же сделать вывод об одновременном разрыве проводящей дорожки 23 или о попытке несанкционированного доступа, благодаря чему посредством логики анализа данных можно обеспечить изменение режима работы интегральной схемы.

Также для случая, когда освобожденные области 1' не могут достигаться посредством устройства управления или анализа данных, предоставляется возможность предусмотреть свободные от подключения проводящие дорожки 34, служащие только для внесения «путаницы». Кроме того, благодаря заполнению проводящими дорожками становится ненужным обычно осуществляемый этап введения металлизированной плоскости для стабилизации поверхностей слоев. Таким образом выгодно повышается надежность микросхемы без дополнительных затрат или при незначительных дополнительных затратах.

Использование: в интегральных микросхемах для защиты от анализа, осуществляемого путем несанкционированного доступа. Сущность изобретения: в интегральной микросхеме с подложкой, имеющей компоненты микросхемы, и, по меньшей мере, одну плоскость разводки с первыми проводящими дорожками, предназначенными для соединения компонентов интегральной микросхемы, в плоскости разводки свободные от первых проводящих дорожек области заполнены вторыми проводящими дорожками для защиты интегральной микросхемы от анализа, осуществляемого путем несанкционированного доступа. В способе изготовления интегральной микросхемы при формировании монтажной схемы свободные от первых проводящих дорожек области плоскости разводки заполняют вторыми проводящими дорожками для защиты интегральной микросхемы от анализа, осуществляемого путем несанкционированного доступа. Техническим результатом заявленного изобретения является создание при низких затратах интегральной микросхемы, обеспечивающей высокую защиту против действующего извне несанкционированного анализа. 2 н. и 8 з.п. ф-лы, 2 ил.

| US 4434361 А, 28.02.1984 | |||

| МАГНИТОСТРИКЦИОННЫЙ ПРИВОД КОРРЕКЦИИ ДЕЛИТЕЛЬНОЙ ЦЕПИ | 0 |

|

SU378306A1 |

| Автоматическая линия формования и сушки керамических изделий | 1978 |

|

SU764985A1 |

| Идентификационная карта | 1984 |

|

SU1251138A1 |

| МИКРОЭЛЕКТРОННОЕ УСТРОЙСТВО | 1998 |

|

RU2151422C1 |

Авторы

Даты

2005-10-27—Публикация

2001-11-08—Подача