Изобретение относится к полупроводниковой интегральной схеме с электронными схемами, реализованными по меньшей мере в одном слое полупроводниковой подложки, упорядоченными по меньшей мере в одну группу, и по меньшей мере с одним проводящим защитным слоем, расположенным по меньшей мере над одной такой группой схем и электрически соединенным по меньшей мере с одной из упомянутых схем.

Подобная полупроводниковая интегральная схема известна из ЕР 0378306 А2. В этой полупроводниковой интегральной схеме первая группа схем размещена в защищенной области, а вторая группа схем размещена в незащищенной области. Защита первой области в известной полупроводниковой интегральной схеме осуществлена с помощью проводящего слоя, который размещен над плоскостью монтажа первой группы схем. Этот проводящий слой электрически соединен с группой схем, причем функционирование этой группы схем в соответствии с их назначением реализуется только при кондиционном состоянии указанного слоя.

Первая группа схем включает в себя микропроцессор, а также относящиеся к нему периферийные схемы, такие как блоки памяти и логическая схема переноса. В блоках памяти может содержаться, в частности, защищенная информация. Кроме того, микропроцессор может иметь специальную структуру, которая особенно хорошо приспособлена для выполнения функций защиты. Посредством проводящего слоя, целостность которого постоянно контролируется, исключается возможность неправомерного доступа и получения информации в процессе работы схемы, например, с помощью растрового электронного микроскопа.

Однако, как и раньше, можно удалить защитный слой и сформировать заменяющие проводники, которые находятся не над критичными с точки зрения защиты областями. Таким путем все равно можно провести исследование схем в процессе работы, хотя и в условиях, связанных с большими затратами.

В ЕР 0169941 А1 описана полупроводниковая интегральная схема с пассивирующим слоем, который экранирует лежащие под ним участки схемы в качестве эквипотенциальной поверхности. Этот пассивирующий слой включен в качестве проводящей дорожки в логические схемы защиты, так что его устранение нарушает функционирование микросхемы и приводит к невозможности динамического анализа. Если, однако, удастся вместо накрывающего защитного пассивирующего слоя проложить некоторого рода шунтирующий проводник, который правда не выполняет проводящую функцию пассивирующего слоя, однако экранирующая функция в этой известной схеме защиты вновь активизирует полупроводниковую интегральную схему.

В ЕР 0300864 А2 предусмотрен проводящий защитный слой, который состоит из двух частичных слоев, емкость которых оценивается. Замена одного или обоих частичных слоев другими проводящими структурами, хотя и не без труда, возможна; во всяком случае имитация емкости другими структурами, которые по меньшей мере частично открывают схемы, позволила бы преодолеть предусмотренные в конструкции интегральной схемы меры защиты. Во всяком случае факт удаления слоев и последующего повторного нанесения с целью проведения по меньшей мере статистического исследования полупроводниковой интегральной схемы позже установить невозможно.

Одним из методов удаления слоев, а также нанесения новых слоев, как, например, шунтирующих проводников, является метод, использующий фокусированный поток ионов. Этот метод, правда, был разработан в первую очередь для устранения ошибок и реструктурирования, однако представляет серьезную опасность для полупроводниковых интегральных схем, критичных с точки зрения обеспечения защищенности.

Поэтому задачей изобретения является создание полупроводниковой интегральной схемы, которая защищена от несанкционированного анализа с применением метода фокусированного потока ионов.

Указанная задача в соответствии с пунктом 1 формулы изобретения решается тем, что подложка полупроводниковой интегральной схемы имеет по меньшей мере один датчик защиты, который выполнен таким образом, что он может сохранять некоторое состояние энергонезависимым образом (с сохранением информации при выключении питания), при этом датчик защиты своим выводом обнаружения связан с проводящим защитным слоем или по меньшей мере с одним из проводящих защитных слоев, а выходной вывод датчика защиты соединен по меньшей мере с одной из схем таким образом, что функционирование схемы в соответствии с ее назначением невозможно, если на выходе датчика защиты приложен определенный энергонезависимый уровень.

Датчик защиты может предпочтительным образом представлять собой транзистор с очень тонким слоем подзатворного оксида по сравнению с соответствующим слоем в транзисторах схем. Но могут применяться и другие конструктивные элементы, действующие в качестве "предохранителей", например диоды. Существенным для такого конструктивного элемента, выполняющего функцию предохранителя, является то, что он под воздействием напряжения может изменяться энергонезависимым образом.

Под "энергонезависимым" изменением в этой связи понимается то, что запомненное состояние сохраняется не только после отключения и повторного приложения напряжения питания, но и что удаление и повторное нанесение проводящего слоя, создающего соединение, обнаруживается и фиксируется. Таким образом, и при целостном слое можно установить, был ли он перед этим удален или производились попытки его удаления.

Было показано, что структуры, обрабатываемые с помощью фокусированного потока ионов, заряжаются электрически. Вырабатываемое при этом напряжение обнаруживается датчиками защиты и оценивается компонентами схемы (схем). Если датчик защиты представляет собой транзистор с очень тонким слоем подзатворного оксида по сравнению с соответствующим слоем других транзисторов, то этот подзатворный оксид разрушается под действием напряжения, обусловленного пучком ионов. Это может быть оценено без особых затруднений.

Датчики защиты могут, с одной стороны, быть распределены по всей поверхности в пределах полупроводниковой интегральной схемы, но, с другой стороны, достаточным является использование незначительного количества датчиков.

Особое преимущество изобретения состоит в том, что удаление защитного слоя с последующим нанесением шунтирующего проводника для случая, когда проверяется наличие защитного слоя, не приведет к успеху, так как датчик защиты обнаруживает удаление защитного слоя энергонезависимым образом и схема после этого не будет функционировать, т.е. не сможет быть приведена в действие ни при наличии защитного слоя, ни при его отсутствии. Существенным при этом является то, что манипулирование защитным слоем фиксируется энергонезависимым образом, что, например, может быть осуществлено путем разрушения подзатворного оксида.

В другом варианте осуществления изобретения датчик защиты выполнен в виде энергонезависимой ячейки памяти, которая образована диффузионными областями стока и истока, образованными по обе стороны канальной области в полупроводниковой подложке, а также электродом затвора, полностью изолированным, размещенным по меньшей мере частично выше канальной области, и двумя управляющими электродами затвора, размещенными над изолированным электродом затвора, причем один из управляющих электродов затвора образует вывод обнаружения, а другой управляющий электрод затвора и диффузионные области соединены со схемой оценки.

При использовании этой новой энергонезависимой ячейки памяти напряжение, обусловленное пучком ионов, приводит к изменению заряда на изолированном затворе, который не может стекать. С помощью второго вывода управляющего затвора, а также выводов диффузионных областей можно в любой момент считать измененное состояние ячейки памяти и тем самым обнаружить его.

Предпочтительным образом изолированный затвор имеет предварительный заряд, причем при наличии множества датчиков защиты предварительный заряд создается с разной полярностью, чтобы обеспечить надежное обнаружение факта манипулирования интегральной схемой.

Изобретение поясняется ниже на примерах его осуществления, иллюстрируемых чертежами, на которых представлено следующее:

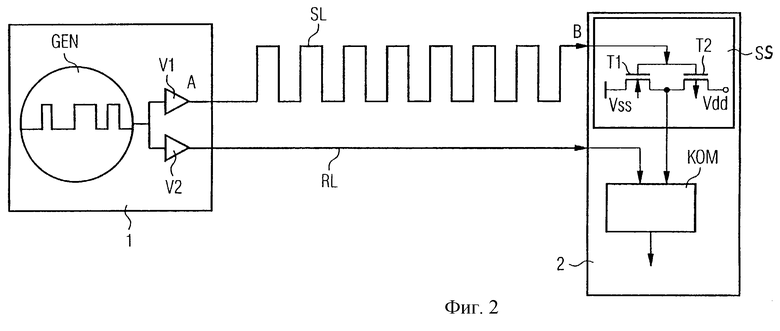

фиг.1- возможный вариант выполнения защитного слоя;

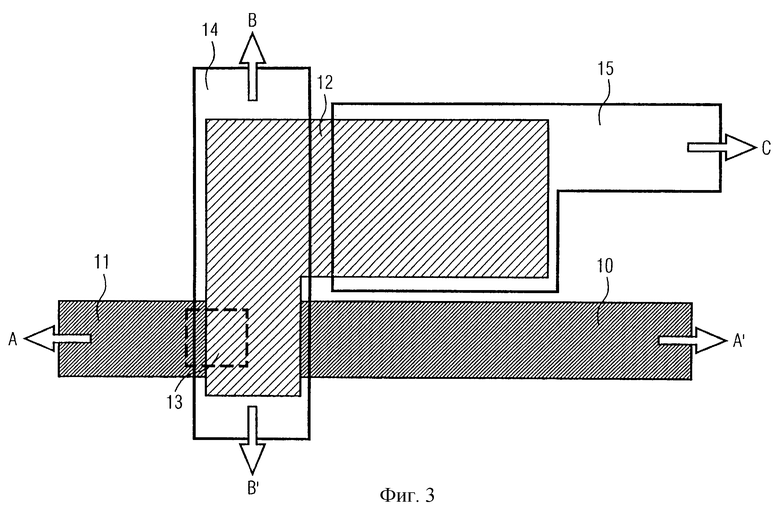

фиг.2 - принципиальная схема возможного варианта выполнения схемы оценки в датчике защиты, соответствующем изобретению;

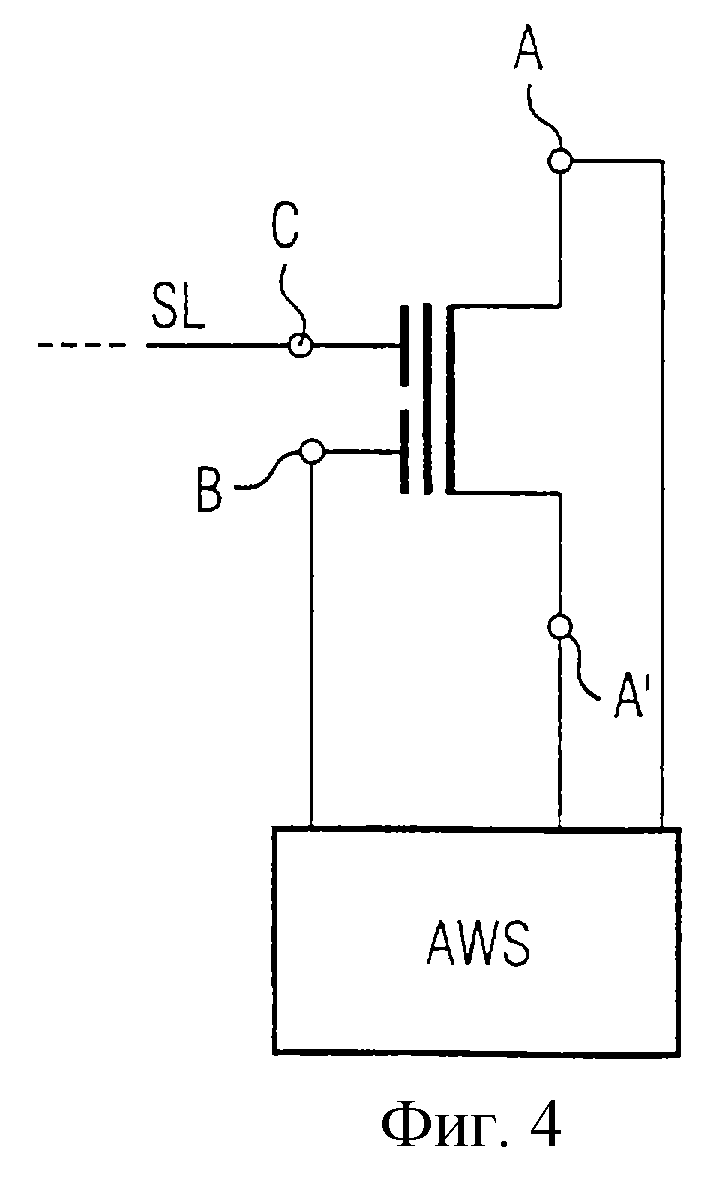

фиг.3 - вид сверху датчика защиты, выполненного в соответствии с изобретением в виде энергонезависимой ячейки памяти;

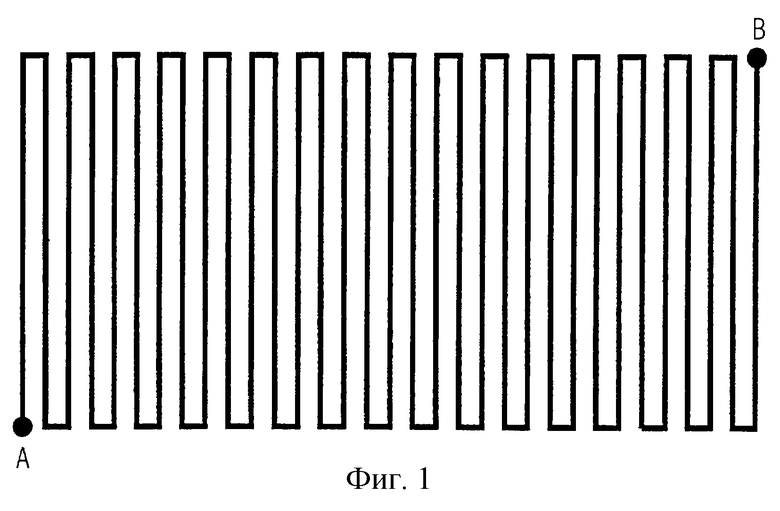

фиг. 4 - схематичное представление схемы оценки, связанной с энергонезависимой ячейкой памяти.

На фиг.1 представлено защитное покрытие в форме меандрового проводника с двумя выводами А, В, которое предпочтительным образом реализуется в самом верхнем слое металлизации в обычном процессе изготовления полупроводниковой интегральной схемы. Выводы А, В имеют сквозные контакты на схемном уровне. Они могут быть связаны там со схемой, показанной на фиг.2.

Генератор сигналов GEN, выполненный в передающем устройстве 1 в полупроводниковой интегральной схеме, вырабатывает сигнал, который в показанном примере через усилители V1, V2 подается к защитному проводнику SL, показанному на фиг.1, и к опорному проводнику RL. Вывод В защитного проводника соединен выводами затворов двух транзисторов T1, T2, включенных по схеме КМОП-инвертора, с тонким слоем подзатворного оксида, действующего в качестве датчика защиты SS. Выход датчика защиты SS, так же как второй вывод опорного проводника RL, соединен с одним из входов компаратора КОМ, выходной сигнал которого показывает, находится ли датчик защиты SS в исправном состоянии. Датчик защиты SS и компаратор КОМ образуют при этом приемную схему 2.

Если датчик защиты SS находится в исправном состоянии, на его выходе вырабатывается такой же сигнал, как и в опорном проводнике RL. Если же датчик защиты под воздействием высокого напряжения, обусловленного неправомерным доступом с использованием пучка ионов, разрушается, то на его выходе вырабатывается постоянное значение - логическая "1" или логический "0", что распознается компаратором КОМ. Выходной сигнал компаратора обуславливает то, что электронная схема, реализованная на интегральной схеме, больше не сможет выполнять предназначенную для нее функцию.

На фиг. 3 представлен вид сверху соответствующей изобретению энергонезависимой ячейки памяти с двумя управляющими электродами затвора. Между двумя диффузионными областями 10, 11, которые функционируют в качестве стока и истока полевого транзистора, выполнена известным способом канальная область, детально не показанная на чертеже, частично покрытая областью изолированного электрода затвора 12, так называемого плавающего затвора. Изолированный слой между канальной областью и областью истока - и соответственно областью стока 11, с одной стороны, и изолированным электродом затвора 12, с другой стороны, в некоторой малой области особенно тонок и образует там туннельное окно 13. Над первой областью изолированного электрода затвора 12 размещен первый управляющий электрод 14 затвора, а над второй областью - второй управляющий электрод 15 затвора. Диффузионная область 10, 11 и управляющие электроды 14, 15 затвора имеют выводы А, А', В, В' и соответственно С.

Новая ячейка памяти может предпочтительным образом применяться вместо транзисторов с тонким слоем подзатворного оксида согласно фиг.2. При этом вывод С ячейки памяти необходимо соединить с выводом В защитного проводника SL. Вывод В ячейки памяти и выводы диффузионных областей А, А' ячейки памяти применяются, с одной стороны, для подачи предварительного заряда на изолированный электрод затвора, а с другой стороны, для оценки состояния заряда изолированного электрода затвора соединяются со схемой оценки AWS, как показано на фиг.4.

Предварительный заряд в предпочтительном варианте осуществления изобретения подается на изолированный электрод затвора перед выпуском полупроводниковых интегральных схем на этапе испытаний путем приложения высокого запрограммированного напряжения величиной примерно 16 В между одним из выводов В или В' первого управляющего электрода 14 затвора и выводом А диффузионной области 11. С помощью этого заряда устанавливается определенное рабочее напряжение транзисторов памяти. Это рабочее напряжение является мерой заряда на изолированном электроде затвора. Если теперь будет иметь место несанкционированный доступ с использованием сфокусированного потока ионов, то между вторым управляющим электродом 15 затвора и канальной областью возникает напряжение. Это напряжение приводит к туннельному току через туннельное окно 13 и тем самым к изменению заряда на изолированном электроде затвора 12. Это изменение заряда может быть обнаружено с помощью схемы оценки AWS за счет определения рабочего напряжения путем приложения изменяющегося напряжения считывания к первому управляющему электроду 14 затвора. Измененное рабочее напряжение указывает на то, что заряд на изолированном электроде затвора был изменен.

Если таким путем энергонезависимым способом был установлен факт несанкционированной попытки доступа с использованием сфокусированного потока ионов, то при последующем вводе в действие полупроводниковой интегральной схемы может быть активизирован соответствующий механизм защиты.

На изолированный электрод затвора 12 в качестве предварительного заряда может быть подан как положительный, так и отрицательный заряд, а для различных датчиков защиты могут быть использованы заряды различной величины и полярности, чтобы повысить надежность обнаружения несанкционированной попытки доступа с использованием сфокусированного потока ионов.

Особое преимущество соответствующего изобретению использования защитного слоя во взаимосвязи с датчиком защиты состоит в том, что датчик защиты энергонезависимым способом регистрирует факт анализа защитного слоя ионным пучком, в результате чего последующее восстановление защитного слоя или соответствующие шунтирующие проводники не могут обеспечить выполнение функций полупроводниковой интегральной схемы в соответствии с ее назначением.

Изобретение относится к полупроводниковым интегральным схемам. Предложена полупроводниковая интегральная схема, содержащая схемы, реализованные по меньшей мере в одном слое полупроводниковой подложки и упорядоченные по меньшей мере в одной группе, и по меньшей мере один проводящий защитный слой (SL), размещенный по меньшей мере над одной из таких групп схем и электрически соединенный по меньшей мере с одной из схем (1, 2). Подложка полупроводниковой интегральной схемы имеет по меньшей мере один датчик защиты (SS), который выполнен с возможностью сохранения некоторого состояния энергонезависимым образом, при этом датчик защиты (SS) своим выводом обнаружения связан с проводящим защитным слоем (SL) или по меньшей мере с одним из проводящих защитных слоев. При этом выходной вывод датчика защиты (SS) соединен по меньшей мере с одной из схем (2) таким образом, что функционирование схемы в соответствии с ее назначением невозможно, если на выходе датчика защиты приложен определенный энергонезависимый уровень. В результате схема защищена от несанкционированного анализа с применением метода фокусированного потока ионов. 5 з.п.ф-лы, 4 ил.

| НОВЫЙ СПОСОБ ПРОКАТКИ УГЛОВЫХ АСИММЕТРИЧНЫХ ПРОФИЛЕЙ | 2005 |

|

RU2288048C1 |

| Пособ получения карбоната кальция | 1975 |

|

SU510434A1 |

| ЕР 169941 А1, 05.02.1986 | |||

| МЕЙЗДА Ф | |||

| ИНТЕГРАЛЬНЫЕ СХЕМЫ ТЕХНОЛОГИЯ И ПРИМЕНЕНИЯ | |||

| - М.: МИР, 1981. | |||

Авторы

Даты

2003-09-27—Публикация

1999-08-18—Подача