Изобретение относится к способу изготовления полупроводникового элемента с частично проходящей в подложке разводкой, а также к изготовленному этим способом полупроводниковому элементу. Полупроводниковые элементы с частично проходящими в подложке разводками известны, например, из DE 3502713 А1 и DE-AS 1614250.

Интегральные схемы, в частности КМОП-схемы, изготовляют со многими технологическими операциями. Затраты на изготовление этих схем определяются при этом комплексностью процесса и физическим временем обработки. Высококомплексные модули требуют зачастую нескольких сотен отдельных технологических операций и многих дней для технологического цикла изделия.

Часть технологических операций приходится при этом затрачивать на изготовление разводки, которая соединяет между собой отдельные активные элементы или обеспечивает присоединение интегральной схемы к "внешнему миру". Обычно подобные соединения реализуют посредством одной или нескольких плоскостей токопроводящих дорожек из алюминия.

Имеются, однако, области, где плоскость токопроводящих дорожек из алюминия, во-первых, слишком дорогая, а, во-вторых, требует большой площади. Кроме того, интегральные схемы, реализованные с помощью алюминиевой разводки, недостаточно защищены от внешних манипуляций или последующего анализа схемы.

Для того чтобы можно было производить манипуляции с интегральной схемой, сначала следует, как правило, проанализировать интегральную схему. Для этого необходимо слой за слоем снять пассивирующий слой или изолирующие слои между плоскостями токопроводящих дорожек, с тем, чтобы можно было исследовать открывшиеся таким образом плоскости разводки. Если при этом плоскости разводки выполнены в виде алюминиевой разводки, то подобный анализ схемы можно произвести относительно просто.

В основе изобретения лежит поэтому задача создания способа изготовления полупроводникового элемента с частично проходящей в подложке разводкой, а также изготовленного этим способом полупроводникового элемента, у которого анализ интегральной схемы, а также последующая манипуляция с ней значительно затруднены.

Далее способ изготовления подобной разводки должен быть как можно лучше согласован со способом изготовления транзисторов и требовать как можно меньше дополнительных технологических операций.

Эта задача решается посредством способа по п.1 формулы изобретения и посредством полупроводникового элемента по п.12. Другие предпочтительные формы выполнения, модификации и аспекты настоящего изобретения приведены в зависимых пунктах формулы, описании и на прилагаемых чертежах.

Согласно изобретению заявлен способ изготовления полупроводникового элемента, по меньшей мере, с частично проходящей в подложке разводкой, причем предусмотрены, по меньшей мере, одно проходящее в полупроводниковой подложке и, по меньшей мере, одно проходящее на полупроводниковой подложке проводящие соединения. Способ согласно изобретению включает в себя следующие операции:

а) подготавливают полупроводниковую подложку, имеющую, по меньшей мере, две области, причем в первой области располагают транзисторы первого типа, а во второй области - транзисторы второго типа;

б) на полупроводниковую подложку наносят первый изолирующий слой;

в) легирующую примесь первого типа проводимости вводят в первую область в зону последующего пересечения между проходящими в полупроводниковой подложке и на полупроводниковой подложке проводящими соединениями и/или легирующую примесь второго типа проводимости вводят во вторую область в зону последующего пересечения между проходящими в полупроводниковой подложке и на полупроводниковой подложке проводящими соединениями;

г) на первый изолирующий слой наносят проводящий слой;

д) посредством фототехнического процесса наносят первую маску, которая в первой области почти полностью покрывает, в основном, только дорожки затворов формируемых транзисторов первого типа, а также при необходимости проходящее на полупроводниковой подложке проводящее соединение и вторую область;

е) в соответствии с этой первой маской проводящий слой преобразуют во второй изолирующий слой или удаляют и, по меньшей мере, одну легирующую примесь первого типа проводимости вводят в полупроводниковую подложку;

ж) посредством фототехнического процесса наносят вторую маску, которая во второй области почти полностью покрывает, в основном, только дорожки затворов формируемых транзисторов второго типа, а также при необходимости проходящее на полупроводниковой подложке проводящее соединение и первую область;

з) в соответствии с этой второй маской проводящий слой преобразуют во второй изолирующий слой или удаляют и, по меньшей мере, одну легирующую примесь второго типа проводимости вводят в полупроводниковую подложку,

так что за счет легирующих примесей, введенных в зоне точек пересечения и посредством первой или второй маски, образуется проходящее в полупроводниковой подложке проводящее соединение.

Эти операции необязательно должны проводиться в указанном порядке, в частности операции б) и в) можно также поменять местами. С помощью изготовленного таким образом полупроводникового элемента согласно изобретению могут быть реализованы низкоомные подныривания под плоскость затвора, что значительно затрудняет последующий анализ схемы. Полупроводниковый элемент согласно изобретению может применяться, таким образом, в тех случаях, когда речь идет о высокой надежности против внешних манипуляций.

Способ согласно изобретению обладает, кроме того, тем преимуществом, что для формирования, по меньшей мере, двух типов транзисторов, например p-МОП- и n-МОП-транзисторов, а также проходящей в подложке разводки он требует лишь три фотослоя, тогда как традиционные способы изготовления требуют обычно 6 или более фотослоев. У способа согласно изобретению полученные посредством фототехнического процесса маски служат в соответствующей области как для структурирования дорожек затворов, так и для ввода легирующей примеси, с тем чтобы получить области истока и стока или проходящие в подложке соединения. За счет экономии трех фотослоев ход процесса значительно упрощается и ускоряется, что обеспечивает экономичное производство. Подобные интегральные схемы могут быть также использованы в тех случаях, когда речь идет, в частности, о небольших производственных расходах.

У способа согласно изобретению предпочтительно, в частности, если между первой и второй областями предусмотрена зона (или зоны), не покрытая обеими масками. Таким образом, гарантировано, что в плоскости проводящего слоя только действительно предусмотренные соединения создают проводящее соединение между первой и второй областями.

Далее предпочтительно, если на проводящий слой наносят, в частности, оксидно-нитридно-оксидный слой, удаляемый после нанесения масок в соответствии с масками.

Также предпочтительно, если проводящим слоем является поликристаллический кремниевый слой.

Согласно одной форме выполнения настоящего изобретения поликристаллический кремниевый слой преобразуют путем окисления во второй изолирующий слой. При этом, в частности, предпочтительно, если поликристаллический кремниевый слой преобразуют во второй изолирующий слой за счет удаления части поликристаллического кремниевого слоя, а оставшуюся часть путем окисления преобразуют в слой оксида кремния.

Далее предпочтительно, если легирующую примесь вводят в полупроводниковую подложку посредством имплантации с последующей термообработкой. При этом для ввода легирующей примеси может быть использована, в частности, возникающая при окислении поликристаллического кремниевого слоя повышенная температура процесса.

Кроме того, предпочтительно, если первая и вторая области имеют каждая зоны, предусмотренные для контактов подложки, первая маска имеет над зонами во второй области, предусмотренными для контактов подложки, отверстия и покрывает зоны в первой области, предусмотренные для контактов подложки, и если вторая маска имеет над зонами в первой области, предусмотренными для контактов подложки, отверстия и покрывает зоны во второй области, предусмотренные для контактов подложки.

Далее предпочтительно, если в заданных областях, в которых должны располагаться формируемые транзисторы, предусмотрены изолирующие зоны, в частности толстослойные оксидные изоляции или мелкощелевые изоляции, которые ограничивают транзисторы.

Изобретение более подробно поясняется ниже с помощью чертежа, на котором изображают:

- фиг.1-5: схематичные сечения различных стадий способа согласно изобретению;

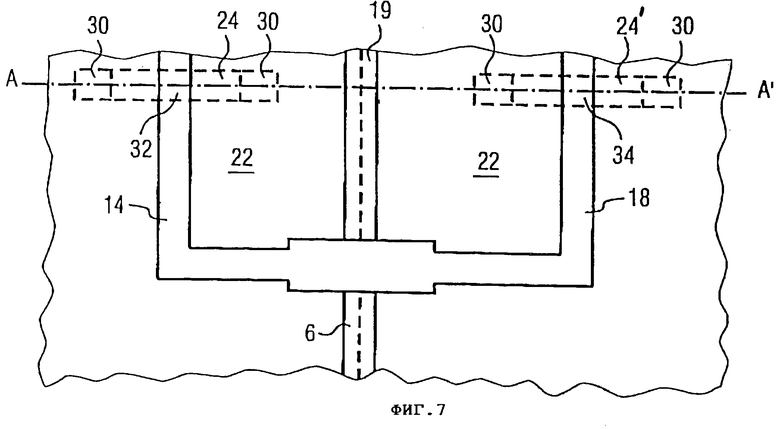

- фиг.6 и 7: виды сверху на изображенную на фиг.4 в сечении структуру.

На фиг.1 изображена полупроводниковая подложка 1, подготавливаемая в качестве отправной точки для способа согласно изобретению. В полупроводниковой подложке 1 р-типа предусмотрен карман 2 n-типа. Протяженность кармана 2 n-типа определяет, таким образом, одну из областей 3, которая позднее принимает диффузию акцепторной примеси в качестве проводящего соединения. Далее в полупроводниковой подложке 1 р-типа предусмотрен карман 4 р-типа. Протяженность кармана 4 р-типа также определяет, таким образом, одну из областей 5, которая позднее принимает диффузию донорной примеси в качестве проводящего соединения.

Кроме того, предусмотрены толстослойные оксидные изоляции 6, которые горизонтально изолируют друг от друга отдельные соединения. Для улучшения изоляции при этом под толстослойными оксидными изоляциями могут еще находиться ионно-имплантированные через защитный слой оксида области 7.

На эту предварительно структурированную полупроводниковую подложку 1 наносили оксидный слой 8 в качестве изолирующего слоя между толстослойными оксидными изоляциями. Этот оксидный слой 8 служит ниже в других зонах полупроводниковой подложки 1 в качестве подзатворного оксида для еще формируемых транзисторов (не показаны). Возникающая в результате этого структура показана на фиг.1.

Посредством фототехнического процесса в карман 2 n-типа полупроводниковой подложки 1 имплантируют атомы 33 бора (энергия имплантации 20 кэВ, доза имплантации 2•1014 см-2). При этом атомы бора имплантируют в зону 23, которая позднее образует пересечение между проходящим в полупроводниковой подложке проводящим соединением 24 и проходящим на полупроводниковой подложке проводящим соединением 14 (фиг.6).

Посредством следующего фототехнического процесса в карман 4 р-типа полупроводниковой подложки 1 имплантируют атомы 35 фосфора (энергия имплантации 20 кэВ, доза имплантации 2•1014 см-2). При этом атомы фосфора имплантируют в зону 25, которая позднее образует пересечение между проходящим в полупроводниковой подложке проводящим соединением 24' и проходящим на полупроводниковой подложке проводящим соединением 18 (фиг.6). Возникающая в результате этого ситуация показана на фиг.2.

Затем методом химического осаждения из газовой фазы на оксидный слой 8 и толстослойную оксидную изоляцию 6 наносят поликристаллический кремниевый слой 10 в качестве проводящего слоя. При этом поликристаллический кремниевый слой 10 имеет, например, толщину 150 нм и легирование донорной примесью 2•1020 см-3). Это легирование может происходить in-situ во время осаждения за счет последующей имплантации или так называемого POCL-покрытия. Затем следует осаждение оксидно-нитридно-оксидного слоя на поликристаллический кремниевый слой 10, причем из оксидно-нитридно-оксидного слоя затем за счет окисления возникает оксидно-нитридно-оксидный слой 11 в качестве защитного слоя.

Посредством фототехнического процесса на оксидно-нитридно-оксидный слой 11 наносят первую маску 12. При этом первая маска 12 покрывает над карманом 2 p-типа, в основном, только соединение 14, тогда как карман 4 р-типа почти полностью прикрыт.

Над зоной 19 (фиг.4) между обоими карманами 2,4 маска 12 немного смещена назад, так что также эта зона открыта.

В соответствии с этой первой маской 12 открытые части оксидно-нитридно-оксидного слоя 11 удаляют травлением. Далее в соответствии с этой первой маской 12 открытую часть поликристаллического кремниевого слоя 10 удаляют на заданную толщину. Наконец в соответствии с этой первой маской 12 в полупроводниковую подложку 1 имплантируют атомы 15 бора и толстослойную оксидную изоляцию 6 (энергия имплантации 20 кэВ, доза имплантации 2•1015 см-2). Поскольку имплантированные в толстослойную оксидную изоляцию 6 атомы бора в дальнейшем не играют роли, на фиг.3 показаны только атомы бора, имплантированные в полупроводниковую подложку 1.

При этом маску 12 можно было бы удалить уже после структурирования защитного слоя 11 или удалить уже после структурирования проводящего слоя 10, однако предпочтительно оставить маску 12 до тех пор, пока не будет завершена имплантация легирующей примеси. Таким образом, можно использовать относительно тонкий проводящий слой, который влечет за собой лишь небольшие топологические различия на поверхности подложки.

По завершении имплантации бора первую маску 12 удаляют и посредством следующего фототехнического процесса наносят вторую маску 17. При этом вторая маска 17 покрывает над карманом 4 р-типа только соединение 18, тогда как карман 2 n-типа почти полностью прикрыт.

Над зоной 19 (фиг.4) между обоими карманами 2,4 маска 17 немного смещена назад, так что также эта зона открыта.

В соответствии с этой второй маской 17 еще имеющиеся, теперь открытые части оксидно-нитридно-оксидного слоя 11 удаляют травлением. Далее в соответствии с этой второй маской 17 еще имеющуюся, открытую часть поликристаллического кремниевого слоя 10 удаляют на заданную толщину. Это приводит, в том числе, к тому, что в зоне 19 между первой и второй областями, не покрываемой обеими масками, поликристаллический кремниевый слой 10 полностью удаляется.

Наконец, в соответствии с этой второй маской 17 в полупроводниковую подложку 1 имплантируют атомы 20 фосфора и/или мышьяка и толстослойную оксидную изоляцию 6 (фосфор: энергия имплантации 130 кэВ, доза имплантации 1•1014 см-2; мышьяк:

энергия имплантации 150 кэВ, доза имплантации 2•1015 см-2). Поскольку имплантированные в толстослойную оксидную изоляцию 6 атомы легирующей примеси в дальнейшем не играют роли, на фиг.4 показаны только имплантированные в полупроводниковую подложку 1 атомы легирующей примеси.

По завершении имплантации фосфора или мышьяка вторую маску 17 удаляют и осуществляют окисление оставшегося и не защищенного защитным слоем 11 поликристаллического кремниевого слоя 10, в результате чего возникает оксидный слой 22 в качестве изолирующего слоя. Покрытые оксидно-нитридно-оксидным слоем 11 соединения 14,18 при этом не окисляются. Окисление поликристаллического кремниевого слоя 10 происходит, например, во влажной атмосфере при температуре около 950oС в течение 80 мин. Эту повышенную температуру используют одновременно для ввода в полупроводниковую подложку легирующих примесей бор или фосфор/мышьяк, с тем, чтобы сформировать, таким образом, проходящие в полупроводниковой подложке проводящие соединения 24,24'.

Концентрация легирующих примесей выбрана при этом так, что проходящие в полупроводниковой подложке проводящие соединения 24,24' обладают в зонах 23,25 пересечений 32,34 достаточной проводимостью. Это препятствует образованию транзисторов в пересечениях 32,34. Возникающая в результате этого ситуация показана на фиг.5.

Согласно другой форме выполнения способа согласно изобретению поликристаллический кремниевый слой 10 удаляют во время травления не только на заданную толщину, но и полностью. Следствием этого является то, что в длительной операции окисления для преобразования оставшегося поликристаллического кремния больше нет необходимости. В этом случае осуществляют лишь относительно кратковременную термообработку для ввода легирующих примесей в полупроводниковую подложку (950oС в течение примерно 20 мин).

На фиг. 6 изображен вид сверху на показанную на фиг.5 в сечении структуру. Показанная на фиг.5 структура возникает за счет разреза по линии А - А' на фиг.6 и последующего раскладывания.

Видно, что дорожки 14,18 затворов представляют собой проходящее на полупроводниковой подложке 1 проводящее соединение, которое соединяет между собой, например, электроды затворов двух транзисторов (не показаны). Напротив, диффузионные области 24,24', которые на более позднем этапе способа контактируют через контактные отверстия в местах 30, представляют собой проводящее соединение, проходящее в полупроводниковой подложке 1.

Если кто-либо предпримет попытку проанализировать изготовленную таким образом интегральную схему, то изображенная на фиг.6 при виде сверху разводка покажется ему расположением двух КМОП-транзисторов. Отличие заключается только в концентрации легирующей примеси в зонах 23,25. Эту концентрацию легирующей примеси можно установить впоследствии, однако, лишь с очень большими затратами. Поэтому последующий анализ схемы не приведет к корректной схеме. Последующая манипуляция с интегральной схемой также значительно затруднена.

На фиг.7 также при виде сверху изображено устройство согласно изобретению, у которого диффузионные области 24,24' лежат по одной линии. Линия А - А' здесь в противоположность фиг.6 вытянута. Напротив, дорожки 14,18 затворов расположены под углом друг к другу.

В заключение осуществляют осаждение дополнительного изолирующего слоя, например, из борофосфоросиликатного стекла и дополнительного проводящего слоя, например, из алюминия для образования первого слоя металлизации. В зависимости от комплексности изготовляемой схемы могут быть нанесены дополнительные изолирующие слои и дополнительные проводящие слои. Для простых схем одного слоя металлизации, как правило, однако, достаточно, так что может быть осажден один пассивирующий слой.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПАМЯТИ И СПОСОБ ИЗГОТОВЛЕНИЯ | 2001 |

|

RU2247441C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ СИЛОВОГО ПОЛУПРОВОДНИКОВОГО ПРИБОРА | 2009 |

|

RU2510099C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВОГО КОМПОНЕНТА С ИНТЕГРИРОВАННЫМ ПОПЕРЕЧНЫМ СОПРОТИВЛЕНИЕМ | 2012 |

|

RU2548589C2 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 1990 |

|

RU2127928C1 |

| Способ изготовления полупроводниковых приборов | 1990 |

|

SU1828560A3 |

| Способ изготовления полупроводниковых приборов | 1990 |

|

SU1830156A3 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ЭНЕРГОНЕЗАВИСИМОЙ ПОЛУПРОВОДНИКОВОЙ ЗАПОМИНАЮЩЕЙ ЯЧЕЙКИ С ОТДЕЛЬНЫМ ТУННЕЛЬНЫМ ОКНОМ | 2000 |

|

RU2225055C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ЭЛЕМЕНТОВ СТРУКТУР ОЧЕНЬ МАЛОГО РАЗМЕРА НА ПОЛУПРОВОДНИКОВОЙ ПОДЛОЖКЕ | 1996 |

|

RU2168797C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА, ИМЕЮЩЕГО САМОВЫРАВНЕННЫЙ КОНТАКТ | 1997 |

|

RU2190897C2 |

| ПОЛУПРОВОДНИКОВАЯ ИНТЕГРАЛЬНАЯ СХЕМА С ЗАЩИТНЫМ ПОКРЫТИЕМ ПОВЕРХНОСТИ | 1999 |

|

RU2213390C2 |

Изобретение относится к области изготовления защищенных интегральных схем, а именно к способу изготовления полупроводникового элемента с проходящей, по меньшей мере, частично в подложке разводкой, а также самому полупроводниковому элементу. Согласно этапам способа изготовления предусмотрено выполнение, по меньшей мере, одного проходящего в полупроводниковой подложке и, по меньшей мере, одного проходящего на полупроводниковой подложке проводящего соединения. В результате полупроводниковый элемент, изготовленный согласно изобретению, позволяет использовать его в тех случаях, когда речь идет о высокой надежности против внешних манипуляций. 2 с. и 10 з.п. ф-лы, 7 ил.

| Автоматическая линия формования и сушки керамических изделий | 1978 |

|

SU764985A1 |

| ИНТЕГРАЛЬНАЯ СХЕМА С ДВУМЯ ТИПАМИ МОП-ТРАНЗИСТОРОВ | 1994 |

|

RU2100874C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ КМОП ИС | 1992 |

|

RU2051443C1 |

| Устройство для вычитания и добавления импульсов | 1976 |

|

SU585601A1 |

| US 4583011 А, 15.04.1986 | |||

| БИКМОП-ПРИБОР И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 1996 |

|

RU2106719C1 |

Авторы

Даты

2003-10-20—Публикация

1999-11-11—Подача