1

(21)4751307/24

(22)19.10.89

(46) 30.10.91. Биш. № 40

(71)Ленинградское объединение электронного приборостроения Светлана

(72)А.Ф. Дряпак, Е.Н.Носова, Р.И.Бе- лицкий, А.В.Палагин, А.И.Зайончковс- кий и В.В.Городецкий

(53)681.3 (088.8)

(56)Клингман Э. Проектирование микропроцессорных систем. М.: Мир, 1980, с. 458-483.

Европейский патент № 0032182, кл. G 06 F 13/00, 1981.

(54)ПРОЦЕССОР ДЛЯ МУЛЬТИПРОЦЕССОРНОЙ СИСТЕМЫ

(57)Изобретение относится к вычислительной технике и предназначено для работы в мультипроцессорной системе обработки данных, использующей общую

магистраль для доступа к общим ресурсам системы, или в однопроцессорных системах, работающих в мультипрограммном режиме. Цель изобретения - повышение быстродействия. Для этого процессор содержит блок микропрограммного управления, арифметико-логическое устройство, регистр команд, магистральный транслятор, буферные регистры, регистр системного адреса, схему сравнения, два шинных формирователя, группу шинных формирователей, три формирователя импульсов, четыре триггера, элемент ИЛИ-НЕ и элемент И. Это позволяет процессору реализовать возможность выполнения текущей задачи и одновременно аппаратно следить за освобождением только своего семафора, не занимая при этом системную шину и не расходуя программные вставки. 3 ил.

с

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

Изобретение относится к вычислительной технике и предназначено для работы в мультипроцессорной системе обработки данных, использующей общую магистраль для. доступа к общим ресурсам системы, или в однопроцессорных системах, работающих в мультипрограммном режиме.

Целью изобретения является повыше ние быстродействия процессора (путем исключения повторных опросов при освобождении семафоров, управляющих другими частями общих ресурсов системы и уменьшение внешних управляющих сигналов процессора).

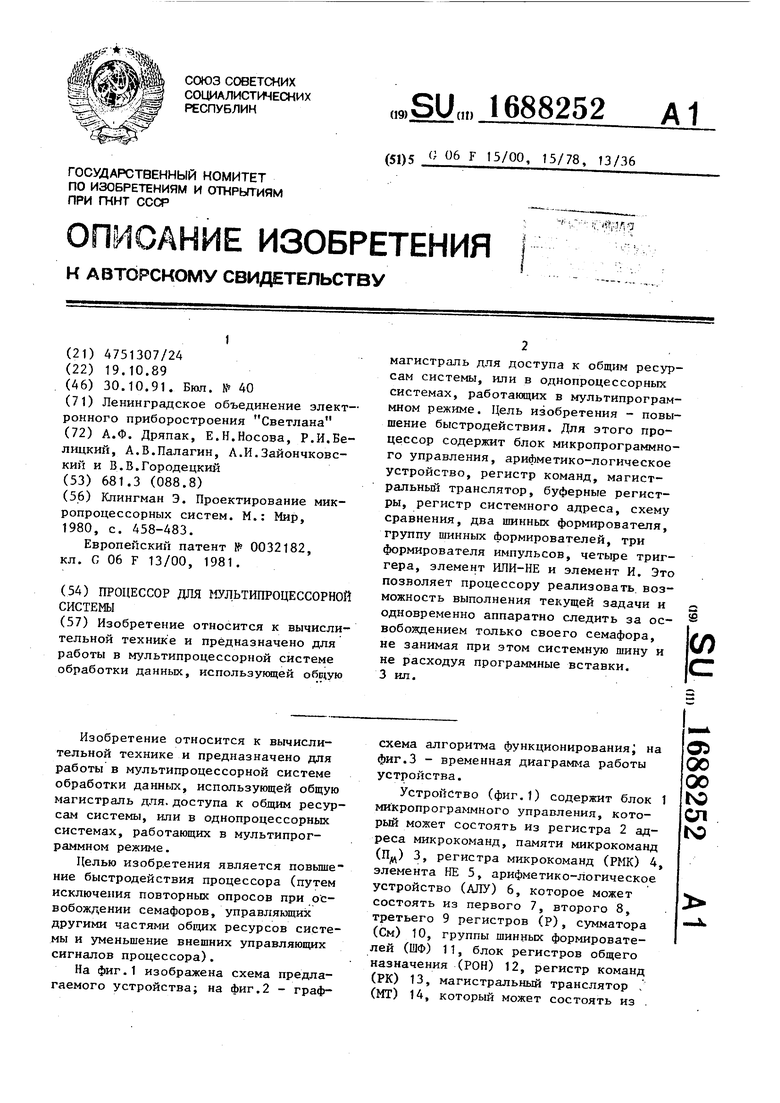

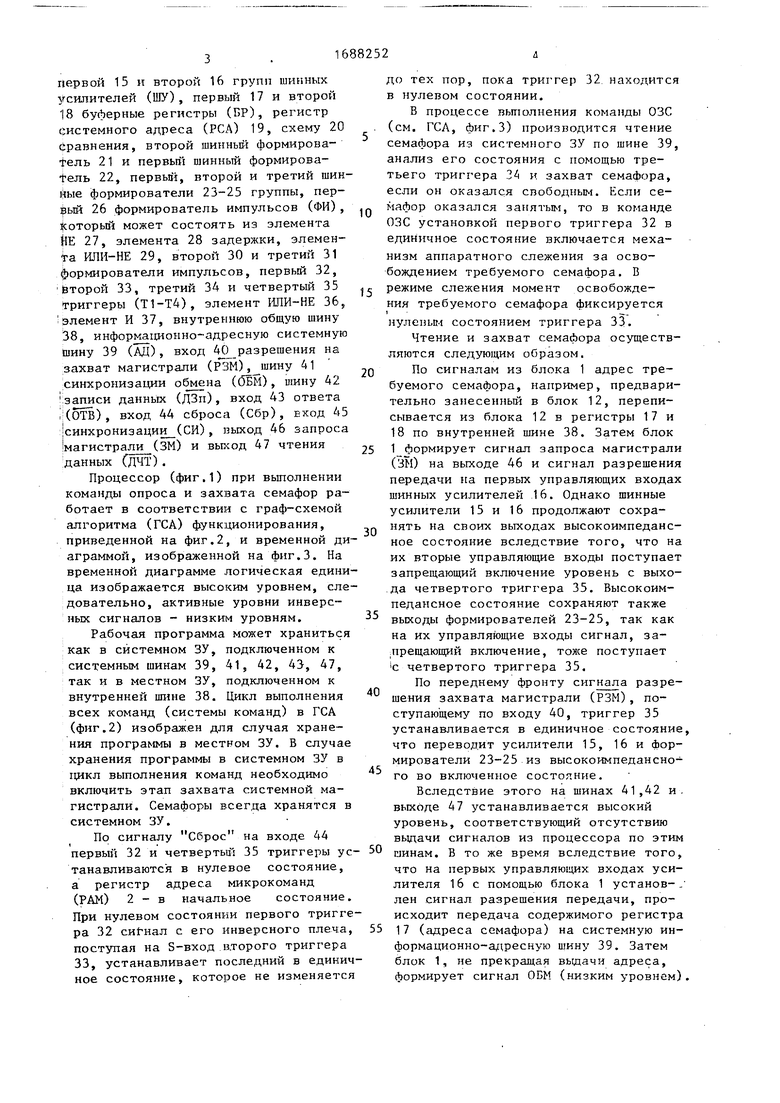

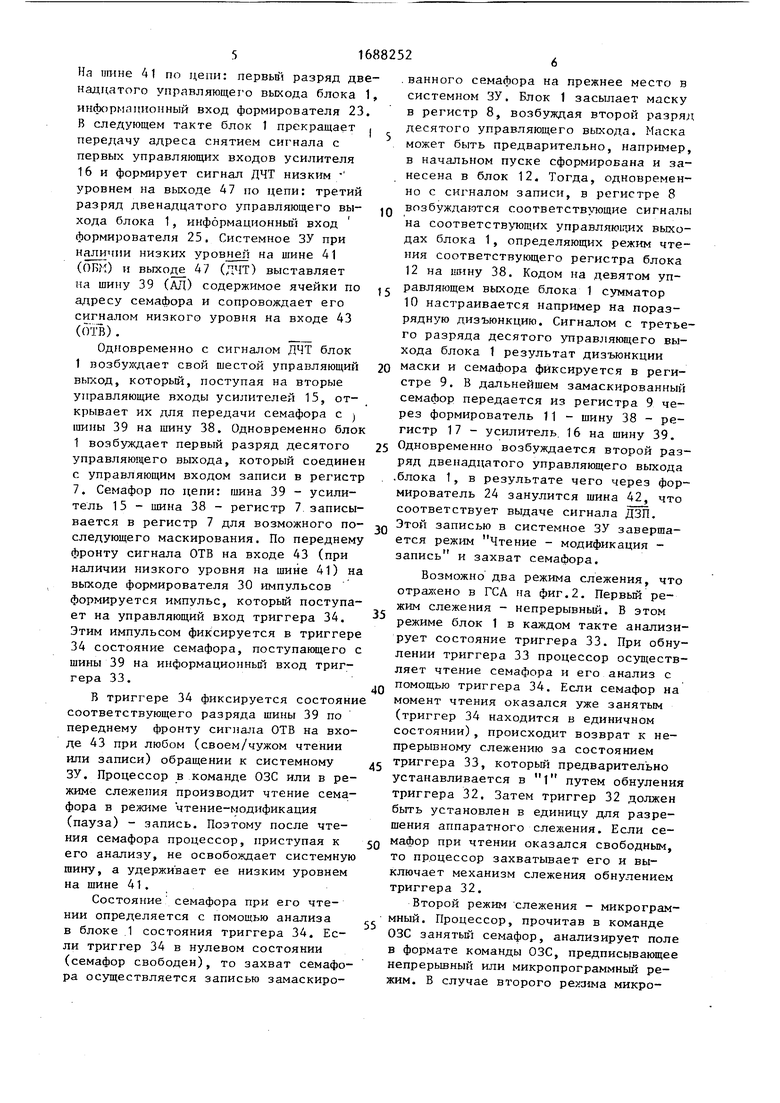

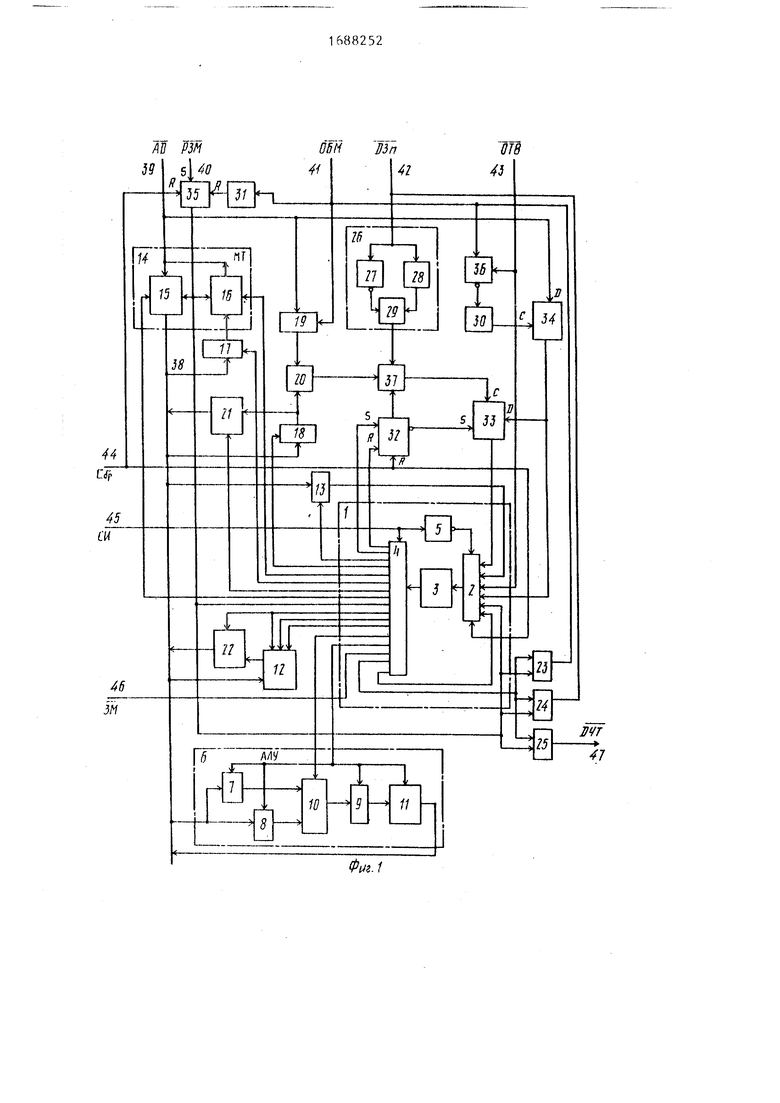

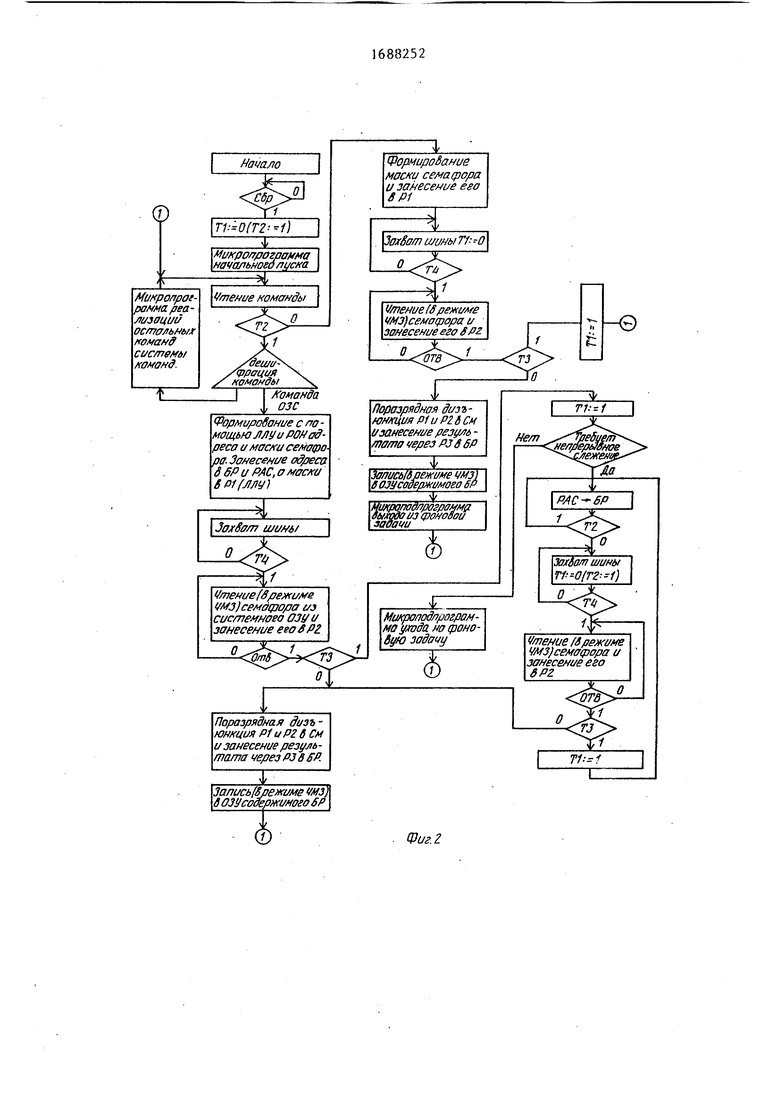

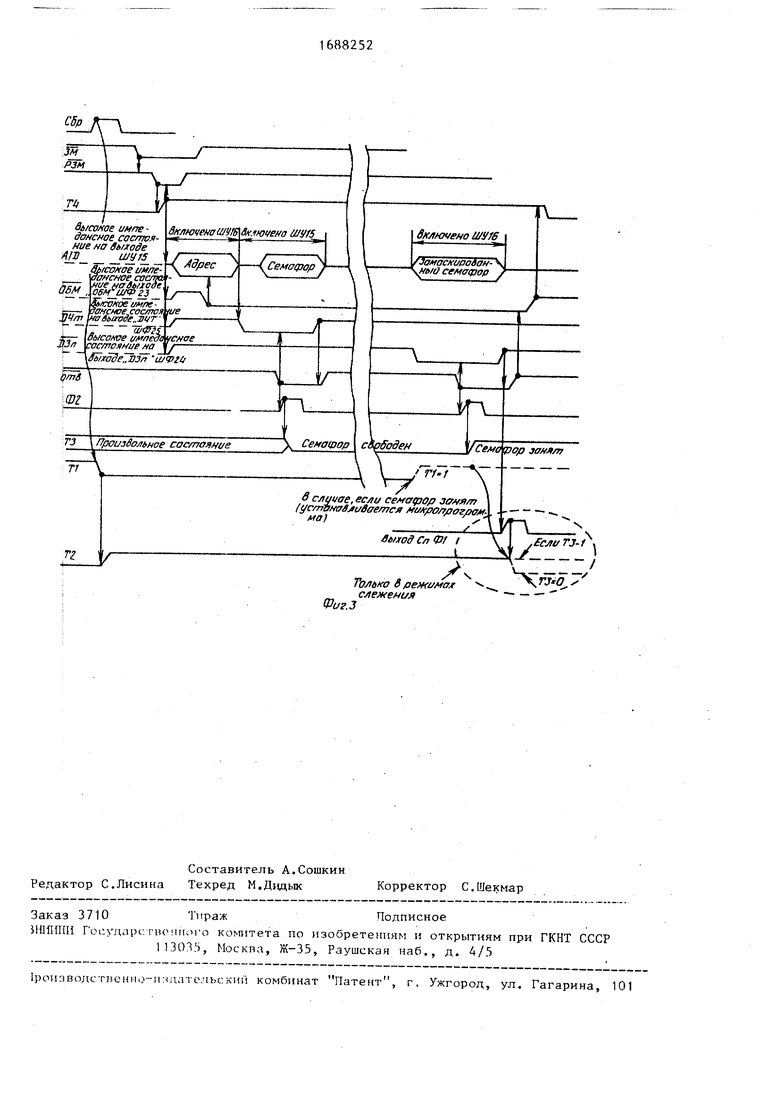

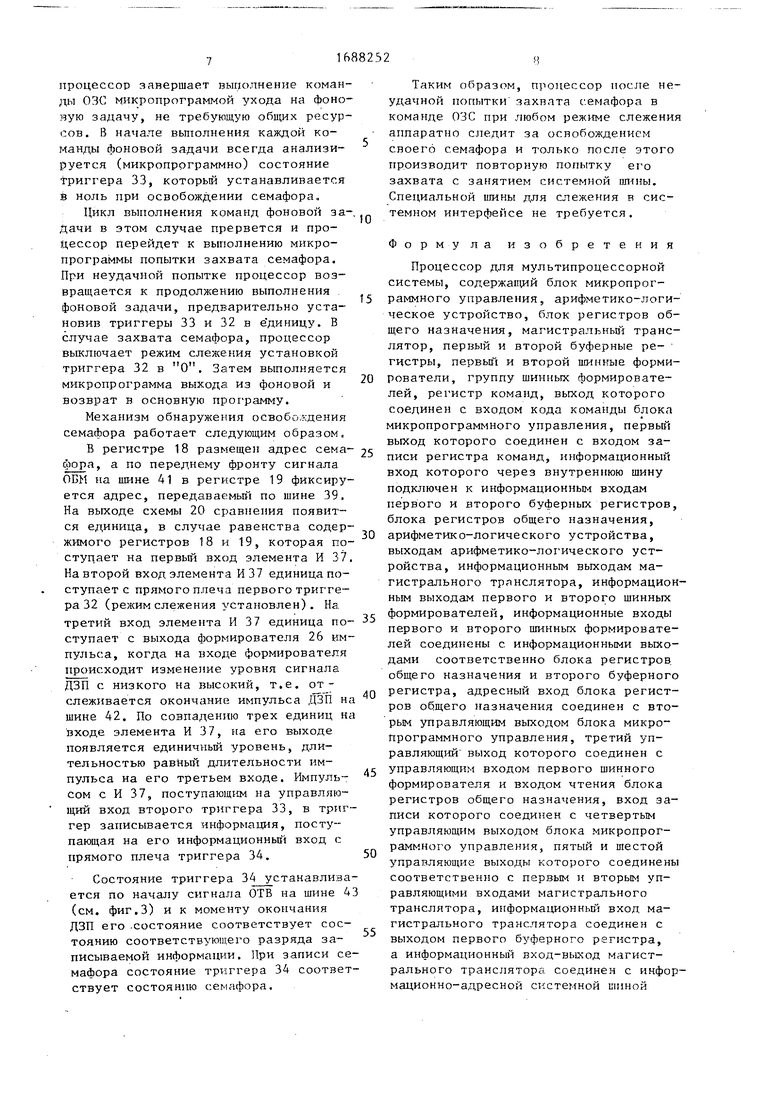

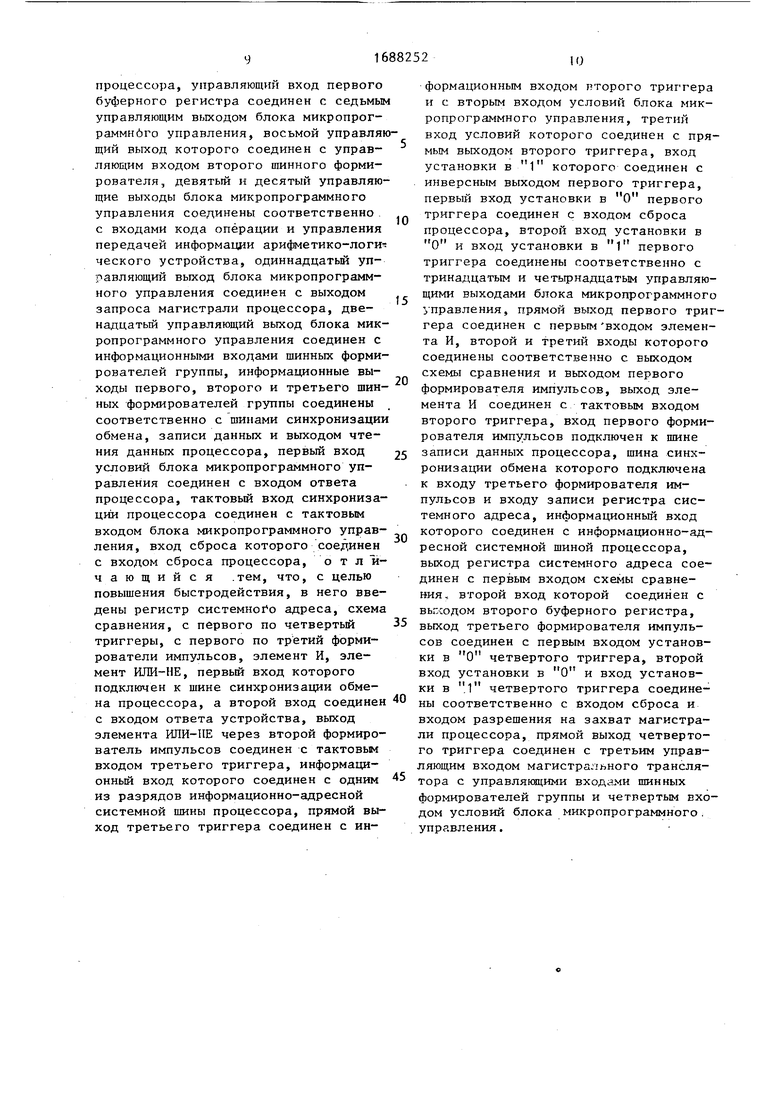

На фиг.1 изображена схема предлагаемого устройства; на фиг.2 - графсхема алгоритма функционирования , на фиг.З - временная диаграмма работы устройства.

Устройство (фиг.1) содержит блок 1 микропрограммного управления, который может состоять из регистра 2 адреса микрокоманд, памяти микрокоманд (П) 3, регистра микрокоманд (РМК) 4, элемента НЕ 5, арифметико-логическое устройство (АЛУ) 6, которое может состоять из первого 7, второго 8, третьего 9 регистров (Р), сумматора (См) 10, группы шинных формирователей (ШФ) 11, блок регистров общего назначения (РОН) 12, регистр команд (РК) 13, магистральный транслятор , (МТ) 14, который может состоять из

сг оо

00

го ел ю

цервой 15 и второй 16 групп шинных усилителей (ШУ), первый 17 и второй 18 буферные регистры (БР), регистр системного адреса (РСА) 19, схему 20 сравнения, второй шинный формирователь 21 и первый шинный формирователь 22, первый, второй и третий шинные формирователи 23-25 группы, первый 26 формирователь импульсов (ФИ), Который может состоять из элемента НЕ 27, элемента 28 задержки, элемента ИЛИ-НЕ 29, второй 30 и третий 31 формирователи импульсов, первый 32, второй 33, третий 34 и четвертый 35 триггеры (Т1-Т4), элемент ШШ-НЕ 36, элемент И 37, внутреннюю общую шину 38, информационно-адресную системную шину 39 (АД), вход 4р разрешения на захват магистрали (PIIM), шину 41 синхронизации обмена (бБМ), шину 42 записи данных (ДЗп), вход 43 ответа i(ОТВ), вход 44 сброса (Сбр), вход 45 синхронизации(СИ), пыход 46 запроса магистрали (ЗМ) и выход 47 чтения данных (ДЧТ).

Процессор (фиг.1) при выполнении команды опроса и захвата семафор работает в соответствии с граф-схемой алгоритма (ГСА) функционирования, приведенной на фиг.2, и временной диаграммой, изображенной на фиг.З. На временной диаграмме логическая единица изображается высоким уровнем, следовательно, активные уровни инверсных сигналов - низким уровням.

Рабочая программа может храниться как в системном ЗУ, подключенном к системным шинам 39, 41, 42, 43, 47, так и в местном ЗУ, подключенном к внутренней шине 38. Цикл выполнения всех команд (системы команд) в ГСА (фиг.2) изображен для случая хранения программы в местном ЗУ. В случае хранения программы в системном ЗУ в цикл выполнения команд необходимо включить этап захвата системной магистрали. Семафоры всегда хранятся в системном ЗУ.

По сигналу Сброс на входе 44 первый 32 и четвертый 35 триггеры ус танавливаются в нулевое состояние, а регистр адреса микрокоманд (РАМ) 2 - в начальное состояние. При нулевом состоянии первого триггера 32 сигнал с его инверсного плеча, поступая на S-вход аторого триггера 33, устанавливает последний в ецинич ное состояние, которое не изменяется

10

15

20

25

30

35

40

45

50

55

до тех пор, пока триггер 32 находится в нулевом состоянии.

В процессе выполнения команды ОЗС (см. ГСА, фиг.З) производится чтение семафора из системного ЗУ по шине 39, анализ его состояния с помощью третьего триггера 34 и захват семафора, если он оказался свободным. Если семафор оказался занятым, то в команде ОЗС установкой первого триггера 32 в единичное состояние включается механизм аппаратного слежения за освобождением требуемого семафора. В режиме слежения момент освобождения требуемого семафора Фиксируется нулевым состоянием триггера 33.

Чтение и захват семайора осуществляются следующим образом.

По сигналам из блока 1 адрес требуемого семафора, например, предварительно занесенный в блок 12, переписывается из блока 12 в регистры 17 и 18 по внутренней шине 38. Затем блок 1 формирует сигнал запроса магистрали (ЗМ) на выходе 46 и сигнал разрешения передачи на первых управляющих входах шинных усилителей 16. Однако шинные усилители 15 и 16 продолжают сохранять на своих выходах высокоимпеданс- ное состояние вследствие того, что на их вторые управляющие входы поступает запрещающий включение уровень с выхода четвертого триггера 35. Высокоим- педансное состояние сохраняют также выходы формирователей 23-25, так как на их управляющие входы сигнал, запрещающий включение, тоже поступает с четвертого триггера 35.

По переднему фронту сигнала разрешения захвата магистрали (РЗМ), поступающему по входу 40, триггер 35 устанавливается в единичное состояние, что переводит усилители 15, 16 и Формирователи 23-25 из высокоимпедансно- го во включенное состояние.

Вследствие этого на шинах 41,42 и выходе 47 устанавливается высокий уровень, соответствующий отсутствию выдачи сигналов из процессора по этим шинам. В то же время вследствие того, что на первых управляющих входах усилителя 16 с помощью блока 1 установ-- лен сигнал разрешения передачи, происходит передача содержимого регистра 17 (адреса семафора) на системную информационно-адресную шину 39. Затем блок 1, не прекращая выдачи адреса, формирует сигнал ОБМ (низким уровнем).

51

На шине 41 по цепи: первый разряд двнадцатого управляющего выхода блока информационный вход формирователя 23 В следующем такте блок 1 прекращает передачу адреса снятием сигнала с первых управляющих входов усилителя 16 и формирует сигнал ДЧТ низким уровнем на выходе 47 по цепи: третий разряд двенадцатого управляющего выхода блока 1, информационный вход формирователя 25. Системное ЗУ при наличии низких уровней на шине 41 ( и выходе 47 (ДЧТ) выставляет на шину 39 (АД) содержимое ячейки по адресу семаЛора и сопровождает его сигналом низкого уровня на входе 43

(ОТВ).

Одновременно с сигналом ДЧТ блок 1 возбуждает свой шестой управляющий выход, который, поступая на вторые управляющие входы усилителей 15, открывает их для передачи семафора с ) шины 39 на шину 38. Одновременно бло 1 возбуждает первый разряд десятого управляющего выхода, который соедине с управляющим входом записи в регист 7. Семафор по цепи: шина 39 - усилитель 15 - шина 38 - регистр 7 записывается в регистр 7 для возможного последующего маскирования. По переднем фронту сигнала ОТВ на входе 43 (при наличии низкого уровня на шине 41) н выходе формирователя 30 импульсов формируется импульс, которьй поступает на управляющий вход триггера 34. Этим импульсом фиксируется в триггер 34 состояние семафора, поступающего шины 39 на информационный вход триггера 33.

В триггере 34 фиксируется состояни соответствующего разряда шины 39 по переднему фронту сигнала ОТВ на входе 43 при любом (своем/чужом чтении или записи) обращении к системному ЗУ. Процессор в команде ОЗС или в режиме слежения производит чтение семафора в режиме чтение-модификация (пауза) - запись. Поэтому после чтения семафора процессор, приступая к его анализу, не освобождает системную шину, а удерживает ее низким уровнем на шине 41.

Состояние семафора при его чтении определяется с помощью анализа в блоке 1 состояния триггера 34. Если триггер 34 в нулевом состоянии (семафор свободен), то захват семафора осуществляется записью замаскиро

10

,

ванного семафора на прежнее место в системном ЗУ. Блок 1 засылает маску в регистр 8, возбуждая второй разряд десятого управляющего выхода. Маска может быть предварительно, например, в начальном пуске сформирована и занесена в блок 12. Тогда, одновременно с сигналом записи, в регистре 8 возбуждаются соответствующие сигналы на соответствующих управляющих выходах блока 1, определяющих режим чтения соответствующего регистра блока 12 на шину 38. Кодом на девятом упj равляющем выходе блока 1 сумматор 10 настраивается например на поразрядную дизъюнкцию. Сигналом с третьего разряда десятого управляющего выхода блока 1 результат дизъюнкции

20 маски и семабора фиксируется в регистре 9. В дальнейшем замаскированный семафор передается из регистра 9 через формирователь 11 - шину 38 - регистр 17 - усилитель 16 на шину 39.

25 Одновременно возбуждается второй разряд двенадцатого управляющего выхода .блока 1, в результате чего через формирователь 24 занулится шина 42, что соответствует выдаче сигнала ДЗП. Этой записью в системное ЗУ завершается режим Чтение - модификация - запись и захват семафора.

Возможно два режима слежения, что

30

5

0

отражено в ГСА на фиг.2. Первый режим слежения - непрерывный. В этом режиме блок 1 в каждом такте анализирует состояние триггера 33. При обнулении триггера 33 процессор осуществляет чтение семафора и его анализ с помощью триггера 34. Если семафор на момент чтения оказался уже занятым (триггер 34 находится в единичном состоянии), происходит возврат к непрерывному слежению за состоянием 5 триггера 33, который предварительно устанавливается в 1 путем обнуления триггера 32. Затем триггер 32 должен быть установлен в единицу для разрешения аппаратного слежения. Если се- майор при чтении оказался свободным, то процессор захватывает его и выключает механизм слежения обнулением триггера 32.

Второй режим слежения - микрограм- мный. Процессор, прочитав в команде ОЗС занятый семафор, анализирует поле в формате команды ОЗС, предписывающее непрерывный или микропрограммный режим. В случае второго режима микро0

5

процессор завершает выполнение команды ОЗС микропрограммой ухода на cboночую задачу, не требующую общих ресурсов. В начале выполнения каждой команды фоновой задачи всегда анализируется (микропрограммно) состояние триггера 33, который устанавливается и ноль при освобождении семафора о

Цикл выполнения команд фоновой за-. Дачи в этом случае прервется и профессор перейдет к выполнению микропрограммы попытки захвата семафора. При неудачной попытке процессор возвращается к продолжению выполнения фоновой задачи, предварительно установив триггеры 33 и 32 в единицу. В случае захвата семафора, процессор выключает режим слежения установкой триггера 32 в О. Затем выполняется микропрограмма выхода из фоновой и возврат в основную программу.

Механизм обнаружения освобождения семафора работает следующим образом,

В регистре 18 размещен адрес семафора, а по переднему фронту сигнала ОБМ на шине 41 в регистре 19 фиксируется адрес, передаваемый по шине 39. На выходе схемы 20 сравнения появится единица, в случае равенства содержимого регистров 18 и 19, которая поступает на первый вход элемента И 37. На второй вход элемента И 37 единица поступает с прямого плеча первого триггера 32 (режим слежения установлен). На третий вход элемента И 37 единица поступает с выхода формирователя 26 им- пульса, когда на входе формирователя происходит изменение уровня сигнала ДЗП с низкого на высокий, т.е. отслеживается окончание импульса ДЗП на шине 42. По совпадению трех единиц на входе элемента И 37, на его выходе появляется единичный уровень, длительностью равный длительности импульса на его третьем входе. Импульсом с И 37, поступающим на управляющий вход второго триггера 33, в триггер записывается информация, поступающая на его информационный вход с прямого плеча триггера 34.

Состояние триггера 34 устанавлива- ется по началу сигнала ОТВ на шине 43 (см. фиг.З) и к моменту окончания ДЗП его состояние соответствует состоянию соответствующего разряда записываемой информации. При записи семафора состояние триггера 34 соответствует состоянию семафора.

0

5

0

5

0

5

0

5

Таким образом, процессор после неудачной попытки захвата семафора в команде ОЗС при любом режиме слежения аппаратно следит за освобождением своего семафора и только после этого производит повторную попытку его захвата с занятием системной шины. Специальной шины для слежения в системном интерфейсе не требуется.

Формула изобретения

Процессор для мультипроцессорной системы, содержащий блок микропрограммного управления, арифметико-логическое устройство, блок регистров общего назначения, магистральный транслятор, первый и второй буферные регистры, первый и второй шинные формирователи, группу шинных формирователей, регистр команд, выход которого соединен с входом кода команды блока микропрограммного управления, первый выход которого соединен с входом записи регистра команд, информационный вход которого через внутреннюю шину подключен к информационным входам первого и второго буферных регистров, блока регистров общего назначения, арифметико-логического устройства, выходам арифметико-логического устройства, информационным выходам магистрального транслятора, информационным выходам первого и второго шинных формирователей, информационные входы первого и второго шинных формирователей соединены с информационными выходами соответственно блока регистров общего назначения и второго буферного регистра, адресный вход блока регистров общего назначения соединен с вторым управляющим выходом блока микропрограммного управления, третий управляющий выход которого соединен с управляющим входом первого шинного формирователя и входом чтения блока регистров общего назначения, вход записи которого соединен с четвертым управляющим выходом блока микропро - раммного управления, пятый и шестой управляющие выходы которого соединены соответственно с первым и вторым управляющими входами магистрального транслятора, информационный вход магистрального транслятора соединен с выходом первого буферного регистра, а информационный вход-выход магистрального транслятора соединен с информационно-адресной системной шиной

процессора, управляющий вход первого буферного регистра соединен с седьмым управляющим выходом блока микропрог- раммнбго управления, восьмой управляющий выход которого соединен с управляющим входом второго шинного формирователя, девятый и десятый управляющие выходы блока микропрограммного управления соединены соответственно с входами кода операции и управления передачей информации арифметико-лог№ ческого устройства, одиннадцатый уп- павляющий выход блока микропрограммного управления соединен с выходом запроса магистрали процессора, двенадцатый управляющий выход блока микропрограммного управления соединен с информационными входами шинных формирователей группы, информационные выходы первого, второго и третьего шинных формирователей группы соединены соответственно с шинами синхронизации обмена, записи данных и выходом чтения данных процессора, первый вход условий блока микропрограммного управления соединен с входом ответа процессора, тактовый вход синхронизации процессора соединен с тактовым входом блока микропрограммного управления, вход сброса которого соединен с входом сброса процессора, о т л и- чающийся тем, что, с целью повышения быстродействия, в него введены регистр системного адреса, схема сравнения, с первого по четвертый триггеры, с первого по третий формирователи импульсов, элемент И, элемент ИЛИ-НЕ, первый вход которого подключен к шине синхронизации обмена процессора, а второй вход соединен с входом ответа устройства, выход элемента ИЛИ-НЕ через второй формирователь импульсов соединен с тактовым входом третьего триггера, информационный вход которого соединен с одним из разрядов информационно-адресной системной шины процессора, прямой выход третьего триггера соединен с ин

0

5

0

55 5

0

0

формационным входом рторого триггера и с вторым входом условий блока микропрограммного управления, третий вход условий которого соединен с прямым выходом второго триггера, вход установки в 1 которого соединен с инверсным выходом первого триггера, первый вход установки в О первого триггера соединен с входом сброса процессора, второй вход установки в О и вход установки в 1 первого триггера соединены соответственно с тринадцатым и четырнадцатым управляющими выходами блока микропрограммного управления, прямой выход первого триггера соединен с первым входом элемента И, второй и третий входы которого соединены соответственно с выходом схемы сравнения и выходом первого формирователя импульсов, выход элемента И соединен с тактовым входом второго триггера, вход первого формирователя импульсов подключен к шине записи данных процессора, шина синхронизации обмена которого подключена к входу третьего формирователя импульсов и входу записи регистра системного адреса, информационный вход которого соединен с информационно-адресной системной шиной процессора, выход регистра системного адреса соединен с первым входом схемы сравнения, второй вход которой соединен с выходом второго буферного регистра, выход третьего формирователя импульсов соединен с первым входом установки в О четвертого триггера, второй вход установки в О и вход установки в 1м четвертого триггера соединены соответственно с входом сброса и входом разрешения на захват магистрали процессора, прямой выход четвертого триггера соединен с третьим управляющим входом магистрального транслятора с управляющими ВХОДАМИ шинных формирователей группы и четвертым входом условий блока микропрограммного управления.

Z52H89L

Начало

(T2-1) |

микропрограмма начального пуска

Н

Формирование с па - мощью ЛЛУи РОН адреса и маски семафо ра. Занесение адреса д 6Р и РАС, о маски SPIfMflyl

Чтение (Sрежиме VM3) семафора из системного ОЗУ ч/ занесение eeo&PZ

Поразрядная диэъ - юнкция Р1иР26 См и занесение резу ль - тата через PJSfffl.

Запись 8режимб УМЗ) д ОЗУ содержимого 6Р

Формирование маски семафора и занесение его SP1

tyxSam шины 7У----11 О

VmeHuefSрежиме чмз)семасрора и занесение его SPZ

I I

Не/л

Залш{брежиме W3) бОЭУсоаержимоео бР

. чграмма т из фоновой

7W

Чтение /6режиме VM3) семафора и занесение его SPZ

Cfffl

JM

РЗМ

Til

Y

ключено ШЩвкчнмет U/yf5

/ Адрес

Л

Семафор

....jKoeuM/тс- Зансное состоя ие KST-выходе..зчг

Высокое 1/меао усное состояние на г-

Дб/ходе пзл а/Фгь

ft

Семафор

77

в c/iut/ae, если семафор з0ня/тг {усгпбнааливается милролрог/юм-у

ма)

тл

П

Фиг.З

I включено

fJaMacKt/роЛан- нью семафор

(f

свободен

(Семо pop заня/п

, 77-/

, если семафор з0ня/тг ивается милролрог/юм-у

тл

выход СпФ I I

З

Уч

Только в режимах ч-. слежения

N

. }

--х7

rj Gl

Авторы

Даты

1991-10-30—Публикация

1989-10-19—Подача