Изобретение относится к импульсной технике, может быть использовано в счетных устройствах вычислительной техник и систем управления, содержащих встроенные системы контроля и диагностики.

Известно счетное устройство (а.с. №1499710 от 08.12.87, Н 03 К 23/40 "Счетное устройство". Л.Б.Егоров, Г.И.Шишкин), содержащее управляющий D-триггер и в каждом разряде D-триггер, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент ИЛИ-НЕ, элемент ИЛИ, связи на дополнительные входы элементов ИЛИ-НЕ и ИЛИ каждою разряда.

Недостатком данного устройства является отсутствие контроля при неустановке в ноль любого разряда счетчика. Кроме того, при несанкционированном переключении любого из разрядных D-триггеров во время действия или отсутствия счетного импульса нет контроля исходного состояния разрядных D-триггеров, что снижает надежность функционирования устройства.

В качестве прототипа был выбран счетчик импульсов в коде Грея с контролем (а.с. СССР 1697583, Н 03 К 21/40 "Счетчик импульсов в коде Грея с контролем". Л.Б.Егоров, Г.И.Шишкин), содержащий шину импульсов, шину обнуления, управляющие и контрольный D-триггеры со статическим управлением, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, инвертор, элемент ИЛИ-НЕ, D-триггер с инверсным тактовым входом, контрольный выход. Счетчик состоит из n разрядов, где n>2, каждый из которых содержит D-триггер, элемент ИЛИ-НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и логический элемент, выполненный в каждом разряде, начиная со второго, в виде элемента ИЛИ.

Недостатком данного счетчика является низкая надежность функционирования, связанная с тем, что для контроля исходного состояния разрядных триггеров используются элементы схемы, участвующие в формировании счета.

Задачей, на решение которой направлено заявляемое устройство, является повышение надежности функционирования за счет увеличения полноты контроля.

Поставленная задача решается тем, что в пересчетном устройстве с контролем, содержащем два управляющих D-триггера со статическим управлением, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, контрольный выход и n разрядов, где n>2, каждый из которых содержит D-триггер, элемент ИЛИ-НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и логический элемент, выполненный в каждом разряде, начиная со второго, в виде элемента ИЛИ, при этом в каждом разряде первый и второй входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с информационным входом и прямым выходом D-триггера данного разряда, в каждом разряде, кроме первого, первый вход элемента ИЛИ-НЕ соединен с инверсным выходом D-триггера предыдущего разряда, прямой выход D-триггера которого соединен с первым входом логического элемента последующего разряда, второй вход логического элемента ИЛИ-НЕ того же разряда с выходом логического элемента предыдущего разряда, в каждом разряде, кроме последнего, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ последующего разряда, первый и второй входы элемента ИЛИ-НЕ первого разряда соединены соответственно с инверсным и тактовым входом первого управляющего D-триггера, прямой выход которого соединен с первым входом логического элемента первого разряда и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с прямым выходом второго управляющего D-триггера, а выход соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого подключен к шине счетных импульсов, тактовому входу второго управляющего D-триггера, второй вход логического элемента первого разряда соединен с тактовым входом первого управляющего D-триггера, информационный вход которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первого разряда и информационным входом второго управляющего D-триггера, вход сброса которого подключен ко входу сброса D-триггера каждого разряда, тактовый вход которого соединен с выходом элемента ИЛИ-НЕ данного разряда, согласно изобретению в него введены D-триггер дополнительного контроля, элемент И, содержащий n входов, первый вход которого соединен с информационным входом D-триггера первого разряда, второй вход - соответственно с информационным входом D-триггера второго разряда, n-й вход - соответственно с информационным входом D-триггера n-разряда, выход элемента И соединен с тактовым входом D-триггера дополнительного контроля, информационный вход которого подключен к шине питания, а установочные R- и S- входы соединены с шиной обнуления и со вторым входом элемента ИЛИ, первый вход которого соединен с инверсным выходом D-триггера дополнительного контроля, выход элемента ИЛИ подключен к R-входу D-триггера каждого разряда, к R-входу первого управляющего D-триггера, к установочным R- и S-входам второго управляющего D-триггера и D-триггера контроля, ко второму входу элемента ИЛИ-НЕ, первый вход которого соединен с шиной счетных импульсов.

Технический результат достигается за счет введения новых конструктивных признаков, обеспечивающих дополнительный контроль состояния всех разрядных D-тригтеров в исходном состоянии и формирования сигнала блокировки счета в случае отрицательного результата контроля.

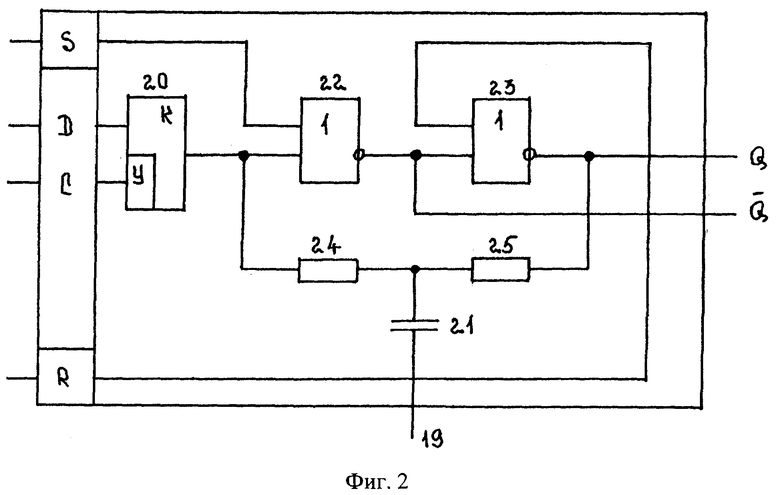

На фиг.1 представлена схема предлагаемого пересчетного устройства с контролем.

Устройство содержит первый, второй управляющие D-триггеры 1, 2 со статическим управлением, разрядные D-триггеры 3.1-3.4, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 4.1-4.3, 12, 13, элементы ИЛИ-НЕ 5.1-5.4, 11, элементы ИЛИ 6.1-6.3, D-триггер контроля 7, D-триггер дополнительного контроля 8, элемент И 9, инвертор НЕ 10, элемент ИЛИ 14, шину 15 контрольного выхода, шину 16 питания, шину 17 счетных импульсов, шину 18 обнуления, шину 19 нулевого потенциала.

Первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 4.1, 4.2... соединены соответственно с информационными входами D-триггеров 3.1, 3.2..., соответствующими входами элемента И 9, выходами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 4.2...

Первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4.3 соединен с выходом элемента НЕ 10 и входом элемента И 9.

Второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4.3 соединен с прямым выходом D-триггера 3.3.

Вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 4.1, 4.2... соединены соответственно с прямыми выходами D-триггеров 3.1, 3.2... и первыми входами элементов ИЛИ 6.2...

Инверсные выходы D-триггеров 1, 3.1, 3.2...3.3 соединены соответственно с первыми входами элементов ИЛИ-НЕ 5.1, 5.2...5.3, 5.4. Выходы элементов ИЛИ-НЕ 5.1, 5.2...5.3, 5.4 соединены с тактовыми входами D-триггеров 3.1, 3.2...3.3, 3.4. Выход элемента ИЛИ-НЕ 5.1 соединен со вторыми входами элементов ИЛИ-НЕ 5.2 и ИЛИ 6.2. Выход элемента ИЛИ-НЕ 5.3 соединен со вторым входом элемента ИЛИ-НЕ 5.4.

Выход элемента ИЛИ 6.1 соединен с третьими входами элементов ИЛИ-НЕ 5.2 и ИЛИ 6.2.

Первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12 соединен с прямым выходом управляющего D-триггера 1 и первым входом элемента И 6.1. Второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12 соединен с прямым выходом D-триггера 2, а выход с первым входом ИСКЛЮЧАЮЩЕЕ ИЛИ 13, выход которого соединен с тактовым входом D-триггера контроля 7, а второй вход с шиной 17 счетных импульсов, которая соединена с тактовым входом D-триггера 2 и первым входом элемента ИЛИ-НЕ 11. Выход элемента ИЛИ-НЕ 11 соединен с тактовым входом D-триггера 1, вторым входом элемента ИЛИ-НЕ 5.1 и вторым входом элемента И 6.1. Информационный вход D-триггера 7 соединен с шиной 16 питания, а инверсный выход D-триггера 7 с контрольным выходом 15.

Шина 18 обнуления соединена с входами R и S установки D-триггера 8 и вторым входом элемента ИЛИ 14. Первый вход элемента ИЛИ 14 соединен с инверсным выходом D-триггера 8, счетный вход которого соединен с выходом элемента И 9, а информационный вход соединен с шиной 16 питания. Выход элемента ИЛИ 14 соединен с входами R установки D-триггеров 1, 3.1, 3.2,...3.3, 3.4, с входами R и S установки D-триггеров 7,2 со вторым входом элемента ИЛИ-НЕ 11.

Управляющие D-триггеры 1 и 2, разрядные D-триггеры 3.1, 3.2,...3.3, 3.4, D-триггеры 7 и 8 построены на основе элементов ИЛИ-НЕ с помехозащищающими RC-элементами в цепи обратной связи и двунаправленным ключом. При этом управляющий D-триггер 2, D-триггер контроля 7 и D-триггер 8 построены по схеме с R- и S-входами. Управляющий D-триггер 1, разрядные D-триггеры 3.1, 3.2,...3.3, 3.4 построены по схеме с R-входом.

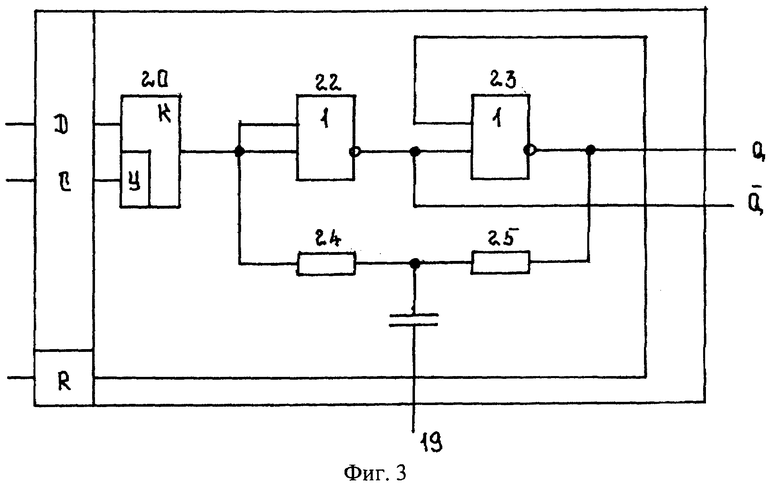

Схема D-триггера с R- и S-входами установки представлена на фиг.2 и является схемой со статическим управлением, содержит элементы ИЛИ-НЕ 22, 23, первый и второй резисторы 24, 25, конденсатор 21, двунаправленный ключ 20. Вход ключа 20 является информационным входом D-триггера, управляющий вход - тактовым входом D-триггера. Выход соединен со вторым входом элемента ИЛИ-НЕ 22. Первый вход элемента ИЛИ-НЕ 22 является установочным S-входом D-триггера, выход соединен с первым входом элемента ИЛИ-НЕ 23 и является инверсным выходом D-триггера. Второй вход элемента ИЛИ-НЕ 23 является установочным R-входом D-триггера. Выход элемента ИЛИ-НЕ 23 является прямым выходом D-триггера.

Первый вывод конденсатора 21 соединен со вторым входом элемента ИЛИ-НЕ 22 через резистор 24 и с выходом элемента ИЛИ-НЕ 23 через резистор 25. Второй вывод конденсатора 21 соединен с шиной 19 нулевого потенциала устройства.

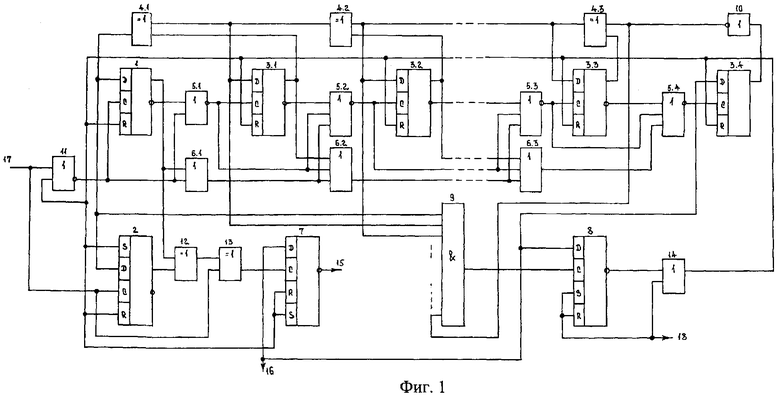

Схема D-триггера с R-входом установки представлена на фиг.3. Схема D-триггера, представленная на фиг.3, отличается от схемы D-триггера на фиг.2 наличием одного установочного R-входа, соединением первого и второго входов элемента ИЛИ-НЕ 22.

Устройство работает следующим образом.

После подачи на шину 18 обнуления импульса положительной полярности и прохождения импульса через элемент ИЛИ 14 разрядные D-триггеры 3.1, 3.2,...3.3, 3.4, D-триггеры управления 1, 2 и D-триггер контроля 7, а также D-триггер 8 устанавливаются в исходное нулевое состояние, характеризующееся наличием сигнала "логический 0" на прямом выходе (Q) и сигнала "логическая 1" на инверсном ( ). В D-триггерах 2, 7, 8 при одновременном воздействии сигналов "логическая 1" на R- и S-входы на их прямых и на инверсных выходах действуют сигналы "логический 0". В процессе действия импульса обнуления на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4.1 действует такой же сигнал, как и на выходе инвертора 10. В процессе действия импульса обнуления на выходе инвертора 10 действует сигнал "логическая 1", и, следовательно, этот сигнал присутствует и на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4.1.

). В D-триггерах 2, 7, 8 при одновременном воздействии сигналов "логическая 1" на R- и S-входы на их прямых и на инверсных выходах действуют сигналы "логический 0". В процессе действия импульса обнуления на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4.1 действует такой же сигнал, как и на выходе инвертора 10. В процессе действия импульса обнуления на выходе инвертора 10 действует сигнал "логическая 1", и, следовательно, этот сигнал присутствует и на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4.1.

В отсутствии счетного импульса (сигнал "логический 0" на шине 17) на тактовом входе управляющего D-триггера 1 формируется сигнал "логическая 1". В этом случае сигнал "логическая 1" с информационного входа D-триггера 1 проходит на его прямой выход. На инверсном выходе D-триггера 1 сигнал "логический 0". Следовательно, на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 12, 13 и на тактовом выводе D-триггера 7 действует сигнал "логическая 1". В результате по окончании импульса обнуления D-триггер 7 устанавливается в состояние "логический 0", на контрольном выходе 15 формируется сигнал "логический 0".

При установке всех разрядов устройства в нулевое состояние на входах элемента И 9 присутствуют сигналы "логическая 1", следовательно, на выходе элемента И 9 формируется сигнал "логическая 1", который поступает па тактовый вход D-триггера 8 и изменяет его состояние, на инверсном выходе D-триггера 8 формируется сигнал "логический 0".

После снятия сигнала обнуления по шине 18 на R-входах D-триггеров 1, 2, 3.1, 3.2...3.3, 3.4 и на втором входе элемента ИЛИ-НЕ 11 устанавливается сигнал "логический 0".

При поступлении первого счетного импульса положительной полярности по шине 17 происходит переключение в состояние "логическая 1" D-триггера 3.1, так как счетный импульс проходит на выход элемента 5.1, на информационном входе D-триггера 3.1 - сигнал "логическая 1". Сигнал "логический 0" на инверсном выходе D-триггера 3.1 готовит к переключению элемент ИЛИ-НЕ 5.2 второго разряда по его первому входу, сигнал "логическая 1" на прямом выходе D-триггера 3.1 изменяет полярность сигнала на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4.1, а значит, на информационных входах D-триггеров 1, 2 присутствует сигнал "логический О". Во время действия счетного импульса управляющий D-триггер 1 не переключается под действием сигнала на его информационном входе, так как на тактовом входе D-триггера 1 - сигнал "логический 0". Управляющий D-триггер 2 под действием сигнала на его информационном входе переключается в состояние "логический 0". На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12 появляется сигнал "логический 0", на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 сохраняется сигнал "логическая 1". Сигнал "логический 0" на первом входе элемента И 9 формирует сигнал "логический 0" на тактовом входе D-триггера 8.

В паузе между первым и вторым счетными импульсами управляющий D-триггер 1 воспринимает информацию с элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4.1, т.е. устанавливается в состояние "логический 0". Состояние управляющего D-триггера 2 ("логическая I") сохраняется. Изменение сигнала на прямом выходе управляющего D-триггера 1 и на первом входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12 компенсируется изменением полярности сигнала на втором входе элемента ИСКЛЮЧАЮЩЕЕЕ ИЛИ 13. В результате на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 и тактовом входе D-триггера 7 сохраняется сигнал "логическая 1". На контрольном выходе 15 сохраняется сигнал "логический 0".

При поступлении по шине 17 второго и последующих счетных импульсов происходит переключение разрядов устройства в соответствии с логикой кода Грея - нечетными импульсами переключается D-триггер 3.1 первого разряда, четными переключаются старшие разряды устройства, при этом переключение осуществляется в разряде, следующем за младшим, находящимся в состоянии "логическая 1".

Рассмотрим работу схемы устройства в случае, если один или несколько его разрядов не установились в исходное состояние на начальном этапе его работы. В этом случае до момента окончания импульса обнуления по шине 18 на одном или нескольких выходах D-триггеров 3.1, 3.2...3.3, 3.4 появляется сигнал "логическая 1", что приводит к появлению сигнала "логический 0" на одном или нескольких входах элемента И 9, что приводит к сохранению сигнала "логическая 1" на инверсном выходе триггера 8. В результате после окончания импульса обнуления по шине 18 на выходе элемента ИЛИ 14 сохраняется уровень "логическая 1", который принудительно удерживает в исходном состоянии разрядные триггеры и блокирует прохождение счетных импульсов через элемент ИЛИ-НЕ 11.

Рассмотрим, как обнаруживаются сбои в работе устройства, начиная с момента действия по шине 17 первого счетного импульса. Во время действия счетного импульса на шине 17 присутствует сигнал "логическая 1", управляющий D-триггер 2 воспринимает сигнал с элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4.1 первого разряда. Если во время действия счетного импульса в любом такте работы счета произошло переключение не одного, а двух, четырех, т.е. любого четного количества разрядов, или ни один разряд устройства не переключился, на прямом выходе управляющего D-триггера 2 формируется сигнал, противоположный сигналу на прямом выходе управляющего D-триггера 1. На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12 формируется сигнал "логическая 1", а на выходе ИСКЛЮЧАЮЩЕЕ ИЛИ 13 сигнал "логический 0". Этот сигнал на тактовом входе D-триггера 7 переключает его в состояние "логический 0" (сигнал "логическая 1" на контрольном выходе 15 устройства). В паузе между счетными импульсами на шине 17 действует сигнал "логический 0", сигнал с элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4.1 воспринимается управляющим D-триггером 1. Если во время пауз между счетными импульсами произошло переключение нечетного количества разрядов счетчика, на прямом выходе D-триггера фиксируется сигнал того же логического уровня, что и на прямом выходе управляющего D-триггера 2, что приводит к появлению сигнала "логический 0" на тактовом входе D-триггера контроля 7 и вызывает его переключение в состояние "логический 0".На контрольном выходе 15 появляется сигнал ошибки - уровень "логическая 1".

По своему назначению и функциональным возможностям предлагаемое устройство аналогично вышеуказанному прототипу. Однако в прототипе элементы, которые контролируют исходное состояние разрядных триггеров, участвуют в счете.

Таким образом, предлагаемое устройство по сравнению с прототипом обладает повышенной полнотой контроля за счет введения дополнительного элемента И 9, несущего информацию о состоянии всех разрядных триггеров на начальном этапе работы счетчика и блокировке работы всего устройства D-триггером дополнительного контроля 8 в случае отрицательного результата контроля начального состояния разрядных триггеров, а также введением элемента ИЛИ-НЕ11, управление вторым входом которого также производится по результатам анализа исходного состояния, что повышает надежность функционирования устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ С КОНТРОЛЕМ | 1989 |

|

SU1697583A1 |

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ С КОНТРОЛЕМ | 1997 |

|

RU2129332C1 |

| ПРЕОБРАЗОВАТЕЛЬ БИИМПУЛЬСНОГО КОДА В БИНАРНЫЙ КОД | 2004 |

|

RU2258305C1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

| ТАЙМЕР С КОНТРОЛЕМ | 1995 |

|

RU2113007C1 |

| Информационное устройство | 1987 |

|

SU1564066A1 |

| Ячейка однородной вычислительной среды | 1986 |

|

SU1386987A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ | 2005 |

|

RU2298624C2 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1506570A1 |

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ | 1982 |

|

SU1101159A1 |

Изобретение относится к импульсной технике, может быть использовано в счетных устройствах вычислительной техники и систем управления, содержащих схемы контроля и диагностики. Техническим результатом является повышение надежности функционирования за счет увеличения полноты контроля. Указанный результат достигается за счет введения D-триггера дополнительного контроля, элемента И, содержащего n входов, элемента ИЛИ, элемент ИЛИ-НЕ. Устройство содержит управляющие D-триггеры, D-триггеры, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, элементы ИЛИ-НЕ, элементы ИЛИ, D-триггер, инвертор, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, шину контрольного выхода, шину питания, шину счетных импульсов, шину обнуления, шину нулевого потенциала. 3 ил.

Пересчетное устройство с контролем, содержащее два управляющих D-триггера со статическим управлением, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, контрольный выход и n-разрядов, где n>2, каждый из которых содержит D-триггер, элемент ИЛИ-НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и логический элемент, выполненный в каждом разряде в виде элемента ИЛИ, в каждом разряде первый и второй входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с информационным входом и прямым выходом D-триггера данного разряда, в каждом разряде, кроме первого, первый вход элемента ИЛИ-НЕ соединен с инверсным выходом D-триггера предыдущего разряда, прямой выход которого соединен с первым входом логического элемента последующего разряда, в каждом разряде, кроме последнего, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ последующего разряда, первый и второй входы элемента ИЛИ-НЕ первого разряда соединены соответственно с инверсными выходом и тактовым входом первого управляющего D-триггера, прямой выход которого соединен с первым входом логического элемента первого разряда и первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с прямым выходом второго управляющего D-триггера, а выход - с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого подключен к шине счетных импульсов, тактовому входу второго управляющего D-триггера, второй вход логического элемента первого разряда соединен с тактовым входом первого управляющего D-триггера, информационный вход которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первого разряда и информационным входом второго управляющего D-триггера, вход сброса которого подключен к входу сброса D-триггера каждого разряда, тактовый вход которого соединен с выходом элемента ИЛИ-НЕ данного разряда, в каждом разряде вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с прямыми выходами D-триггеров и первыми входами логических элементов, выход элемента ИЛИ-НЕ соединен со вторыми входами элемента ИЛИ-НЕ и логического элемента последующего разряда, выход логического элемента предыдущего разряда соединен с третьими входами элемента ИЛИ-НЕ и логического элемента последующего разряда, выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с тактовым входом D-триггера контроля, выход первого элемента ИЛИ-НЕ соединен с тактовым входом первого управляющего D-триггера, вторым входом элемента ИЛИ-НЕ первого разряда и вторым входом логического элемента первого разряда, информационный вход D-триггера контроля соединен с шиной питания, а инверсный выход D-триггера контроля - с контрольным выходом устройства, причем в процессе действия импульса обнуления на выходе инвертора действует сигнал «логическая 1», отличающееся тем, что в него введены D-триггер дополнительного контроля, элемент И, содержащий n-входов, первый вход которого соединен с информационным входом D-триггера первого разряда, второй вход - с информационным входом D-триггера второго разряда, n-й вход - с информационным входом D-тригтера n-разряда, выход элемента И соединен с тактовым входом D-триггера дополнительного контроля, информационный вход которого подключен к шине питания, а установочные R и S-входы соединены с шиной обнуления и со вторым входом элемента ИЛИ, первый вход которого соединен с инверсным выходом D-триггера дополнительного контроля, выход элемента ИЛИ подключен к R-входу D-триггера каждого разряда, к R-входу первого управляющего D-триггера, к установочным R и S-входам второго управляющего D-триггера и D-триггера контроля, ко второму входу первого элемента ИЛИ-НЕ, первый вход которого соединен с шиной счетных импульсов, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ последнего разряда соединен с выходом элемента НЕ и входом элемента И.

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ С КОНТРОЛЕМ | 1989 |

|

SU1697583A1 |

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ | 1987 |

|

SU1499711A1 |

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ С КОНТРОЛЕМ | 1997 |

|

RU2129332C1 |

| US 4941161 A, 10.07.1990 | |||

| JP 2002232289 A, 16.08.2002. | |||

Авторы

Даты

2005-11-10—Публикация

2003-06-09—Подача