Изобретение относится к микропроцессорной технике и может быть использовано в микропроцессорных АСУ ТП.

Известная микропроцессорная система, состоящая из микропроцессора, тактового генератора, системного контроллера, дешифратора адреса памяти, оперативной памяти, постоянной памяти, шинного формирователя памяти, дешифратора адресов устройств ввода-вывода, шинных формирователей ввода-вывода, трех элементов ИЛИ, первого, второго и третьего шинных формирователей, триггера, регистра, схемы сравнения и четырех элементов И (А.С. 1418653, кл. G 05 B, 1988 г.).

Недостатком такой системы является высокая сложность программного обеспечения и низкая его контролепригодность.

Известна также микропроцессорная система для программного управления электроавтоматикой, содержащая микропроцессор, тактовый генератор, системный контроллер, буфер адреса, дешифратор адреса памяти, постоянную память, оперативную память, шинный формирователь памяти, дешифратор адреса устройств ввода-вывода, регистр, шинные формирователи ввода-вывода, шинный формирователь ввода, шинный формирователь младшего адреса, шинный формирователь старшего адреса, шинный формирователь записи, шинный формирователь управления, триггер, четыре элемента ИЛИ, три элемента И, одновибратор, два элемента задержки, дешифратор, мультиплексор и два элемента ИЛИ (А.С. 1532899, кл. G 05 B 19/18,1989 г.).

Недостатком такой системы является низкая контролепригодность программного обеспечения.

Наиболее близкой по технической сущности к предлагаемым является система для программного управления технологическим оборудованием, содержащая микропроцессор, тактовый генератор, системный контроллер, буфер адреса, дешифратор адреса памяти, постоянную память, оперативную память, шинный формирователь памяти, дешифратор адреса устройств ввода-вывода, шинные формирователи ввода-вывода в количестве, равном количеству групп входных и выходных переменных, три элемента ИЛИ, шинный формирователь входного вектора, регистр кода состояния, первый триггер и шинный формирователь адреса программы, причем первый и второй входы тактового генератора подключены к кварцевому резонатору, третий и четвертый входы тактового генератора являются входами "Готовность" и "Сброс" микропроцессорной системы соответственно, пятый вход тактового генератора подключен к выходу синхронизации микропроцессора, первый и второй выходы тактового генератора подключены к первому и второму тактовым входам микропроцессора, третий и четвертый выходы тактового генератора подключены к входам "Готовность" и "Сброс" микропроцессора соответственно, шестой вход микропроцессора является входом "Запрос прерывания" микропроцессорной системы, пятый выход тактового генератора подключен к входу синхронизации системного контроллера, адресные выходы микропроцессора подключены к входам буфера адреса, выходы/входы данных микропроцессора подключены к входам/выходам данных системного контроллера, выходы управления микропроцессора подключены к входам управления системного контроллера, второй и третий выходы микропроцессора являются выходами разрешения прерывания и ожидания микропроцессорной системы соответственно, выходы буфера адреса являются шиной адреса микропроцессорной системы соответственно, выходы/входы данных системного контроллера являются шиной данных микропроцессорной системы, выходы управления системного контроллера являются шиной управления микропроцессорной системы, информационные входы дешифратора адреса памяти подключены к шине адреса микропроцессорной системы, вход разрешения дешифратора адреса памяти подключен к выходу первого элемента ИЛИ, первый и второй выходы которого подключены к разрядам шины управления микропроцессорной системы "Чтение памяти", "Запись в память" соответственно, первый выход дешифратора адреса памяти подключен к первому входу разрешения постоянной памяти, второй выход дешифратора адреса памяти подключен к входу разрешения оперативной памяти, входы/выходы шинного формирователя памяти подключены к шине данных микропроцессорной системы, входы шинного формирователя памяти подключены к выходам оперативной памяти, выходы шинного формирователя памяти подключены к входам данных оперативной памяти, адресные входы постоянной и оперативной памяти подключены к шине адреса микропроцессорной системы, вход записи оперативной памяти подключен к разряду шины управления микропроцессорной системы "Запись в память", информационные входы дешифратора адреса устройств ввода/вывода подключены к шине адреса микропроцессорной системы, вход разрешения дешифратора адреса устройств ввода/вывода подключен к выходу второго элемента ИЛИ, первый и второй входы которого подключены к разрядам шины управления микропроцессорной системы "Ввод из устройства ввода", "Вывод в устройство вывода" соответственно, разряды группы выходов дешифратора адреса устройств ввода/вывода подключены к первым входам разрешения соответствующих шинных формирователей ввода/вывода, второй вход разрешения шинных формирователей ввода/вывода подключен к разряду шины управления "Ввод из устройства ввода", входы/выходы шинных формирователей ввода/вывода подключены к шине данных микропроцессорной системы, группы входов шинных формирователей ввода/вывода являются первой группой информационных входов микропроцессорной системы, а их группы выходов являются первой группой информационных выходов микропроцессорной системы, информационные входы регистра кода состояния подключены к шине данных микропроцессорной системы, а первая группа выходов регистра кода состояния является второй группой информационных выходов контроля входного вектора микропроцессорной системы, информационные входы шинного формирователя входного вектора являются второй группой информационных входов явных логических условий микропроцессорной системы, выходы/входы шинных формирователей входного вектора и адреса программы подключены к шине данных микропроцессорной системы, отличающаяся тем, что в нее введены триггеры со второго по 11-й, образующие совместно с первым триггером группу из n триггеров явных и неявных логических условий, и регистр, причем первый и второй входы разрешения буфера адреса объединены между собой и соединены со вторыми входами разрешения постоянной памяти и шинного формирователя памяти, первый вход микропроцессора является входом захвата системы, первый вход разрешения шинного формирователя памяти соединен с входом разрешения оперативной памяти, входы/выходы постоянной памяти соединены с шиной данных микропроцессорной системы, информационные входы регистра кода состояния и регистра объединены между собой, выход регистра соединен с информационным входом шинного формирователя адреса программы и является выходом адреса программы системы, вход разрешения второго шинного формирователя адреса программы соединен с шиной управления микропроцессорной системы, каждый из разрядов третьей группы выходов дешифратора адреса памяти соединен с синхровходами соответствующих триггеров явных и неявных логических условий группы, первым входом разрешения шинного формирователя входного вектора, который является первым выходом микропроцессорной системы, первым входом третьего элемента ИЛИ, синхровходом регистра, синхровходом регистра кода состояния, который является вторым выходом контроля микропроцессорной системы, первым входом разрешения шинного формирователя адреса программы, второй вход разрешения шинного формирователя входного вектора подключен к шине адреса микропроцессорной системы, прямые выходы триггеров явных и неявных логических условий группы соединены с информационными входами шинного формирователя входного вектора и являются выходами контроля входного вектора микропроцессорной системы, информационные входы триггеров явных и неявных логических условий группы соединены с шиной данных микропроцессорной системы, третий выход тактового генератора подключен ко второму входу третьего элемента ИЛИ, выход которого подключен к входам установки в исходное состояние триггеров явных и неявных логических условий группы, peгистра и регистра кода состояния (патент 2072546 (РФ), кл. G 05 В 19/18, 1997 г.).

Недостатком прототипа является низкая достоверность функционирования.

Это обусловлено тем, что в прототипе отсутствуют технические средства контроля выполнения команд условных переходов, что может привести к реализации неправильной последовательности выполнения программы и выдаче неправильной информации в группу триггеров явных и неявных логических условий. Правильность ветвления обеспечивается отсутствием отказов (сбоев) в схемах формирования последующего адреса в счетчике команд микропроцессора с учетом значения соответствующего признака результата операции, по которому производится ветвление. Результат операции фиксируется в регистре микропроцессора, например в регистре-аккумуляторе, и по значению результата устанавливаются так называемые флажки-триггеры признаков результатов (нулевой результат, положительный результат, четный результат, наличие переноса и пр.) Однако в прототипе проверка правильности результатов операций в арифметико-логическом устройстве микропроцессора и в схемах формирования последующего адреса условного перехода невозможна.

В современных микропроцессорных системах на базе процессоров фирмы Intel все шире применяются средства контроля и диагностирования, введен контроль по нечетности шины адреса, информации команды и данных, контролируются операции в сопроцессоре и т.д (Гук М. Процессоры Intel: от 8086 до Pentium II. СПб: Питер, 1998. - 224 с.; Гук М. Процессоры Pentium II, Pentium Pro и просто Pentium. СПб: Питер, 1999. -288 с.).

Выполняется многоступенчатая конвейерная выборка команд, реализовано "предсказание" направления ветвлений. Однако такой важный процесс, как собственно выполнение условного перехода по значению бита некоторого признака, пока не реализован. Это значительно снижает достоверность функционирования и может привести к ошибкам вычислений, подобным выявленной ошибке в сопроцессоре с плавающей точкой (в Pentium), которые фирма Intel до сих пор бесплатно заменяет.

В связи с этим, целью настоящего изобретения является повышение достоверности функционирования.

Поставленная цель достигается тем, что в систему для программного управления технологическим оборудованием, содержащую микропроцессор, тактовый генератор, системный контроллер, буфер адреса, дешифратор адреса памяти, постоянную память, оперативную память, дешифратор адреса устройств ввода-вывода, r шинных формирователей ввода-вывода, где r - количество групп входной и выходной информации, три элемента ИЛИ, шинный формирователь входного вектора автоматной модели, шинный формирователь кода программы, группу n триггеров логических условий, где n - число проверяемых логических условий, регистр кода состояния, регистр кода программы, причем первый и второй входы тактового генератора подключены к кварцевому резонатору, третий вход тактового генератора является входом "Сброс" микропроцессорной системы, четвертый вход тактового генератора подключен к выходу синхронизации микропроцессора, первый и второй выходы тактового генератора подключены к первому и второму тактовым входам микропроцессора, третий и четвертый выходы тактового генератора подключены к -толам "Сброс" и "Готовность" микропроцессора соответственно, пятый вход микропроцессора является входом "Захват" микропроцессорной системы, шестой вход микропроцессора является входом "Запрос прерывания" микропроцессорной системы, второй выход микропроцессора является выходом ожидания микропроцессорной системы, трети выход микропроцессора является выходом разрешении прерывания микропроцессорной системы, пятый выход тактового генератора подключен к входу синхронизации системного контроллера, адресные выходы микропроцессора подключены к входам буфера адреса, выходы-входы данных микропроцессора подключены к входам-выходам данных системного контроллера, выходы управления микропроцессора подключены ко входам управления системного контроллера, выход управления микропроцессора "Подтверждение захвата" подключен ко входу разрешения буфера адреса, выходы буфера адреса являются шиной адреса микропроцессорной системы, выходы-входы данных системного контроллера являются шиной данных микропроцессорной системы, выходы управления системного контроллера являются шиной управления микропроцессорной системы, информационные входы дешифратора адреса памяти подключены к шине адреса микропроцессорной системы, вход разрешения дешифратора адреса памяти подключен к выходу первого элемента ИЛИ, первый и второй входы которого подключены к разрядам шины управления микропроцессорной системы "Чтение памяти", "Запись в память" соответственно, первый выход дешифратора адреса намят подключен к первому входу разрешения постоянной памяти, второй вход разрешения которой подключен к разряду шины управления микропроцессорной системы "Чтение памяти", второй выход дешифратора адреса памяти подключен к входу разрешения оперативной памяти, вход записи которой подключен к разряду шины управления микропроцессорной системы "Запись в память", адресные входы постоянной и оперативной памяти подключены к шине адреса микропроцессорной системы, выходы данных постоянной памяти и входы-выходы оперативней памяти подключены к шине данных микропроцессорной системы, информационные входы дешифратора адреса устройств входа-выхода подключены к шине адреса микропроцессорной системы, вход разрешения дешифратора адреса устройств ввода-вывода подключен к выходу второго элемента ИЛИ, первый и второй входы которого подключены к разрядам шины управления микропроцессорной системы "Ввод из устройства ввода", "Вывод в устройство вывода" соответственно, r разрядов первой группы выходов дешифратора адреса устройств ввода-вывода подключены к первым входам разрешения соответствующих r шинных формирователей ввода-выхода, второй вход разрешения r шинных формирователей ввода-вывода подключен к разряду шины управления "Ввод из устройства ввода", входы-выходы r шинных формирователей ввода-вывода подключены к шине данных микропроцессорной системы, группы входов r шинных формирователей ввода-вывода являются группой r информационных входов микропроцессорной системы, а их группы выходов являются группой r информационных выходов микропроцессорной системы, выходы триггеров группы n триггеров логических условий вместе с выходами регистра кода состояния являются группой выходов контроля входного вектора автоматной модели и подключены к информационным входам шинного формирователя входного вектора автоматной модели, входы обнуления регистра кода состояния и регистра кода программы, триггеров из группы r триггеров логических условий подключены к выходу четвертого элемента ИЛИ, первый вход которого подключен к четвертому выходу "Сброс" тактового генератора, выходы регистра кода программы являются выходами кода программы системы и подключены к информационным входам шинного формирователя кода программы, выходы которого и информационные входы регистра кода программы подключены к шине данных системы, выходы шинного формирователя входного вектора автоматной модели подключены к шине данных системы, первый вход третьего элемента ИЛИ подключен к четвертому выходу "Сброс" тактового генератора.

Согласно изобретению введены блок памяти автоматной модели, шинный формирователь автоматной модели, триггер готовности, регистр управления записью признаков, два регистра признаков, мультиплексор, дешифратор-демультиплексор, два счетных триггера, четвертый элемент ИЛИ, два элемента И, два элемента задержки, регистр сравнения и схема сравнения, причем информационные входы триггеров из группы r триггеров логических условии и первая группа адресных входов блока памяти автоматной модели, содержащая один разряд, подключены к выходам мультиплексора, входы синхронизации триггеров из группы r триггеров логических условий подключены к соответствующим выходам дешифратора-демультиплексора, вход разрешения шинного формирователя кода программы подключен к первому выходу второй группы выходов дешифратора адреса устройств ввода-вывода, второй выход второй группы выходов которого подключен к входу синхронизации регистра кода программы, трети выход второй группы выходов дешифратора адреса устройств ввода-вывода подключен ко входу разрешения шинного формирователя входного вектора автоматной модели, четвертый выход второй группы выходов дешифратора адреса устройств ввода-вывода подключен к входу разрешения шинного формирователя автоматной модели, пятый выход второй группы выходов дешифратора адреса устройств ввода-вывода подключен к входам синхронизации регистра кода состояния и регистра сравнения, выходы которого подключены ко второй группе входов схемы сравнения и являются выходами контроля выполнения программы системы, вход обнуления регистра сравнения подключен к входу обнуления регистра кода состояния, а информационные входы регистра сравнения подключены к шине данных системы, выходы регистра кода состояния подключены к первой группе входов схемы сравнения и к информационным входам шинного формирователя автоматной модели, выходы которого подключены к шине данных системы, вторая группа адресных входов блока памяти автоматной модели подключена к выходам регистра кода состояния, а третья группа адресных входов блока памяти автоматной модели подключена к выходам регистра кода программы, выходы блока памяти автоматной модели подключены к информационным входам регистра кода состояния и являются выходами контроля автоматной модели, входы синхронизации триггера готовности и регистра управления записью признаков подключены к первому выходу третьей группы выходив дешифратора адреса устройств ввода-вывода, второй выход которой подключен к первому входу четвертого элемента ИЛИ, третий выход третьей группы выходов дешифратора адреса устройств ввода-вывода подключен ко второму входу третьего элемента ИЛИ, второй вход четвертого элемента ИЛИ подключен к четвертому выходу "Сброс" тактового генератора, а выход четвертого элемента ИЛИ подключен к входам обнулении триггера готовности, регистра управления записью признаков и первого и второго счетных триггеров, третий вход четвертого элемента ИЛИ подключен к выходу второго элемента задержки, вход которого подключен ко входу разрешения дешифратора-демультиплексора и выходу первого элемента задержки, вход первого элемента задержки подключен к выходу второго счетного триггера, счетный вход которого подключен к инверсному выходу первого счетного триггера, счетный вход первого счетного триггера подключен ко входам синхронизации первого и второго pегистров признаков и к выходу первого элемента И, первый вход которого подключен к выходу триггера готовности, а второй вход первого элемента И подключен к разряду шины управления микропроцессорной системы "Запись в память", информационные входы регистра управления записью признаков и первого регистра признаков подключены к шине данных микропроцессорной системы, первая группа выходов регистра управления записью признаков подключена к адресным входам дешифратора-демультиплексора и является выходами контроля номера логического условия системы, вторая группа выходов регистра управления записью признаков подключена к адресным входам мультиплексора и является выходами контроля номера признака системы, выходы первого регистра признаков подключены к информационным входам мультиплексора и информационным входам второго регистра признаков, а также являются выходами контроля первого регистра признаков системы, выходы второго регистра признаков являются выходами контроля второго регистра признаков системы, входы обнуления первого и второго регистра признаков подключены к четвертому выходу "Сброс" тактового генератора, выход схемы сравнения является выходом ошибки ветвления и подключен к первому входу второго элемента И, второй вход которого является входом готовности системы, а выход второго элемента И подключен к пятому входу "Готовность" тактового генератора.

Технико-экономическая эффективность предлагаемого устройства может быть оценена величиной повышения достоверности функционирования за счет контроля условных переходов.

Сущность изобретения заключается и повышении достоверности функционирования за счет введения средств контроля условных переходов, которые позволяют:

а) фиксировать диагностическую информацию о результатах операции, выполненной в арифметико-логическом устройстве микропроцессора, и признаках этих операций (слово состояния процессора);

б) формировать эталонный код линейного участка программ с помощью автоматной модели с учетом значения признака операции;

в) фиксировать код фактически выполняемого линейного участка программы,

г) сравнивать эталонный код линейного участка и фактически исполняемый с формированием сигнала ошибки при их неравенстве.

Сущность изобретения реализуется следующей совокупностью конструктивных признаков - новых элементов и связей, определяющих соответствие заявляемого технического решения критерию "новизна".

Введение триггера готовности и соответствующих ему связей позволяет подготовить cpедствa контроля к приему слова состояния процессора, которое программно записывается в стек, находящийся в оперативной памяти, а аппаратно - в регистры признаков.

Введение peгистра управления записью признаков и соответствующих ему связей позволяет настроить средства котроля к оценке требуемого признака и к записи его в триггеры логических условии.

Введение двух регистров признаков и соответствующих им связей позволяет аппаратно фиксировать дополнительную диагностическую информацию (слово состояния процессора) при программном выполнении записи ее в стек, что обеспечивает контроль и запись требуемого признака, и контроль результата операции.

Введение мультиплексора и соответствующих ему связей позволяет выделить в признаковой информации значения требуемого признака для записи и хранения и изменения состояния автоматной модели в блоке памяти автоматной модели.

Введение дешифратора-демультиплексора и соответствующих ему связей позволяет обеспечить запись требуемого признака в требуемый триггер группы n триггеров логических условий.

Введение счетных триггеров и соответствующих им связей позволяет обеспечить прием только двух сигналов записи и стек и последующее снятие готовности - обнуление триггера готовности.

Введение двух элементов задержки и соответствующих им связей позволяет обеспечить требуемую временную выдержку для ожидания завершения переходных процессов при фиксации диагностической информации.

Введение схемы сравнения и соответствующих ей связей позволяет формировать сигнал ошибки ветвления (условного перехода) в случае не сравнения кодов фактически исполняемого линейного участка и кода, сформированного автоматной моделью.

Введение блока памяти автоматной модели и соответствующих ему связей позволяет хранить эталонные коды линейных участков, формируемые с учетом кода текущего исполняемого участка и значения признака (переменной ветвления).

Введение регистра сравнения и соответствующих ему связей позволяет фиксировать программно выдаваемый в схему код фактически исполняемого линейного участка.

Введение новых связей для регистра кода состояния позволяет фиксировать эталонный код линейного участка программы, считываемый с блока памяти автоматной модели.

Введение новых связей для регистра кода программы позволяет считывать из блока памяти автоматной модели информацию, соответствующую данной программе.

Введение шинного формирователя автоматной модели и соответствующих ему связей позволяет программно вводить информацию с выхода регистра состояния при тестировании.

Введение новых связен для триггеров группы n триггеров логических условий позволяет фиксировать в них значения признаков, т.e. переменных ветвления с выходов мультиплексора.

Введение четвертого элемента ИЛИ и соответствующих ему связей позволяет обнулять триггер готовности в процессе контроля и тестирования.

Введение первого элемента И и соответствующих ему связей позволяет формировать сигналы записи признаковой информации в регистре признаков при контроле условных переходов.

Введение второго элемента И и соответствующих ему связей позволяет снимать сигнал готовности с тактового генератора при обнаружении ошибки ветвления.

Таким образом, предлагаемое техническое решение соответствует критерию "существенные отличия", поскольку в известных устройствах - аналоге и прототипе - не достигается свойство повышения достоверности функционирования вследствие отсутствия указанной совокупности конструктивных признаков.

При использовании предлагаемой системы может быть получен положительный эффект повышения достоверности функционирования за счет контроля условных переходов в программном обеспечении.

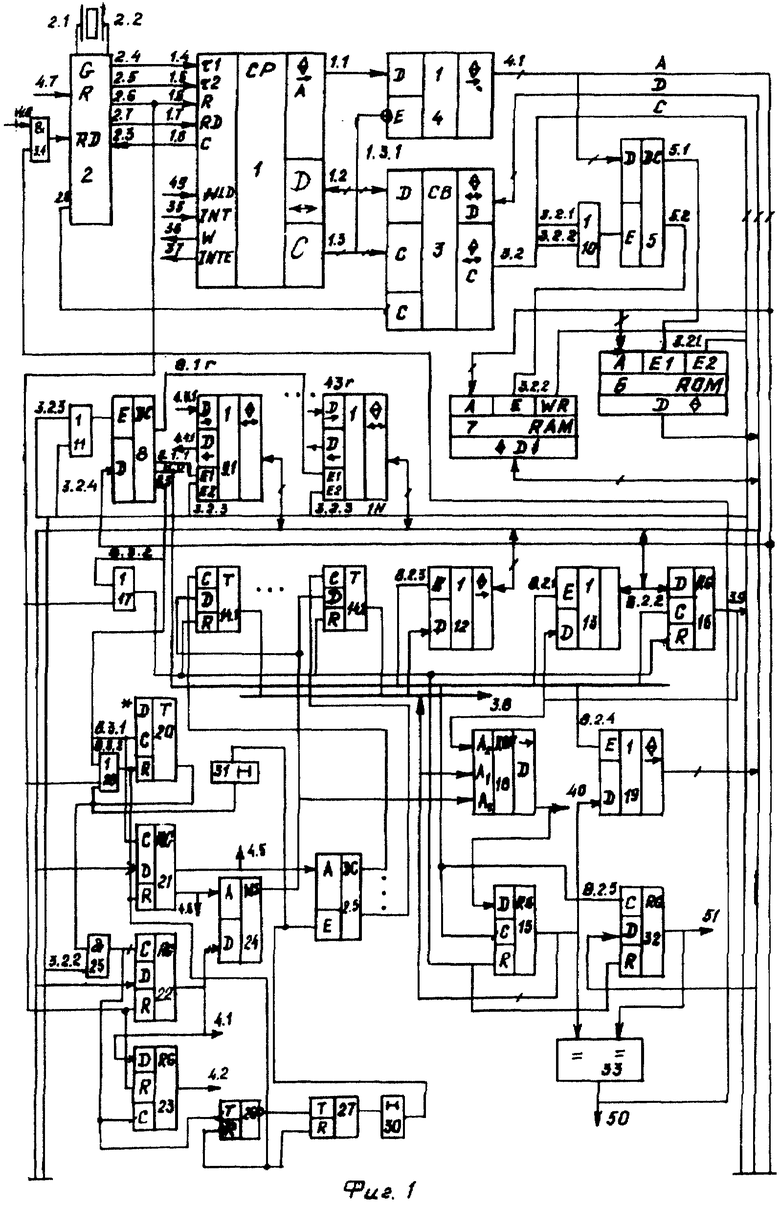

На фиг. 1 приведена функциональная электрическая схема предлагаемой системы для программного управления технологическим оборудованием.

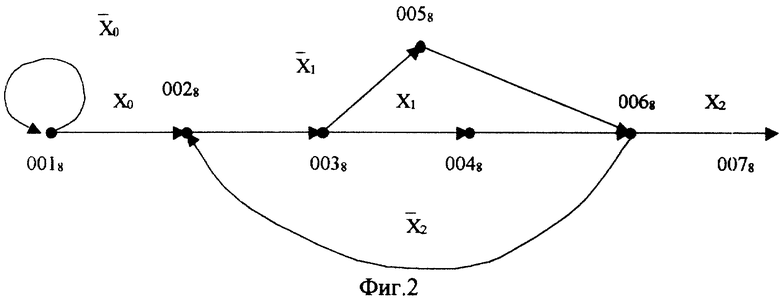

На фиг. 2 приведен пример графа исполняемой программы.

Система для программного управления технологическим оборудованием (фиг. 1) содержит: микропроцессор 1, содержащий выходы адреса 1.1, выходы/входы данных 1.2, выходы управления 1.3; тактовые входы 1.4 и 1.5, вход сброса 1.6, вход готовности 1.7, выход синхронизации 1.8, тактовый генератор 2, содержащий входы 2.1 и 2.2 подключения кварцевого резонатора, вход 2.3 синхронизации, тактовые выходы 2.4 и 2.5, выход сброса 2.6, выход готовности 2.7 и выход системного строба 2.8; системный контроллер 3, содержащий выходы/входы данных 3.1, являющиеся шиной данных микропроцессорной системы, выходы управления 3.2, являющиеся шиной управлении микропроцессорной системы, буфер адреса 4, содержащий выходы 4.1, являющиеся шиной адреса микропроцессорной системы, дешифратор адреса памяти 5, содержащий выход 5.1 подключения постоянной памяти, выход 5.2. подключения оперативной памяти; постоянную память 6; оперативную память 7; дешифратор адреса устройств ввода-вывода 8, содержащий первую группу выходов подключения устройств ввода-вывода 8.1, группы выходов два 8.2 и три 8.3, r шинных формирователей ввода-вывода 9.1. . .9.r; первый элемент ИЛИ 10, второй элемент ИЛИ 11, шинный формирователь входного вектора автоматной модели 12, шинный формирователь кода программы 13, группу n триггеров логических условий 14.1...14.n, регистр кода состояния 15, регистр кода программы 16; третий элемент ИЛИ 17; блок памяти автоматной модели 18, шинный формирователь автоматной модели 19; триггер готовности 20; регистр управления записью признаков 21; первый 22 и второй 23 регистры признаков; мультиплексор 24; дешифратор-демультиплексор 25, первый 26 и второй 27 счетные триггеры; четвертый элемент ИЛИ 28, первый элемент И 29, первый 30 и второй 31 элементы задержки, регистр сравнения 32, схему сравнения 33, второй элемент И 34, вход запроса прерывания 35, выход ожидания 36; выход разрешения прерывания 37; группу выходов контроля входного вектора автоматной модели 38, выход кода программы 39; выходы контроля автоматной модели 40; выходы контроля 41 первого регистра признаков; выходы контроля 42 второго регистра признаков; группу r информационных входов 43.1. . . 43.r; группу r информационных выходов 44.1...44.r; выход контроля номера логического условия 45, выходы контроля номера признака 46, вход сброса 47, вход готовности 48, вход захвата 49, выход ошибки ветвления 50, выходы контроля выполнения программы 51.

Первый 2.1 и второй 2.2 входы тактового генератора 2 подключены к кварцевому резонатору. Третий вход тактового генератора 2 является входом "Сброс" 47 микропроцессорной системы. Четвертый вход 2.3 тактового генератора 2 подключен к выходу синхронизации 1.8 микропроцессора 1. Первый 2.4 и второй 2.5 выходы тактового генератора 2 подключены к первому 1.4 и второму 1.5 тактовым входам микропроцессора 1. Третий 2.6 и четвертый 2.7 выходы тактового генератора 2 подключены к входам "Сброс" 1.6 и "Готовность" 1.7 микропроцессора 1 соответственно. Пятый вход микропроцессора 1 является входом "Захват" 49 микропроцессорной системы. Шестой вход микропроцессора 1 является входом "Запрос прерывания" 35 микропроцессорной системы. Второй выход микропроцессора 1 является выходом ожидания 36 микропроцессорной системы. Третий выход микропроцессора 1 является выходом разрешения прерывания микропроцессорной системы 37. Пятый выход 2.8 тактового генератора 2 подключен к входу синхронизации системного контроллера 3. Адресные выходы 1.1 микропроцессора 1 подключены к входам буфера адреса 4 Адресные выходы 1.1 микропроцессора 1 подключены к входам буфера адреса 4. Выходы-входы данных 1.2 микропроцессора 1 подключены к входам-выходам данных системного контроллера 3. Выходы управления 1.3 микропроцессора 1 подключены к входам управления системного контроллера 3. Выход управления 1.3.1 микропроцессора "Подтверждение захвата" подключен к входу разрешения буфера адреса 4. Выходы буфера адреса 4 являются шиной адреса 4.1 микропроцессорной системы. Выходы-входы данных системного контроллера 3 являются шиной данных 3.1 микропроцессорной системы. Выходы управления системного контроллера 3 являются шиной управления 3.2 микропроцессорной системы. Информационные входы дешифратора адреса памяти 5 подключены к шине адреса 3.1 микропроцессорной системы. Вход разрешения дешифратора адреса памяти 5 подключен к выходу первого элемента ИЛИ 10, первый и второй входы которого подключены к разрядам 3.2.1, 3.2.2 шины управления 3.2 микропроцессорной системы "Чтение памяти", "Запись в память" соответственно. Первый выход 5.1 дешифратора адреса памяти 5 подключен к первому входу разрешения постоянной памяти 6, второй вход разрешения которой подключен к разряду 3.2.1 шины управления 3.2 микропроцессорной системы "Чтение памяти". Второй выход 5.2 дешифратора адреса памяти 5 подключен к входу разрешения оперативной памяти 7, вход записи которой подключен к разряду 3.2.2 шины управления 3.2 микропроцессорной системы "Запись в память". Адресные входы постоянной 6 и оперативной памяти 7 подключены к шине адреса 4.1 микропроцессорной системы. Выходы данных постоянной памяти 6 и входы-выходы оперативной памяти 7 подключены к шине данных 3.1 микропроцессорной системы. Информационные входы дешифратора адреса устройств 8 входа-выхода подключены к шине адреса 4.1 микропроцессорной системы. Вход разрешения дешифратора адреса устройств ввода-вывода 8 подключен к выходу второго элемента ИЛИ 1.1, первый и второй входы которого подключены к разрядам 3.2.3, 3.2.4 шины управления 3.2 микропроцессорной системы "Ввод из устройства ввода", "Вывод в устройство вывода" соответственно, r разрядов первой группы выходов 8.1 дешифратора адреса устройств ввода-вывода 8 подключены к первым входам разрешения соответствующих r шинных формирователей ввода-вывода 9.1...9.r. Второй вход разрешения r шинных формирователей ввода-вывода 9.1. ..9.r подключен к разряду 3.2.3 шины управления 3.2 "Ввод из устройства ввода". Входы-выходы r шинных формирователей ввода-вывода 9.1...9.r подключены к шине данных 3.1 микропроцессорной системы. Группы входов r шинных формирователей ввода-вывода являются группой r информационных входов 43.1... 43.r микропроцессорной системы, и их группы выходов являются группой r информационных выходов 44.1...44.r микропроцессорной системы. Выходы триггеров группы n триггеров логических условий 14.1..14.n вместе с выходами регистра кода состояния 15 являются группой выходов 38 контроля входного вектора автоматной модели и подключены к информационным входам шинного формирователя входного вектора автоматной модели 12. Входы обнуления регистра кода состояния 15 и регистра кода программы 16, триггеров из группы r триггеров логических условий 14.1... 14.n подключены к выходу четвертого элементе ИЛИ 17, первый вход которого подключен к четвертому выходу 2.6 "Сброс" тактового генератора 2. Выходы регистра кода программы 16 являются выходами кода программы 39 системы и подключены к информационным входам шинного формирователя кода программы 13, выходы которого и информационные входы регистра кода программы 16 подключены к шине данных 3.1 системы. Выходы шинного формирователя входного вектора автоматной модели 12 подключены к шине данных 3.1 системы. Первый вход третьего элемента ИЛИ 17 подключен к четвертому выходу 2.6 "Сброс" тактового генератора 2. Информационные входы триггеров из группы r триггеров логических условий 14.1 14.r и первая группа А0 адресных входов блока памяти автоматной модели 18, содержащая один разряд, подключены к выходам мультиплексора 24. Входы синхронизации триггеров из группы r триггеров логических условий 14.1...14.n подключены к соответствующим выходам дешифратора-демультиплексора 25. Вход разрешения шинного формирователя кода программы 13 подключен к первому выходу 8.2.1 второй группы выходов 8.2 дешифратора адреса устройств ввода-вывода 8, второй выход 8.2.2 второй группы выходив 8.2 которого подключен к входу синхронизации pегистра кода программы 16. Третий выход 8.2.3 второй группы выходов 8.2 дешифратора адреса ycтpoйств ввода-вывода 8 подключен к входу разрешения шинного формирователя входного вектора автоматной модели 12. Четвертый выход 8.2.4 второй группы 8.2 выходов дешифратора адреса устройств ввода-вывода 8 подключен к входу разрешения шинного формирователя автоматной модели 19. Пятый выход 8.2.5 второй группы выходов 8.2 дешифратора адреса устройств ввода-вывода 8 подключен к входам синхронизации регистра кода состояния 15 и регистра сравнения 32, выходы которого подключены ко второй группе входов схемы сравнения 33 и являются выходами контроля 51 выполнения программы системы. Вход обнуления регистра сравнения 32 подключен к входу обнуления регистра кода состояния 15, а информационные входы регистра сравнения 32 подключены к шине данных 3.1 системы. Выходы регистра кода состояния 15 подключены к первой группе входов схемы сравнения 33 и к информационным входам шинного формирователя автоматной модели 19, выходы которого подключены к шине данных системы 31. Вторая группа A1 адресных входов блока памяти автоматной модели 18 подключена к выходам регистра кода состояния 15, а третья А2 группа адресных входов блока намят автоматной модели 18 подключена к выходам регистра кода программы 16. Выходы блока памяти автоматной модели 18 подключены к информационным входам регистра кода состояния 15 и являются выходами контроля автоматной модели 40. Входы синхронизации триггера готовности 20 и регистра управления записью признаков 21 подключены к первому выходу 8.3.1 третьей группы 8.3 выходов дешифратора адреса устройств входа-выхода 8, второй выход 8.3.2 которой подключен к первому входу четвертого элемента ИЛИ 28. Третий выход 8.3.3 третьей группы 8.3 выходов дешифратора адреса устройств ввода-вывода 8 подключен ко второму входу третьего элемента ИЛИ 17 Второй вход четвертого элемента ИЛИ 28 подключен к четвертому выходу 2.6 "Сброс" тактового генератора 2. Выход четвертого элемента ИЛИ 28 подключен к входам обнуления триггepa готовности 20, регистра управлении записью признаков 21 и первого 22 и второго 23 счетных триггеров. Тpeтий вход четвертого элемента ИЛИ 28 подключен к выходу второго элемента задержки 31, вход которого подключен к входу разрешения дешифратора-демультиплексора 25 и выходу первого элемента задержки 30. Вход первого элемента задержки 30 подключен к выходу второго счетного триггера 27, счетный вход которого подключен к инверсному выходу первого счетного триггера 26. Счетный вход первого счетного триггера 26 подключен ко входам синхронизации первого 22 и второго 23 регистров признаков и к выходу первого элемента И 29, первый вход которого подключен к выходу триггера готовности 20. Второй вход первого элемента И 29 подключен к разряду 3.2.2 шины управления 3.2 микропроцессорной системы "Запись в память". Информационные входы регистра управления записью признаков 21 и первого регистра признаков 22 подключены к шине данных 3.1 микропроцессорной системы. Первая группа выходов регистра управления записью признаков 21 подключена к адресным входам дешифратора-демультиплексора 25 и является выходом 45 контроля номера логического условия системы. Вторая группа выходов регистра управления 21 записью признаков подключена к адресным входам мультиплексора 24 и является выходами 46 контроля номера признака системы. Выходы первого регистра признаков 22 подключены к информационным входам мультиплексора 29 и информационным входам второго регистра признаков 22, а также является выходами контроля 41 первого регистра признаков системы. Выходы второго регистра признаков 23 являются выходами контроля 42 второго регистра признаков системы. Входы обнуления первого 22 и второго 23 регистра признаков подключены к четвертому выходу 2.6 "Сброс" тактового генератора 2. Выход схемы сравнения 33 является выходом 50 ошибки ветвления и подключен к первому входу второго элемента И 34, второй вход которого является входом готовности 48 системы. Выход второго элемента И 34 подключен к пятому входу "Готовность" тактового генератора 2.

Микропроцессор 1 воспринимает внешние тактовые сигналы, а также сигналы управления, и генерирует сигналы адреса, данных и управления, считывает команды из постоянной 6 или оперативной 7 памяти, выполняет ее с возможной записью информации и оперативную память 7, в устройства вывода или принимает информацию из устройств ввода, реагируя на внешние сигналы управления. Микропроцессор 1 может быть реализован, например, на стандартной интегральной микросхеме КР 580 ИК 80 А (Микропроцессоры и микропроцессорные комплексы интегральных микросхем: Справочник В 2-х т. /В.-Б.Б. Абрайтис, Н.Н. Аверьянов, А.И. Белоус и др.; М.: Радио и связь, 1988. T.1. С.55-67).

Тактовый генератор 2 предназначен для формирования сигналов синхронизации микропроцессора 1, системного контроллера 3 и формирования сигналов системного сброса и готовности.

Тактовый генератор 2 может быть, например, реализован на стандартной интегральной микросхеме KP 5801 Ф24 (там же, с. 157-160).

Системный контроллер 3 предназначен для обеспечения двунаправленной передачи информации по шине данных 3.1 и для формирования шины управления 3.2 микропроцессорной системы.

Он может быть реализован, например, на стандартной интегральной микросхеме КР 580 ВК 28 (там же, с. 160-163).

Буфер адреса 4 предназначен для формирования шины адреса 4.1, обеспечивая требуемую ее нагрузочную способность, а также обеспечивает отключение ее при активизации сигнала 1.3.1 выходов управления микропроцессора 1.3 путем перевода своих выходов в высокоимпедансное состояние.

Буфер адреса 4 может быть реализован на стандартных интегральных микросхемах 586ВА86 (там же, с. 166-169).

Дешифратор адреса памяти 5 предназначен для дешифрации но разрешающему сигналу с выхода первого элемента ИЛИ 10 адресной информации с шины адреса 4.1 для подключения постоянной 6 (выход 5.1) или оперативной 7 (выход 5.2) памяти по разрешающим входам (входам выборки кристалла).

Дешифратор адреса памяти может быть реализован, например, на стандартных интегральных микросхемах 155ИД3.

Постоянная память 6 предназначена для хранения не разрушаемых при выключении питания программ и данных и выдачи этой информации при ее чтении, когда активированы сигналы 5.1 дешифратора памяти 5 и 3.2.1 шины управления 3.2.

Постоянная память 6 может быть реализована, например, на стандартных интегральных микросхемах 556РТ5.

Оперативная память 7 предназначена для записи и хранения программ и данных только во время работы микропроцессорной системы. При обращении к оперативной памяти активирован сигнал 5.2 дешифратора памяти 5. При записи в оперативную память, кроме того, активирован сигнал 3.2.2, а при чтении этот сигнал деактивирован.

Оперативная память 7 может быть реализована, например, на стандартных интегральных микросхемах 541PУ2.

Дешифратор адреса устройств ввода-вывода 8 предназначен для дешифрации по разрешающему сигналу с выхода второго элемента ИЛИ 11 адресной информации для подключения соответствующего из r шинных формирователей ввода-вывода 9.1. . .9.r по соответствующему разряду первой группы выходов 8.1; для подключения шинного формирователя кода программы 13, регистра кода программы 16, шинного формирователя входного вектора автоматной модели 12, шинного формирователя автоматной модели 19, регистра кода состояния 15 и регистра сравнения 32 - по соответствующему разряду второй группы выходов 8.2; для подключения триггера готовности 20 и обнуления его через четвертый элемент ИЛИ 28 - по соответствующему разряду третьей группы выходов 8.3.

Дешифратор адреса устройств ввода/вывода может быть реализован, например, на стандартных интегральных микросхемах 155ИД3.

Первый элемент ИЛИ 11 предназначен для управления по входу разрешения дешифратором адреса памяти 5 в том случае, если активированы выходы 3.2.1 (чтение памяти) шины управления 3.2 либо 3.2.2 (запись в память).

Второй элемент ИЛИ 12 предназначен для управления по входу разрешения дешифратором адреса устройств ввода-вывода 9 в том случае, если активированы выходы 3.2.3 (ввод) или 3.2.4 (вывод) шины управления 3.2 системы.

Шинный формирователь входного вектора автоматной модели 12 предназначен для ввода в микропроцессор 1 по разрешающему сигналу 8.2.3 с дешифратора адреса устройств ввода-вывода 8 информации, установленной на группе выходов контроля входного вектора автоматной модели 38, т.е информации о значении переменных условных переходов, имеющейся в триггерах группы 12 триггеров логических условий 14.1...14.n, о значении кода состояния, имеющегося в регистре кода состояния 15.

Шинный формирователь входного вектора автоматной модели 12 может быть реализован, например, на стандартной интегральной микросхеме 580ВА86.

Шинный формирователь кода программы 13 предназначен для ввода в микропроцессор 1 по разрешающему сигналу 8.2.1 с дешифратора адреса устройств ввода-вывода 8 информации кода программы, установленной на выходах регистра кода программы 16 и выходах кода программы 39.

Шинный формирователь кода программы 13 может быть реализован, например, на стандартной интегральной микросхеме 580ВА86.

Группа n триггеров логических условий 14.1...14.n предназначена для записи значений логических условий, проверяемых в ходе выполнения программы командами условного перехода, с выходок мультиплексора 24 но синхросигналам, формируемым на выходах дешифратора 25. Кроме того, часть триггеров 14.1... 14. n может использоваться для записи дополнительных переменных, по которым не производится ветвление, но которые могут контролироваться.

Группа n триггеров логических условий 14.1...14.r обнуляется сигналом с выхода третьего элемента ИЛИ 17 и формирует входной вектор автоматной модели, выдаваемой на соответствующие выходы 38 при реализации структурированной программы аналогично прототипу.

Группа n триггеров логических условий 14.1...14.r может быть реализована, например, на стандартных интегральных микросхемах 155ТМ2.

Регистр кода состояния 15 предназначен для записи, хранения и выдачи кода состояния программы, т.е. кода текущего (исполняемого) линейного участка программы. Этот код записывается с выходов блока памяти автоматной модели 18 по сигналу 8.2.5 с выхода дешифратора адреса устройств ввода-вывода 8 и ведется на первую группу входов схемы сравнения 33 и первую группу адресных входов блока памяти автоматной модели 18.

Регистр кода состояния 15 обнуляется сигналом с выхода третьего элемента ИЛИ 17 и может быть реализован, например, на стандартных интегральных микросхемах 155ИР13.

Регистр кода программы 16 предназначен для записи, хранения и выдачи кода программы, т. е номера исполняемой программы. Этот код записывается с шины данных 3.1 по сигналу 8.2.2 с выхода дешифратора адреса устройств ввода-вывода 8 и выдается на выходы 39 кода программы и вторую группу адресных входов блока памяти автоматной модели 18.

Регистр кода программы 16 может быть реализован, например, на стандартных интегральных микросхемах 155ИР13.

Третий элемент ИЛИ 17 предназначен для формирования сигнала обнуления группы n триггеров логических условий 14.1...14.n, регистра кода состояния 15, регистра кода программы 16 и регистра сравнения 32 либо сигналом системного сброса с выхода 2.6 тактового генератора 2, либо по сигналу 8.3.4 с выхода дешифратора адреса устройств ввода-вывода 8.

Блок памяти автоматной модели 18 предназначен для хранения и выдачи информации последующего состояния в зависимости от кода текущего состояния - первая группа входов блока памяти автоматной модели 18, значения переменной ветвления - нулевая группа входов блока памяти автоматной модели 18 и значения кода программы 39.

Информация последующего состояния выдается на информационные входы регистра состояния 15 и на выходы 40 автоматной модели.

Блок памяти автоматной модели может быть реализован, например, на стандартных интегральных микросхемах 556РТ5.

Шинный формирователь автоматной модели 19 предназначен для ввода в микропроцессор 1 информации с выходов регистра кода состояния 15 по разрешающему сигналу 8.2.4 с выхода дешифратора адреса устройств ввода-вывода 8.

Шинный формирователь автоматной модели 19 может быть реализован, например, на стандартной интегральной микросхеме 580ВА86.

Триггер готовности 20 предназначен для формирования сигнала готовности к приему информации о признаках (слова состояния PSW) на первый элемент И 29 по сигналу 8.3.1 с выхода дешифратора адреса устройств ввода-вывода 8, т.е. при выводе информации управления записью признаков в регистр управления записью признаков 21.

Триггер готовности 20 обнуляется сигналом с выхода четвертого элемента ИЛИ 28.

Триггер готовности 20 - триггер D типа, для ТТЛ микросхем неподключенный вход D эквивалентен логической единице. Поэтому по переднему фронту сигнала синхронизации триггер 20 устанавливается в состояние "единицы", формируя сигнал логической единицы на своем выходе.

Триггер готовности 20 может быть реализован, например, на стандартной интегральной микросхеме 155ТМ2.

Регистр управления записью признаков 21 предназначен для приема с шины данных информации управления записью признаков: номера логического условия на адресные входы дешифратора-демультиплексора 25 и на выходы контроля номера логического условия 45; номера признака - на адресные входы мультиплексора 24 и на выходы контроля номера признака 46. Эта информация записывается в процессе выполнения микропроцессором 1 команды вывода по адресу, при этом возбуждается выход 8.3.1 дешифратора адреса устройств ввода-вывода 8.

Регистр управления записью признаков 21 может быть реализован, например, на стандартных интегральных микросхемах 155ИР13.

Первый регистр признаков 22 предназначен для записи информации признаков с шины данных 3.1 по сигналам с выхода первого элемента И в процессе реализации микропроцессором 1 команды записи слова состояния (PSW) в стек, находящейся в оперативной памяти 7. После выполнения этой команды в первом регистре признаков 22 находится информация о признаках последней выполненной в арифметико-логическом устройстве микропроцессора 1 операции. Эта информация выдается на информационные входы мультиплексора 24 и на выходы контроля 41 первого регистра признаков.

Первый регистр признаков 22 обнуляется сигналом системного сброса с выходов 2.6 тактового генератора 2.

Первый регистр признаков 22 может быть реализован, например, на стандартных интегральных микросхемах 155ИР13.

Второй регистр признаков 23 предназначен для записи информации признаков с выходов первого регистра признаков 22. По первому сигналу синхронизации, поступающему с выхода первого элемента И 29 во второй регистр признаков 23 записывается нулевая информация, поскольку в исходном положении регистры 22, 23 обнулены сигналом системного сброса 2.6 с выходов тактового генератора 2, а в первый регистр признаков 22 записывается информация состояния регистра аккумулятора микропроцессора 1 после выполненной операции. По второму синхроимпульсу во второй регистр признаков 23 переписывается эта информация из первого регистра признаков 22, а в первый регистр признаков 22 записывается информация о признаках.

Второй регистр признаков 23 может быть реализован, например, на стандартных интегральных микросхемах 155ИР13.

Мультиплексор 24 предназначен для подключения к информационным входам триггеров группы n триггеров логических условий 14.1...14.n с выхода первого регистра признаков 22 в соответствии с сигналами адреса, установленного на второй группе выходов регистра управления записью признаков 21.

Мультиплексор 24 может быть реализован, например, на стандартных интегральных микросхемах 155КП1.

Дешифратор-демультиплексор 25 предназначен для формирования синхросигнала записи значения логического условия на соответствующие синхровходы триггеров группы n триггеров логических условий 14.1...14.n по сигналу с выхода первого элемента задержки 30 в соответствии с адресом, установленном на первой группе выходов регистра управления записью признаков 21.

Дешифратор-демультиплексор 25 может быть реализован, например, на стандартных интегральных микросхемах 155ИД3.

Первый 26 и второй 27 счетные триггеры предназначены для фиксации прохождения двух сигналов записи на выходе первого элемента И 29 с целью формирования импульса синхронизации для записи значений логических условий. По первому импульсу на выходе первого элемента И 29 устанавливается первый счетный триггер 26, и на его инверсном выходе формируется логический ноль. По второму импульсу на выходе первого элемента И 29 первый счетный триггер 26 обнуляется, на его инверсном выходе устанавливается логическая единица, поэтому устанавливается второй счетный триггер 27 и формирует на своем выходе сигнал логической единицы. Первый 26 и второй 27 счетный триггеры обнуляются сигналом с выхода четвертого элемента ИЛИ 28.

Первый 26 и второй 27 счетный триггеры могут быть реализованы, например, на стандартных интегральных микросхемах 155ТМ2, у которых неинверсные выходы подключены к информационным входам.

Четвертый элемент ИЛИ 28 предназначен для формирования сигнала сброса при поступлении либо системного сброса 2.6 с выхода тактового генератора 2, либо по сигналу 8.3.2 с выхода дешифратора адреса устройств ввода-вывода 8, либо при поступлении сигнала с выхода второго элемента задержки.

Первый элемент И 29 предназначен для формирования сигнала синхронизации первого 22 и второго 23 pегистров признаков и счетного сигнала для первого счетного триггера 26 в том случае, если триггер готовности 20 установлен и на шине управления 3.2 имеется cигнал 3.2.2 записи в память, т.е. в момент записи слова состояния (PSW) в стековую область оперативной памяти 7.

Первый элемент задержки 30 предназначен для задержки сигнала со второго счетного триггера 27 на дешифратор-демультиплексор 25 и второй элемент задержки 31 на время, определяемое необходимостью завершения переходных процессов записи информации во второй регистр признаков 23, изменения состояния мультиплексора 24.

Второй элемент задержки 31 предназначен для задержки сигнала с выхода первого элемента задержки 30 на время, определяемое необходимостью завершения переходных процессов при записи информации в группу n триггеров логических условий 14.1...14.n.

Первый 30 и второй 31 элементы задержки могут быть реализованы, например, путем последовательного соединения требуемого количества логических элементов.

Регистр сравнения 32 предназначен для приема с шины данных номера фактически исполняемого линейного участка по сигналу 8.2.5 с выходов дешифратора адреса устройств ввода-вывода 8 в процессе выполнения микропроцессором 1 соответствующей команды вывода и выдачи этой информации на вторую группу входов схемы сравнения 33.

Регистр сравнения 32 обнуляется сигналом с выхода третьего элемента ИЛИ 17 и может быть реализован, например, на стандартных интегральных микросхемах 155ИР13.

Схема сравнения 33 предназначена для сравнения номера фактически исполняемого линейного участка, установленного на выходах регистра сравнения 32 и кода состояния, сформированного автоматной моделью и установленного на выходах регистра кода состояния 15.

Схема сравнения 33 может быть реализована, например, на стандартных интегральных микросхемах 531СП1.

Второй элемент И 34 предназначен для формирования сигнала готовности на соответствующий вход тактового генератора 2 в том случае, если имеется внешний сигнал готовности 48 и на выходе схемы сравнения логическая единица, т.е. нет ошибки ветвления. В случае наличия ошибки ветвления сигнал готовности снимается, и процесс выполнения команд прекращается.

Вход запроса прерывания 35 предназначен для приема внешнего сигнала запроса прерывания.

Выход ожидания 36 предназначен для выдачи сигнала ожидания, который активируется, если не активирован вход готовности тактового генератора 2.

Выход разрешения прерывания 37 предназначен для выдачи сигнала разрешения прерывания, активный уровень с которого снимается, если микропроцессор 1 переходит в режим прерывания.

Группа выходов контроля входного вектора автоматной модели 38 предназначена для выдачи информации о состоянии логических условий на данный момент времени и кода текущего состояния.

Выход кода программы 39 предназначен для выдачи кода номера исполняемой программы.

Выходы контроля автоматной модели 40 предназначены для выдачи информации о последующем состоянии автоматной модели.

Выходы контроля первого регистра признаков 41 предназначены для выдачи информации о значении признаков, имеющихся в регистре 41.

Выходы контроля второго регистра признаков 42 предназначены для выдачи информации о результате контролируемой операции, имеющейся во втором регистре признаков 23.

Группа r информационных входов 43.1...43 r предназначена для ввода информации в микропроцессорную систему с технологического оборудования через шинные формирователи 9.1...9.r.

Группа r информационных выходов 44.1...44.r предназначена для выдачи информации на технологическое оборудование через шинные формирователи 9.1...9. r.

Выходы контроля номера логического условия 45 предназначены для выдачи информации о номере логического условия для последующего контроля.

Выходы контроля номера признака 46 предназначены для выдачи информации о номере признака для последующего контроля.

Вход сброса 47 предназначен для приема внешнего сигнала сброса для обнуления микропроцессорной системы.

Вход готовности 48 предназначен для приема внешнего сигнала готовности.

Вход захвата 49 предназначен для приема сигнала запроса на прямой доступ в память.

Выход ошибки ветвления 50 предназначен для выдачи сигнала ошибки ветвления с целью повышения достоверности функционирования.

Выходы контроля выполнения программы 51 предназначены для выдачи сигналов номера фактически исполняемых линейных участков с целью контроля, например, некоторым сторожевым таймером. Перед началом выполнения программы выходы 51 обнулены, и после окончания программы они также будут обнулены.

Оценим технико-экономическую эффективность предлагаемой микропроцессорной системы.

Пусть вероятность сбоя при выполнении команды q. Тогда достоверность функционирования системы при выполнении команды условного перехода может быть оценена величиной (1-q). Пусть вероятность сбоя (отказа) средств контроля при формировании сигнала ошибки условных переходов qk. Тогда достоверному функционированию системы соответствуют ситуации: 1) бессбойного выполнения команды условного перехода и подтверждение этого средствами контроля; 2) обнаружение сбоя средствами контроля

(l-q)(1-qk)+q(1-qk).

Таким образом, повышение достоверности функционирования за счет контроля одного условного перехода может быть оценено величиной

Кроме того, дополнительно увеличено количество диагностической информации за счет выдачи результатов операций на выходы 42, а также дополнительно контролируются и безусловные переходы.

Система для программного управления технологическим оборудованием работает следующим образом.

а) Обычный режим работы.

В этом режиме микропроцессорная система работает аналогично прототипу. После включения питания тактовый генератор 2 начинает формировать две неперекрывающиеся тактовые последовательности, которые с его выходов 2.4 и 2.5 подаются на входы 1.4 и 1.5 микропроцессора 1. Стабильность частоты обеспечивается подключением к входам тактового генератора 2.1 и 2.2 кварцевого резонатора. Микропроцессор 1 начинает генерировать выходные сигналы 1) после подачи сигнала "Сброс" на его вход 1,6, причем предварительно внешний сигнал "Сброс" подается на вход 47 микропроцессорной системы, стробируется в тактовом генераторе 2 и с его выхода 2.6 поступает на соответствующий вход микропроцессора 1; 2) после установления уровня логической "1" на входе готовности 48 микропроцессорной системы, который проходит через второго элемент И 34, второй вход которого активирован после сброса, обнуляющею регистры 15, 32 через элемент ИЛИ 17, выходом схемы сравнения 33, на соответствующий вход тактового генератора 2, причем с выхода 2.7 тактового генератора 2 стробированный сигнал готовности поступает на вход 1.7 микропроцессора 1. Если же на входе ожидания 48 установлен сигнал логического "0", то на выходе 36 устанавливается сигнал логической "1", свидетельствующий о том, что микропроцессор 1 находится в состоянии ожидания.

Микропроцессор 1 выдает слово состояния на свои выходы/входы данных 1.2 по синхросигналу на выходе 1.8, который поступает на вход 2.3 тактового генератора 2, с выхода 2.8 которого системный строб поступает на вход синхронизации системного контроллера 3. По системному стробу в системный контроллер 3 записывается слово состояния с выходив/входов данных 1.2 микропроцессора 1. По слову состояния и информации на выходах управления 1.3 микропроцессора 1 системный контроллер 3 формирую шину управления 3.2 микропроцессорной системы. Системный контроллер 3 формирует также и шину данных 3.1 микропроцессорной системы и обеспечивает двунаправленную передачу данных по ней. Шину адреса 4.1 микропроцессорной системы по адресным сигналам 1.1 микропроцессора 1 формирует буфер адреса 4. После формирования шин адреса 4.1, данных 3.1 и управления 3.2 микропроцессор начинает чтение и выполнение программы, записанной в постоянной памяти 6, начиная с нулевого адреса (после сброса программный счетчик микропроцессора 1 обнуляется). Дешифратор адреса памяти 5 активирует свой выход 5.1, так как на шине адреса микропроцессорной системы 4.1 выставлен адрес постоянной памяти 6 (после сброса - нулевой), а на шине управления 3.2 установлен активный сигнал 3.2.1 чтения памяти, в связи с чем элемент ИЛИ 11 активирует вход разрешения дешифратора адреса памяти 5. Активный уровень на выходе 5.1 дешифратора адреса памяти 5 подключает постоянную память 6 по первому входу разрешения. По второму входу разрешения постоянная намять 6 подключается сигналом чтения 3.2.1 с шины управления 3.2.

Команды и данные считываются в микропроцессор 1 в соответствии с адресом, выставленном на шине адреса 4.1 Например, может выполняться программа начальной загрузки из внешних запоминающих устройств в оперативную память 7. Для записи информации в оперативную память 7 активируется выход записи 3.2.2 шины управления 32 микропроцессорной системы, и, соответственно, выход 5.2 дешифратора адреса памяти 5, так как на шине адреса 41 в этом случае выставляется адрес оперативной памяти 7. При этом вход разрешении оперативной памяти 7 активируется выходом 5.2 дешифратора адреса памяти 5, ее вход записи активируется выходом 3.2.2 шины управления 3.2. Данные записываются с шины данных 3.2 в соответствующую ячейку оперативной памяти 7.

При чтении оперативной памяти 7 микропроцессорная система работает аналогично, за исключением того, что не активируется выход 3.2.2 шины управления 3.2, активируется выход чтения 3.2.1 шины управления 3.2. Информация из оперативной памяти 7 считывается на шину данных микропроцессорной системы 3.1, через системный контроллер 3 - на выходы/входы 1.7 микропроцессора 1 и в микропроцессор 1 в соответствии с адресами, выставленными на шине адреса 4.1.

Таким образом, выполняется программа управления технологическим оборудованием. При необходимости перехода на подпрограммы часть оперативной памяти 7 используется как стек.

Микропроцессорная система вводит данные со своих дискретных информационных входов 43.1. ..43.r или выводит данные на свои информационные выходы 44.1...44.r. При вводе/выводе данных активными уровнями сигналов ввода 3.2.3 либо вывода 3.2.4 (ввод или вывод) выход элемента ИЛИ 11 активирует вход разрешения дешифратора адреса устройств ввода/вывода 8, который дешифрирует адрес устройства ввода/вывода, установленный на шине адреса 4.1, при вводе/выводе информации с входов 43 (на входы 44) активируется один из выходов группы выходов 8.1, подключающий один из г шинных формирователей ввода/вывода 9 по первому входу разрешения. Режим работ шинных формирователей ввода/вывода 10 определяется информацией 3.2.3 на втором входе разрешения, причем при активировании сигнала ввода 3.2.3 шинные формирователи ввода/вывода 9 переводятся в режим ввода с входов 43, в противном случае - в режим вывода на выходы 44. Так, в том числе может вводиться программа с внешних накопителей в оперативную память 7 с помощью дополнительных технических средств.

Микропроцессорную систему можно перевести в режим прерывания подачей сигнала логической "1" на вход 35, при этом, если прерывания разрешены, снимается cигнал разрешения прерывания с выхода 37. Данный режим в предлагаемой микропроцессорной системе не рассматривается. По сигналу логической "1" на входе захвата 34 микропроцессор 1 переводит выходы адреса 1.1 и выходы/входы данных 1.2 в состояние высокого импеданса, формирует на выходе 1.3.2 сигнал подтверждения захвата, который переводит выходы/входы 3.1, а выходы 3.2 системного контроллера 3 в состояние высокого импеданса, в это же состояние по первому и второму входам разрешения переводятся выходы 4.1 буфера адреса. Режим захвата в данной микропроцессорной системе также не используется.

Микропроцессорная система может вводить информацию с аналоговых датчиков. При этом часть групп входов 43 используется для снятия информации с внешнего АЦП, а часть групп выходов 44 используется для управления ЦАП, в том числе и с целью управления аналоговыми исполнительными органами с помощью дополнительных технических средств.

б) Режим реализации дисциплины программно-аппаратной унификации алгоритмов управления с контролем ветвлений.

В этом режиме микропроцессорная система выполняет программы управления технологическим оборудованием, контролируя последовательности ее выполнения на основе конечно-автоматной модели с контролем ветвлений. Декомпозиция конечно-автоматной модели обеспечивается так же, как и в прототипе. Отличие заключается в процессе формирования информации, предназначенной для записи в триггеры логических условий 14. Перед выполнением условного перехода микропроцессор выполняет команду вывода (например, OUT port N) но адресу триггepa готовности 20 (в программу дополнительно включаются команды вывода). При этом возбуждается выход 8.3.1 дешифратора адреса устройств ввода-вывода 8. Предварительно, перед началом функционирования системы триггер готовности 20 обнулен сигналом системного сброса с выхода 2.6 генератора 2 через четвертый элемент ИЛИ 28. Триггер готовности 20 устанавливается по переднему фронту сигнала 8.3.1, поскольку на его входе D логическая единица (для ТТЛ-схем неподключенный вход эквивалентен логической единице, для других типов схем необходимо подключить вход D к источнику питания "+" через ограничительный резистор). Байт управления записью признаков по сигналу 3.2.1 записывается в регистр управления. Выход триггера готовности 20 активирует первый вход элемента И 29, подготавливая его к срабатыванию. Элемент И 29 срабатывает при выдаче информации из микропроцессора для записи в оперативную память 7, то есть при возбуждении сигнала 3.2.2 "Запись в память" на шине управления 3.2. Этот сигнал 5удет возбужден и при выполнении команды записи в стек слова состояния процессора, например, PUSH PSW. Именно это слово состояния и хранит информацию о признаках последней выполненной в арифметико-логическом устройстве процессора операции. Таким образом, необходимо выполнить требуемую для выполнения условного перехода операцию (например, вычитания из операнда операнд), установить триггер готовности 20 командой вывода, несущей информацию о номере переменной и номере признака, записываемой в регистр 21, выполнить команду записи в стек слова состояния. По последней команде в стек (находящийся в оперативной памяти 7) записывается содержание аккумулятора и содержимое регистра признаков микропроцессора, т. е. два байта, сопровождаемые сигналом записи 3.2.2. Поэтому содержимое аккумулятора по первому сигналу записи 3.2.2 помимо записи в стек будет записано и в первый регистр признаков 22. Одновременно во второй peгистр признаков 23 будет записана информация из первого регистра признаков 41, а поскольку регистры 22, 23 обнулены перед началом работы сигналом системного сброса, 2.6 - нулевая информация. Кроме того, сигналом с выхода элемента И 29 установится по переднему фронту счетный триггер 26, также обнуленный перед началом работы сигналом системного сброса 2.6 через четвертый элемент ИЛИ 28. По второму сигналу записи 3.2.2 на шину данных выдается содержимое регистра признаков микропроцессора, которые, помимо записи в соответствующую ячейку стека, по сигналу с выхода элемента И 29 будут записаны в первый регистр признаков 22, содержимое которого будет переписано во второй регистр признаков 23 одновременно с этим. Таким образом, информация о результатах операции, предшествующей команде условного перехода - содержимое аккумулятора микропроцессора, содержимое регистра признаков микропроцессора устанавливается на соответствующих выходах 42, 41. Кроме того, информация о номере логического условия и номере проверяемого признака уже установлена на соответствующих выходах 45, 46 с выходов регистра управления записью признаков 21. Информация о содержимом первого регистра признаков 22 поступает на информационные входы мультиплексора 24, на адресные входы которого поступает код номера признака с регистра 21, поэтому на выходе мультиплексора 24 устанавливается значение того признака, по которому предстоит условный переход.

По второму сигналу записи в память помимо вышеописанного произойдет сброс первого счетного триггер 26 и установка второго счетного триггера 27 (сигналом с инверсного выхода счетного триггера 26), поэтому активируется выход второго счетного триггера 27. С задержкой, определяемой необходимостью завершения переходных процессов записи информации в регистр 22, изменения состояния мультиплексора 24, передающего информацию о признаках на информационные входы n триггеров логических условий 14, возбуждается выход первого элемента задержки 30. Это приводит к побуждению входа разрешения дешифратора-демультиплексора 25, что в свою очередь приводит к возбуждению одного из его n выходов, что определяется адресной информацией, поступающей с первой группы выходов регистра управления записью признаков 21. Таким образом, возбуждается тот выход дешифратора-демультиплексора 25, который соответствует номеру переменной логического условия в данной программе. Поэтому информация о соответствующем признаке запишется с выходов мультиплексора 24 в триггер из группы триггеров логических условий 14, номер, которого соответствует номеру переменной логического условия в данной программе.

Далее, с задержкой, определяемой необходимым временем завершения переходных процессов при записи информации в триггер из группы n триггеров логических условий 14.1-14. n изменения состояний памяти автоматной модели 18, сработает второй элемент задержки 32, который через четвертый элемент ИЛИ 28 сбросит триггер готовности 20 и первый 26 и второй 27 счетный триггеры, подготавливая схему к приему очередной информации о признаках. Адресная информация на память автоматной модели 18 сформирована: первая группа адресных входов - кодом текущего состояния (с выхода регистра 15), нулевой вход - информацией с выхода мультиплексора 24 (значение переменной ветвления), вторая группа входов - кодом исполняемой программы с выходов регистра кода состояния программы 16, в который предварительно перед началом работы по программе записывается код исполняемой программы командой вывода, в процессе чего возбуждается выход 8.2.2 дешифратора адреса устройств ввода-вывода 8. Таким образом, на выходе блока памяти автоматной модели 18 всегда установлен код нового линейного участка программы управления технологическим оборудованием в соответствии со значением переменной условного перехода. Для восстановления значения указателя стека необходимо выполнить соответствующую команду, например, POP PSW.

Далее, микропроцессор выполняет команду условного перехода, после чего микропроцессор перед выполнением нового линейного участка программы выполняет команду вывода кода линейного участка, имеющегося в программе (поле, например, соответствующей предварительной компиляции, например, в виде непосредственного операнда) по адресу, возбуждающему выход 8.2.5 дешифратора адреса устройств ввода-вывода 8. При этом этот код с шины данных в регистр сравнения 32 по сигналу на его выходе информации, поступающему с выхода 8.2.5 дешифратора адреса устройств ввода-вывода. Этот же сигнал обеспечивает запись информации с выхода блока памяти автоматной модели 18 в регистр кода состояния 15. Таким образом, в регистре кода состояния 15 находится кол состояния, определяемый автоматной моделью программы: кодом предыдущего состояния и значением переменной ветвления (для данного кода программы), а в регистре сравнения 32 находится код состояния, в которое реально перешла программа после выполнения команды ветвления. При бессбойной работе микропроцессорной системы эти коды должны быть одинаковые, т.е. на выходе схемы сравнения 33 должна быть логическая единица. В противном случае, если был выполнен переход ошибочно, на выходе схемы сравнения формируется логический ноль, и через второй элемент И 34 сигнал готовности с соответствующего входа тактового генератора 2 будет снят, что приведет и к обнулению входа готовности 1.7 микропроцессора 1. Сигнал готовности анализируется микропроцессором 1 перед началом исполнения очередной команды, поэтому переходные процессы изменения состояний входов схемы сравнения 33 не приводят к нарушению вычислений. Таким образом, очередная команда не будет выполнена, а на выходе ошибки ветвления 50 будет установлен нулевой сигнал ошибки ветвления.

Информация о коде текущего линейного участка и значениях переменных программы выдается на группу выходов контроля входного вектора автоматной модели 38, информация о коде исполняемой программы выдается на входы программы 39, информация о последующем коде линейного участка (для данного состояния выхода мультиплексора 24) выдается на выходе контроля автоматной модели 40. Совместно с информацией на выходах 41 контроля регистра признаков и выходах контроля 42 второго регистра признаков, выходах контроля номера логического условия 45 и выходах контроля номера признака 46 эта информация может быть использована как для контроля средств контроля, так и для контроля вычислительного процесса.

Микропроцессор 1 может использовать информацию, имеющуюся в регистре кода состояния 15. Для этого выполняется команда ввода по адресу шинного формирователя автоматной модели 19. Активизируется выход 8.2.4 дешифратора адреса устройств и ввода-вывода 8, который по входу разрешения подключает шинный формирователь автоматной модели 19, передающей информацию с выходов блока памяти автоматной модели 18 на шину данных 3.1, а далее - в микропроцессор.

Микропроцессор 1 может использовать информацию, имеющуюся в регистре кода программы 16. Для этого выполняется команда ввода по адресу шинного формирователя кода программ 13. Активизируется выход 8.2.1 дешифратора адреса устройств ввода-вывода 8, который по входу разрешения подключает шинный формирователь кода программ 13, передающий информацию с выходов регистра кода программ 16 на шину данных 3.1 и далее - в микропроцессор.

Для повышения достоверности функционирования микропроцессорной системы возможно двукратное выполнение операции перед ветвлением. По первому выполнению производится фиксация признаков аналогично выше описанному, а по второму - собственно ветвление.

Микропроцессорная система может проверить входной вектор автоматной модели, установленный на выходе 38 и представляющий собой конкатенацию (сцепление) кода логических условий на выходах n триггеров логических условий 14.1-14.n и кода текущего состояния с выходов регистра состояния 15. При этом соответствующая информация передается на шину данных 32 через шинный формирователь входного вектора автоматной модели 12 по разрешающему сигналу 8.2.3 дешифратора адреса устройств ввода-вывода, поступающему при выполнении команды ввода по адресу шинного формирователя входного вектора автоматной модели 12. Триггеры логических условии 14.1-14n и регистр кода состояния 15 могут быть обнулены сигналом 8.3.4 дешифратора адреса устройств ввода-вывода 8 при выполнении команды ввода или вывода по соответствующему адресу, что выполняется с началом отработки очередной программы.

Перед началом работы или отработки очередной программы регистры кода состояния 15 и сравнения 32 обнулены выходом третьего элемента ИЛИ 17.

Для контроля безусловных переходов микропроцессор аналогично вышеописанному производит команду вывода в регистр сравнения 32, в результате чего вновь произойдет сравнение кодов реально выполняемого линейного участка (в регистре сравнения 32) и кода, полученного с выхода блока памяти автоматной модели 18 и записанного в регистре кода состояния 15.

По выходам контроля выполнения программы 51 внешнее оборудование с использованием, например, сторожевого таймера может оценивать допустимые интервалы выполнения программ с момента установки кода первого линейного участка (начало программы) до момента обнуления регистра сравнения 32 (конец программы).

Возможно также проконтролировать другие результаты операций - не только операций перед условными переходами. Для этого в произвольной точке программы необходимо выполнить команды, аналогично вышеописанным командам, обеспечивающим запись информации в регистры признаков 22, 23, а в группе n триггеров логических условий 14 предусмотреть один из триггеров для записи этой дополнительной информации.

После обнаружения ошибки ветвления может производиться сброс и начинает выполняться программа тестирования, включающая тестирование средств контроля. При этом правильность формирования сигналов на выходах контроля входного вектора автоматной модели 38 проверяется путем ввода информации через шинный формирователь входного вектора автоматной модели 12; на выходах кода программы 39 -путем ввода информации через шинный формирователь автоматной модели 19; на выходах контроля выполнения программы 51, выходах контроля номера признака 46, выходах контроля номера логического уровня 45, выходах контроля 41 первого регистра признаков, выходах контроля 42 второго регистра признаков может проверяться путем подключения с помощью дополнительных технических средств через входы в группе r информационных входов 43.1...43.r.

Для устранения сбоев возможно неоднократное проведение операции перед ветвлением. После обнаружения ошибки ветвления с помощью дополнительных технических средств, зафиксировав состояние выходов контроля выполнения программы 51, может инициировать процесс повторения операции, после которой была обнаружена ошибка ветвления.

При тестировании средств контроля может использоваться сигнал обнуления 8.3.4 группы выходов 8.3 дешифратора устройств ввода-вывода 8, когда производится команда ввода/вывода по соответствующему адресу.

Признаковая информация, записываемая в первый 21 и второй 22 регистры признаков, может сравниваться с признаковой информацией, записанной в стек, находящийся в оперативной памяти 7.

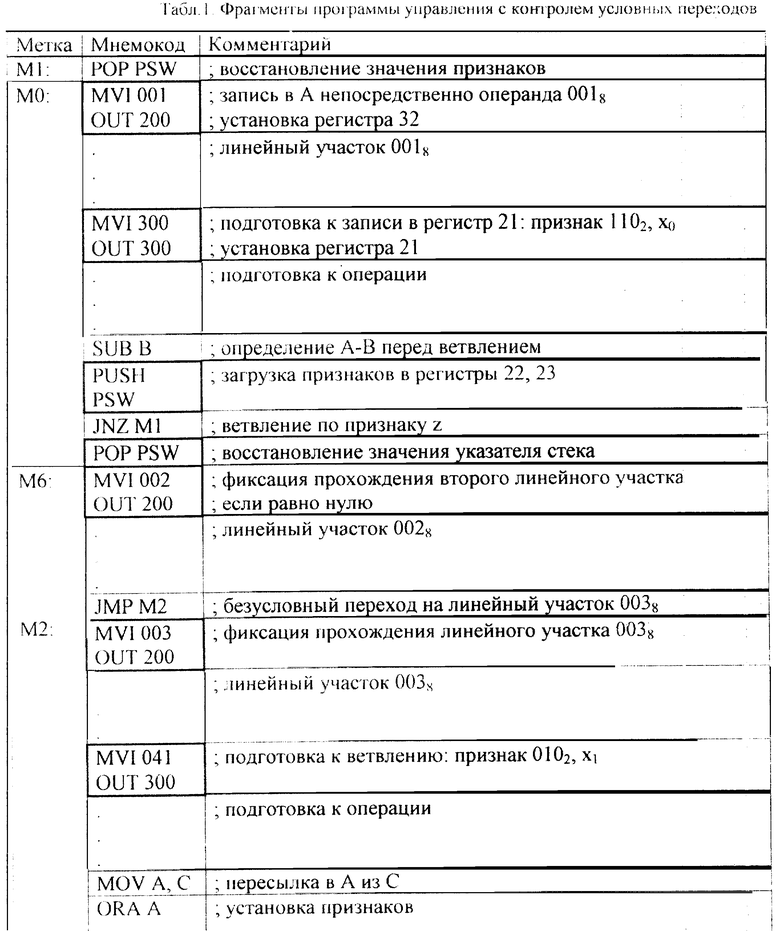

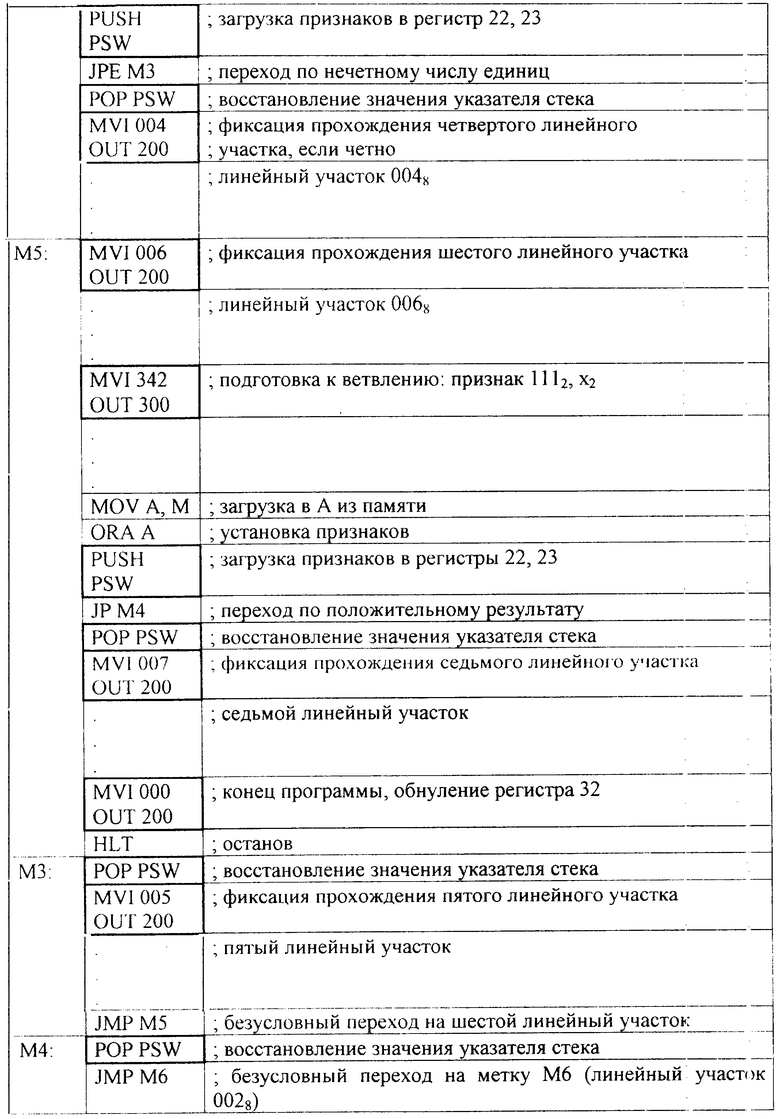

Рассмотрим пример конкретного выполнения системы для программного управления технологическим оборудованием.

Распределение портов в восьмеричном коде: 2008 - регистр сравнения 32 (для записи номера выполняемого линейного участка); 3008 - регистр управления записью признаков 21. Номера признаков: знак (S)-1112, ноль (z)-1102, вспомогательный перенос (АС)-1002, четность (Р)-0102, перенос (С)-0002.

Распределение разрядов информации в регистре управления записью признаков: номер признака - разряды 7,6,5; номер переменной - разряды 4,3,2,1,0.

Пусть граф исполняемой программы имеет вид, представленный на фиг.2.

На графе (фиг.2) ребра - это линейные участки, отмеченные восьмеричными кодами своих номеров; дуги, помеченные значениями переменных, описывают ветвление программы. Тогда фрагменты некоторой программы управления технологическим оборудованием с контролем условных переходов (Язык Ассемблер-80) могут быть описаны таблицей 1. В таблице 1 обведены те команды, которые введены с целью контроля.

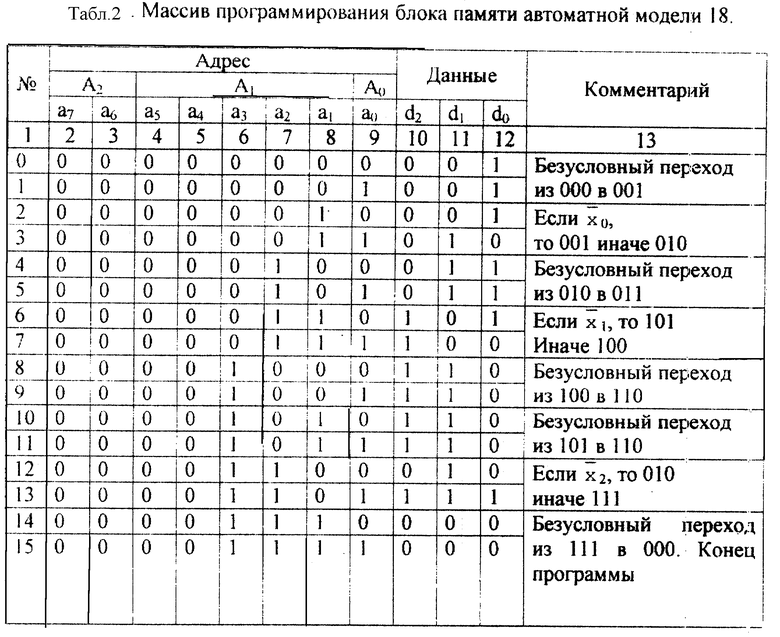

Графу исполняемой программы (фиг.2) соответствует массив программирования блока памяти автоматной модели (табл.2).

Допустим, исполняется программа с нулевым номером, т.с регистр кода программы 16 обнулен (фиг. 1)

В исходном состоянии регистр кода состояния 15 и регистр сравнения 32 обнулены сигналом системном сброса 2.6. Обнулены и регистр управления записью признаков 21, первый 22 и второй 23 регистры признаков. Тогда адресные входы блока памити автоматной модели 18 также обнулены. Код не зависит от значения переменной, поэтому записан в двух строках, хотя на выходе мультиплексора 24 в исходном состоянии - ноль. Поэтому на выходе установлен код следующего состояния 0012. После начала программы с метки М0 (табл. 1) микропроцессор выводит код следующего состояния 0018 по адресу 2008, т.е. возбуждается выход 8.2.5 дешифратора адреса устройств ввода-вывода 8, в регистр сравнения 32 записывается код 0012, а в регистр кода состояния 15 - информация с выхода блока памяти автоматной модели 18. На выходе схемы сравнения так же, как и в исходном cocтоянии, поддерживается логическая единица.

Завершив вынолнение линейного участка программы (табл.2) микропроцессор выводит в регистр управления записью признаков код  что означает, что будет провериться признак 1102 (ноль-z), и это нулевая переменная x0 (000). Далее выполняется подготовка к операции, устанавливающей значение признака. Пусть такой операцией будет вычитание из содержимого регистра - аккумулятора (А) содержимое регистра (В).

что означает, что будет провериться признак 1102 (ноль-z), и это нулевая переменная x0 (000). Далее выполняется подготовка к операции, устанавливающей значение признака. Пусть такой операцией будет вычитание из содержимого регистра - аккумулятора (А) содержимое регистра (В).