Изобретение относится к импульсной технике, может быть использовано в счетных устройствах вычислительной техники и систем управления, содержащих встроенные схемы контроля и диагностики.

Цель изобретения увеличение полноты контроля.

Поставленная цель достигается за счет введения новых конструктивных признаков, обеспечивающих дополнительный контроль состояния всех разрядных триггеров на начальном этапе работы счетчика.

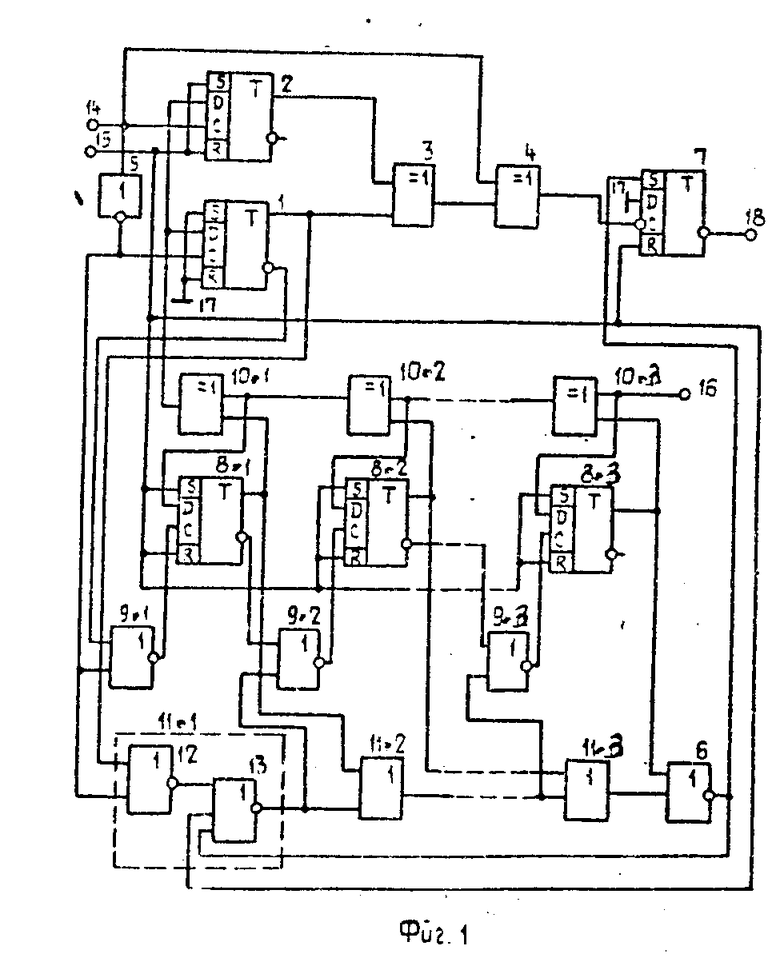

На фиг.1 представлена схема предлагаемого счетчика импульсов в коде Грея с контролем; на фиг.2 схема синхронного D-триггера со статическим управлением и установочными R-, S-входами.

Счетчик содержит первый, второй управляющие D-триггеры 1, 2 со статическим управлением, первый, второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 3, 4, инвертор 5, элемент ИЛИ-НЕ 6, D-триггер 7 с инверсным тактовым входом, D-триггеры 8.1-8.3 разрядов, элементы ИЛИ-НЕ 9.1-9.3 разрядов, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 10.1-10.3 разрядов, логический элемент 11.1 первого разряда, элементы ИЛИ 11.2, 11.3 старших разрядов, первый, второй дополнительные элементы ИЛИ-НЕ 12, 13 логического элемента 11.1, шину 14 счетных импульсов, шину 15 обнуления, шину 16 управления, шину 17 нулевого потенциала, контрольный выход 18.

Первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 10.1-10.3 соединены соответственно с информационными входами D-триггеров 8.1-8.3, выходами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 10.2, 1.3 и шиной 16 управления. Вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 10.1-10.3 соединены соответственно с прямыми выходами D-триггеров 8.1-8.3 и первыми входами элементов ИЛИ 11.2, 11.3 и ИЛИ-НЕ 6. Инверсные выходы D-триггеров 1, 8.1, 8.2 соединены соответственно с первыми входами элементов ИЛИ-НЕ 9.1-9.3, выходы которых соединены соответственно с тактовыми входами D-триггеров 8.1-8.3. Первый вход элемента ИЛИ-НЕ 12 соединен с прямым выходом D-триггера 1 и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3, второй вход и выход которого соединены соответственно с прямым выходом D-триггера 2 и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4, выход и второй вход которого соединены соответственно с инверсным тактовым входом D-триггера 7 и шиной 14 счетных импульсов, которая соединена с тактовым входом D-триггера 2 и через инвертор 5 с тактовым входом D-триггера 1 и вторыми входами элементов ИЛИ-НЕ 9.1 и 12. Выход последнего соединен с первым входом элемента ИЛИ-НЕ 13, выход которого соединен с вторыми входами элемента ИЛИ-НЕ 9.2 и элемента ИЛИ 11.2, выход которого соединен с вторыми входами элемента ИЛИ-НЕ 9.3 и элемента ИЛИ 11.3, выход которого соединен с вторым входом элемента ИЛИ-НЕ 6. Выход последнего соединяется с вторым входом элемента ИЛИ-НЕ 13 и установочным S-входом D-триггера 7, информационный вход и инверсный выход которого соединены соответственно с шиной 17 и контрольным выходом 18. Шина 17 соединена с входами S и R установки D-триггера 1. Шина 15 обнуления соединена с входами S установки D-триггеров 2, 8.1-8.3, входами R сброса D-триггеров 2, 7, 8.1-8.3 и третьим входом элемента ИЛИ-НЕ 13.

Управляющие D-триггеры 1 и 2, разрядные D-триггеры 8.1, 8.2, 8.3, D-триггер 7 построены на основе логических элементов ИЛИ-НЕ с помехозащищающими RC-элементами в цепи обратной связи и двунаправленным ключом. Схема D-триггера, представленная на фиг.2, является схемой со статическим управлением, содержит первый и второй элементы ИЛИ-НЕ 19, 20, первый и второй резисторы 21, 22, конденсатор 23, двунаправленный ключ 24. Вход ключа 24 является информационным входом D-триггера, управляющий вход тактовым входом D-триггера, выход соединен с первым входом элемента ИЛИ-НЕ 19 и через резистор 21 с первым выводом конденсатора 23. Второй вход элемента ИЛИ-НЕ 19 является установочным S-входом D-триггера, выход соединен с первым входом элемента ИЛИ-НЕ 20 и является инверсным выходом D-триггера. Второй вход элемента ИЛИ-НЕ 20 является установочным R-входом D-триггера, выход через резистор 22 соединен с первым выводом конденсатора 23 и является прямым выходом D-триггера. Второй вывод конденсатора 23 соединен с шиной 17 нулевого потенциала счетчика. При использовании D-триггера (фиг.2) в качестве D-триггера 7 с инверсным тактовым входом на его С-входе устанавливают дополнительный инвертор сигнала.

Счетчик импульсов в коде Грея с контролем работает следующим образом.

При правильном функционировании счетчика при поступлении на шину 15 обнуления импульса положительной полярности разрядные D-триггеры 8.1, 8.2, 8.3, D-триггер 2 управления и D-триггер 7 устанавливаются в исходное нулевое состояние, характеризующееся наличием сигнала "лог.0" на прямом выходе (Q) и сигнала "лог. 1" на инверсном выходе (Q). Подключение установочных S-входов D-триггеров 2, 8.1, 8.2, 8.3 соответственно к R-входам этих триггеров позволяет исключить влияние затянутого фронта сигнала на первом входе элемента ИЛИ-НЕ 19 (см. фиг. 2) при закрытом двунаправленном ключе 24 при действии импульса обнуления на D-триггер, находящийся в состоянии "лог.1" (конденсатор 23 заряжен). В процессе действия импульса обнуления на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10.1 первого разряда действует такой же сигнал, как и на шине 16 управления счетчика. Пусть для определенности счетчик работает в режиме сложения. Тогда на шине 16 всегда действует сигнал "лог.1". Сигнал "лог. 1" в процессе действия импульса обнуления присутствует и на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10.1.

В отсутствие счетного импульса (сигнал "лог."0" на шине 14) на тактовом входе управляющего триггера 1 сигнал "лог."1". В этом случае сигнал "лог."1" с его информационного входа проходит на прямой выход (на инверсном выходе D-триггера 1 сигнал "лог."0"). В результате на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 3, 4 и на инверсном тактовом входе D-триггера 7 действует сигнал "лог. "1". Подготавливается к переключению элемент ИЛИ-НЕ 9.1 первого разряда (устанавливается сигнал "лог."0" на его первом входе).

Импульс обнуления, действуя на третий вход элемента ИЛИ-НЕ 13, вызывает на его выходе сигнал "лог."0". При установке всех разрядов счетчика в нулевое состояние на выходе элемента ИЛИ-НЕ 6 формируется сигнал "лог."1". При одновременном воздействии сигналов "лог."1" на R- и S-входы D-триггера 7 на его прямом и инверсном выходах действуют сигналы "лог."0". После снятия импульса обнуления по шине 15 на R-входах D-триггеров 2, 8.1, 8.2, 8.3 устанавливается сигнал "лог. "0". На выходе элемента 6 и на S-входе триггера 7 сигнал "лог."1" сохраняется, так как элемент ИЛИ-НЕ 13 блокирован по второму входу сигналом "лог."1" с элемента 6 (элементы 13, 11.2, 11.3, 6 представляют собой сложный RS-триггер с одним R-входом (третий вход элемента ИЛИ-НЕ 13) и S-входами (первые входы элементов 11.2, 11.3, 6). В результате после окончания импульса обнуления D-триггер 7 устанавливается в состояние "лог. "1", т.е. на его инверсном выходе и контрольном выходе 18 счетчика сохраняется сигнал "лог."0". Сигнал "лог."0" на выходе 18 счетчика информирует о его правильном функционировании в процессе обнуления и счета и в дальнейшем должен сохраняться.

При поступлении первого счетного импульса положительной полярности по шине 14 счетчика происходит переключение в состояние "лог."1" D-триггера 8.1 первого разряда (счетный импульс проходит на выход элемента ИЛИ-НЕ 9.1, на информационном входе D-триггера 8.1 сигнал "лог."1"). Сигнал "лог."0" на инверсном выходе D-триггера 8.1 подготавливает к переключению элемент ИЛИ-НЕ 9.2 второго разряда по первому входу, сигнал "лог."1" на прямом выходе триггера 8.1 изменяет полярность сигнала на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10.1 первого разряда, а значит, на информационных входах D-триггеров 1.2 сигнал "лог. "0". Во время действия счетного импульса D-триггер 1 не переключается под действием сигнала на его информационном входе, т.к. на тактовом входе D-триггера 1 сигнал "лог."0", D-триггер 2 под действием сигнала на его информационном входе переключается в состояние "лог."0". На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3 появляется сигнал "лог."0", на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4 сохраняется сигнал "лог."1".

В результате переключения D-триггера 8.1 первого разряда на первом входе элемента ИЛИ 11.2 появляется сигнал "лог."1", устанавливающий выход элемента ИЛИ-НЕ 6 и S-вход триггера 7 в состояние "лог."0". Таким образом, с момента начала действия первого счетного импульса D-триггер 7 готов к переключению по инверсному тактовому входу, но при правильном функцио- нировании счетчика во время первого счетного импульса своего состояния не изменяет ("лог."0" на инверсном выходе D-триггера 7).

В паузе между первым и вторым счетными импульсами D-триггер 1 воспринимает информацию с элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10.1, т.е. устанавливается в состояние "лог."0". Состояние D-триггера 2 ("лог."1") сохраняется. Изменение сигнала на прямом выходе D-триггера 1 и на первом входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3 компенсируется изменением полярности сигнала на втором входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4. В результате на выходе последнего и инверсном тактовом входе D-триггера 7 сохраняется сигнал "лог."1".

На контрольном выходе 18 счетчика сохраняется сигнал "лог."0".

При поступлении по шине 14 второго и последующих счетных импульсов происходит переключение разрядов счетчика в соответствии с логикой кода Грея: нечетными счетными импульсами переключается триггер 8.1 первого разряда, четными переключаются старшие разряды счетчика. При этом переключение осуществляется в разряде, следующем за самыми младшим, находящимся в состоянии "лог."1".

Рассмотрим работу схемы счетчика в случае, если один или несколько его разрядов не установились в исходное состояние на начальном этапе его работы. В этом случае до момента окончания импульса обнуления по шине 15 на одном или нескольких прямых выходах триггеров 8.1, 8.2, 8.3 появляется потенциал "лог."1", что приводит к снятию сигнала "лог."1" на выходе элемента ИЛИ-НЕ 6 и на S-входе D-триггера 7. В результате после окончания импульса обнуления D-триггер 7 остается в состоянии "лог."0", т.е. на его инверсном выходе появляется сигнал "лог. "1", сигнализирующий о неправильном функционировании схемы. Важно подчеркнуть, что в схема счетчика-прототипа обнаруживалась неустановка в исходное состояние только нечетного количества разрядов счетчика, поскольку для анализа неисправностей там использовался выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первого разряда. Одновременное изменение сигналов вследствие неисправностей элементов на выходах четного количества разрядов не приводит к изменению сигнала на выходе указанного элемента. В данной схеме обнаруживается неустановка в исходное состояние любого числа разрядов счетчика.

Рассмотрим, как обнаруживаются сбои в работе схемы счетчика, начиная с момента действия по шине 14 первого счетного импульса. Как было показано, в этот момент времени прекращается действие сигнала установки по S-входу D-триггера 7, и в дальнейшем переключение D-триггера может произойти только под действием фронта сигнала отрицательной полярности по его инверсному тактовому входу. Во время действия счетного импульса на шине 14 присутствует сигнал "лог. "1", управляющий D-триггер 2 воспринимает сигнал с элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10.1 первого разряда. Если во время действия счетного импульса в любом такте работы счетчика произошло переключение не одного, а двух, четырех и т.д. т.е. любого четного количества разрядов, или вообще ни один разряд счетчика не переключился, на прямом выходе D-триггера 2 фиксируется сигнал, противоположный сигналу на прямом выходе D-триггера 1. Тогда на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3 формируется сигнал "лог."1", а на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4 сигнал "лог."0". Этот же сигнал действия на инверсном тактовом входе D-триггера 7 вызывает переключение его в состояние "лог. "0" ("лог."1" на контрольном выходе 18 счетчика). В паузе между счетными импульсами на шине 14 действует сигнал "лог."0", сигнал с элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10.1 воспринимается D-триггером 1. Если во время паузы между счетными импульсами в любом такте работы счетчика произошло переключение одного, трех и т.д. т.е. любого нечетного количества разрядов счетчика, на прямом выходе D-триггера 1 фиксируется сигнал того же логического уровня, что и на прямом выходе D-триггера 2. Нетрудно проследить, что это приводит к появлению сигнала "лог. "0" на инверсном тактовом входе D-триггера 7 и вызывает его переключение. На контрольном выходе 18 счетчика появляется сигнал ошибки уровень "лог."1".

Таким образом, из описания видно, что предлагаемый объект по сравнению с прототипом обладает повышенной полнотой контроля за счет организации в схеме дополнительного контрольного сигнала (формируется на выходе элемента ИЛИ-НЕ 6), несущего информацию о состоянии всех разрядных триггеров на начальном этапе работы счетчика, с последующей передачей этого и основного контрольного сигнала (формируется на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4) на контрольный выход счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ С КОНТРОЛЕМ | 1997 |

|

RU2129332C1 |

| Счетчик импульсов | 1985 |

|

SU1298906A1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1995 |

|

RU2113007C1 |

| Счетчик импульсов | 1986 |

|

SU1422404A1 |

| Устройство для контроля многоканальных импульсных последовательностей | 1989 |

|

SU1732332A1 |

| Счетчик - делитель | 1989 |

|

SU1674362A1 |

| Устройство для анализа формы однократных электрических импульсов | 1983 |

|

SU1095103A1 |

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ | 1991 |

|

RU2042268C1 |

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ | 1987 |

|

SU1499711A1 |

| ПЕРЕСЧЕТНОЕ УСТРОЙСТВО С КОНТРОЛЕМ | 2003 |

|

RU2264031C2 |

Изобретение относится к импульсной технике, может быть использовано в счетных устройствах вычислительной техники и систем управления, содержащих схемы контроля и диагностики. Цель - увеличение полноты контроля - достигается за счет введения D - триггера 7 с инверсным тактовым входом, элемента ИЛИ - НЕ 6 и реализации логического элемента 11.1 в виде двух дополнительных элементов ИЛИ - НЕ 12, 13. Устройство также содержит управляющие D - триггеры 1,2, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 3, 4, инвертор 5, D - триггеры 8.1 - 8.3, элементы ИЛИ - НЕ 9.1 - 9.3, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 10.1 - 10.3, элементы ИЛИ 11.2, 11.3, шину 14 счетных импульсов, шину 15 обнуления, шину 16 управления, шину 17 нулевого потенциала и контрольный выход 18. В предлагаемом устройстве обеспечивается дополнительный контроль состояния всех триггеров 8.1 - 8.3 на начальном этапе работы. 2. ил.

СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ С КОНТРОЛЕМ, содержащий два управляющих D-триггера со статическим управлением, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, инвертор, контрольный выход и n разрядов, где n ≥ 2, каждый из которых содержит D-триггер, элемент ИЛИ НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и логический элемент, выполненный в каждом разряде, начиная с второго, в виде элемента ИЛИ, в каждом разряде первый и второй входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с информационным входом и прямым выходом D-триггера данного разряда, в каждом разряде, кроме первого, первый вход элемента ИЛИ НЕ соединен с инверсным выходом D-триггера предыдущего разряда, прямой выход D-триггера которого соединен с первым входом логического элемента последующего разряда, второй вход логического элемента которого соединен с вторым входом элемента ИЛИ НЕ того же разряда и выходом логического элемента предыдущего разряда, в каждом разряде, кроме последнего, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ последующего разряда, первый и второй входы элемента ИЛИ НЕ первого разряда соединены соответственно с инверсным выходом и тактовым входом первого управляющего D-триггера, прямой выход которого соединен с первым входом логического элемента первого разряда и первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с прямым выходом второго управляющего D-триггера, а выход с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого подключен к шине счетных импульсов, тактовому входу второго управляющего D-триггера и через инвертор к второму входу логического элемента первого разряда и тактовому входу первого управляющего D-триггера, информационный вход которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первого разряда и информационным входом второго управляющего D-триггера, вход сброса которого подключен к шине обнуления и входу сброса D-триггера каждого разряда, тактовый вход которого соединен с выходом элемента ИЛИ НЕ данного разряда, а первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ последнего разряда соединен с шиной управления, отличающийся тем, что, с целью увеличения полноты контроля, в него введены элемент ИЛИ НЕ и D-триггер с инверсным тактовым входом, инверсный выход которого соединен с контрольным выходом, логический элемент в первом разряде содержит первый и второй дополнительные элементы ИЛИ НЕ, первый и второй входы первого дополнительного элемента ИЛИ НЕ являются соответственно первым и вторым входами логического элемента, в котором выход первого дополнительного элемента ИЛИ НЕ соединен с первым входом второго дополнительного элемента ИЛИ НЕ, выход которого соединен с выходом логического элемента, первый и второй входы элемента ИЛИ НЕ счетчика соединены соответственно с прямым выходом D-триггера последнего разряда и выходом логического элемента последнего разряда, а выход с вторым входом второго дополнительного элемента ИЛИ НЕ логического элемента первого разряда и установочным S-входом D-триггера с инверсным тактовым входом, установочный R-вход которого соединен с шиной обнуления и третьим входом второго дополнительного элемента ИЛИ НЕ логического элемента первого разряда, выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с инверсным тактовым входом D-триггера, информационный вход которого соединен с шиной нулевого потенциала и входами установки первого управляющего D-триггера, шину обнуления соединена с входами установки второго управляющего D-триггера и D-триггеров разрядов.

| СЧЕТЧИК ИМПУЛЬСОВ В КОДЕ ГРЕЯ | 1987 |

|

SU1499711A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-06-09—Публикация

1989-09-05—Подача