feed

с коррекции

конан о о

:л

(Put.1

Изобретение относится к радиотехнике и приборостроению и может быть использовано в синхронизирующих системах для коррекции шкапы времени.

Цель изобретения - повышение точ- ности коррекции.

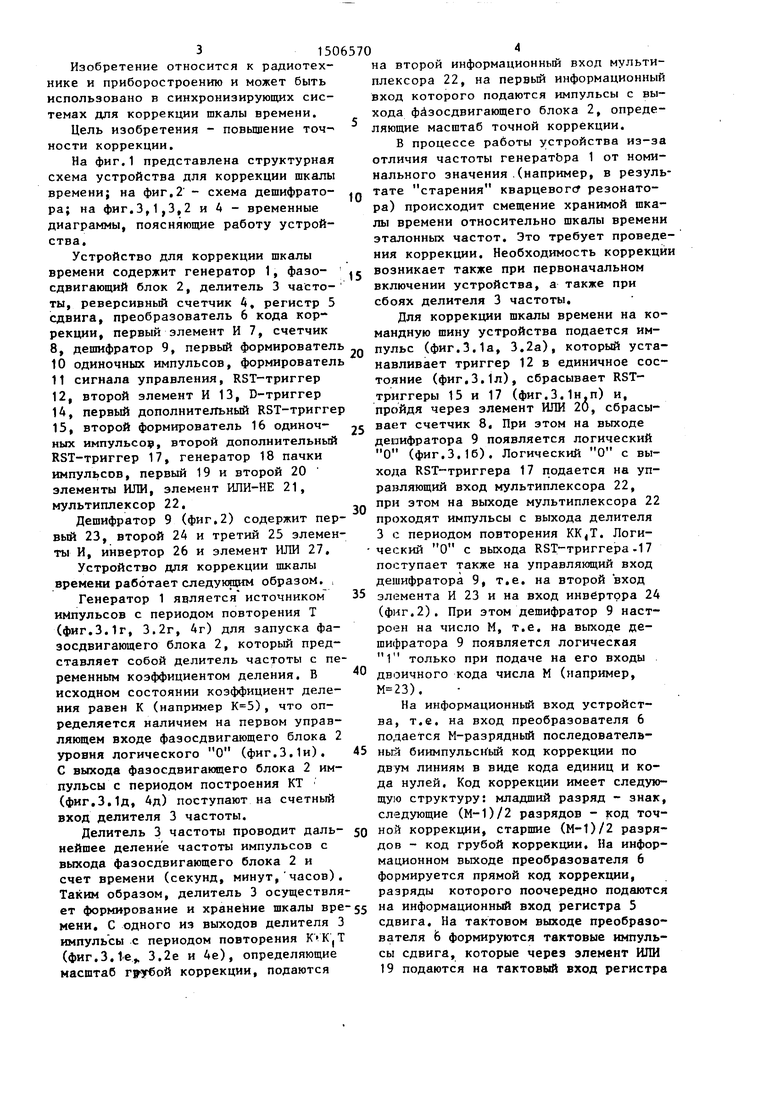

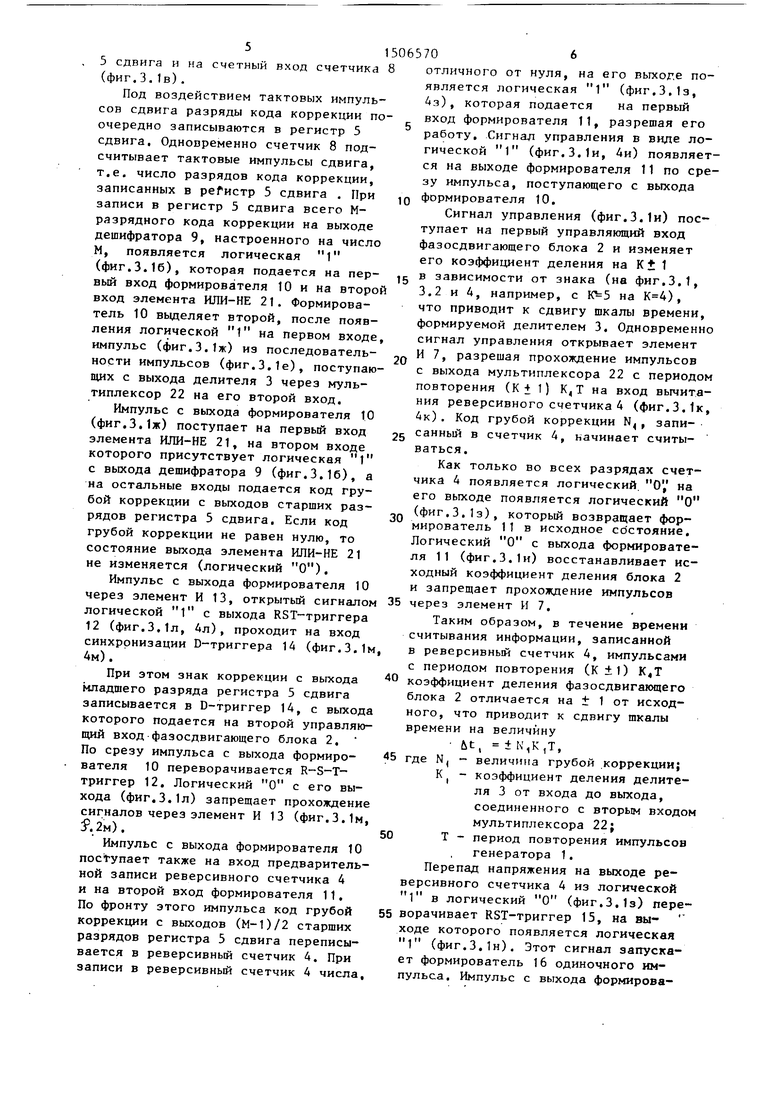

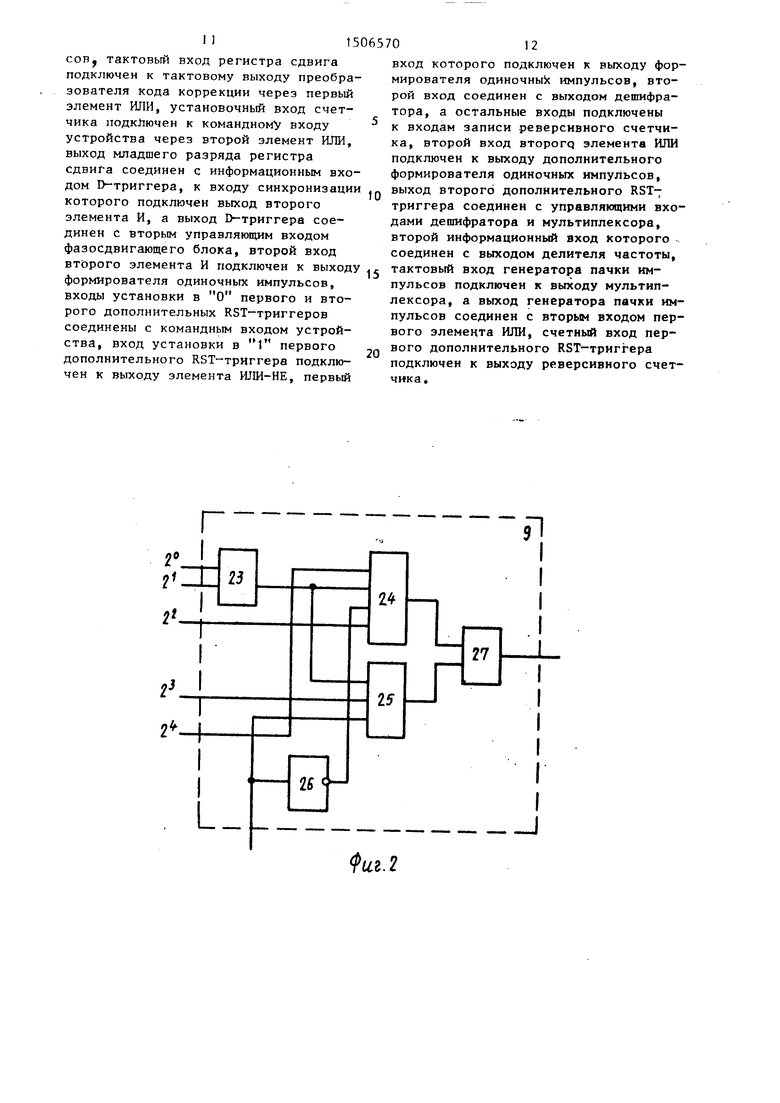

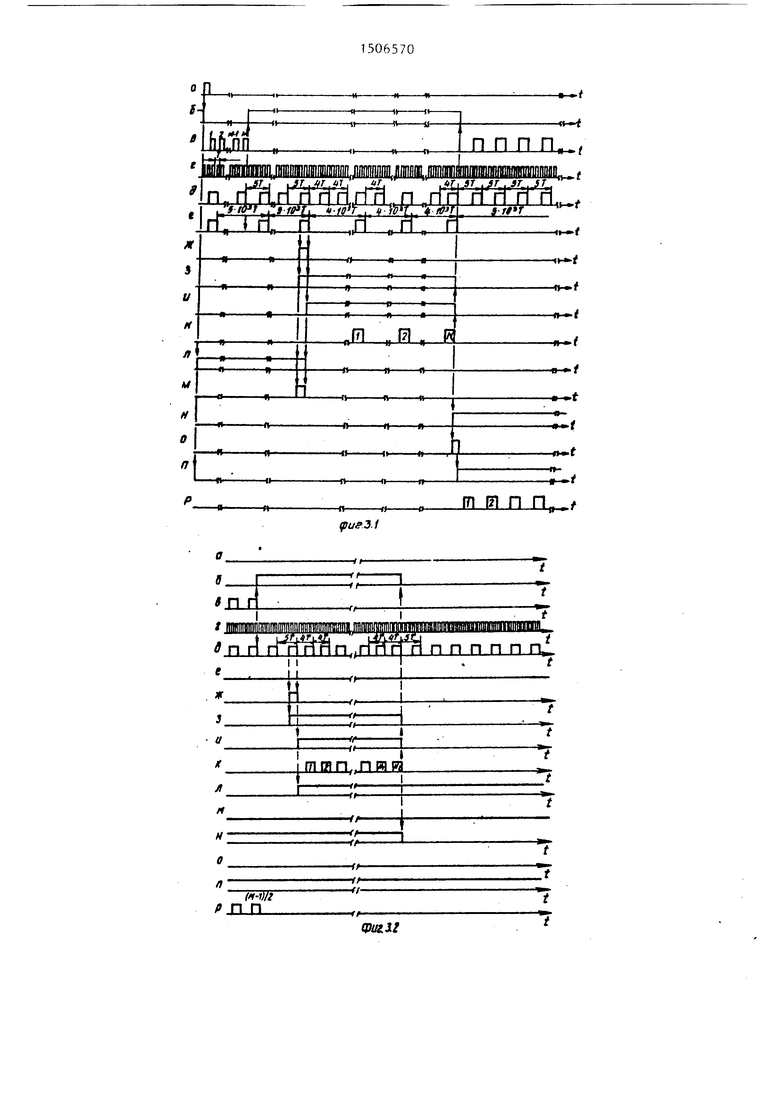

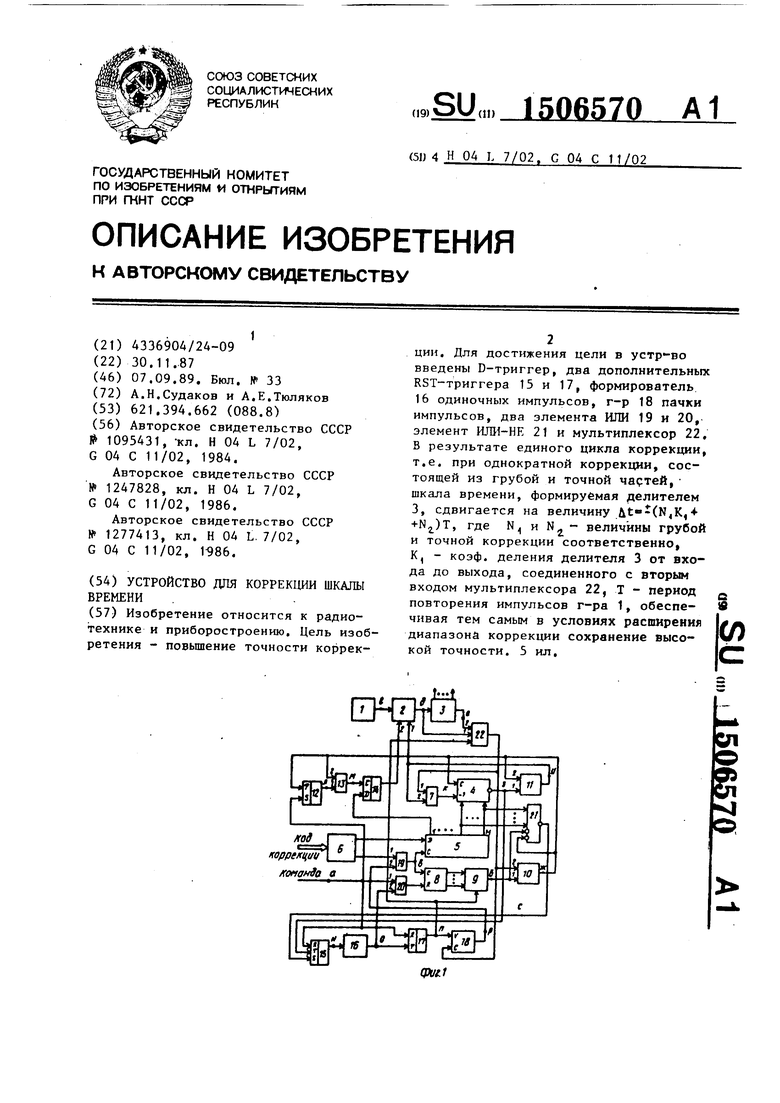

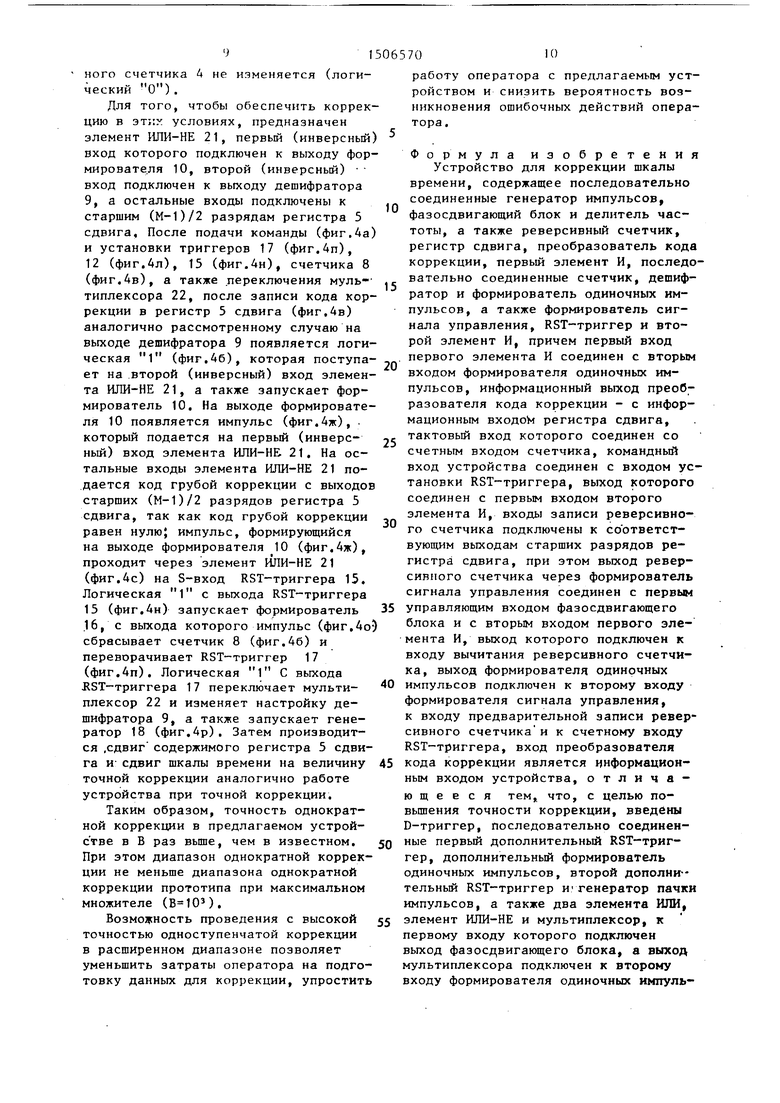

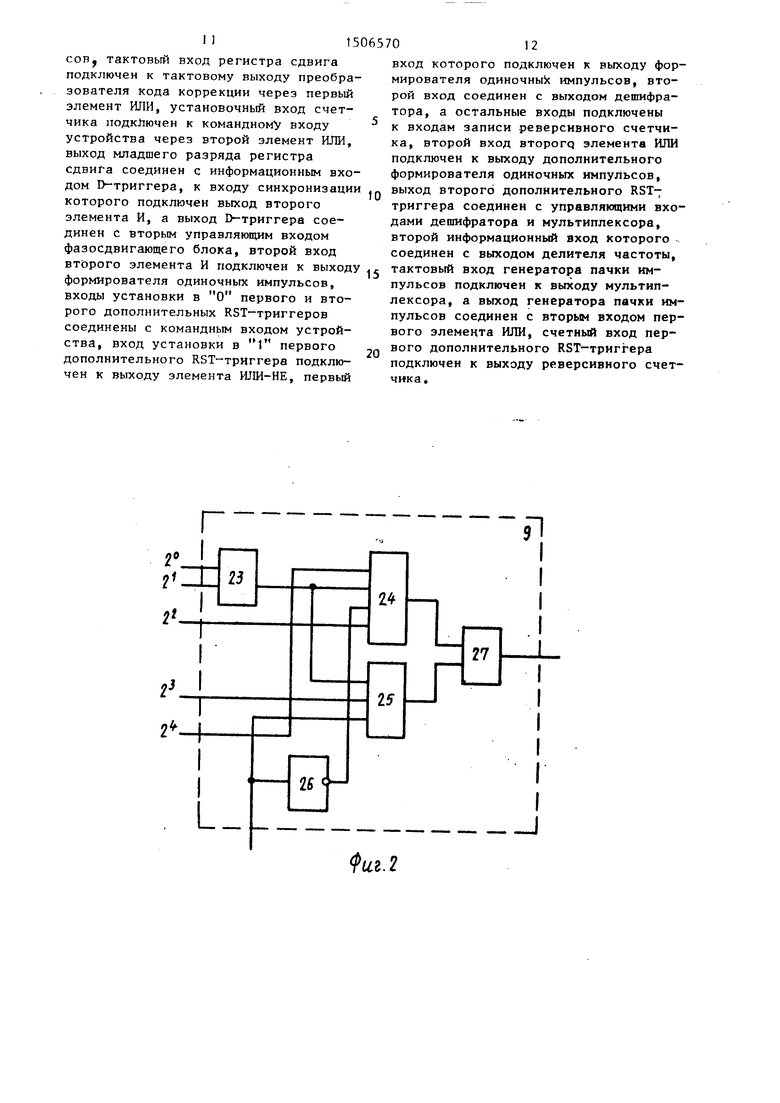

На фиг.1 представлена структурная схема устройства для коррекции шкалы времени; на фиг,2 - схема дешифрато- ра; на фиг,3,1,3,2 и А - временные диаграммы, поясняющие работу устройства.

Устройство для коррекции шкалы времени содержит генератор 1, фазо- сдвигающий блок 2, делитель 3 частоты, реверсивный счетчик 4, регистр 5 сдвига, преобразователь 6 кода коррекции, первый элемент И 7, счетчик 8, дешифратор 9, первый формирователь

10одиночных импульсов, формирователь

11сигнала управления, RST-триггер 12, второй элемент И 13, D-триггер

14,первый дополнительный RST-триггер

15,второй формирователь 16 одиноч- ных импульсо, второй дополнительный RST-триггер 17, генератор 18 пачки импульсов, первый 19 и второй 20 элементы ИЛИ, элемент ИЛИ-НЕ 21, мультиплексор 22,

Дешифратор 9 (фиг,2) содержит первый 23, второй 24 и третий 25 элементы И, инвертор 26 и элемент ИЛИ 27,

Устройство для коррекции шкалы времени работает следукл образом. .

Генератор 1 является источником импульсов с периодом повторения Т (фиг.3,1 г, 3.2г, 4г) для запуска фа- зосдвигающего блока 2, который представляет собой делитель частоты с переменным коэффициентом деления, В исходном состоянии коэффициент деления равен К (например ), что определяется наличием на первом управляющем входе фазосдвигающего блока 2 уровня логического О (фиг,3,1 и), С выхода фазосдвигающего блока 2 импульсы с периодом построения КТ (фиг.ЗЛд, 4д) поступают на счетный вход делителя 3 частоты.

Делитель 3 частоты проводит даль- нейшее деление частоты импульсов с выхода фазосдвигающего блока 2 и счет времени (секунд, минут, часов), Таким образом, делитель 3 осуществляет формирование и хранение шкалы вре мени. С одного из выходов делителя 3 импульсы с периодом повторения (фиг,3,1е,, 3,2е и 4е), определяющие масштаб грубой коррекции, подаются

0

.,

с

s

5 0 5

0

на второй информационный вход мультиплексора 22, на первый информационный вход которого подаются импульсы с выхода фАзосдвигающего блока 2, определяющие масштаб точной коррекции,

В процессе работы устройства из-за отличия частоты генератЬра 1 от номинального значения .(например, в результате старения кварцевогсг резонатора) происходит смещение хранимой шкалы времени относительно шкалы времени эталонных частот. Это требует проведения коррекции. Необходимость коррекции возникает также при первоначальном включении устройства, а также при сбоях делителя 3 частоты.

Для коррекции шкапы времени на командную шину устройства подается импульс (фиг,3,1 а, 3,2а), который устанавливает триггер 12 в единичное состояние (фиг,3,1л), сбрасывает RSTтриггеры 15 и 17 (фиг,3,1н,п) и, пройдя через элемент ИЛИ 20, сбрасывает счетчик 8, При этом на выходе дешифратора 9 появляется логический О (фиг,3,1 б). Логический О с выхода RST-триггера 17 подается на управляющий вход мультиплексора 22, при этом на выходе мультиплексора 22 проходят импульсы с выхода делителя 3 с периодом повторения , Логический О с выхода RST-триггера-17 поступает также на управляющий вход дешифратора 9, т.е, на второй вход эл1Емента И 23 и на вход инвертора 24 (фиг,2), При этом дешифратор 9 настроен на число М, т,е, на выходе дешифратора 9 появляется логическая 1 только при подаче на его входы двоичного кода числа М (например, ),

На информационный вход устройства, т,е, на вход преобразователя 6 подается М-разрядный последовательный биимпульснГый код коррекции по двум линиям в виде кода единиц и кода нулей. Код коррекции имеет следующую структуру; младший разряд - знак, следующие (М-1)/2 разрядов - код точной коррекции, старшие (М-1)/2 разрядов - код грубой коррекции. На информационном выходе преобразователя 6 формируется прямой код коррекции, разряды которого поочередно подаются на информационный вход регистра 5 сдвига. На тактовом выходе преобразователя 6 формируются тактовые импульсы сдвига, которые через элемент ИЛИ 19 подаются на тактовый вход регистра

5 сдвига и на счетный вход счетчика 8 (фиг.3.1в).

Под воздействием тактовых импульсов сдвига разряды кода коррекции поочередно записываются в регистр 5 сдвига. Одновременно счетчик 8 подсчитывает тактовые импульсы сдвига, т.е. число разрядов кода коррекции, записанных в реГистр 5 сдвига . При записи в регистр 5 сдвига всего М- разрядного кода коррекции на выходе дешифратора 9, настроенного на число М, появляется логическая 1 (фиг.3.1б), которая подается на первый вход формирователя 10 и на второй вход элемента ИЛИ-НЕ 21. Формирователь 10 выделяет второй, после появления логической 1 на первом входе.

отличного от нуля, на его вьгхог.е появляется логическая 1 (фиг.3.1з, 4з), которая подается на первый вход формирователя 11, разрешая его работу. Сигнал управления в виде логической 1 (фиг.3.1и, Ди) появляется на выходе формирователя 11 по срезу импульса, поступающего с выхода формирователя 10.

Сигнал управления (фиг.3.1и) поступает на первый управляющий вход фазосдвигающего блока 2 и изменяет его коэффициент деления на К± 1 Ig в зависимости от знака (на фиг.3.1, 3.2 и , например, с на ), что приводит к сдвигу шкалы времени, формируемой делителем 3. Одновременно сигнал управления открывает элемент

10

импульс (фиг.3.1ж) из последователь- И 7, разрешая прохождение импульсов ности импульсов (фиг.3.1е), поступаю- с выхода мультиплексора 22 с периодом щих с выхода делителя 3 через мультиплексор 22 на его второй вход.

Импульс с выхода формирователя 10

25

повторения (KI 1) К, Т на вход вычитания реверсивного счетчика 4 (фиг.3.1к, 4к). Код грубой коррекции N, запи- санньй в счетчик 4, начинает считываться.

Как только во всех разрядах счет30

(фиг.3.1ж) поступает на первый вход элемента ИЛИ-НЕ 21, на втором входе которого присутствует логическая 1 с выхода дешифратора 9 (фиг.3.16), а на остальные входы подается код грубой коррекции с выходов старших разрядов регистра 5 сдвига. Если код грубой коррекции не равен нулю, то состояние выхода элемента ИПИ-НЕ 21 не изменяется (логический О).

Импульс с выхода формирователя 10 через элемент И 13, открытый сигналом 35 через элемент И 7.

логической 1 с выхода RST-триггера Таким образом, в течение времени 12 (фиг.3.1л, 4л), проходит на вход считывания информации, записанной синхронизации D-триггера 14 (фиг.3.1м, в реверсивный счетчик 4, импульсами 4м).с периодом повторения (К±1) К,

чика 4 появляется логический. О на его выходе появляется логический О

(фиг.3.1з), который возвращает формирователь 11 в исходное со стояние. Логический О с выхода формирователя 11 (фиг.3.1 и) восстанавливает исходный коэффициент деления блока 2 и запрещает прохождение импульсов

При этом знак коррекции с выхода младшего разряда регистра 5 сдвига записывается в D-триггер 14, с выхода которого подается на второй управляющий вход фазосдвигающего блока 2. По срезу импульса с выхода формирователя 10 переворачивается R-S-T- триггер 12. Логический О с его выхода (фиг,3.1л) запрещает прохождение сигналов через элемент И 13 (фиг.3.1м, 5.2м).

Импульс с выхода формирователя 10 поступает также на вход предварительной записи реверсивного счетчика 4 и на второй вход формирователя 11. По фронту этого импульса код грубой коррекции с выходов (М-1)/2 старших разрядов регистра 5 сдвига переписывается в реверсивный счетчик 4. При записи в реверсивный счетчик 4 числа.

отличного от нуля, на его вьгхог.е появляется логическая 1 (фиг.3.1з, 4з), которая подается на первый вход формирователя 11, разрешая его работу. Сигнал управления в виде логической 1 (фиг.3.1и, Ди) появляется на выходе формирователя 11 по срезу импульса, поступающего с выхода формирователя 10.

Сигнал управления (фиг.3.1и) поступает на первый управляющий вход фазосдвигающего блока 2 и изменяет его коэффициент деления на К± 1 в зависимости от знака (на фиг.3.1, 3.2 и , например, с на ), что приводит к сдвигу шкалы времени, формируемой делителем 3. Одновременно сигнал управления открывает элемент

И 7, разрешая прохождение импульсов с выхода мультиплексора 22 с периодом

повторения (KI 1) К, Т на вход вычитания реверсивного счетчика 4 (фиг.3.1к, 4к). Код грубой коррекции N, запи- санньй в счетчик 4, начинает считываться.

Как только во всех разрядах счет

через элемент И 7.

чика 4 появляется логический. О на его выходе появляется логический О

(фиг.3.1з), который возвращает формирователь 11 в исходное со стояние. Логический О с выхода формирователя 11 (фиг.3.1 и) восстанавливает исходный коэффициент деления блока 2 и запрещает прохождение импульсов

где NJ

К.

коэффициент деления фазосдвигающего блока 2 отличается на ± 1 от исходного, что приводит к сдвигу шкалы времени на величину &t, iK,K,T,

- величина грубой коррекции; - коэффициент деления делителя 3 от входа до выхода, соединенного с вторьм входом мультиплексора 22; период повторения импульсов генератора 1.

Перепад напряжения на выходе реверсивного счетчика 4 из логической 1 в логический О (фиг.3.1з) пере- ворачивает RST-триггер 15, на выходе которого появляется логическая 1 (фиг.3.1н). Этот сигнал запускат формирователь 16 одиночного имульса. Импульс с выхода формирова

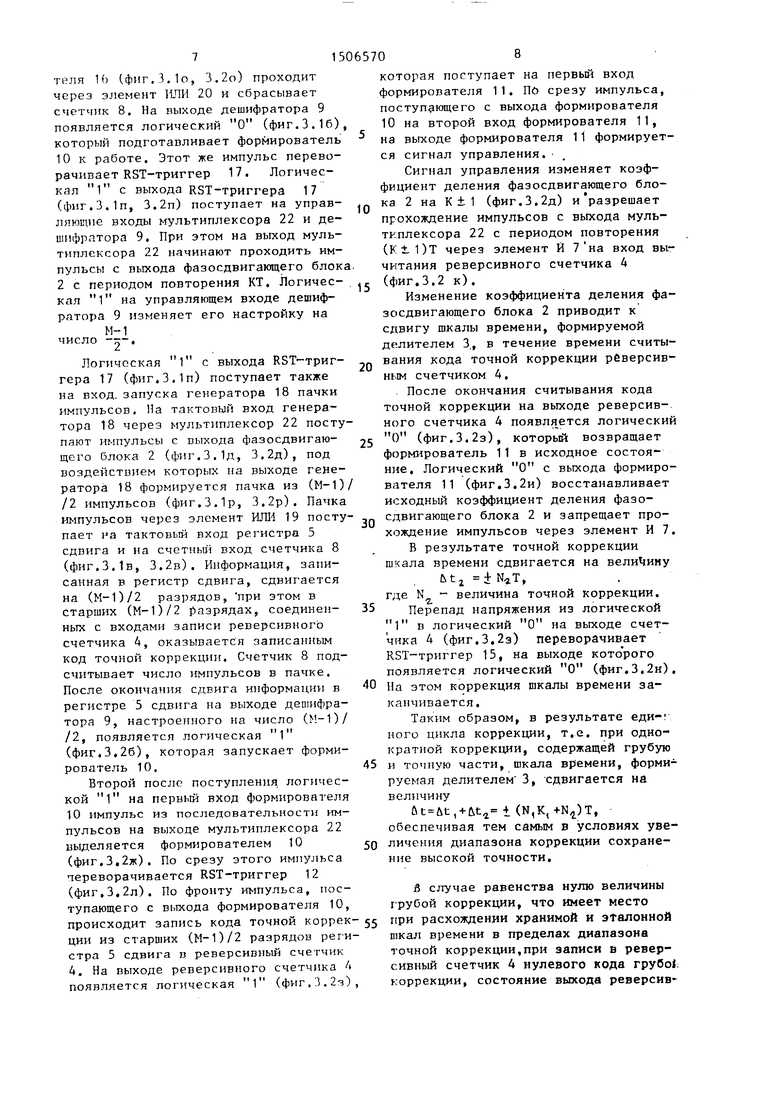

Т теля 1Ь (фиг.3.1о, 3.2о) проходит через элемент ПНИ 20 и сбрасывает счетчик 8. На выходе дешифратора 9 появляется логический О (фиг.3.1 б), который подготавливает формирователь 10 к работе. Этот же импульс переворачивает RST-триггер 17. Логическая 1 с выхода RST-триггера 17 (фиг.3.1п, 3.2п) поступает на управляющие входы мультиплексора 22 и дешифратора 9, При этом на выход мультиплексора 22 начинают проходить импульсы с выхода фазосдвигаклцего блока 2 с периодом повторения КТ. Логическая 1 на управляющем входе дешифратора 9 изменяет его настройку на

М-1 число

Логическая 1 с выхода RST-триггера 17 (фиг.3.1п) поступает также на вход, запуска генератора 18 пачки импульсов. На тактовый вход генератора 18 через мультиплексор 22 поступают импульсы с выхода фазосдвигаю- щего блока 2 (фиг.3,1д, 3,2д), под воздействием которых на выходе генератора 18 формируется пачка из (М-1)/ /2 импульсов (фиг.3.1р, 3.2р). Пачка импульсов через элемент ИЛИ 19 поступает на тактовый вход регистра 5 сдвига и на счетньи вход счетчика 8 (фиг.3.1в, 3.2в). Информация, записанная в регистр сдвига, сдвигается на (М-1)/2 разрядов, при этом в старших (М-1)/2 разрядах, соединенных с входами записи реверсивного счетчика 4, оказывается записанным код точной коррекции. Счетчик 8 подсчитывает число импульсов в пачке. После окончания сдвига информации в регистре 5 сдвига на выходе дешифратора 9, настроенного на число (-1)/ /2, появляется логическая 1 (фиг.3,26), которая запускает формирователь 10.

Второй после поступления, логической 1 на первый вход формирователя 10 импульс из последовательности импульсов на выходе мультиплексора 22 выделяется формирователем 10 (фиг,3,2ж). По срезу этого импульса переворачивается RST-триггер 12 (фиг,3.2л). По фронту импульса, поступающего с выхода формирователя 10, происходит запись кода точной коррекции из старших (М-1)/2 разрядов регистра 5 сдвига в реверсивный счетчик 4. На выходе реверсивного счетчика А появляется логическая 1 (фиг,3,2з)

0

5

0

5

0

5

0

5

0

5

которая поступает на первый вход формирователя 11, По срезу импульса, поступающего с выхода формирователя 10 на второй вход формирователя 11, на выходе формирователя 11 формируется сигнал управления.

Сигнал управления изменяет коэффициент деления фазосдвигающего блока 2 на К ± 1 (фиг,3,2д) и разрешает прохождение импульсов с выхода мультиплексора 22 с периодом повторения (К11)Т через элемент И 7 на вход вычитания реверсивного счетчика 4 (фиг.3.2 к).

Изменение коэффициента деления фазосдвигающего блока 2 приводит к сдвигу шкалы времени, формируемой д(лителем 3., в течение времени считывания кода точной коррекции реверсивным счетчиком 4,

После окончания считывания кода точной коррекции на выходе реверсивного счетчика 4 появляется логический О (фиг.3.2з), который возвращает формирователь 11 в исходное состояние. Логический О с выхода формирователя 11 (фиг.3,2и) восстанавливает исходный коэффициент деления фазосдвигающего блока 2 и запрещает прохождение импульсов через элемент И 7.

В результате точной коррекции шкала времени сдвигается на вели11ину

Citj i , где N - величина точной коррекции,

Перепад напряжения из логич еской 1 в логический О на выходе счетчика 4 (фиг,3.2з) переворачивает RST-триггер 15, на выходе кото рого появляется логический О (фиг.3,2н). На этом коррекция шкапы времени заканчивается.

Таким образом, в результате еди-; ного цикла коррекции, т,с, при однократной коррекции, содержащей грубую и точную части, шкала времени, формируемая делителем 3, сдвигается на величину

6t ut,+ut 1 (N,K,-(-N)T, обеспечивая тем самым в условиях увеличения диапазона коррекции сохранение высокой точности,

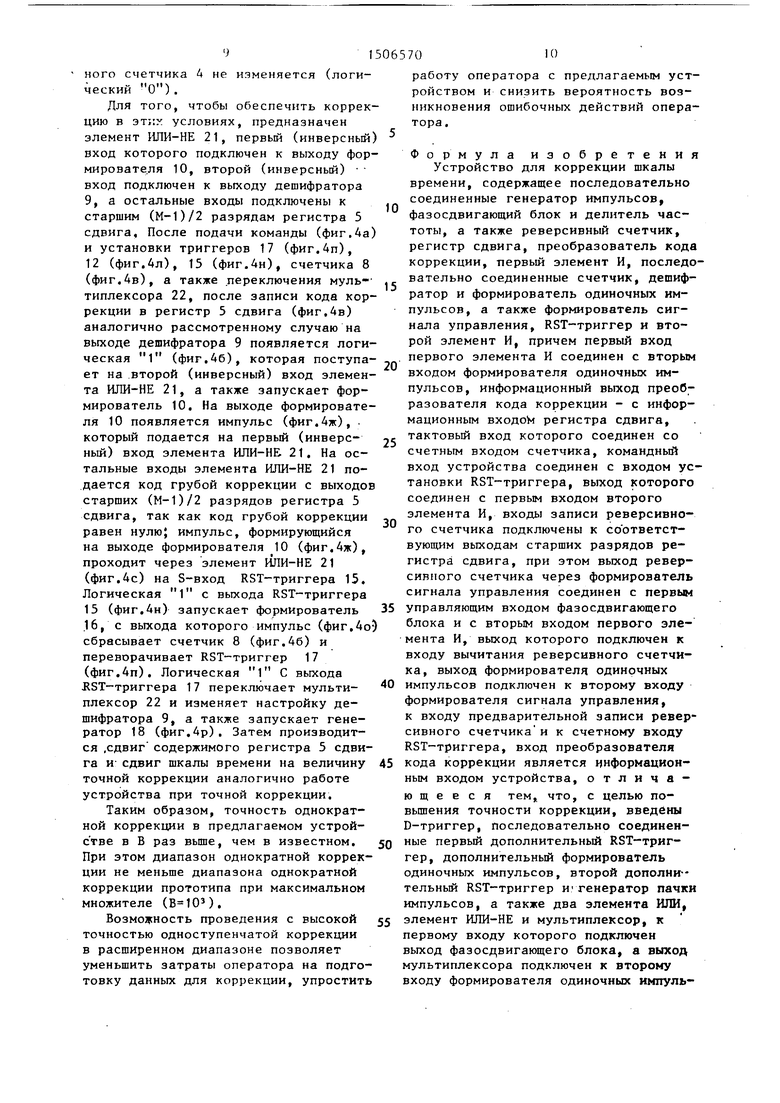

и случае равенства нулю величины грубой коррекции, что имеет место при расхождении хранимой и эталонной шкал времени в пределах диапазона точной коррекции,при записи & реверсивный счетчик 4 нулевого кода груС5о1; коррекции, состояние выхода реверсивного счетчика А не изменяется (логический о).

Для того, чтобы обеспечить коррекцию в эт;:х условиях, предназначен элемент ИЛИ-НЕ 21, первый (инверсный) вход которого подключен к выходу формирователя 10, второй (инверсный) вход подключен к выходу дешифратора 9, а остальные входы подключены к старшим (М-1)/2 разрядам регистра 5 сдвига. После подачи команды (фиг.Аа) и установки триггеров 17 (фиг.4п), 12 (фиг.4л), 15 (фиг.АН), счетчика 8 (фиг.Ав), а также переключения муль- типлексора 22, после записи кода коррекции в регистр 5 сдвига (фиг.Ав) аналогично рассмотренному случаю на выходе дешифратора 9 появляется логи

ческая 1 (фиг.Аб), которая поступает на второй (инверсный) вход элемента ИЛИ-НЕ 21, а также запускает формирователь 10. На выходе формирователя 10 появляется импульс (фиг.Аж), который подается на первый (инверсный) вход элемента ИПИ-НЕ 21. На остальные входы элемента ИЛИ-НЕ 21 подается код грубой коррекции с выходо старших (М-1)/2 разрядов регистра 5 сдвига, так как код грубой коррекции равен нулю; импульс, формирующийся на выходе формирователя 10 (фиг.Аж), проходит через элемент ИЛИ-НЕ 21 (фиг.4с) на S-вход RST-триггера 15. Логическая 1 с выхода RST-триггера 15 (фиг.4н) запускает формирователь .16, с выхода которого импульс (фиг.4о сбрасывает счетчик 8 (фиг.4б) и переворачивает RST-триггер 17 (фиг.4п). Логическая 1 С выхода Л5Т-триггера 17 переключает мультиплексор 22 и изменяет настройку дешифратора 9, а также запускает генератор 18 (фиг.4р). Затем производится .сдвиг содержимого регистра 5 сдвига и сдвиг шкалы времени на величину точной коррекции аналогично работе устройства при точной коррекции.

Таким образом, точность однократной коррекции в предлагаемом устрой- с тве в В раз вьш1е, чем в известном. При этом диапазон однократной коррекции не меньше диапазона однократной коррекции прототипа при максимальном множителе ().

Возмодсность проведения с высокой точностью одноступенчатой коррекции в расширенном диапазоне позволяет уменьшить затраты оператора на подготовку данных для коррекции, упростить

10

15

0

5

0

5

0

0

5

5

работу оператора с предлагаемым устройством и снизить вероятность возникновения ошибочных действий оператора .

Формула изобретения Устройство для коррекции шкалы

времени, содержащее последовательно соединенные генератор импульсов, фазосдвигающий блок и делитель частоты, а также реверсивный счетчик, регистр сдвига, преобразователь кода коррекции, первый элемент И, последовательно соединенные счетчик, дешифратор и формирователь одиночных импульсов, а также формирователь сигнала управления, RST-триггер и второй элемент И, причем первый вход первого элемента И соединен с вторым входом формирователя одиночных импульсов, информационный выход пресб разователя кода коррекции - с информационным входов регистра сдвига, тактовый вход которого соединен со счетным входом счетчика, командный вход устройства соединен с входом установки RST-триггера, выход которого соединен с первым входом второго элемента И, входы записи реверсивного счетчика подключены к соответствующим выходам старших разрядов регистра сдвига, при этом выход реверсивного счетчика через формирователь сигнала управления соединен с первым управляющим входом фазосдвигающего блока и с вторым входом первого элемента И, выход которого подключен к входу вычитания реверсивного счетчика, выход формирователя одиночных импульсов подключен к второму входу формирователя сигнала управления, к входу предварительной записи реверсивного счетчика и к счетному входу RST-триггера, вход преобразователя кода коррекции является информационным входом устройства, отличающееся тем, что, с целью по- вьштения точности коррекции, введены D-триггер, Последовательно соединенные первый дополнительный RST-триггер, дополнительный формирователь

одиночных импульсов, второй ДОПОЛНИ-тельный RST-триггер и генератор пачки импульсов, а также два элемента ИЛИ, элемент ИЛИ-НЕ и мультиплексор, к первому входу которого подключен выход фазосдвигающего блока, а выход мультиплексора подключен к второму входу формирователя одиночных импульсов, тактовый вход регистра сдвига подключен к тактовому выходу преобразователя кода коррекции через первый элемент ИЛИ, установочный вход счетчика подключен к командному входу устройства через второй элемент ИЛИ, выход младшего разряда регистра сдвига соединен с информационным входом D-триггера, к входу синхронизации которого подключен выход второго элемента И, а выход D-триггера соединен с вторым управляющим входом фазосдвигающего блока, второй вход второго элемента И подключен к выходу формирователя одиночных импульсов, входы установки в О первого и второго дополнительных RST-триггеров соединены с командным входом устройства, вход установки в Ч первого дополнительного RST-триггера подключен к выходу элемента ИЛИ-НЕ, первый

вход которого подключен к выходу формирователя одиночный импульсов, второй вход соединен с выходом дешифратора, а остальные входы подключены к входам записи реверсивного счетчика, второй вход BToporq элемента ИЛИ подключен к выходу дополнительного формирователя одиночных импульсов, выход второго дополнительного RST- триггера соединен с управляющими входами дешифратора и мультиплексора, второй информационный вход которого соединен с выходом делителя частоты, тактовый вход генератора пачки импульсов подключен к выходу мультиплексора, а выход генератора пачки импульсов соединен с вторым входом первого элемента ИЛИ, счетный вход первого дополнительного RST-триггера подключен к выходу реверсивного счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство коррекции шкалы времени | 1988 |

|

SU1525932A1 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1277413A2 |

| Устройство для коррекции шкалы времени | 1982 |

|

SU1095431A1 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1247828A2 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Устройство для коррекции шкалы времени | 1986 |

|

SU1365039A2 |

| Устройство для коррекции шкалы времени | 1986 |

|

SU1370643A2 |

| Устройство для коррекции шкалы времени | 1986 |

|

SU1413590A2 |

| Устройство коррекции шкалы времени | 1990 |

|

SU1774307A1 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1307598A1 |

Изобретение относится к радиотехнике и приборостроению. Цель изобретения - повышение точности коррекции. Для достижения цели в устройство введены Д-триггер, два дополнительных RST-триггера 15, 17, формирователь 16 одиночных импульсов, генератор 18 пачки импульсов, два элемента ИЛИ 19, 20, элемент ИЛИ-НЕ 21 и мультиплексор 22. В результате единого цикла коррекции, т.е. при однократной коррекции, состоящей из грубой и точной частей, шкала времени, формируемая делителем 3, сдвигается на величину ΔТ=±(N1K1 + N2T), ГДЕ N1 И N2 - ВЕЛИЧИНЫ ГРУБОЙ И ТОЧНОЙ КОРРЕКЦИИ СООТВЕТСТВЕННО, K1 - КОЭФ.ДЕЛЕНИЯ ДЕЛИТЕЛЯ 3 ОТ ВХОДА ДО ВЫХОДА, СОЕДИНЕННОГО СО ВТОРЫМ ВХОДОМ МУЛЬТИПЛЕКСОРА 22, Т-ПЕРИОД ПОВТОРЕНИЯ ИМПУЛЬСОВ Г-РА 1, ОБЕСПЕЧИВАЯ ТЕМ САМЫМ В УСЛОВИЯХ РАСШИРЕНИЯ ДИАПАЗОНА КОРРЕКЦИИ СОХРАНЕНИЕ ВЫСОКОЙ ТОЧНОСТИ. 5 ИЛ.

цг.г

шпрж Зг;Тг|

iii

aJE

I I

wv/r п

шпшяшшиддишшдтшишццш.

ШШШ

п n п п п ГЦ

t 7

Фти

t 7

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1247828A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1277413A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1989-09-07—Публикация

1987-11-30—Подача