Изобретение относится к микроэлектронике и может быть использовано в производстве гибридных интегральных схем.

Целью изобретения является повышение качества схем за счет увеличения адгезии слоев коммутации к диэлектрической подложке с одновременным сокращением техпроцесса, что достигается путем защиты поверхности подложки технологическим слоем металла в процессе формирования межслойной изоляции из полиимида.

Способ защиты поверхности подложки тонким слоем ванадия до формирования межслойной изоляции из полиимида позволяет использовать для межоперационной очистки поверхности подложки сокращенный цикл очистки, так как поверхность подложки непосредственно не контактирует с полиимидным лаком, кроме участков межуровневых пересечений проводников. Это приводит к повышению адгезии за счет исключения возможности появления органических загрязнений непосредственно на поверхности диэлектрической подложки. Кроме того, используя селективный травитель ванадия удается сохранить нижнюю коммутацию без изменения и ограничиться сокращенным циклом очистки поверхности подложки перед напылением верхнего уровня коммутации с сохранением удовлетворительной адгезии его к поверхности подложки.

Таким образом, использование слоя ванадия в качестве временной технологической защиты поверхности подложки обеспечивает высокую адгезию верхнего уровня коммутации к поверхности подложки при одновременном упрощении всего технологического процесса, так как появляется возможность ограничиться простыми технологическими приемами очистки поверхности подложки перед напылением верхнего уровня коммутации.

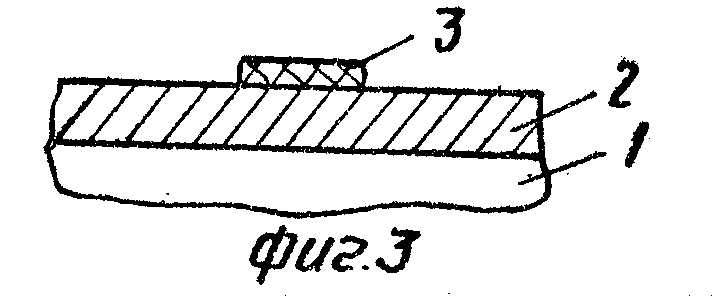

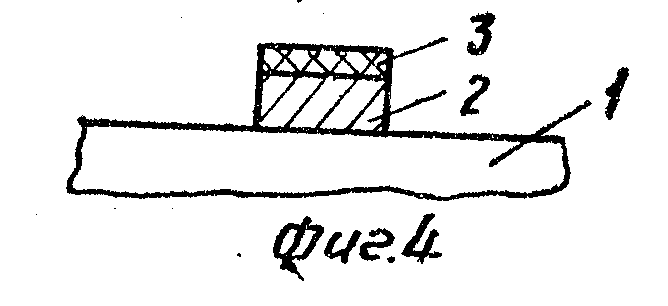

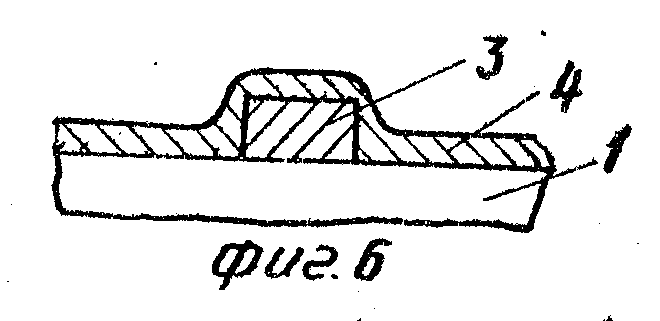

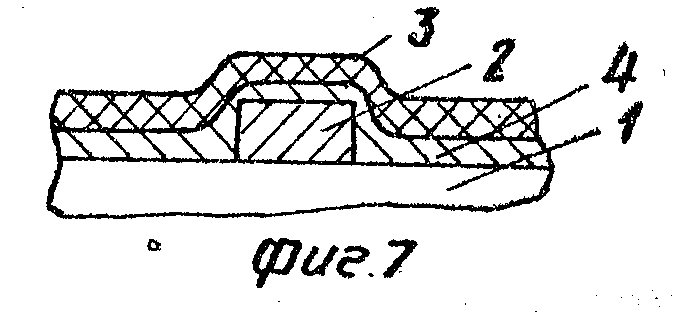

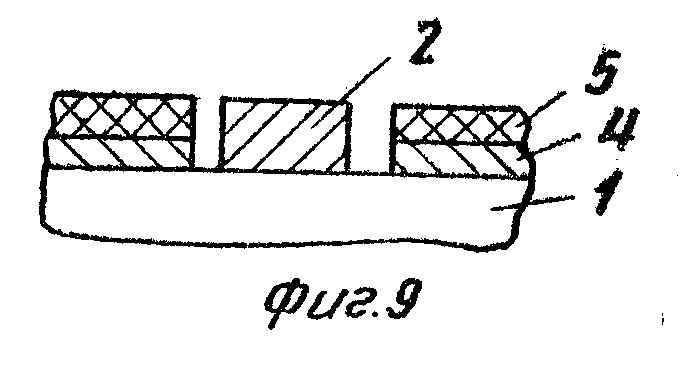

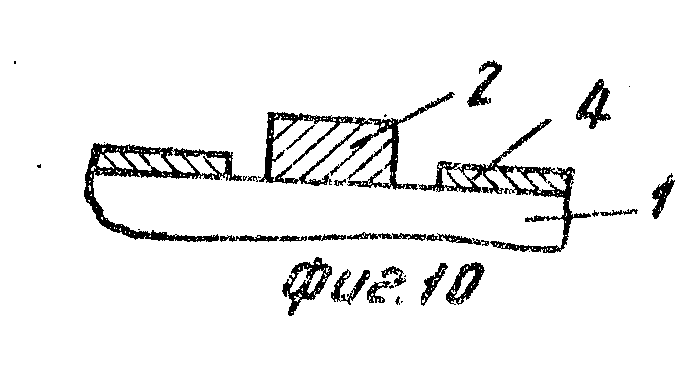

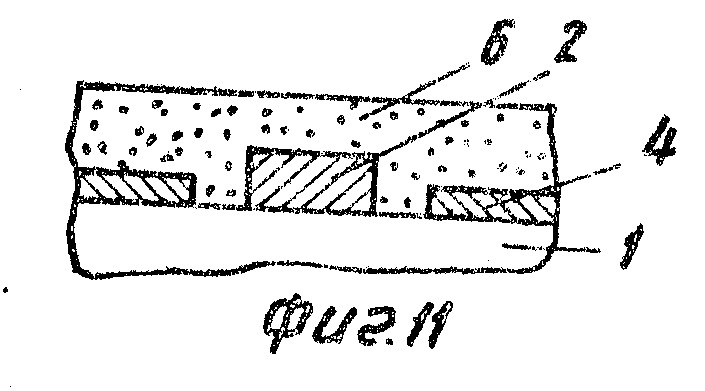

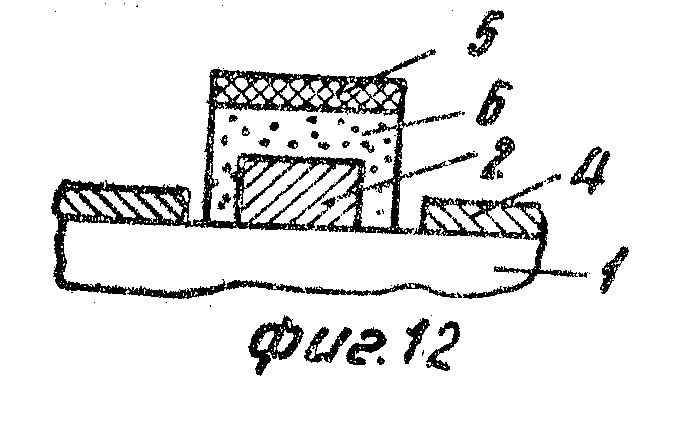

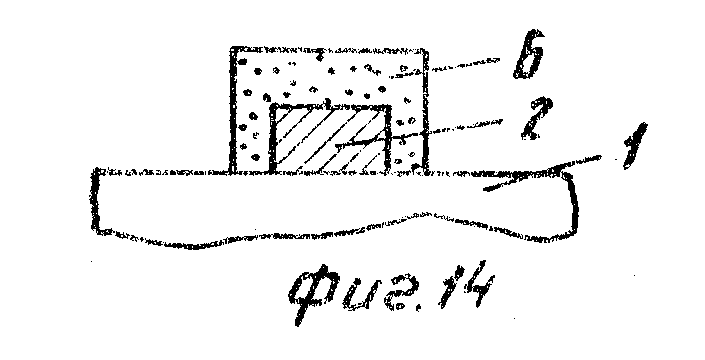

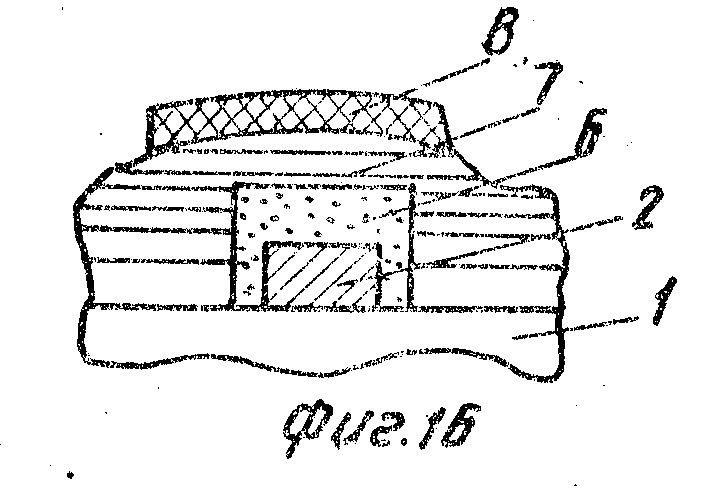

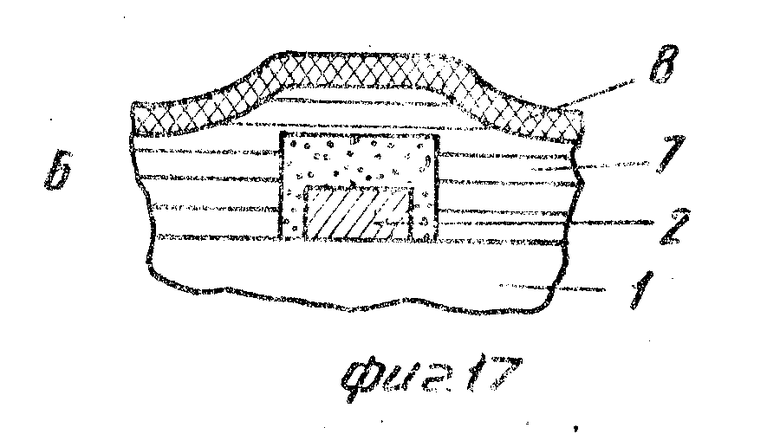

На фиг. 1-18 приведены схемы технологического процесса реализации способа, где показаны: диэлектрическая подложка 1, слой 2 хром-медь-хром нижнего уровня коммутации, маска 3 из фоторезиста, технологический слой 4 ванадия, маска 5 из фоторезиста, слой 6 полиимида, слой 7 ванадий-медь верхнего уровня коммутации, маска 8 фоторезиста.

П р и м е р. На поверхность подложки 1 из поликора или ситалла наносят сплошной слой 2 хром-медь-хром толщиной 1,5-2,0 мкм методом вакуумного напыления. Формируют маску 3 из фоторезиста с рисунком схемы проводников нижнего уровня коммутации (фиг. 1-3). Удаляют слой 2 (фиг. 4) через маску 3 селективными травителями: для хрома соляная кислота дистиллированная вода=1: 1 при температуре 55 ± 5оС; для меди хромовый ангидрид серная кислота дистиллированная вода= 9:3:20 при комнатной температуре.

Удаляют маску 3 (фиг. 5).

Очищают поверхность подложки со сформированным нижним уровнем коммутации кипячением в изопропиловом спирте в течение 10 мин. Напыляют в вакууме сплошной технологический слой 4 ванадия толщиной 0,1-0,15 мкм на поверхность подложки с проводниками нижнего уровня коммутации (фиг. 6).

Формируют окна в слое 4 ванадия на участках межслойной изоляции методом фотолитографии с помощью маски 5 (фиг. 7-8).

Травят слой ванадия 4 на участках подложки, незакрытых фоторезистом, т. е. в местах межуровневых пересечений проводников в травителе перекись водорода 30% вода дистиллированная=1:1 при комнатной температуре (фиг. 9).

Удаляют маску 5 фоторезиста с поверхности ванадия (фиг. 10).

Формируют межслойную изоляцию 6 на основе полиимидного лака АД-9103, разбавленного диметилформамидом в соотношении 2:1, при помощи фотолитографии, для чего наносят на поверхность подложки полиимидный лак центрифугированием в течение 1 мин при скорости вращения центрифугии 500-600 об/мин (фиг. 11); сушат слой 6 полиимидного лака в термошкафу ступенчато: при температуре 60оС в течение 10 мин, при температуре 80оС в течение 10 мин, при температуре 100оС в течение 10 мин, при температуре 120оС в течение 30 мин.

Наносят на поверхность полиимидного лака слой 8 фоторезиста и сушат в термошкафу, экспонируют фоторезист через фотошаблон. Проявляют рисунок в межслойной изоляции, после чего удаляют фоторезист с поверхности межслойной изоляции (фиг. 12-14).

Задубливают полиимидный лак в термошкафу при температуре 200 ± 10оС в течение 2 ч.

Удаляют слой 4 ванадия травлением в составе: перекись водорода 30% вода дистиллированная=1:1 при комнатной температуре (фиг. 15).

Очищают поверхность подложки со сформированными на ней проводниками нижнего уровня коммутации и межслойной изоляции кипячением в изопропиловом спирте в течение 15 мин.

Напыляют сплошной слой ванадий-медь на поверхность подложки вакуумным осаждением и усиливают вакуумную медь гальванической до толщины 4-5 мкм электрохимическими осаждением (фиг. 16).

Формируют рисунок верхнего уровня коммутации методом фотолитографии с помощью маски 8 (фиг. 17-18).

Травят пробельные участки слоя 7 ванадий-медь, удаляют маску 8 фоторезиста с рисунка проводников верхнего уровня коммутации.

Осаждают защитное покрытие никель-золото толщиной 2-3 мкм на проводники коммутации методом химического осаждения.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ ТОНКОПЛЕНОЧНОЙ МИКРОСХЕМЫ | 1991 |

|

RU2040131C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МИКРОПЛАТ С МНОГОУРОВНЕВОЙ ТОНКОПЛЕНОЧНОЙ КОММУТАЦИЕЙ | 2009 |

|

RU2398369C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТОНКОПЛЕНОЧНЫХ МНОГОУРОВНЕВЫХ ПЛАТ ДЛЯ МНОГОКРИСТАЛЬНЫХ МОДУЛЕЙ, ГИБРИДНЫХ ИНТЕГРАЛЬНЫХ СХЕМ И МИКРОСБОРОК | 2011 |

|

RU2459314C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МНОГОУРОВНЕВЫХ ТОНКОПЛЕНОЧНЫХ МИКРОСХЕМ | 2004 |

|

RU2264676C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МНОГОУРОВНЕВОЙ КОММУТАЦИИ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ | 1992 |

|

RU2017353C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МНОГОСЛОЙНЫХ РАДИОЭЛЕКТРОННЫХ КОМПОНЕНТОВ | 2023 |

|

RU2826900C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МНОГОСЛОЙНЫХ ПЕЧАТНЫХ ПЛАТ | 1991 |

|

RU2072123C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТОНКОПЛЕНОЧНОЙ СТРУКТУРЫ ГИБРИДНОЙ ИНТЕГРАЛЬНОЙ МИКРОСХЕМЫ СВЕРХВЫСОКОЧАСТОТНОГО ДИАПАЗОНА | 2005 |

|

RU2293400C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МАГНИТОРЕЗИСТИВНОГО ДАТЧИКА | 2011 |

|

RU2463688C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МНОГОУРОВНЕВЫХ ТОНКОПЛЕНОЧНЫХ МИКРОСХЕМ | 2011 |

|

RU2474004C1 |

Изобретение относится к микроэлектронике и может быть использовано в производстве гибридных интегральных схем. Целью изобретения является повышение качества схем за счет увелечения адгезии слоев коммутации к диэлектрической подложке с одновременным сокращением техпроцесса, что достигается путем защиты поверхности подложки технологическим слоем металла в процессе формирования межслойной изоляции из полиимида. Способ позволяет использовать для межоперационной очистки поверхности подложки сокращенный цикл очистки, так как поверхность подложки непосредственно не контактирует с полиимидным лаком, кроме участков межуровневых пересечений проводников. 18 ил.

СПОСОБ ИЗГОТОВЛЕНИЯ ТОНКОПЛЕНОЧНОЙ МИКРОСХЕМЫ, включающий последовательное вакуумное осаждение на диэлектрическую подложку слоев хрома, меди, хрома, формирование нижнего уровня коммутаций с помощью фотолитографии, формирование межслойной изоляции путем нанесения слоя полиимида, и вскрытия в нем окон для межслойных переходов, последовательное вакуумное осаждение слоев ванадия и меди с гальваническим наращиванием слоя меди и формирование верхнего уровня коммутации с помощью фотолитографии, отличающийся тем, что, с целью повышения качества микросхем за счет увеличения адгезии верхнего уровня коммутации к подложке, перед нанесением слоя полиимида наносят технологический слой ванадия и формируют в нем окна на участках межслойной изоляции, а перед вакуумным осаждением слоев ванадия и меди технологический слой ванадия удаляют селективным травлением.

| Коробка скоростей | 1929 |

|

SU33413A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1995-05-20—Публикация

1989-08-04—Подача