(54) УСТРОЙСТВО ДЛЯ 1ЖКЛОВОЙ СИНХРОНИЗАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

| Генератор сигналов сложной формы | 1985 |

|

SU1280597A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| Устройство циклового фазирования аппаратуры передачи дискретной информации | 1989 |

|

SU1626432A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2005 |

|

RU2280956C1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| Генератор случайных чисел | 1987 |

|

SU1524048A1 |

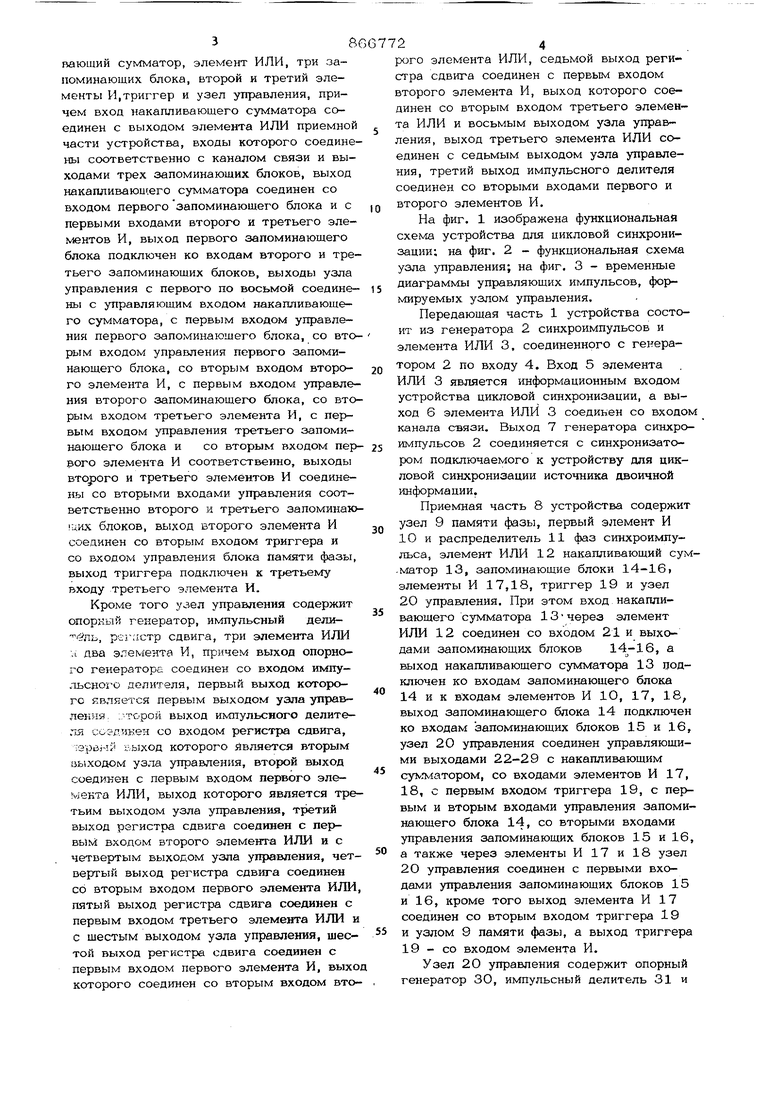

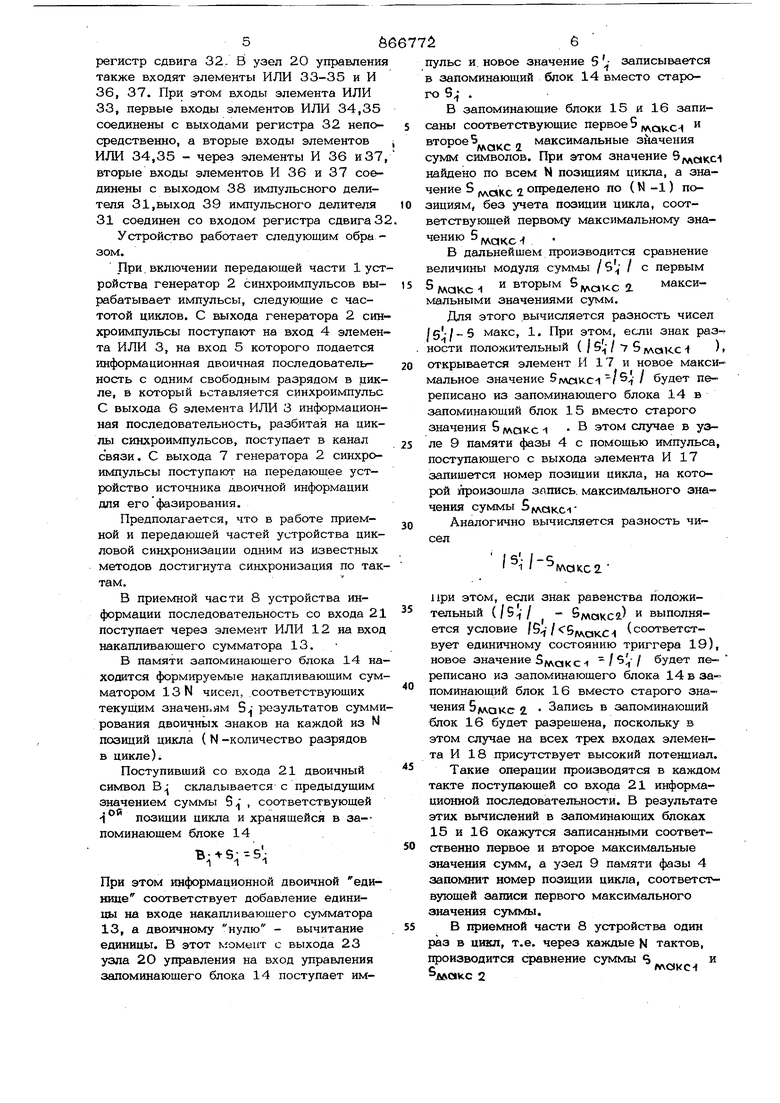

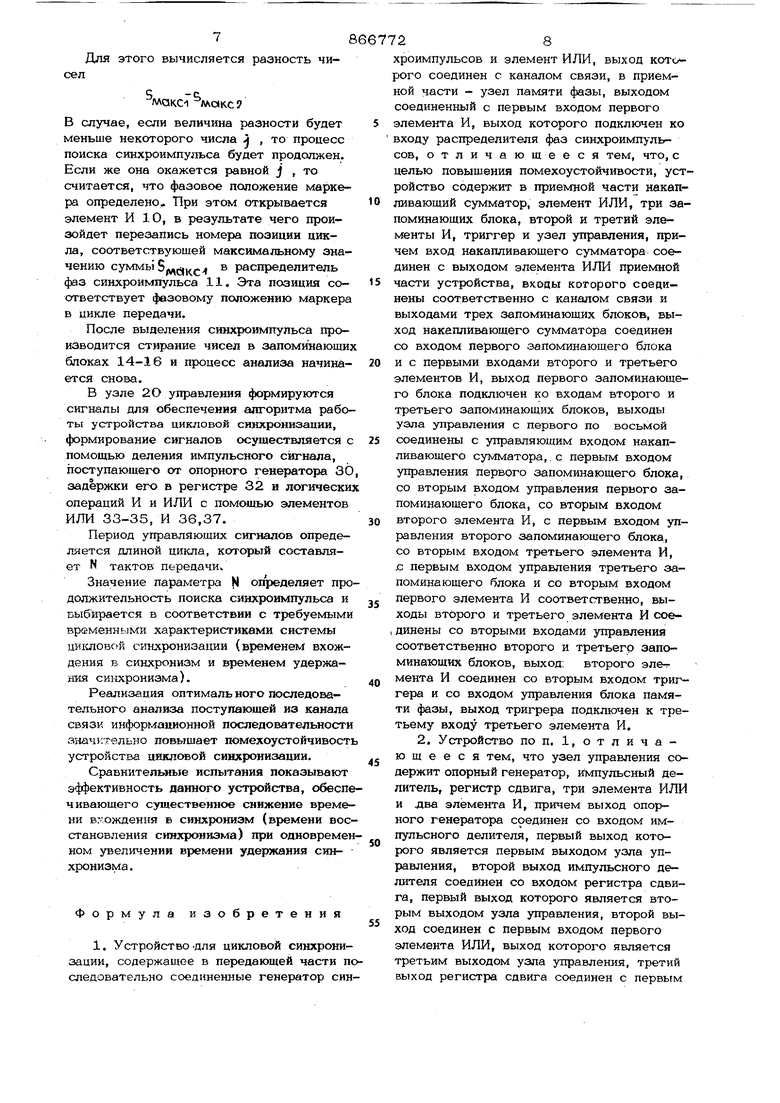

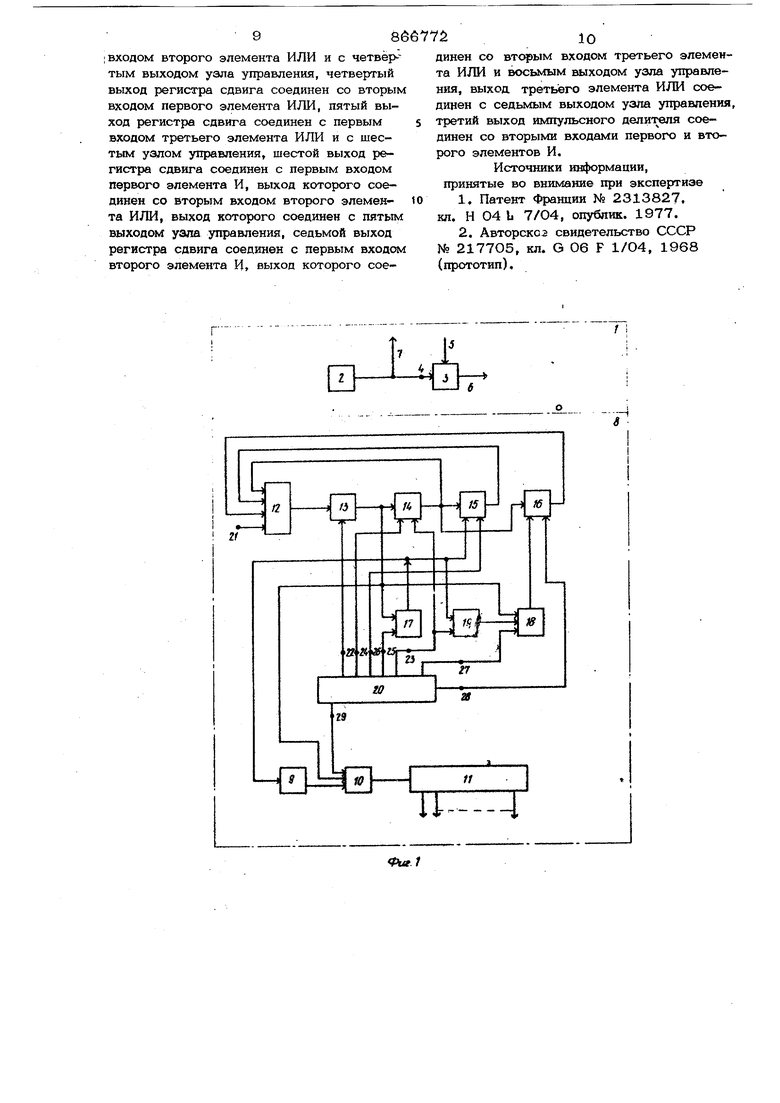

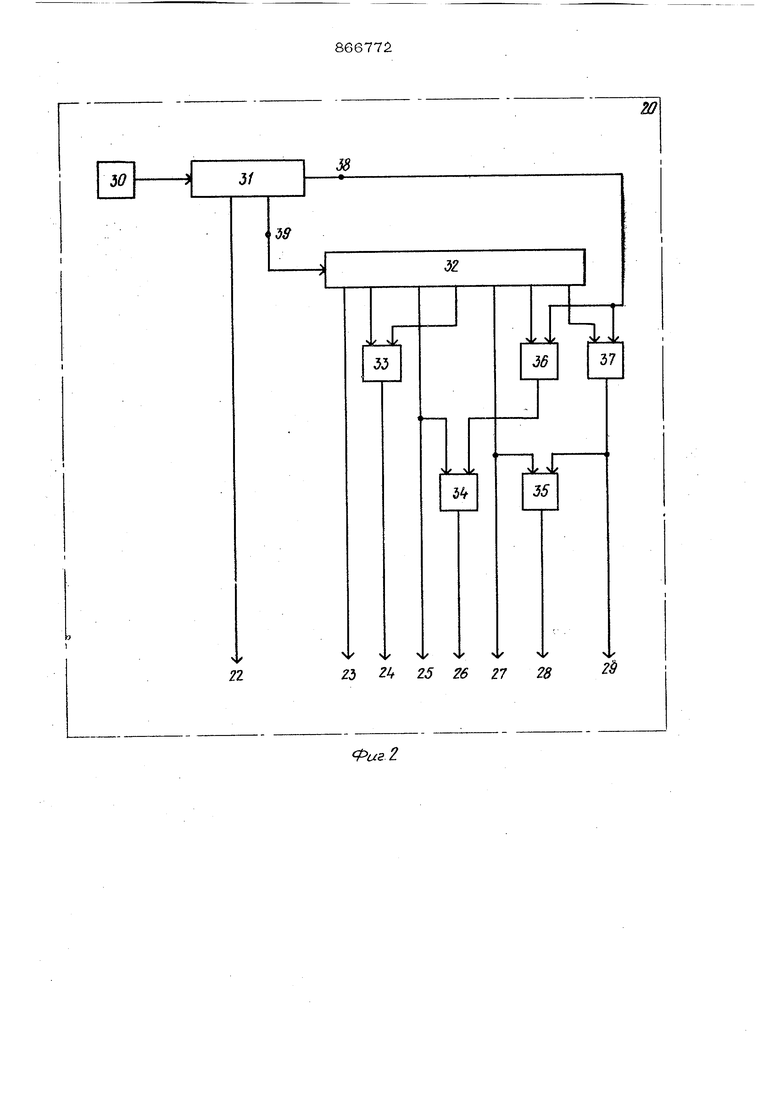

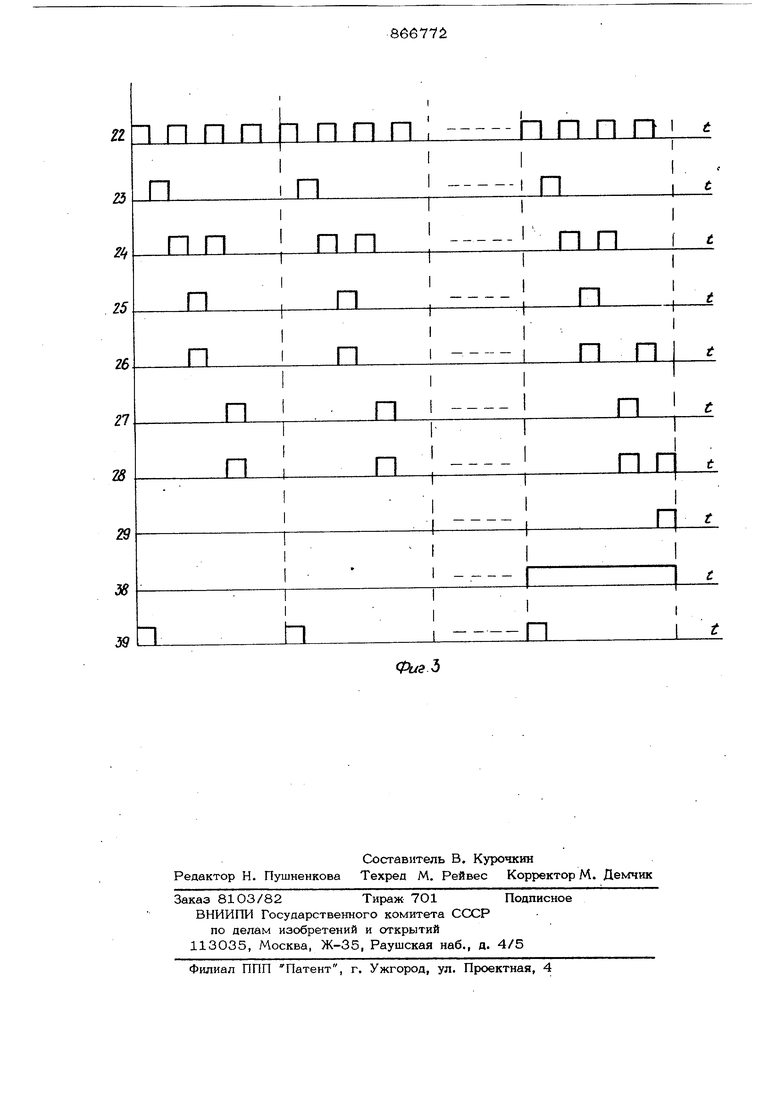

Изобретение относится к технике передачи двоичной информации по каналам связи. Известны устройства для цикловой син хронизации, используемые в системах передачи двоичной информации, содержащие на передаче узел для вставления в начале каждой группы информационных двоичных символов одного двоичного элемента (маркера), а на приемной стороне - схем селекции синхронизирующих сигналов til. Из известных наиболее близким по технической сущности к предлагаемому является устройство для цикловой синхронизации 23. Передающая часть этого устройства состоит из генератора синхроимпульсов и элемента ИЛИ, на один из входов которого подаются синхроимпульсы с выхода генератора, а на другой вход поступает информационная двоичная последовательность с одним свободным разрядом в каж дом цикле, куда вставляется синхроимпульс. Приемная часть устройства содержит соединенные последовательно блок поиска синхроимпульса и блок повышения достоверности выделения синхроимпульса и распределитель фаз синхроимпульса. При действии помех в канале связи любая ошибка при приеме маркера приводит к начальному поиску в блоке поиска синхроимпульса. Это снижает помехоустойчивость устройства цикловой синхронизации. Цель изобретения - повыщение помехоустойчивости устройства для цикловой синхронизации. Поставленная цель достигается тем, что устройство для цикловой синхронизации, содержащее в передающей части последовательно соединенные генератор синхроимпульсов и элемент ИЛИ, выход которого соединен с каналом связи, в приемной части - узел памяти фазы, выходом соединенный с первым входом первого элемента И, выход которого подключен ко входу распределителя фаз синхроимпульсов, содержит в приемной части накапливаюший сумматор, элемент ИЛИ, три запоминающих блока, второй и третий элементы И,триггер и узел управления, причем вход накапливающего сумматора соединен с выходом элемента ИЛИ приемно части устройства, входы которого соедине ны соответственно с каналом связи и выходами трех запоминающих блоков, выход накапливающего сумматора соединен со входом первого запоминающего блока и с первыми входами второго и третьего элементов И, выход первого запоминающего блока подключен ко входам второго и тре тьего запоминающих блоков, выходы узла управления с первого по восьмой соедине ны с управляющим входом накапливающего сумматора, с первым входом управления первого запоминающего блока, со вто рым входом управления первого запоминающего блока, со вторым входом второго элемента И, с первым входом управле ния второго запоминающего блока, со вто рым входом третьего элемента И, с первым входом управления третьего запоминающего блока и со вторым входом пер вого элемента И соответственно, выходы второго и третьего элементов И соединены со вторыми входами управления соответственно второго и третьего запоминаю щих блоков, выход второго элемента И соединен со вторым входом триггера и со входом управления блока памяти фазы выход триггера подключен к третьему входу третьего элемента И. Кроме того узел управления содержит опорный генератор, импульсный дели - ль. регастр сдвига, три элемента ИЛИ д два элемента И, причем выход опорного генератора соединен со входом импу- .тьсногО делителя, первый выход которого является первым выходом узла управления . ; -торой выход импульсного делителя сордикен со входом регистра сдвига, ;эрвги аыход которого является вторым выходом узла управления, второй выход соединен с первым входом первого элемента ИЛИ, выход которого является тре тьим выходом узла управления, третий выход регистра сдвига соединен с первым входом второго элемента ИЛИ и с четвертым выходом узла управления, чет вертый выход регистра сдвига соединен со вторым входом первого элемента ИЛИ пятый выход регистра сдвига соединен с первым входом третьего элемента ИЛИ и с шестым выходом узла управления, шестой выход регистра сдвига соединен с первым входом первого элемента И, выхо которого соединен со вторым входом вто рого элемента ИЛИ, седьмой выход регистра сдвига соединен с первьм входом второго элемента И, выход которого соединен со вторым входом третьего элемента ИЛИ и восьмым выходом узла управления, выход третьего элемента ИЛИ соединен с седьмым выходом узла управления, третий выход импульсного делителя соединен со вторыми входами первого и второго элементов И. На фиг. 1 изображена функциональная схема устройства для цикловой синхронизации; на фиг. 2 - функциональная схема узла управления; на фиг. 3 - временные диаграммы управляющих импульсов, формируемых узлом управления. Передающая часть 1 устройства состоит из генератора 2 синхроимпульсов и элемента ИЛИ 3. соединенного с генератором 2 по входу 4. Вход 5 элемента ИЛИ 3 является информационным входом устройства цикловой синхронизации, а выход 6 элемента ИЛИ 3 соединен со входом канала связи. Выход 7 генератора синхроимпульсов 2 соединяется с синхронизатором подключаемого к устройству для цикловой синхронизации источника двоичной информации. Приемная часть 8 устройства содержит узел 9 памяти фазы, первый элемент И 10 и распределитель 11 фаз синхроимпульса, элемент ИЛИ 12 накапливающий сум.матор 13, запоминающие блоки 14-16, элементы И 17,18, триггер 19 и узел 20 управления. При этом вход накапливающего сумматора 13 через элемент ИЛИ 12 соединен со входом 21 и выходами запоминающих блоков , а выход накапливающего сумматора 13 подключен ко входам запоминающего блока 14 и к входам элементов И 1О, 17, 18, выход запоминающего блока 14 подключен ко входам запоминающих блоков 15 и 16, узел 20 управления соединен управляющими выходами 22-29 с накапливающим сут гматором, со входами элементов И 17, 18, с первым входом триггера 19, с первым и вторым входами управления запоминающего блока 14, со вторыми входами управления запоминающих блоков 15 и 16, а также через элементы И 17 и 18 узел 2О управления соединен с первыми входами управления запоминающих блоков 15 и 16, кроме того выход элемента И 17 соединен со вторым входом триггера 19 и узлом 9 памяти фазы, а выход триггера 19 - со входом элемента И. Узел 20 управления содержит опорный генератор ЗО, импульсный делитель 31 и 56 регистр сдвига 32. В узел 20 управлени также входят элементы ИЛИ 33-35 и И 36, 37. При этом входы элемента ИЛИ 33, первые входы элементов ИЛИ 34,35 соединены с выходами регистра 32 непосредственно, а вторые входы элементов ИЛИ 34,35 - через элементы И 36 и37 вторые входы элементов И 36 и 37 соединены с выходом 38 импульсного делителя 31, выход 39 импульсного делителя 31 соединен со входом регистра сдвига 3 Устройство работает следующим образом. При. включении передающей части 1 уст ройства генератор 2 синхроимпульсов вырабатывает импульсы, следующие с частотой циклов. С выхода генератора 2 син хроимпульсы поступают на вход 4 элемен та ИЛИ 3, на вход 5 которого подается информационная двоичная последовательность с одним свободным разрядом в цик ле, в который вставляется синхроимпульс С выхода 6 элемента ИЛИ 3 информацион ная последовательность, разбитая на циклы синхроимпульсов, поступает в канал связи. С выхода 7 генератора 2 синхроимпульсы поступают на передающее устройство источника двоичной информации для его фазирования. Предполагается, что в работе приемной и передающей частей устройства цикловой синхронизации одним из известных методов достигнута синхронизация по так там, В приемной части 8 устройства информации последовательность со входа 21 поступает через элемент ИЛИ 12 на вход накапливающего сумматора 13. В памяти запоминающего блока 14 на ходится формируемые накапливающим сум матором 13 N чисел, соответствующих текущим значеньям результатов сумми рования двоичных знаков на каждой из N позиций цикла (N -количество разрядов в цикле). Поступивщий со входа 21 двоичный СИМВОЛ В складывается с предыдущим значением суммы 9 , соответствующей позиции цикла и хранящейся в за-поминающем блоке 14 B- S--5, При этом информационной двоичной единице соответствует добавление единицы на входе накапливающего сумматора 13, а двоичному нулю - вычитание единицы. В этот момент с выхода 23 узла 20 управления на вход управления запоминающего блока 14 поступает импульс и. новое значение S - записывается в запоминающий блок 14 вместо старого . В запоминающие блоки 15 и 16 записаны соответствующие первое 5 и второе 5 максимальные значения сумм символов. При этом значение S oiKC-1 найдено по всем N позициям цикла, а значение S акс 2 определено по (N -1) позициям, без учета позиции цикла, соответствующей первому максимальному значению 5 В дальнейшем производится сравнение величины модуля суммы / / с первым SMOKC-I и вторым 2- максимальными значениями сумм. Для этого вычисляется разность чисел |д. макс, 1. При этом, если знак разности полохсительный ( 15l{ / 7 6 акс 1 ) открывается элемент И 17 и новое максимальное значение .c1 / будет переписано из запоминающего блока 14 в запоминающий блок 15 вместо старого значения 6 ллакс -i этом случае в узле 9 памяти фазы 4 с помощью импульса, поступающего с выхода элемента И 17 запишется номер позиции цикла, на которой произошла ЗАПИСЬ, максимального значения суммы SNVOKCIАналогично вычисляется разность чисел/ 5- / -«; 1 (лакс2 при этом, если знак равенства положительный {/S-f/ - бдлсаксг выполняется условие /5 / 6/дакС-1 (соответствует единичному состоянию триггера 19), новое значение -t / V / будет переписано из запоминающего блока 14 в запоминающий блок 16 вместо старого значения бдлокс 2 Запись Б запоминающий блок 16 будет разрешена, поскольку в этом случае на всех трех входах элемента И 18 присутствует высокий потенциал. Такие операции производятся в каждом такте поступающей со входа 21 информационной последовательности. В результате этих вычислений в запоминающих блоках 15 и 16 окажутся записанными соответственно первое и второе максимальные значения сумм, а узел 9 памяти фазы 4 запомнит номер позиции цикла, соответствующей записи первого максимального значения суммы. В приемной части 8 устройства один раз в цикл, т.е. через каждые N тактов, производится сравнение суммы Sи сwvoKCf AftOHcC 2 78 Для этого вычисляется разность чис -с ллакс-1 ллакс В случае, если величина разности будет меньше некоторого числа , то процесс поиска синхроимпульса будет продолжен. Если же она окажется равной j , то считается, что фазовое положение маркера определено При этом открывается элемент И 10, в результате чего произойдет перезапись номера позиции цикла, соответствующей максимальному значению суммы в распределитель фаз синхроимпульса 11. Эта позиция соответствует фазовому положению маркера в цикле передачи. После выделения синхроимпульса производится стирание чисел в запоминающих блоках 14-16 и процесс анализа начинается снова. В узле 2 О управления формируются сигналы для обеспечения алгоритма работы устройства цикловой синхрюнизаиии, формирование сигналов осуществляется с помощью деления импульсного сигнала, поступающего от опорного генератора 30 задержки его в регистре 32 и логически операций И и ИЛИ с помощью элементов ИЛИ 33-35, И 36,37, Период управляющих сигналов определяется длиной цикла, который составляет N тактов передачи. Значение параметра Н определяет про должительность поиска синхроимпульса и выбирается в соответствии с требуемыми временными характеристиками системы ЦИ1СЛОВОЙ синхронизации (временем вхождения в синхронизм и временем удержания сш-{хронизма). Реализация оптималь ного последовательного анализа поступающей из канала связи информационной последовательности «значительно повышает помехоустойчивост устройства цикловой синхронизации, Сравнительные испытания показывают эффективность данного устройства, обеспе чивающего существенное снижение времени вхождения в синхронизм (времени вос становления синхронизма) при одновремен ном увеличении времени удержания синхронизма. Формула изобретения 1, Устройство-для цикловой синхронизации, содержащее в передающей части п следовательно соединенные генератор син 2 хроимпульсов и элемент ИЛИ, выход которого соединен с каналом связи, в приемной части - узел памяти фазы, выходом соединенный с первым входом первого элемента И, выход которого подключен ко входу распределителя фаз синхроимпульсов, отличающееся тем, что, с целью повышения помехоустойчивости, устройство содержит в приемной части накапливающий сумматор, элемент ИЛИ, три запоминающих блока, второй и третий элементы И, триггер и узел управления, причем вход накапливающего сумматора соединен с выходом элемента ИЛИ приемной части устройства, входы которого соединены соответственно с каналом связи и выходами трех запоминающих блоков, выход накапливающего сумматора соединен со входом первого запоминающего блока и с первыми входами второго и третьего элементов И, выход первого запоминающего блока подключен ко входам второго и третьего запоминающих блоков, выходы узла управления с первого по восьмой соединены с управляющим входом накапливающего сумматора,, с первым входом управления первого запоминающего блока, со вторым входом управления первого запоминающего блока, со вторым входом второго элемента И, с первым входом управления второго запоминающего блока, со вторым входом третьего элемента И, .с первым входом управления третьего запоминающего блока и со вторым входом первого элемента И соответственно, выходы второго и третьего элемента И сое.динены со вторыми входами управления соответственно второго и третьего запоминающих блоков, выход: второго эле мента И соединен со вторым входом триггера и со входом управления блока памяти фазы, выход тригрера подключен к третьему входу третьего элемента И. 2. Устройство по п. 1, отличающее с я тем, что узел управления содержит опорный генератор, импульсный делитель, регистр сдвига, три элемента ИЛИ и два элемента И, причем выход опорного генератора соединен со входом импульсного делителя, первый выход которого является первым выходом узла управления, второй выход импульсного делителя соединен со входом регистра сдвига, первый выход которого является вторым выходом узла управления, второй выход соединен с первым входом первого элемента ИЛИ, выход которого является третьим выходом узла управления, третий выход регистра сдвига соединен с первым 986 i входом второго элемента ИЛИ и с четверо тым выходом узла управления, четвертый выход регистра сдвига соединен со вторым входом первого элемента ИЛИ, пятый выход регистра сдвига соединен с первым входом третьего элемента ИЛИ и с шестым узлом управления, шестой выход регистра сдвига соединен с первым входом первого элемента И, выход которого соединен со вторым входом второго элемента ИЛИ, выход которого соединен с пятым выходом узла управления, седьмой выход регистра сдвига соединен с первым входом второго элемента И, выход которого соеLAдинен со вторым входом третьего элемента ИЛИ и восьмым выходом узла управления, выход третьего элемента ИЛИ соединен с седьмым выходом узла управления, третий выход импульсного делителя соединен со вторыми входами первого и второго элементов И. Источники информации, принятые во внимание при экспертизе 1.Патент Франции № 2313827. кл. Н 04 Ь 7/04, опубпик. 1977. 2.Авторскоз свидетельство СССР № 2177О5, кл. G 06 F 1/04, 1968 (прототип).

-{

//

гь 24 25 26 27 28

21

2ё

Pus2

Физ 5

Авторы

Даты

1981-09-23—Публикация

1979-10-24—Подача