Изобретение относится к электросвязи и может быть использовано для циклового фазирования систем передачи дискретной информации.

Целью изобретения является повышение быстродействия.

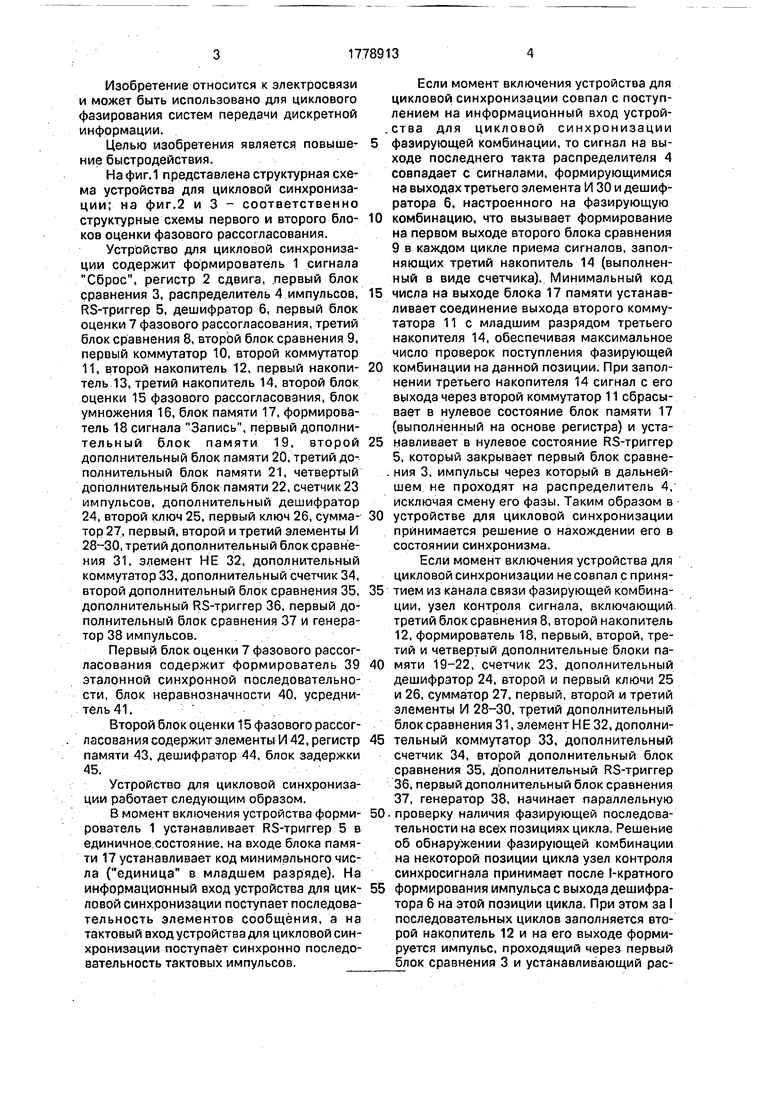

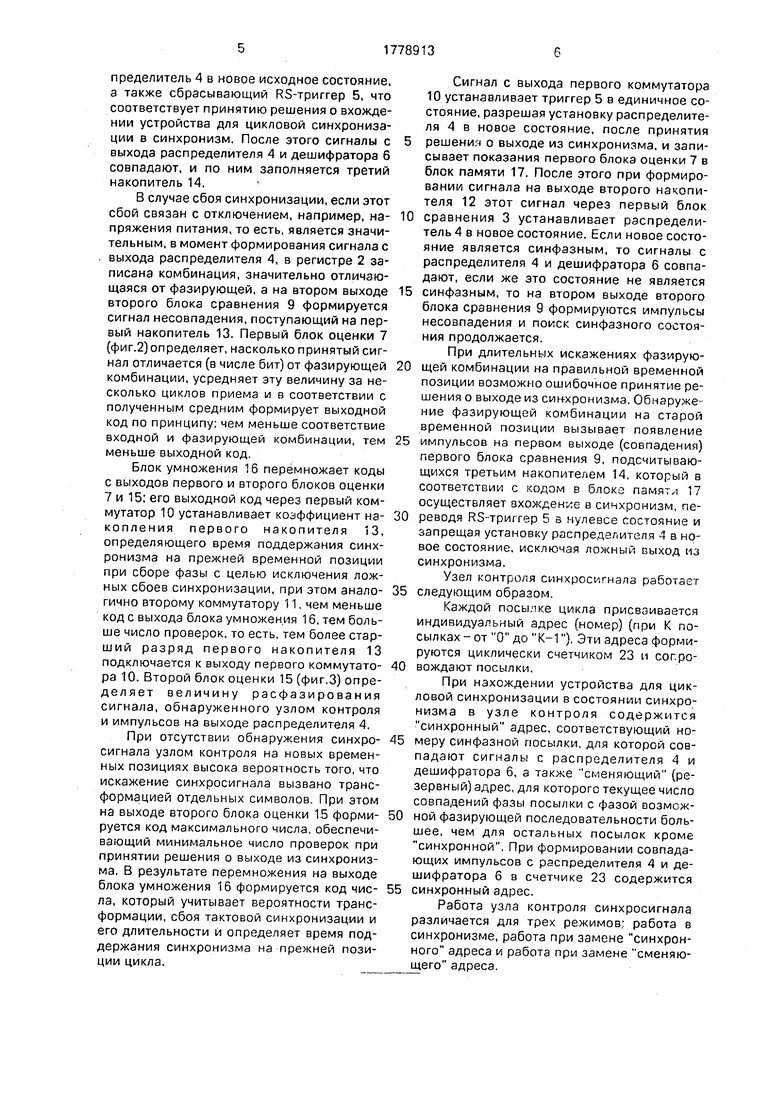

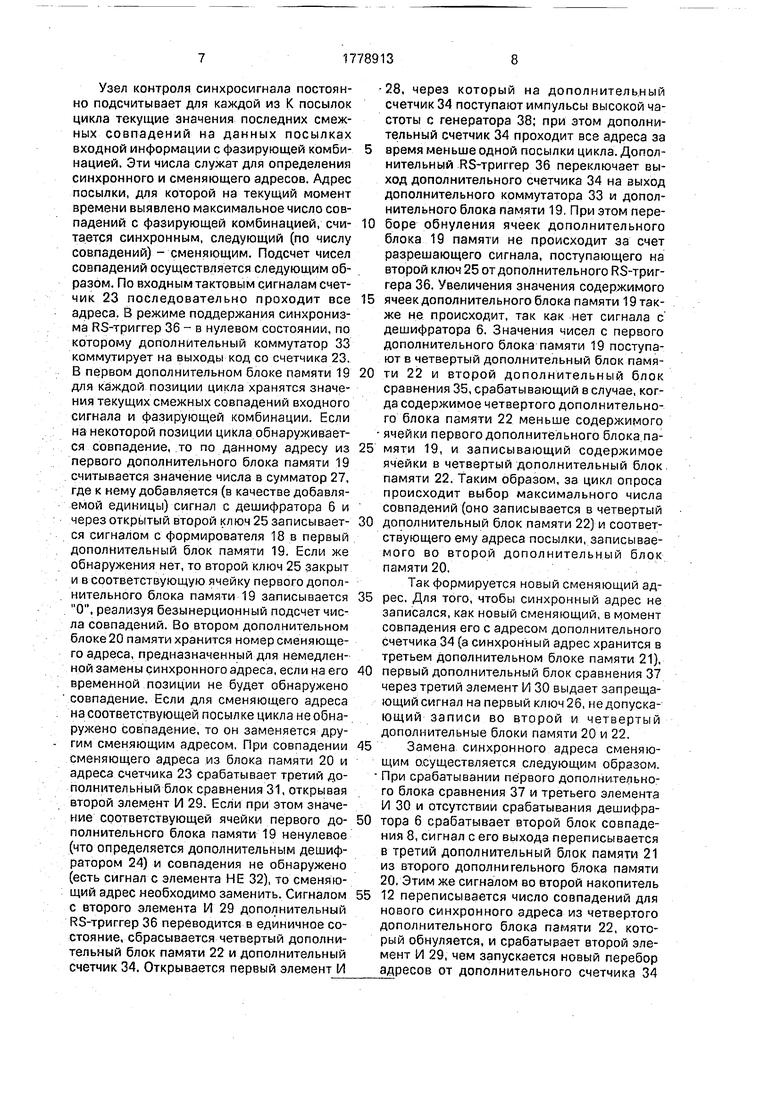

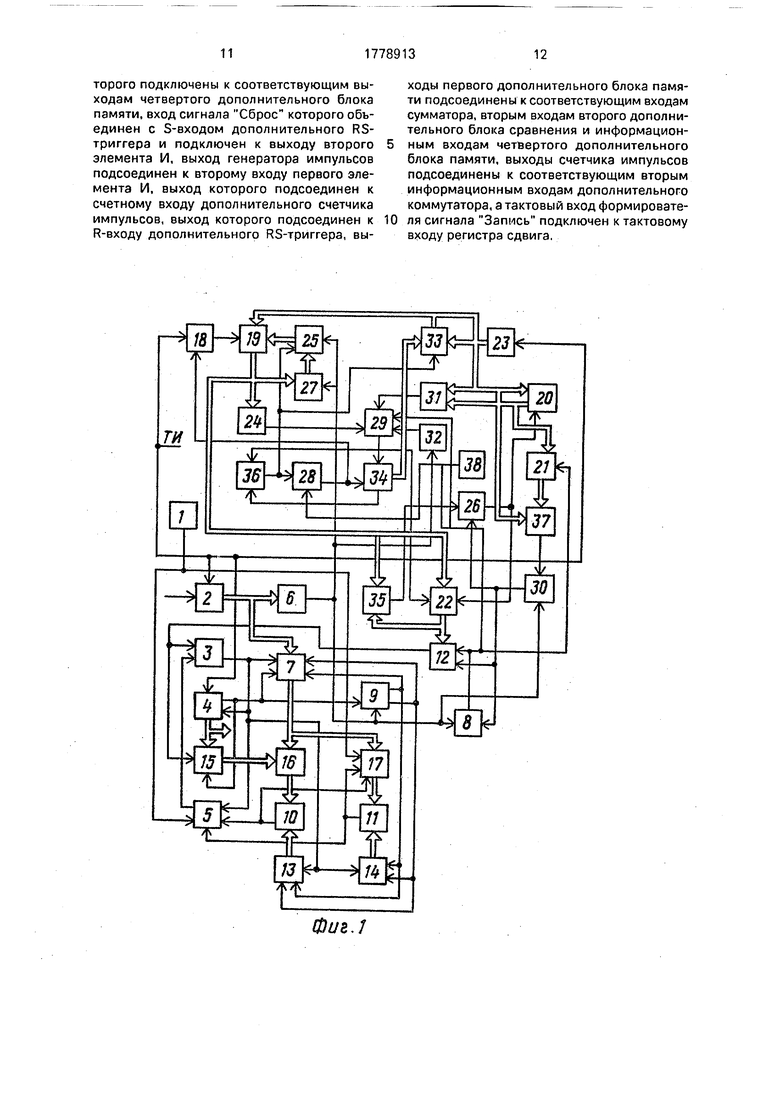

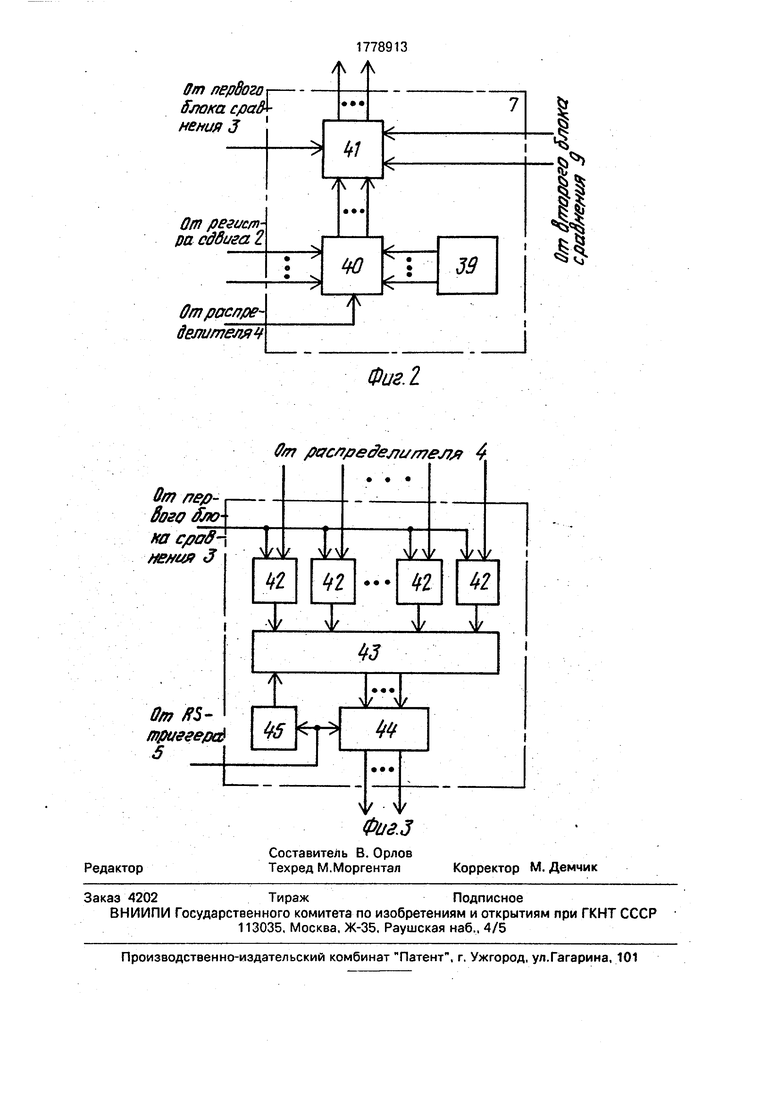

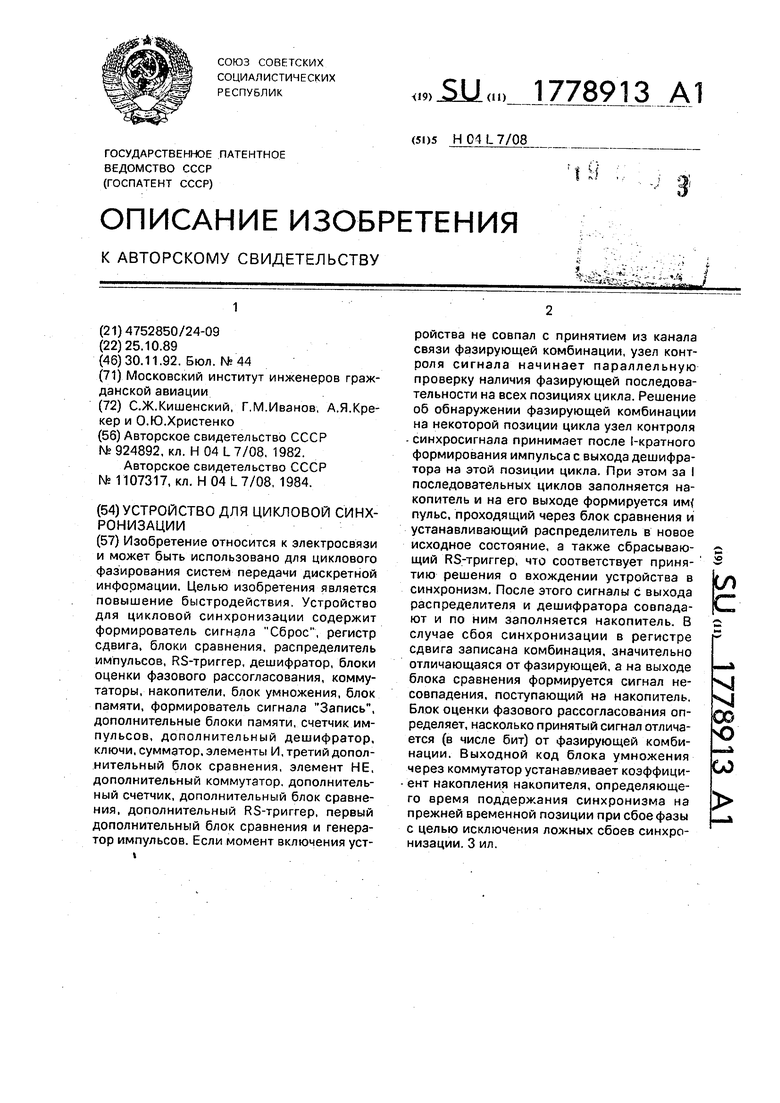

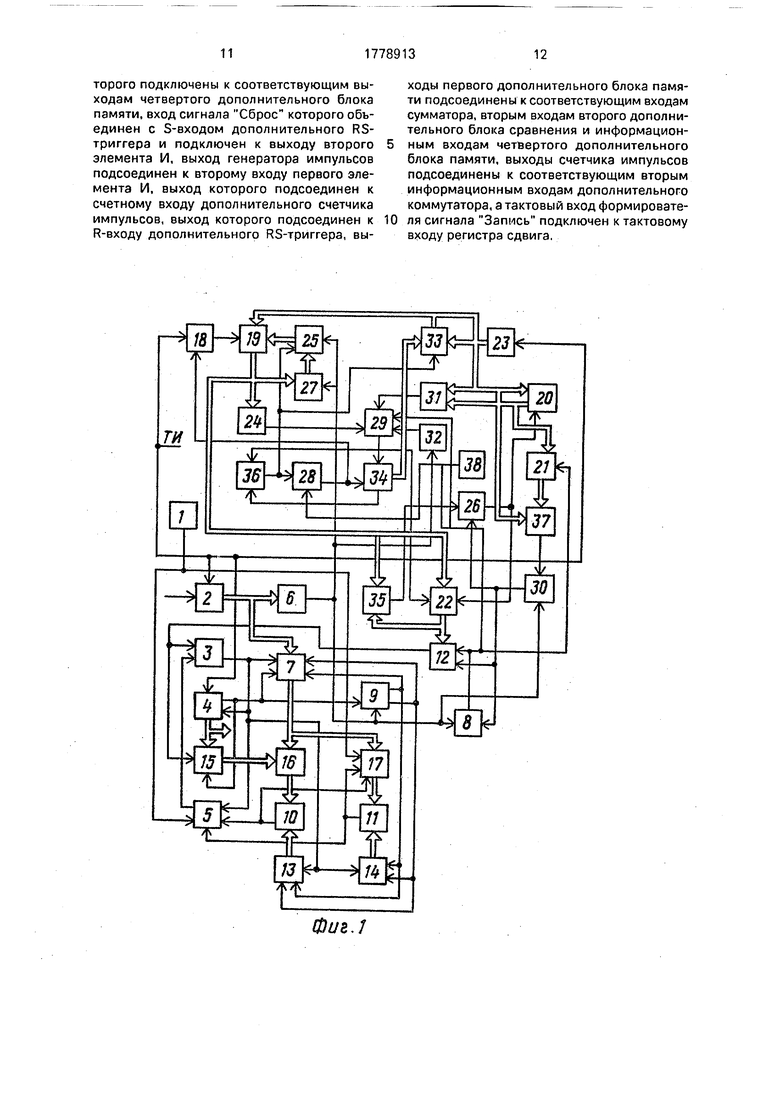

Нафиг.1 представлена структурная схема устройства для цикловой синхронизации; на фиг.2 и 3 - соответственно структурные схемы первого и второго блоков оценки фазового рассогласования.

Устройство для цикловой синхронизации содержит формирователь 1 сигнала Сброс, регистр 2 сдвига, первый блок сравнения 3, распределитель 4 импульсов, RS-триггер 5, дешифратор 6, первый блок оценки 7 фазового рассогласования, третий блок сравнения 8, второй блок сравнения 9, первый коммутатор 10, второй коммутатор 11, второй накопитель 12, первый накопитель 13, третий накопитель 14, второй блок оценки 15 фазового рассогласования, блок умножения 16, блок памяти 17, формирователь 18 сигнала Запись, первый дополни- тельный блок памяти 19, второй дополнительный блок памяти 20, третий дополнительный блок памяти 21, четвертый дополнительный блок памяти 22, счетчик 23 импульсов, дополнительный дешифратор 24, второй ключ 25, первый ключ 26, сумматор 27, первый, второй и третий элементы И 28-30, третий дополнительный блок сравнения 31, элемент НЕ 32, дополнительный коммутатор 33, дополнительный счетчик 34, второй дополнительный блок сравнения 35, дополнительный RS-триггер 36, первый дополнительный блок сравнения 37 и генератор 38 импульсов.

Первый блок оценки 7 фазового рассогласования содержит формирователь 39 эталонной синхронной последовательности, блок неравнозначности 40, усреднитель 41.

Второй блок оценки 15 фазового рассогласования содержит элементы И 42, регистр памяти 43, дешифратор 44, блок задержки 45.

Устройство для цикловой синхронизации работает следующим образом.

В момент включения устройства формирователь 1 устанавливает RS-триггер 5 в единичное состояние, на входе блока памяти 17 устанавливает код минимального числа (единица в младшем разряде). На информационный вход устройства для цикловой синхронизации поступает последовательность элементов сообщения, а на тактовый вход устройства для цикловой синхронизации поступает синхронно последовательность тактовых импульсов.

Если момент включения устройства для цикловой синхронизации совпал с поступлением на информационный вход устрой- .ства для цикловой синхронизации

фазирующей комбинации, то сигнал на выходе последнего такта распределителя 4 совпадает с сигналами, формирующимися на выходах третьего элемента И 30 и дешифратора 6, настроенного на фазирующую

комбинацию, что вызывает формирование на первом выходе второго блока сравнения 9 в каждом цикле приема сигналов, заполняющих третий накопитель 14 (выполненный в виде счетчика). Минимальный код

числа на выходе блока 17 памяти устанавливает соединение выхода второго коммутатора 11с младшим разрядом третьего накопителя 14, обеспечивая максимальное число проверок поступления фазирующей

комбинации на данной позиции. При заполнении третьего накопителя 14 сигнал с его выхода через второй коммутатор 11 сбрасывает в нулевое состояние блок памяти 17 (выполненный на основе регистра) и устанавливает в нулевое состояние RS-триггер 5, который закрывает первый блок сравне- . ния 3, импульсы через который в дальнейшем не проходят на распределитель 4, исключая смену его фазы. Таким образом в

устройстве для цикловой синхронизации принимается решение о нахождении его в состоянии синхронизма.

Если момент включения устройства для цикловой синхронизации не совпал с принятием из канала связи фазирующей комбинации, узел контроля сигнала, включающий третий блок сравнения 8, второй накопитель 12, формирователь 18, первый, второй, третий и четвертый дополнительные блоки памяти 19-22, счетчик 23, дополнительный дешифратор 24, второй и первый ключи 25 и 26, сумматор 27, первый, второй м третий элементы И 28-30, третий дополнительный блок сравнения 31, элемент НЕ 32, дополнительный коммутатор 33, дополнительный счетчик 34, второй дополнительный блок сравнения 35, дополнительный RS-триггер

36,первый дополнительный блок сравнения

37,генератор 38, начинает параллельную . проверку наличия фазирующей последовательности на всех позициях цикла. Решение об обнаружении фазирующей комбинации на некоторой позиции цикла узел контроля синхросигнала принимает после 1-кратного

формирования импульса с выхода дешифратора 6 на этой позиции цикла. При этом за I последовательных циклов заполняется второй накопитель 12 и на его выходе формируется импульс, проходящий через первый

блок сравнения 3 и устанавливающий распределитель 4 в новое исходное состояние, а также сбрасывающий RS-триггер 5, что соответствует принятию решения о вхождении устройства для цикловой синхронизации в синхронизм. После этого сигналы с выхода распределителя 4 и дешифратора 6 совпадают, и по ним заполняется третий накопитель 14.

В случае сбоя синхронизации, если этот сбой связан с отключением, например, на- пряжения питания, то есть, является значительным, в момент формирования сигнала с выхода распределителя 4, в регистре 2 записана комбинация, значительно отличающаяся от фазирующей, а на втором выходе второго блока сравнения 9 формируется сигнал несовпадения, поступающий на первый накопитель 13. Первый блок оценки 7 (фиг.2) определяет, насколько принятый сигнал отличается (в числе бит) от фазирующей комбинации, усредняет эту величину за несколько циклов приема и в соответствии с полученным средним формирует выходной код по принципу: чем меньше соответствие входной и фазирующей комбинации, тем меньше выходной код.

Блок умножения 16 перемножает коды с выходов первого и второго блоков оценки 7 и 15; его выходной код через первый коммутатор 10 устанавливает коэффициент на- копления первого накопителя 13, определяющего время поддержания синхронизма на прежней временной позиции при сборе фазы с целью исключения ложных сбоев синхронизации, при этом знало- гично второму коммутатору 11, чем меньше код с выхода блока умножения 16, тем больше число проверок, то есть, тем более стар- ший разряд первого накопителя 13 подключается к выходу первого коммутато- ра 10. Второй блок оценки 15 (фиг.З) определяет величину расфазирования сигнала, обнаруженного узлом контроля и импульсов на выходе распределителя 4.

При отсутствии обнаружения синхро- сигнала узлом контроля на новых временных позициях высока вероятность того, что искажение синхросигнала вызвано трансформацией отдельных символов. При этом на выходе второго блока оценки 15 форми- руется код максимального числа, обеспечивающий минимальное число проверок при принятии решения о выходе из синхронизма. В результате перемножения на выходе блока умножения 16 формируется код чис- ла, который учитывает вероятности трансформации, сбоя тактовой синхронизации и его длительности и определяет время поддержания синхронизма на прежней позиции цикла.

Сигнал с выхода первого коммутатора 10 устанавливает триггер 5 в единичное состояние, разрешая установку распределителя 4 в новое состояние, после принятия решения о выходе из синхронизма, и записывает показания первого блока оценки 7 в блок памяти 17. После этого при формировании сигнала на выходе второго накопителя 12 этот сигнал через первый блок сравнения 3 устанавливает распределитель 4 в новое состояние. Если новое состояние является синфазным, то сигналы с распределителя 4 и дешифратора 6 совпадают, если же это состояние не является синфазным, то на втором выходе второго блока сравнения 9 формируются импульсы несовпадения и поиск синфазного состояния продолжается.

При длительных искажениях фазирующей комбинации на правильной временной позиции возможно ошибочное принятие решения о выходе из син-хронизмз. Обнаружение фазирующей комбинации на старой временной позиции вызывает появление импульсов на первом выходе (совпадения) первого блока сравнения 9, подсчитывающихся третьим накопителем 14, который в соответствии с кодом в блоке памяти 17 осуществляет вхождение в синхронизм, переводя RS-триггер 5 в нулевое состояние и запрещая установку распределителя 4 в новое состояние, исключая ложный выход из синхронизма.

Узел контроля синхросигнала работает следующим образом.

Каждой посылке цикла присваивается индивидуальный адрес (номер) (при К посылках - от О до К-1). Эти адреса формируются циклически счетчиком 23 и сопровождают посылки.

При нахождении устройства для цикловой синхронизации в состоянии синхронизма в узле контроля содержится синхронный адрес, соответствующий номеру синфазной посылки, для которой совпадают сигналы с распределителя 4 и дешифратора 6, а также сменяющий (резервный) адрес, для которого текущее число совпадений фазы посылки с фазой возможной фазирующей последовательности большее, чем для остальных посылок кроме синхронной. При формировании совпадающих импульсов с распределителя 4 и дешифратора 6 в счетчике 23 содержится синхронный адрес.

Работа узла контроля синхросигнала различается для трех режимов работа в синхронизме, работа при замене синхронного адреса и работа при замене сменяющего адреса.

Узел контроля синхросигнала постоянно подсчитывает для каждой из К посылок цикла текущие значения последних смежных совпадений на данных посылках входной информации с фазирующей комбинацией. Эти числа служат для определения синхронного и сменяющего адресов. Адрес посылки, для которой на текущий момент времени выявлено максимальное число совпадений с фазирующей комбинацией, считается синхронным, следующий (по числу совпадений) - сменяющим. Подсчет чисел совпадений осуществляется следующим образом. По входным тактовым сигналам счетчик 23 последовательно проходит все адреса. В режиме поддержания синхронизма RS-триггер 36 - в нулевом состоянии, по которому дополнительный коммутатор 33 коммутирует на выходы код со счетчика 23. В первом дополнительном блоке памяти 19 для каждой позиции цикла хранятся значения текущих смежных совпадений входного сигнала и фазирующей комбинации. Если на некоторой позиции цикла обнаруживается совпадение, то по данному адресу из первого дополнительного блока памяти 19 считывается значение числа в сумматор 27, где к нему добавляется (в качестве добавляемой единицы) сигнал с дешифратора 6 и через открытый второй ключ 25 записывается сигналом с формирователя 18 в первый дополнительный блок памяти 19. Если же обнаружения нет, то второй ключ 25 закрыт и в соответствующую ячейку первого дополнительного блока памяти 19 записывается О, реализуя безынерционный подсчет числа совпадений. Во втором дополнительном блоке 20 памяти хранится номер сменяющего адреса, предназначенный для немедленной замены синхронного адреса, если на его временной позиции не будет обнаружено совпадение. Если для сменяющего адреса на соответствующей посылке цикла не обнаружено совпадение, то он заменяется другим сменяющим адресом. При совпадении сменяющего адреса из блока памяти 20 и адреса счетчика 23 срабатывает третий дополнительный блок сравнения 31, открывая второй элемент И 29. Если при этом значение соответствующей ячейки первого дополнительного блока памяти 19 ненулевое (что определяется дополнительным дешифратором 24) и совпадения не обнаружено (есть сигнал с элемента НЕ 32), то сменяющий адрес необходимо заменить. Сигналом с второго элемента И 29 дополнительный RS-триггер 36 переводится в единичное состояние, сбрасывается четвертый дополнительный блок памяти 22 и дополнительный счетчик 34. Открывается первый элемент И

28, через который на дополнительный счетчик 34 поступают импульсы высокой частоты с генератора 38; при этом дополнительный счетчик 34 проходит все адреса за

время меньше одной посылки цикла. Дополнительный RS-триггер 36 переключает выход дополнительного счетчика 34 на выход дополнительного коммутатора 33 и дополнительного блока памяти 19. При этом пере0 боре обнуления ячеек дополнительного блока 19 памяти не происходит за счет разрешающего сигнала, поступающего на второй ключ 25 от дополнительного RS-триг- гера 36. Увеличения значения содержимого

5 ячеек дополнительного блока памяти 19 также не происходит, так как нет сигнала с дешифратора 6. Значения чисел с первого дополнительного блока памяти 19 поступают в четвертый дополнительный блок памя0 ти 22 и второй дополнительный блок сравнения 35, срабатывающий в случае, когда содержимое четвертого дополнительного блока памяти 22 меньше содержимого

ячейки первого дополнительного блока па- 5 мяти 19, и записывающий содержимое

ячейки в четвертый дополнительный блок памяти 22. Таким образом, за цикл опроса происходит выбор максимального числа совпадений (оно записывается в четвертый

0 дополнительный блок памяти 22) и соответствующего ему адреса посылки, записываемого во второй дополнительный блок памяти 20.

Так формируется новый сменяющий ад5 рее. Для того, чтобы синхронный адрес не записался, как новый сменяющий, в момент совпадения его с адресом дополнительного счетчика 34 (а синхронный адрес хранится в третьем дополнительном блоке памяти 21),

0 первый дополнительный блок сравнения 37 через третий элемент И 30 выдает запрещающий сигнал на первый ключ 26, не допускающий записи во второй и четвертый дополнительные блоки памяти 20 и 22.

5 Замена синхронного адреса сменяющим осуществляется следующим образом.

При срабатывании первого дополнительного блока сравнения 37 и третьего элемента И 30 и отсутствии срабатывания дешифра0 тора 6 срабатывает второй блок совпадения 8, сигнал с его выхода переписывается в третий дополнительный блок памяти 21 из второго дополнительного блока памяти 20, Этим же сигналом во второй накопитель

5 12 переписывается число совпадений для нового синхронного адреса из четвертого дополнительного блока памяти 22, который обнуляется, и срабатывает второй элемент И 29, чем запускается новый перебор адресов от дополнительного счетчика 34

для формирования нового сменяющего ад- реса.

Формула изобретения Устройство для цикловой синхронизации, содержащее последовательно соединенные регистр сдвига, первый блок оценки фазового рассогласования, первый блок умножения, первый коммутатор, RS-триггер и первый блок сравнения, выход которого подсоединен к первому входу Сброс первого блока оценки фазового рассогласования, последовательно соединенные дешифратор, второй блок сравнения и первый накопитель, выходы которого подсоединены к соответствующим информационным входам первого коммутатора, выход которого подсоединен к входу сигнала Запись, последовательно соединенные формирователь сигнала Сброс, блок памяти и второй коммутатор, выход которого подсоединен к входу Сброс блока памяти и R-входу RS- триггера, S-вход которого подключен к выходу формирователя сигнала Сброс, последовательно соединенные распределитель импульсов и второй блок оценки фазового рассогласования, выходы которого подсоединены к соответствующим вторым входам блока умножения, а также счетчик импульсов, второй и третий накопители и третий блок сравнения, вход которого подключен к выходу дешифратора, первый выход второго блока сравнения подсоединен к входу сигнала эталонной комбинации первого блока сравнения подсоединен к входу сигнала эталонной комбинации первого блока оценки фазового рассогласования, счетному входу третьего накопителя и входу сигнала Сброс третьего накопителя, второй выход второго блока сравнения подсоединен к входам сигнала Сброс первого блока оценки фазового рассогласования и третьего накопителя, выход первого блока сравнения подсоединен к устанавливающему входу распределителя импульсов, дополнительному R-входу RS-триггера и входам сигнала Сброс первого накопителя и третьего накопитепя, выходы которого подсоединены к соответствующим информационным входам второго коммутатора, выход распределителя импульсов подсоединен к разрешающему входу первого блока оценки фазового рассогласования и тактовым входам второго блока сравнения и второго блока оценки фазового рассогласования, выход второго накопителя подсоединен к второму входу первого блока сравнения и управляющему входу второго блока оценки фазового рассогласования, выходы первого блока оценки фазового рассогласования подсоединены к соответствующим информационным входам блока памяти, выходы регистра сдвига подсоединены к соответствующим входам дешифратора, а вход счетчика импульсов подключен к тактовым 5 входам регистра сдвига и распределителя импульсов, причем информационный вход и тактовый вход регистра сдвига и выходы распределителя импульсов являются соответственно информационным входом, так0 товым входом и выходами устройства, о т л

ичающееся тем, что, с целью повышения

быстродействия, введены последовательно

соединенные дополнительный RS-триггер,

первый элемент И, формирователь сигна5 ла Запись, первый дополнительный блок памяти, дополнительный дешифратор, второй элемент И, дополнительный счетчик им- пульсов, дополнительный коммутатор, второй и третий дополнительные блоки па0 мяти, первый дополнительный блок сравнения, третий элемент И, первый ключ, четвертый дополнительный блок памяти, второй дополнительный блок сравнения, выход которого подсоединен к информаци5 онному входу первого ключа, последовательно соединенные сумматор и второй ключ, выходы которого подсоединены к соответствующим информационным входам первого дополнительного блока памяти, а

0 также второй дополнительный блок сравнения, элемент НЕ и генератор импульсов, при этом выход дешифратора подсоединен непосредственно к управляющему входу второго ключа, входу сумматора и второму

5 входу третьего элемента И и через элемент НЕ к второму входу второго элемента И, третий вход которого подключен к выходу третьего дополнительного блока сравнения, выход дополнительного RS-триггера

0 подсоединен к дополнительному управляющему входу второго ключа и управляющему входу дополнительного коммутатора, выходы которого подключены к соответствующим управляющим входам первого допол5 нительного блока памяти,вторым входам первого дополнительного блока сравнения и первым входам третьего дополнительного блока сравнения, вторые входы которого подключены к соответствующим выходам

0 второго дополнительного блока памяти, вход сигнала Запись которого подключен к выходу первого ключа, второй вход третьего блока сравнения объединен со счетным входом второго накопителя и подключен к

5 выходу третьего элемента И, выход третьего блока сравнения подсоединен к входу сиг-, нала Запись третьего дополнительного блока памяти, четвертому входу второго элемента И и входу сигнала Запись второго накопителя, информационные входы которого подключены к соответствующим выходам четвертого дополнительного блока памяти, вход сигнала Сброс которого объединен с S-входом дополнительного RS- триггера и подключен к выходу второго элемента И, выход генератора импульсов подсоединен к второму входу первого элемента И, выход которого подсоединен к счетному входу дополнительного счетчика импульсов, выход которого подсоединен к R-входу дополнительного RS-триггера, вы

ходы первого дополнительного блока памяти подсоединены к соответствующим входам сумматора, вторым входам второго дополнительного блока сравнения и информационным входам четвертого дополнительного блока памяти, выходы счетчика импульсов подсоединены к соответствующим вторым информационным входам дополнительного коммутатора, а тактовый вход формирователя сигнала Запись подключен к тактовому входу регистра сдвига.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1478363A1 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1469562A1 |

| Устройство цикловой синхронизации | 1980 |

|

SU944136A1 |

| Устройство цикловой синхронизации | 1980 |

|

SU924892A1 |

| Многоканальное устройство синхронизации и выравнивания потоков информации | 1979 |

|

SU886018A1 |

| УСТРОЙСТВО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 2006 |

|

RU2306674C1 |

| Устройство цикловой синхронизации | 1981 |

|

SU987836A1 |

| Устройство асинхронного сопряжения цифровых сигналов | 1983 |

|

SU1111257A1 |

Изобретение относится к электросвязи и может быть использовано для циклового фазирования систем передачи дискретной информации. Целью изобретения является повышение быстродействия. Устройство для цикловой синхронизации содержит формирователь сигнала Сброс, регистр сдвига, блоки сравнения, распределитель импульсов, RS-триггер, дешифратор, блоки оценки фазового рассогласования, коммутаторы, накопители, блок умножения, блок памяти, формирователь сигнала Запись, дополнительные блоки памяти, счетчик импульсов, дополнительный дешифратор, ключи, сумматор, элементы И, третий дополнительный блок сравнения, элемент НЕ, дополнительный коммутатор, дополнительный счетчик, дополнительный блок сравнения, дополнительный RS-триггер, первый дополнительный блок сравнения и генератор импульсов. Если момент включения устt ройства не совпал с принятием из канала связи фазирующей комбинации, узел контроля сигнала начинает параллельную проверку наличия фазирующей последовательности на всех позициях цикла. Решение об обнаружении фазирующей комбинации на некоторой позиции цикла узел контроля - синхросигнала принимает после 1-кратного формирования импульса с выхода дешифратора на этой позиции цикла. При этом за I последовательных циклов заполняется накопитель и на его выходе формируется им пульс, проходящий через блок сравнения и устанавливающий распределитель в новое исходное состояние, а также сбрасывающий RS-триггер, что соответствует принятию решения о вхождении устройства в синхронизм. После этого сигналы с выхода распределителя и дешифратора совпадают и по ним заполняется накопитель. В случае сбоя синхронизации в регистре сдвига записана комбинация, значительно отличающаяся от фазирующей, а на выходе блока сравнения формируется сигнал несовпадения, поступающий на накопитель. Блок оценки фазового рассогласования определяет, насколько принятый сигнал отличается (в числе бит) от фазирующей комбинации. Выходной код блока умножения через коммутатор устанавливает коэффициент накопления накопителя, определяющего время поддержания синхронизма на прежней временной позиции при сбое фазы с целью исключения ложных сбоев синхронизации. 3 ил. ЬГ Ё VI VI 00 ЧЭ «о W

Фиг.

От распределителя 4

| Устройство цикловой синхронизации | 1980 |

|

SU924892A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-11-30—Публикация

1989-10-25—Подача