Область техники

Настоящее изобретение относится к системе связи, в частности, к устройству и способу перемежения для системы связи. Более конкретно, настоящее изобретение относится к устройству и способу перемежения, которые могут быть использованы для генерации адресов перемежения и для определения размера перемежителя так, чтобы повысить эффективность памяти перемежителя.

Предшествующий уровень техники

Перемежение представляет собой метод, обычно используемый для повышения эффективности кода исправления ошибок в канале с замиранием, тесно связанный с декодированием случайного кода исправления ошибок. Многие приложения, такие как радиоинтерфейс для стандарта IMT-2000 (Международная мобильная телекоммуникация-2000), требуют хорошо определенного способа для реализации различных методов перемежения. Кроме того, такие методы дополнительно служат для улучшения надежности цифровых систем связи, в частности, для повышения эффективности существующих и перспективных цифровых систем связи.

Стандарт IMT-2000 рекомендует использовать в качестве канального перемежителя перемежитель с обращением (реверсированием) битов. Однако такой перемежитель может иметь различные размеры, а прямая и обратная линии связи, определенные стандартом IMT-2000, могут иметь различные типы логических каналов. Поэтому для обеспечения диапазона требований стандарта IMT-2000 требуется увеличенный объем памяти перемежителя. Например, в режиме N=3 передачи прямой линии связи могут использоваться перемежители с различными размерами, такие как от 144 до 36864 бит/кадр. Краткое описание перемежителя с реверсированием битов представлено ниже.

На фиг.1 показана блок-схема, иллюстрирующая метод перестановки для перемежителя с реверсированием битов. Согласно фиг.1 перемежение с реверсированием битов представляет собой метод для генерации адресов перемежения путем изменения битовых позиций адреса с наиболее значимого (старшего) бита (MSB) на наименее значимый (младший) бит (LSB). Этот способ перемежения имеет ряд преимуществ. Во-первых, поскольку перемежитель может быть реализован с использованием перечисляющей функции, то память использовать просто и легко реализовать перемежители с различными размерами. Кроме того, позиции битов в перемеженной последовательности распределены случайным образом в большинстве местоположений. Однако перемежитель с размером, который не может быть выражен как степень числа 2, имеет низкую эффективность использования памяти. Например, для реализации 36864-битового перемежителя потребуется память объемом 64 кбит (65536=216). Это объясняется тем, что наибольшее целое число, которое может быть выражено как степень числа 2, среди чисел меньших, чем 36864, есть число 65536. Поэтому 28672 (65536-36864) битов являются неиспользуемыми в памяти перемежителя, тем самым обуславливая потери памяти. Кроме того, хотя память имеет достаточную емкость, очень трудно реализовать способ для передачи символов. Кроме того, приемнику трудно определить точные позиции принятых символов. Наконец, поскольку используются различные типы перемежителей, необходимо сохранить различные правила перемежения в памяти, что требует использования контроллера, такого как центральный процессорный блок (ЦПБ), чтобы также иметь значительную емкость памяти.

Обычные способы перемежения также имеют ряд дополнительных недостатков. Во-первых, при существующих способах перемежения размер перемежителя не может быть выражен как степень числа 2, и перемежитель наибольшего размера имеет самый низкий уровень эффективности памяти. То есть при проектировании перемежителя для прямой линии стандарта IMT-2000 размер каждого логического канала не выражается как 2m, и перемежитель имеет большой размер. Поэтому использование способа с реверсированием битов является неэффективным.

Во-вторых, в существующих способах перемежения в типовом случае необходимо сохранять различные правила перемежения или команды в соответствии с размерами перемежителя в контроллере, ЦПБ или хосте (ведущем узле) приемопередатчика. Поэтому память хоста требует отдельного блока памяти команд, в дополнение к буферу премежителя.

В-третьих, если размер перемежителя установлен как 2m, чтобы использовать способ перемежения с чередованием битов, то необходимо исключить необязательные недействительные адреса. Поэтому перемежитель реализует сложный способ передачи и испытывает трудности в получении синхронизации символов при реализации.

Соответственно существует необходимость в устройстве и способе перемежения, которые обеспечивают возможность реализации перемежителя с эффективным использованием памяти, который может использовать метод перемежения с реверсированием битов без излишней сложности.

Сущность изобретения

Поэтому задачей настоящего изобретения является создание способа и устройства перемежения, предназначенных для генерации адресов перемежения для различных размеров перемежителя посредством единственного алгоритма в системе связи.

Также задачей настоящего и изобретения является создание способа и устройства перемежения, которые являются более эффективными и требуют только объема памяти перемежителя, равного размеру N кадра, при использовании в системе связи.

Также задачей настоящего и изобретения является создание устройства и способа перемежения входных данных в системе связи с размером перемежителя, равным N=2m×j+a(где 0<a<2m).

Указанные и другие результаты достигаются по существу обеспечением устройства и способа перемежения, которые используют операции определения нового размера N'=2m×(j+1) перемежителя и адресов от 0 до N'-1, если заданный размер N перемежителя больше, чем 2m×j, и меньше, чем 2m×(j+1), последовательного сохранения N битов входных данных в памяти с новым размером N' перемежителя от адреса 0 до адреса N-1, выполнения перемежения с частичным реверсированием битов (PBRO), осуществления перемежения в памяти с новым размером N' перемежителя и считывания данных из памяти путем удаления адресов, соответствующих адресам от N до N'-1 памяти, перед перемежением.

Устройство и способ также обеспечивают перемежение входных данных в системе связи с размером перемежителя, равным N=2m×j+a (где 0<a<2m). Устройство и способ перемежения используют операции определения адресов в последовательном направлении столбцов в памяти со структурой R×C матрицы размера N'=2m×(j+1), сохранения входных данных в последовательном направлении столбцов в памяти от адреса 0 до адреса N-1, причем никакие входные данные не сохранены в (2m-а) областях, соответствующих адресам от N до N'-1 в последнем столбце в памяти, и генерирования выходных адресов со структурой R×C матрицы путем PBRO-перемежения определенных адресов. Устройство и способ далее обеспечивают генерирование адреса считывания для считывания данных, сохраненных в памяти, путем определения выходных адресов в последовательном направлении столбцов, где генерируемый адрес считывания исключает выходные адреса, соответствующие адресам от N до N'-1.

Краткое описание чертежей

Вышеуказанные и другие задачи, признаки и преимущества настоящего изобретения поясняются в нижеследующем детальном описании со ссылками на чертежи, на которых представлено следующее:

Фиг.1 - блок-схема, иллюстрирующая пример известной модели перестановок перемежителя с реверсированием битов согласно предшествующему уровню техники;

Фиг.2 - блок-схема, иллюстрирующая пример структуры перемежителя согласно варианту осуществления настоящего изобретения;

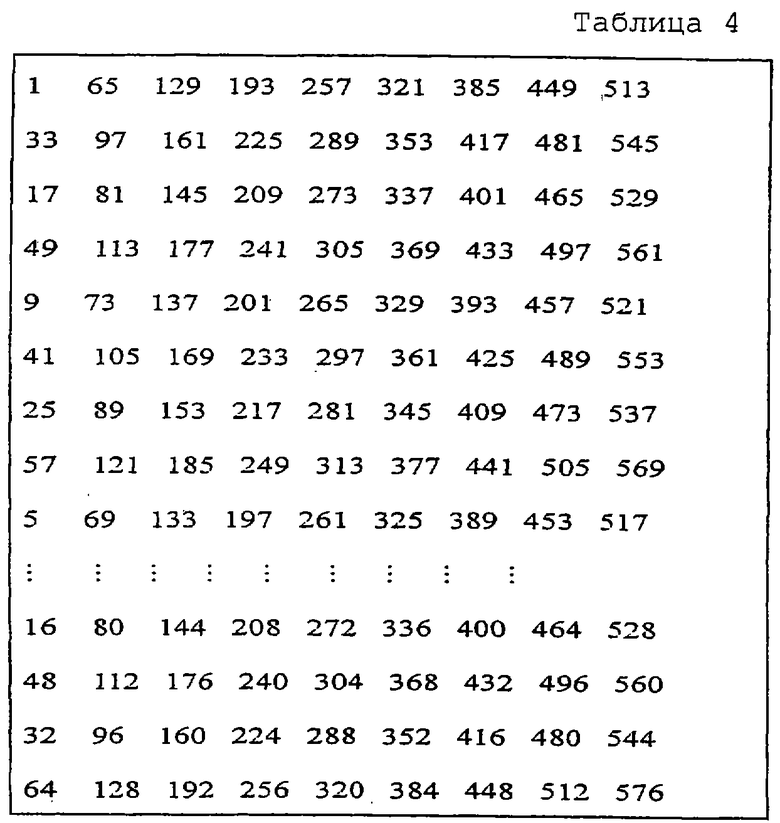

Фиг.3 - блок-схема, иллюстрирующая пример структуры обращенного перемежителя, соответствующего перемежителю по фиг.2;

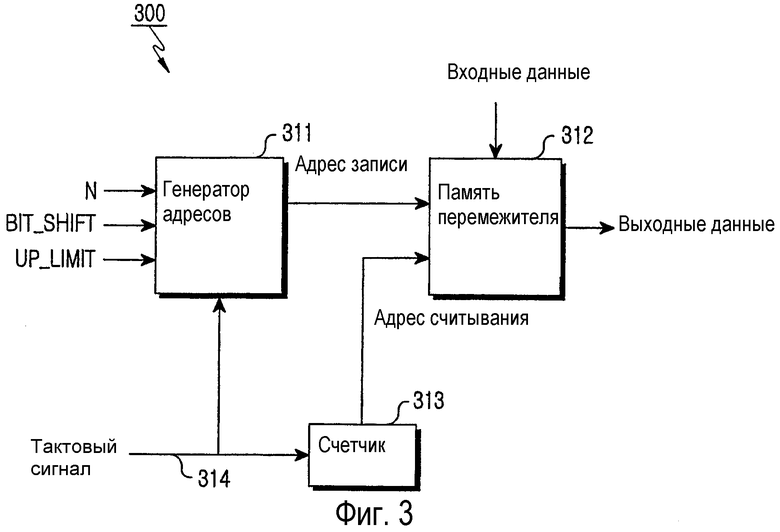

Фиг.4 - блок-схема последовательности операций, иллюстрирующая пример процесса перемежения с частичным реверсированием битов (PBRO) согласно варианту осуществления настоящего изобретения;

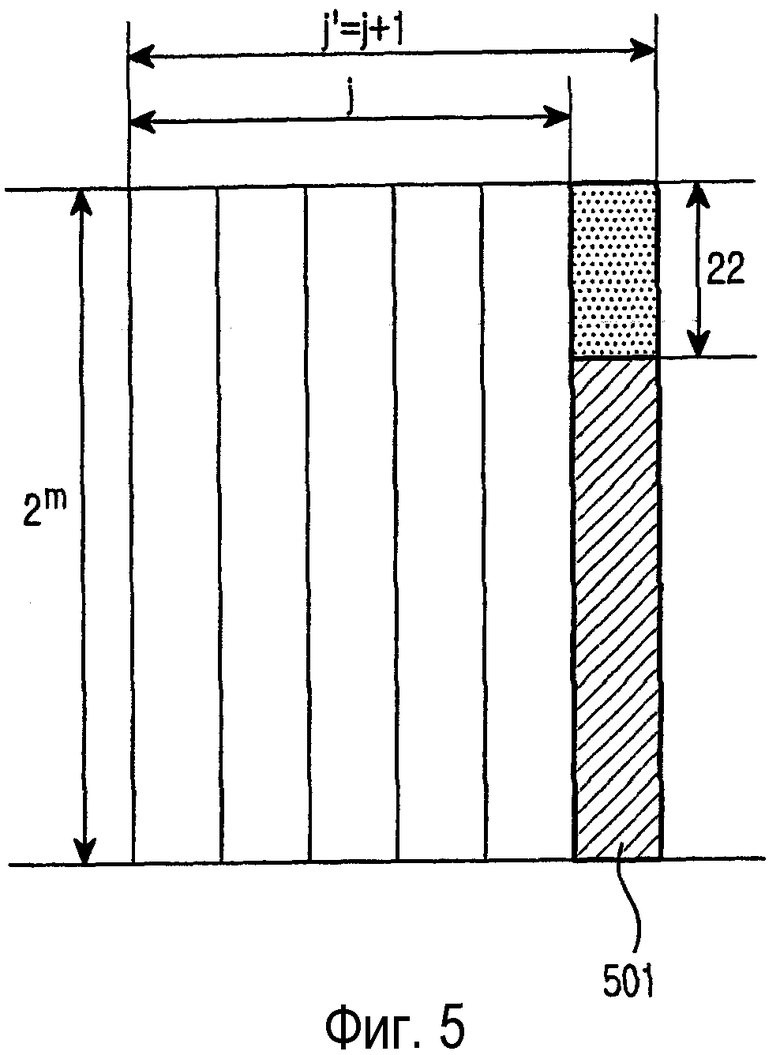

Фиг.5 - пример способа выполнения операции PBRO-перемежения согласно другому варианту осуществления настоящего изобретения;

Фиг.6 - иллюстрация операции PBRO-перемежения для размера N=406 перемежителя в соответствии с вариантом осуществления настоящего изобретения.

Детальное описание предпочтительных вариантов осуществления изобретения

Предпочтительный вариант осуществления настоящего изобретения описан ниже со ссылками на чертежи. В последующем описании хорошо известные специалистам в данной области техники функции или структуры подробно не описываются, чтобы не затемнять сущность изобретения несущественными деталями.

В процессе работы перемежитель/обращенный перемежитель согласно варианту осуществления настоящего изобретения осуществляет перестановку последовательности входных символов в соответствии с алгоритмом перемежения/обращенного перемежения. Последовательность символов затем сохраняется в выходном буфере в новой последовательности. Поэтому описанный ниже перемежитель/ обращенный перемежитель включает в себя, по меньшей мере, память премежителя, такую как буфер входных данных и буфер выходных данных, генератор адресов и общий счетчик.

Память перемежителя, генератор адресов и счетчик перемежителя/обращенного перемежителя показаны на фиг.2, где приведен пример структуры перемежителя 200 согласно варианту осуществления настоящего изобретения. Согласно фиг.2 генератор 211 адресов генерирует адрес перемежения для считывания битовых символов, последовательно сохраненных в памяти 212 перемежителя, путем приема размера N перемежителя, первого параметра 'm' (или параметра сдвига бита BIT_SHIFT), второго параметра 'j' (или параметр ограничения сверху UP_LIMIT) и тактового сигнала. Память 212 перемежителя последовательно сохраняет входные битовые символы в режиме записи и выводит битовые символы согласно адресу, обеспеченному от генератора 211 адресов в режиме считывания. Счетчик 213 отсчитывает входной тактовый сигнал 214 и выдает значение отсчета тактового сигнала в память 212 перемежителя в качестве адреса записи.

Как описано выше, перемежитель 200 последовательно записывает входные данные в память 212 перемежителя в режиме записи и выводит данные, сохраненные в памяти 212 перемежителя, согласно адресу считывания, сформированному генератором 211 адресов.

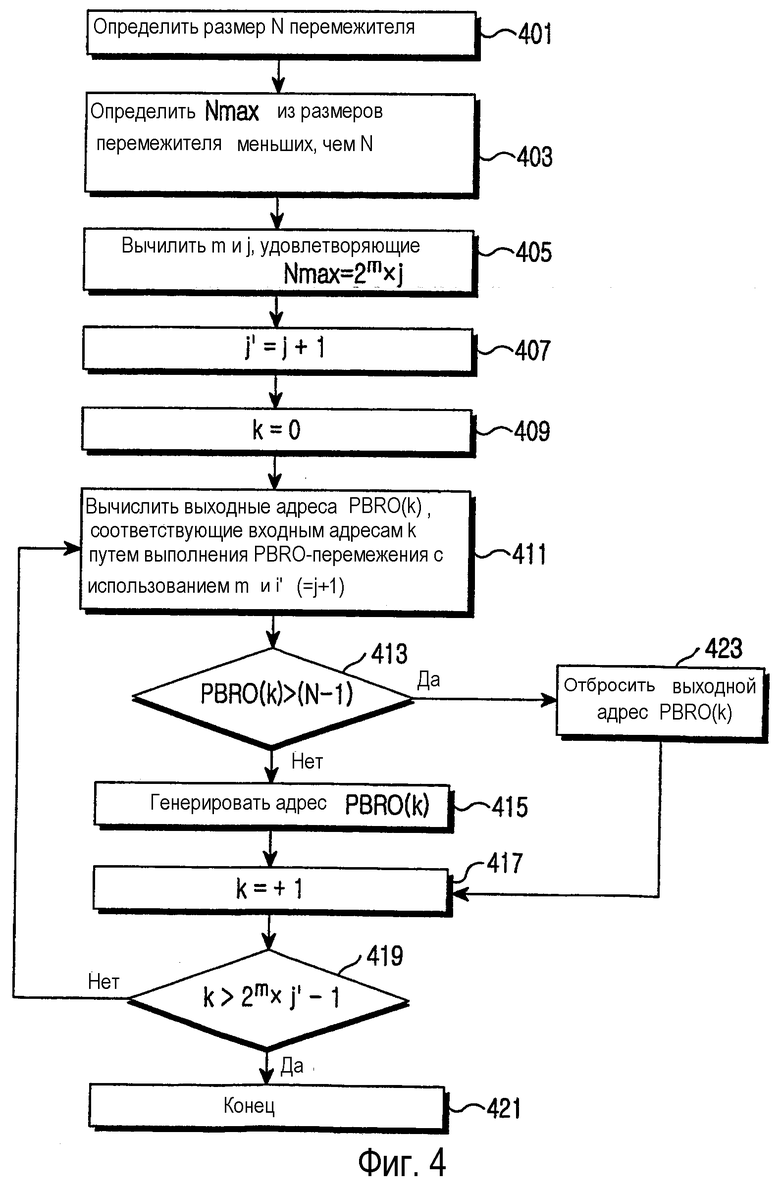

В данном случае генератор 211 адресов генерирует адрес считывания или адрес перемежения согласно алгоритму перемежения с частичным реверсированием битов (PBRO), определенному ниже в виде уравнения (1).

r=k mod j

S=BRO(PUC)

ADDRESS_READ=r×2m+s

В уравнении (1) 'k' представляет последовательные числа от 0 до N-1 (0≤k≤N-1), указывающие последовательность бита выходных данных, 'm' представляет первый параметр, указывающий число последовательных нулей (0) от младшего бита (LSB) до старшего бита (MSB), и 'j' представляет второй параметр, соответствующий десятичному значению битов иных, чем биты последовательных нулей. Здесь размер N перемежителя определяется как 2m×j.

Ниже описан способ генерации адреса перемежения для считывания входных символов, последовательно записанных в памяти 212 перемежителя, с учетом уравнения (1). Если, как в примере, приведенном выше, размер перемежителя равен N, то в уравнении (1) k(=0,1.2,...,N-1) указывает временной индекс входных данных, а третий параметр 'r', PUC и четвертый параметр 's' указывают предварительно определенные параметры. Кроме того, 'mod' и '/' обозначают операцию по модулю и операцию деления для вычисления остатка и частного соответственно. Кроме того, BRO(H) обозначает функцию реверсирования битов для преобразования 'H' в двоичный формат и затем преобразования его в десятичное значение путем реверсированного упорядочения двоичного значения от MSB к LSB. Поэтому с использованием функции уравнения (1) перемежитель 200 может вычислить индекс последовательности считывания ADDRESS_READ соответственно последовательности 'k' входных данных и считывать содержимое памяти в соответствии с индексом последовательности считывания ADDRESS_READ. Первый параметр 'm' и второй параметр 'j' определяются в соответствии с размером перемежителя. После того как размер N перемежителя, первый параметр 'm' и второй параметр 'j' определены, перемежитель генерирует, в зависимости от этих значений, новый индекс адресации ADDRESS_READ, соответствующий каждому 'k' согласно следующему алгоритму, и считывает данные из памяти 212 перемежителя с использованием индекса адресации ADDRESS_READ.

Ниже описан способ определения первого параметра 'm' и второго параметра 'j' из размера кадра (или размера перемежителя) N. Для предварительно определенного размера N перемежителя размер N выражается как двоичное значение. Затем вычисляется число последовательных нулей (0) от младшего бита (LSB) до старшего бита (MSB), и это значение определяется как первый параметр 'm'. Кроме того, второй параметр 'j' определяется путем учета усеченных битов, исключая биты последовательных '0' и преобразования их в десятичное число. Например, если N=576, то оно может быть выражено как двоичное значение N=[10 0100 0000]. Поэтому m=6 и j=(1001)2=9.

На фиг.3 показана структура обращенного перемежителя 300, соответствующего перемежителю 200, описанному выше. Согласно фиг.3 генератор 311 адресов генерирует адрес памяти перемежителя для выполнения операции записи путем получения значения N размера перемежителя, значения BIT_SHIFT (т.е. первый параметр 'm') значение UP_LIMIT (т.е. второй параметр 'j') и тактовый сигнал и выдает сформированный адрес памяти перемежителя в память 312 обращенного перемежителя. Память 312 обращенного перемежителя сохраняет входные данные соответственно адресу записи, полученному от генератора 311 адресов в режиме записи, и последовательно выводит сохраненные данные в режиме считывания. Счетчик 313 отсчитывает входной тактовый сигнал 314 и выдает отсчитанное значение тактового сигнала в память 312 обращенного перемежителя в качестве значения адреса считывания.

Обращенный перемежитель 300 имеет по существу ту же самую структуру, что и перемежитель 200, описанный выше, и выполняет операцию обратной операции перемежителя 200. То есть отличие обращенного перемежителя 300 от перемежителя 200 заключается в том, что входные данные сохраняются в памяти 312 обращенного перемежителя с использованием алгоритма уравнения (1) в режиме записи и данные последовательно считываются в режиме считывания. Обращенный перемежитель 300 сохраняет данные в исходной последовательности в режиме записи, чтобы восстановить исходную последовательность данных, переданных от передатчика.

Для удобства описание ниже приведено со ссылкой на перемежитель 200. Ссылки даются на вариант осуществления, который применим как к системе стандарта IMT-2000, так и к системе множественного доступа с кодовым разделением каналов стандарта CDMA-2000.

Сначала со ссылкой на Таблицу 1 приводится детальное описание, касающееся размера перемежителя, используемого в прямой линии связи системы стандарта IMT-2000.

(5 мс)

(5 мс)

(5 мс)

(26,6 мс)

(5 мс)

В таблице 1 F-DCH обозначает прямой основной канал, F-SCH - прямой дополнительный канал, F-CCCH - прямой общий канал управления, F-SYNC CH - прямой канал синхронизации, F-PCH - прямой канал поискового вызова, F-DCCH - прямой выделенный канал управления.

Как следует из таблицы 1, система стандарта IMT-2000 предусматривает 12 размеров перемежителя (N=12), каждый применяется к прямым логическим каналам, как указано посредством '0'. Например, прямой основной канал F-FCH (установка скорости 2) использует размеры перемежителя 144 бита, 576 битов и 1152 бита. В данном случае для размера перемежителя, равного 144 битам, используется кадр 5 мс.

В таблице 2 приведены первый параметр 'm' и второй параметр 'j', вычисленные для размеров перемежителя, приведенных в таблице 1.

(5 мс/кадр)

5 мс/кадр

(26,22 мс/кадр)

(20 мс/кадр)

Ниже со ссылкой на таблицу 2 приведено описание вычисления BIT_SHIFT и UP_LIMIT для размера перемежителя N=9216. Сначала размер перемежителя 9216 выражается как двоичное значение N=[10 0100 0000 0000]. Для этого двоичного значения вычисляется максимальное число нулей (0) от младшего бита до старшего бита, и вычисленное значение определяется как первый параметр 'm' (или BIT_SHIFT). Затем усеченные биты, исключающие биты последовательных нулей, собираются вместе и преобразуются в десятичное значение (1001=9(10)). Это десятичное значение есть UP_LIMIT(9).

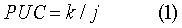

Приведенные ниже таблицы 3 и 4 иллюстрируют соответственно режим записи и режим считывания для перемежителя с N=576 в качестве примера.

В режиме записи биты входных данных последовательно сохраняются в памяти 212 перемежителя от адреса 0 до адреса 574, как показано в таблице 3. Затем в режиме считывания биты данных выводятся из памяти 212 перемежителя с использованием адресов считывания, сформированных генератором 211 адресов.

Третий бит выходных данных (k=2) также может быть описан со ссылкой на уравнение (1). Сначала для N=576 BIT_SHIFT=6 и UP_LIMIT=9. Поэтому r=2mod9=2 и PUC=2/9=0. Кроме того, s=BRO(0)=0. В результате окончательно вычисленный адрес ADDRESS_READ=2×26+0=128. Однако поскольку таблица 4 показывает адреса считывания от 1 до N, то действительный адрес определяется путем добавления 1 к вычисленному адресу.

Вышеуказанная операция PBRO-перемежения была описана со ссылкой на случай, когда размер N перемежителя равен 2m×j и определен посредством первого параметра 'm' и второго параметра 'j'. Однако если размер N перемежителя больше, чем 2m×j, и меньше, чем 2m×(j+1), то операция PBRO-перемежения должна выполняться другим способом. То есть если размер N перемежителя равен 2m×j+а, то необходимо выполнить другую операцию перемежения. Здесь 'a' является положительным числом больше нуля и меньше, чем 2m (0<a<2m). При реализации системы может иметь место случай, когда размер перемежителя не равен 2m×j согласно характеристике верхнего уровня, или первый параметр 'm' слишком мал, даже если размер N перемежителя равен 2m×j. В этом случае перемежитель может не иметь PBRO-характеристики, так что потребуется другая операция перемежения. Если размер перемежителя равен 384=27×3, то первый и второй параметры могут быть определены как m=7 и j=3 соответственно. Однако в случае, когда размер перемежителя равен 406=27×3+22, то размер перемежителя не может быть выражен в терминах 2m×j, хотя первый и второй параметры определены как m=7 и j=3 соответственно. Поскольку возможный размер перемежителя, который может быть выражен в терминах 2m×j, равен 2×(26×3+11)=2×203, первый и второй параметры могут быть определены как m=1 и j=203 соответственно. В действительности, однако, если m=1, PBRO-характеристика не обеспечивается.

Таблица 5, представленная ниже, иллюстрирует случай, когда PBRO-перемежение возможно в соответствии с размером перемежителя, и случай, когда PBRO-перемежение невозможно в соответствии с размером перемежителя. Более конкретно, таблица 5 иллюстрирует параметры m и j', определенные для 6 размеров перемежителя, соответственно равных 406, 790, 1558, 2326, 3094 и 3862, при а=22.

j+

1

(=27 3)

3)

(=27 3+22)

3+22)

(=28 3)

3)

(=28 3+22)

3+22)

(=29 3)

3)

(=29 3+22)

3+22)

(=28 9)

9)

(=28 9+22)

9+22)

(=210 3)

3)

(=210 3+22)

3+22)

(=28 15)

15)

(=28 15+22)

15+22)

"Совершенные случаи", показанные в левом столбце таблицы 5, представляют случаи, когда PBRO-перемежение возможно, поскольку размер перемежителя равен N=Nmax, в частности, 384, 768, 1536, 2304, 3072 и 3840. В то же время "несовершенные случаи", показанные в правом столбце таблицы 5, представляют случаи, когда PBRO-характеристика потеряна; "отбросить" представляет число адресов, которые должны быть удалены из выходных адресов перемежения.

Поэтому настоящее изобретение обеспечивает способ, позволяющий осуществить PBRO-перемежение для любого размера перемежителя, показанного в таблице 5.

На фиг.4 показана блок-схема последовательности операций для перемежителя 200 согласно варианту осуществления настоящего изобретения. Более конкретно, фиг.4 иллюстрирует процедуру выполнения PBRO-перемежения в отношении размеров перемежителя, указанных для "несовершенных случаев" в таблице 5. Эта процедура включает в себя этапы сохранения входных данных в памяти 212 перемежителя в соответствии с адресом записи, значением отсчета со счетчика 213, и считывания данных, сохраненных памяти 212 перемежителя соответственно адресу считывания, сформированному генератором 211 адресов. Способ генерирования адреса записи счетчиком 213 хорошо известен специалистам в данной области техники, поэтому он здесь не описывается. В противоположность этому ниже приведено подробное описание способа генерации адреса считывания генератором 211 адресов перемежителя 200.

Согласно фиг.4 генератор 211 адресов на этапе 401 определяет размер N перемежителя. Размер N перемежителя равен размеру данных, подлежащих перемежению. После этого генератор 211 адресов на этапе 403 вычисляет максимальное значение Nmax, удовлетворяющее 2m×j, среди значений Nmax меньших, чем размер N перемежителя, и на этапе 405 вычисляет первый параметр m и второй параметр j, удовлетворяющий соотношению Nmax=2mxj, с использованием способа PBRO-перемежения, применимого к "совершенным случаям" из таблицы 5.

Затем генератор 211 адресов на этапе 407 определяет j' путем добавления 1 к второму параметру j и на этапе 409 инициализирует параметр k. Как описано выше, параметр k представляет последовательность считывания. После этого на этапе 411 генератор 211 адресов определяет новый размер перемежителя N'=2mxj'=2mx(j+1), исходя из m и j'=j+1. В данном случае новый размер перемежителя характеризуется соотношением N'>N>Nmax. После этого генератор адресов вычисляет выходной адрес PBRO(k) с использованием способа PBRO-перемежения в соответствии с первым параметром m и вторым параметром j.

Согласно варианту осуществления настоящего изобретения последовательность информационных символов (входных данных), принимаемых в режиме записи, последовательно сохраняется в памяти перемежителя от адреса 0 до адреса N-1. Поэтому перемежителю требуется память размером N. То есть, хотя перемежитель может быть спроектирован таким образом, что память перемежителя может иметь дополнительные области от адреса N до адреса N'-1, эти области памяти не используются. Данная операция записи выполняется путем генерации адреса записи счетчиком 213 по фиг.2. Счетчик 213 служит в качестве генератора адресов записи.

В описанном выше варианте осуществления настоящего изобретения генератор адресов выполняет PBRO-перемежение в соответствии с уравнением (1) с использованием нового размера N' перемежителя в режиме записи для генерации адреса считывания PBRO(k) для выходной последовательности k и затем считывает информационные символы, последовательно сохраненные в памяти перемежителя, в соответствии с генерированным адресом считывания.

При осуществлении режима считывания генератор адресов на этапе 413 определяет, является ли сформированный адрес считывания PBRO(k) большим, чем N-1. Если сформированный адрес считывания PBRO(k) больше, чем N-1, то генератор адресов на этапе 423 отбрасывает сформированный адрес считывания. В противном случае, если сформированный адрес считывания PBRO(k) меньше или равен N-1, то генератор адресов на этапе 415 считывает данные, сохраненные соответственно сформированному адресу считывания.

После этого генератор адресов на этапе 417 увеличивает параметр k, представляющий последовательность вывода, на 1 и на этапе 419 определяет, является ли параметр k большим, чем 2mxj'-1 (или N'-1). Если параметр k меньше или равен 2mxj'-1, то генератор адресов возвращается на этап 411 для последовательной генерации адреса считывания. Однако если параметр k больше, чем 2mxj'-1, то генератор адресов на этапе 421 прекращает операцию генерации адресов считывания. Среди сформированных адресов считывания адрес, больший или равный размеру перемежителя N, отбрасывается. Поэтому в качестве окончательных адресов считывания для перемежителя может использоваться количество адресов, равное числу N входных битовых символов.

Кроме того, таблица 5 иллюстрирует параметры m и j', определенные для 6 размеров перемежителя, соответственно равных 406, 790, 1558, 2326, 3094 и 3862. Как показано в таблице 5, j' на 1 превышает параметр j, вычисленный из Nmax.

Фиг.5 иллюстрирует способ выполнения операции PBRO-перемежения, относящейся к "несовершенным случаям", с использованием параметров m и j', представленных в таблице 5. Согласно фиг.5 22 битовых символа добавлены к последнему столбцу 501, и адреса 2m-22, определенные посредством исключения 22 элементов из элементов последнего столбца, не используются. Поэтому после выполнения PBRO-перемежения битовые символы, принадлежащие к этой части, удаляются. Если предполагаются входные данные с размером перемежителя N=2mxj+a (где 0<a<2m), то входные данные последовательно сохраняются в направлении столбцов в памяти адресов от адреса 0 до адреса N-1, и в данном случае никакие входные данные не сохраняются в (2m-a) областях, соответствующих адресам от N до N'-1.

Фиг.6 иллюстрирует операцию PBRO-перемежения для размера перемежителя N=406 в соответствии с вариантом осуществления настоящего изобретения. Для размера перемежителя N=406 значение Nmax равно 384=27×3, как показано в таблице 5, а первый и второй параметры определены соответственно как m=7 и j=3. Поэтому j'=j+1=4. В режиме записи перемежитель 200 последовательно сохраняет входные битовые символы от 0-го до 40-го символа в памяти перемежителя, как показано на фиг.6. Поскольку остальные битовые символы не существуют, они представлены на чертеже как Х. Перемежитель последовательно сохраняет 406 входных битовых символов в направлении столбцов в памяти перемежителя, имеющей форму матрицы R×C (=27×(3+1)). Здесь только 22 битовых символа сохранены в последнем (j=1)-м столбце, и ни один битовый символ не сохранен в остальных 106 адресах.

Перемежитель 200 выполняет PBRO-перемежение соответственно уравнению (1) в режиме считывания. Если выходной адрес больше или равен размеру перемежителя 406, то перемежитель не выводит соответствующий выходной адрес. Поэтому предложенный перемежитель выводит точно N=406 адресов и имеет память перемежителя с размером N=406.

Другим применением варианта осуществления настоящего изобретения, описанного выше, может являться случай, когда перемежаются входные данные с размером N=2mxj+a(где 0<a<2m). Такая операция перемежения реализуется путем определения сначала адресов в последовательном направлении столбцов памяти с матричной структурой N'=2mx(j+1). Затем входные данные сохраняются в последовательном направлении столбцов в памяти от адреса 0 до адреса N-1. В данном случае никакие данные не сохраняются в (2m-a) областях, соответствующих адресам от N до N'-1 в последнем столбце памяти. Полученные адреса затем подвергаются PBRO-перемежению для генерации выходного адреса соответственно R×C матрице. Выходные адреса определяются в последовательном направлении столбцов для генерации адреса считывания для считывания данных, сохраненных в памяти. В данном случае, как и в случае формирования адреса считывания, выходные адреса, соответствующие адресам от N до N'-1, отбрасываются.

Таблица 5 и 6 иллюстрируют параметры m и j, необходимые для выполнения PBRO-перемежения соответственно "несовершенным случаям" согласно другому варианту осуществления настоящего изобретения. Как показано выше, в таблице 5 были представлены параметры m и j, определенные для 6 размеров перемежителя, соответственно равных 406, 790, 1558, 2326, 3094 и 3862, при а=22.

В таблице 6 представлены параметры m и j', определенные для 6 размеров перемежителя, соответственно равных 408, 792, 1560, 2328, 3096 и 3864, при а=24.

j+

1

(=27 3)

3)

(=27 3+24)

3+24)

(=28 3)

3)

(=28 3+24)

3+24)

(=29 3)

3)

(=29 3+24)

3+24)

(=28 9)

9)

(=28 9+24)

9+24)

(=210 3)

3)

(=210 3+24)

3+24)

(=28 15)

15)

(=28 15+24)

15+24)

Таблица 6 показывает параметры m и j', определенные для 6 размеров перемежителя, соответственно равных 408, 792, 1560, 2328, 3096 и 3864, при а=24. Однако с учетом процедуры по фиг.4 таблица 6 может быть заменена на таблицу 7.

j+

1

(=27 3)

3)

(=27 3+24)

3+24)

(=28 3)

3)

(=28 3+24)

3+24)

(=29 3)

3)

(=29 3+24)

3+24)

(=210 2)

2)

(=28 9+22)

9+22)

(=210 3)

3)

(=210 3+24)

3+24)

(=211 1)

1)

(=28 15+24)

15+24)

Если размер перемежителя соответствует "несовершенным случаям", то обращенное перемежение выполняется согласно процедуре, обратной процедуре перемежения, которая была описана в связи с PBRO-перемежением и обращенным перемежением. То есть в процессе обращенного перемежения генерируется адрес записи с использованием процедуры по фиг.4 для генерирования адреса считывания, который был использован в процессе перемежения. Поэтому хотя адрес записи генерируется с новым перемежителем, имеющим больший размер, чем реальный перемежитель, ненужные адреса исключаются из сформированных адресов записи, и в памяти сохраняется столько битов данных, сколько определяется размером реального перемежителя.

Как описано выше, настоящее изобретение обеспечивает способ эффективной генерации адресов для различных размеров перемежителей, которые не могут быть выражены через степень числа 2 и тем самым способствуют увеличению неэффективного использования памяти перемежителя. Кроме того, адрес для различных размеров перемежителя может генерироваться согласно одному алгоритму, предотвращая потери ресурса памяти, обусловленные сохранением правил перемежения для соответствующих размеров перемежителя в ЦПБ. Кроме того, настоящее изобретение способствует повышению эффективности использования памяти, поскольку предложенный перемежитель требует такого объема памяти, каков размер N кадра.

Хотя изобретение показано и описано со ссылками на определенные его варианты осуществления, специалистам в данной области техники должно быть понятно, что различные изменения по форме и в деталях могу быть осуществлены без отклонения от сущности и объема изобретения, как определено в формуле изобретения. Например, хотя настоящее изобретение описано со ссылкой на случай, когда значение 'a' равно 22 и 24, изобретение может быть применено и к случаю, когда 'a' меньше, чем 2m.

Заявлены устройство и способ перемежения для определения нового размера N'=2m×(j+1) перемежителя и адресов от 0 до N-1, если заданный размер N перемежителя больше, чем 2m×j, и меньше, чем 2m×(j+1), где m представляет первый параметр, указывающий число последовательных нулевых битов от младшего бита (LSB) до старшего бита (MSB), и j представляет второй параметр, соответствующий десятичному значению битов иных, чем биты последовательных нулей. Устройство и способ перемежения предусматривают последовательное сохранение N битов входных данных в памяти перемежителя с новым размером N' перемежителя от адреса 0 до адреса N-1. Затем устройство и способ перемежения выполняют перемежение с частичным реверсированием битов (PBRO) в памяти с новым размером N' перемежителя и считывание данных из памяти путем удаления адресов, соответствующих адресам от N до N'-1, из памяти перед перемежением. Технический результат - повышение эффективности памяти перемежителя. 5 н. и 5 з.п. ф-лы, 6 ил., 7 табл.

| US 6304991 B1, 16.10.2001 | |||

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ РАДИОВЕЩАТЕЛЬНОЙ ПЕРЕДАЧИ ЦИФРОВЫХ СООБЩЕНИЙ | 1994 |

|

RU2110148C1 |

| US 6314534 B1, 6.11.2001 | |||

| US 6198733 B1, 6.03.2001. | |||

Авторы

Даты

2006-04-20—Публикация

2003-01-09—Подача