Устройство для сортировки двумерного массива данных принадлежит к области вычислительной техники, а именно к устройствам обработки числовых массивов информации, и предназначено для перестановки строк и столбцов двумерного массива данных, представленного в виде матрицы и хранящегося в памяти вычислительного устройства.

Известно "Устройство для исследования сетей Петри" по патенту РФ №2024057, предназначенное для сортировки данных и содержащее блок управления, регистр начальной маркировки, формирователь пачек импульсов, блок задания топологии графа, элементы ИЛИ, формирователь одиночного импульса с временной задержкой, две группы элементов И, дешифратор, схему сравнения, блок памяти, элементы задержки. Блок памяти является общим для аналога и заявляемого изобретения.

Наиболее близким по технической сущности и достигаемому результату к заявляемому изобретению является "Устройство для перебора перестановок" по патенту РФ №2012054, предназначенное для формирования в произвольной последовательности перестановок, и может быть использовано для решения комбинаторных задач. Устройство содержит два дешифратора, два мультипликатора, два элемента ИЛИ, группу из n сумматоров, блоков деления, две группы из n регистров, три группы элементов задержки и группу элементов И. Общими признаками для аналога и предлагаемого технического решения являются две группы из n регистров. Недостатком данного устройства является то, что объектом перестановок является одномерный массив данных.

Устройство предназначено для решения следующей задачи.

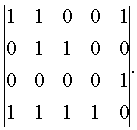

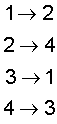

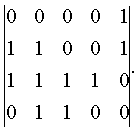

В матрице регистров первой памяти записана информация. Задача изобретения заключается в том, чтобы осуществить заданную перестановку строк и/или столбцов матрицы. Например, поменять местами строки следующей бинарной матрицы

Если осуществить следующую перестановку для строк:

то получится преобразованная матрица:

Для каждой строки матрицы, при том что матрица является двумерным массивом данных, записанном в регистрах первой памяти, внешним воздействием задается соответствующий новый номер. Характер воздействия может быть различным, например, могут поступать соответствующие сигналы от внешнего устройства, сопрягаемого с заявляемым, или задаваться пользователем (оператором) путем нажатия кнопок или переключателей. Блок кнопок или переключателей, по сути, также является внешним устройством для заявленного изобретения. Другим внешним устройством может быть логическое устройство (вычислительное устройство, электронное цифровое устройство), формирующее сигналы управления перестановкой строк по какому-либо правилу.

Может требоваться сортировка как строк, так и столбцов. При этом аналогично можно сортировать столбцы, если расположить заданный массив, поменяв местами строки со столбцами при начальной процедуре записи информации в первую память. Поэтому в дальнейшем, говоря о строках, будем подразумевать, что на их месте могут быть столбцы, и соответственно тогда вместо столбцов следует подразумевать строки. Для памяти вычислительного устройства или любого электронного устройства понятие строки и столбца применительно к хранимому двумерному массиву является относительным, поэтому при описании состава устройства использовано понятие множества. Соответствующие множества могут быть соотнесены со строками или столбцами, что используется для большей наглядности.

Настоящее устройство может быть выполнено в виде микросхемы или входить в микросхему в составе вычислительного устройства и предназначаться для технической реализации алгоритма сортировки двумерного массива данных, в частности реляционной базы данных или обработки числовой матрицы при решении уравнений с помощью технических (автоматических) средств обработки информации.

Устройство для сортировки двумерного массива данных содержит блок регистров первой памяти, блок регистров второй памяти, коммутатор, соединенный первыми входами с соответствующими выходами блока регистров первой памяти; выходами с соответствующими входами блока регистров второй памяти; на вторые входы коммутатора поданы сигналы управления коммутацией блоков регистров первой и второй памяти между собой, которые являются управляющими входами устройства для сортировки двумерного массива данных; на входы блока регистров первой памяти и третий вход коммутатора поданы синхросигналы (сдвиговые импульсы).

Блок регистров первой памяти содержит mn первых ячеек хранения данных, представляющих собой первые единичные сдвиговые регистры хранения одной единицы информации; каждая из ячеек принадлежит одному из m первых непересекающихся множеств, содержащих по n этих ячеек и символизирующих одну (один) из m строк (столбцов) двумерного массива данных, и одновременно принадлежит одному из n вторых непересекающихся множеств, содержащих по m этих ячеек и символизирующих один (одну) из n столбцов (строк) двумерного массива данных; в каждом из m первых непересекающихся множеств n первых единичных сдвиговых регистров образуют один из m первый n-ячеечный сдвиговый регистр путем соединения сдвиговых выходов i-го единичного сдвигового регистра с соответствующими сдвиговыми входами i+1-го единичного сдвигового регистра; сдвиговый вход 1-го единичного сдвигового регистра в каждом из m первых n-ячеечных сдвиговых регистров является входом для синхросигналов (сдвиговых импульсов); выход состояния n-го единичного сдвигового регистра в каждом из m первых n-ячеечных сдвиговых регистров является одним из m выходов блока регистров первой памяти и соединен с соответствующим одним из m первых входов коммутатора.

В каждом, одном из m, первом n-ячеечном сдвиговом регистре первые единичные сдвиговые регистры соединены между собой таким образом, что третий выход i-го единичного сдвигового регистра соединен с первым входом i+1-го единичного сдвигового регистра для передачи от i-го регистра к i+1-му логического нуля; четвертый выход i-го единичного сдвигового регистра соединен со вторым входом i+1-го единичного сдвигового регистра для передачи от i-го регистра к i+1-му логической единицы; первый вход 1-го единичного сдвигового регистра в каждом из m первых n-ячеечных сдвиговых регистров является входом данного первого n-ячеечного сдвигового регистра и одним из m входов устройства для сортировки двумерного массива данных для подачи синхросигналов (сдвиговых импульсов).

Блок регистров второй памяти содержит mn вторых ячеек хранения данных, представляющих собой вторые единичные сдвиговые регистры хранения одной единицы информации; каждая из ячеек принадлежит одному из m третьих непересекающихся множеств, содержащих по n этих ячеек и символизирующих одну (один) из m строк (столбцов) двумерного массива данных, и одновременно принадлежит одному из n четвертых непересекающихся множеств, содержащих по m этих ячеек и символизирующих один (одну) из n столбцов (строк) двумерного массива данных; в каждом из m третьих непересекающихся множеств n единичных сдвиговых регистров образуют один из m второй n-ячеечный сдвиговый регистр путем соединения сдвиговых выходов i-го единичного сдвигового регистра с соответствующими сдвиговыми входами i+1-го единичного сдвигового регистра; сдвиговые входы 1-го единичного сдвигового регистра в каждом из m вторых n-ячеечных сдвиговых регистров соединены с соответствующими выходами коммутатора.

В каждом втором n-ячеечном сдвиговом регистре вторые единичные сдвиговые регистры соединены между собой таким образом, что третий выход i-го единичного сдвигового регистра соединен с первым входом i+1-го единичного сдвигового регистра для передачи от i-го регистра к i+1-му логического нуля, четвертый выход i-го единичного сдвигового регистра соединен со вторым входом i+1-го единичного сдвигового регистра для передачи от i-го регистра к i+1-му логической единицы; первый вход 1-го единичного сдвигового регистра в каждом из m вторых n-ячеечных сдвиговых регистров является входом данного второго n-ячеечного сдвигового регистра для передачи логического нуля и является нулевым входом соответствующей одной из m пар входов блока регистров второй памяти; второй вход 1-го единичного сдвигового регистра в каждом из m вторых n-ячеечных сдвиговых регистров является входом данного второго n-ячеечного сдвигового регистра для передачи логической единицы и является единичным входом соответствующей одной из m пар входов блока регистров второй памяти.

Блоки регистров первой и второй памяти являются практически одинаковы и отличаются только соединениями своих входов и выходов.

Ниже приведено описание двух возможных вариантов выполнения коммутатора.

Вариант 1. Коммутатор содержит m первых логических конъюнкторов (элементов И), вторые входы которых являются первыми m входами коммутатора и соединены с соответствующими m выходами блока регистров первой памяти; первый логический дизъюнктор (элемент ИЛИ), каждый из m входов которого соединен с выходом соответствующего одного из m первых конъюнкторов, а выход соединен со вторыми входами m вторых логических конъюнкторов (элементов И), на первый вход каждого из которых, являющийся одним из m первых из 2m вторых входов коммутатора и одновременно одним из управляющих входов устройства для сортировки двумерного массива данных для управления коммутацией сдвиговых регистров блоков регистров первой и второй памяти между собой, подан соответствующий один из m первых управляющих сигналов; первые входы первых конъюнкторов являются вторыми из вторых входов коммутатора, на каждый из которых подается один из m вторых управляющих сигналов, являющихся управляющими входами устройства для сортировки двумерного массива данных; выход каждого из m вторых конъюнкторов соединен со входом соответствующего одного из m первых инверторов и с первым входом соответствующего одного из m третьих конъюнкторов, вторые входы которых соединены вместе и являются третьим входом коммутатора для подачи внешних синхросигналов (сдвиговых импульсов); выход каждого первого инвертора соединен с первым входом соответствующего, одного из m, четвертого конъюнктора, второй вход каждого из которых соединен со вторым входом соответствующего третьего конъюнктора; третьи входы соответствующих третьих и четвертых конъюнкторов соединены между собой и с соответствующими первыми входами вторых конъюнкторов; выходы соответствующих третьих и четвертых конъюнкторов образуют m пар выходов, которые являются выходами коммутатора и соединяются с соответствующими входами блока регистров второй памяти.

Такое выполнение коммутатора позволяет переносить информацию построчно (по столбцам) из одной памяти в другую. Ниже приведен вариант выполнения коммутатора, который позволяет переносить информацию из одной памяти в другую одновременно по всем строкам (столбцам), что сокращает время работы устройства, но усложняет его конструкцию.

Вариант 2. Коммутатор содержит m пятых логических конъюнкторов (элементов И), каждый из которых принадлежит одному из m пятых непересекающихся множеств, содержащих по m элементов И и символизирующих одну (один) из m строк (столбцов) двумерной матрицы, и одновременно принадлежит одному из m шестых непересекающихся множеств, содержащих по m элементов И и символизирующих один (одну) из m столбцов (строк) двумерной матрицы; на первый вход каждого пятого элемента И подан соответствующий один из m2 управляющих сигналов, являющихся вторыми входами коммутатора и одновременно управляющими входами устройства для сортировки двумерного массива данных для управления коммутацией блоков регистров первой и второй памяти между собой; вторые входы пятых элементов И, образующих один (одну) столбец (строку), т.е. принадлежащих одному из m шестых непересекающихся множеств, соединены вместе и соединены с соответствующим выходом, одним из m, блока регистров первой памяти и являются m первыми входами коммутатора; выходы каждого из m пятых элементов И, образующих строку (столбец), соединены с соответствующими m входами соответствующего второго логического дизъюнктора, одного из m; выход каждого из m вторых дизъюнкторов соединен со входом соответствующего одного из m вторых инверторов и с первым входом соответствующего одного из m шестых конъюнкторов, вторые входы которых соединены вместе и являются третьим входом коммутатора для подачи внешних синхросигналов (сдвиговых импульсов); выход каждого второго инвертора соединен с первым входом соответствующего, одного из m, седьмого конъюнктора, второй вход каждого из которых соединен со вторым входом соответствующего шестого конъюнктора; выходы соответствующих шестых и седьмых конъюнкторов образуют m пар выходов, которые являются выходами коммутатора и соединяются с соответствующими входами блока регистров второй памяти.

Написание слов в скобках означает, что эти слова можно употреблять вместо соответствующих предыдущих слов, например "столбцов" вместо "строк".

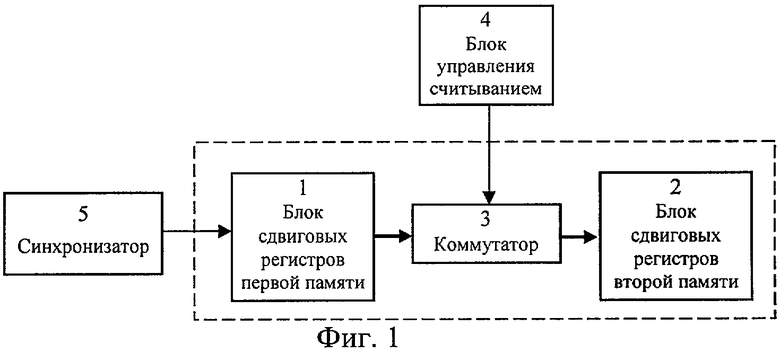

На фиг.1 представлена структурная схема устройства, здесь 1 - блок сдвиговых регистров первый памяти, 2 - блок сдвиговых регистров второй памяти, 3 - коммутатор, 4 - блок управления считыванием, 5 - синхронизатор. В прямоугольнике, очерченном пунктиром, расположены блоки заявленного изобретения, синхронизатор и блок управления считыванием являются внешними устройствами.

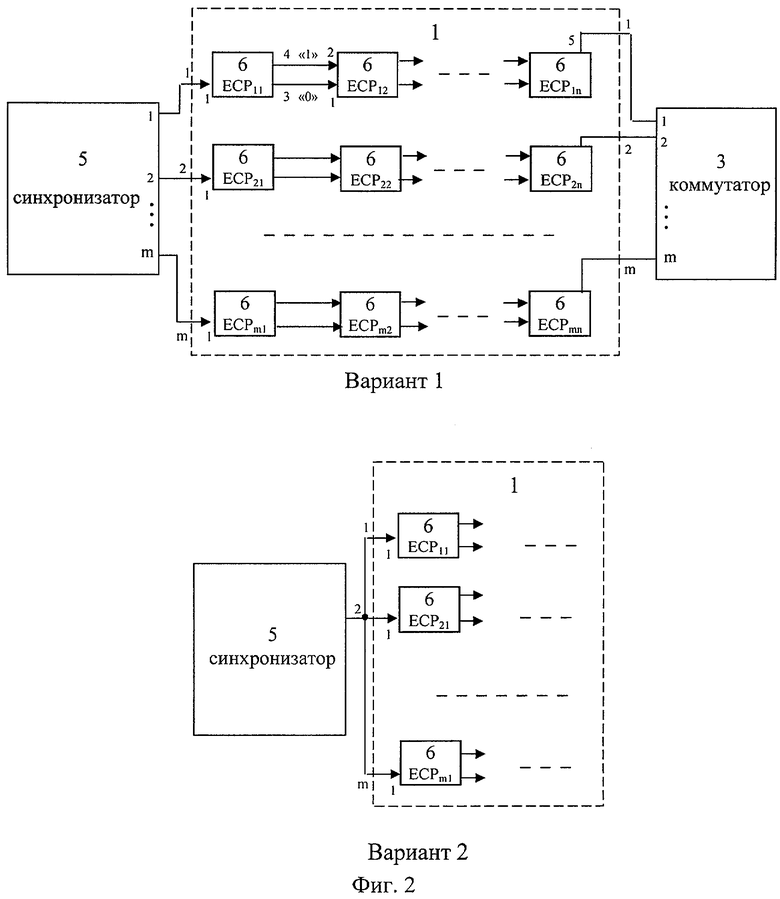

На фиг.2 изображены два варианта функциональной схемы блока регистров первой памяти 1. Здесь 6 - первые единичные сдвиговые регистры. Варианты различаются способом соединения входов блока 1 с синхронизатором 5. В первом варианте каждый из m входов блока 1 соединен с одним из m выходов блока 5. Во втором варианте все входы блока 1 соединены вместе и подключены к единственному выходу блока 5.

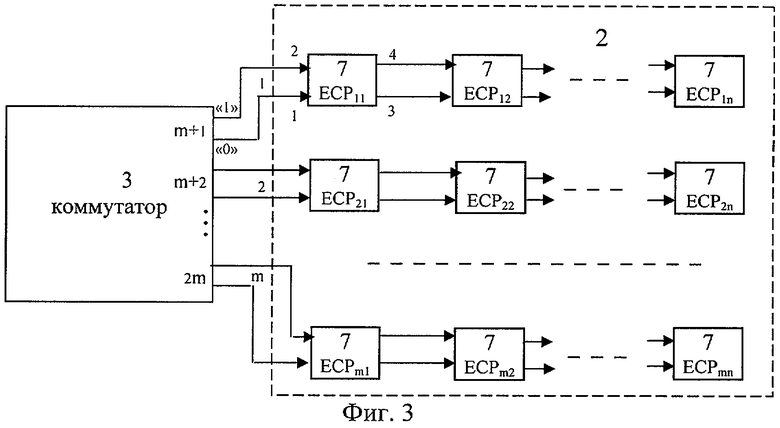

На фиг.3 представлена схема блока регистров второй памяти 2. Здесь 7 - вторые единичные сдвиговые регистры.

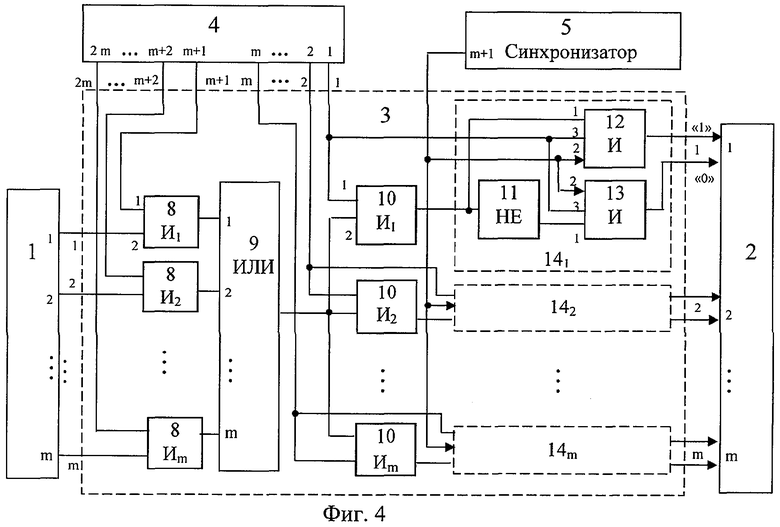

На фиг.4 представлен вариант функциональной схемы коммутатора 3, который далее будет называться первым (или вариант 1). Здесь 8 - первые логические конъюнкторы, их m штук, первые входы их являются вторыми из вторых управляющих входов коммутатора; 9 - первый m-входовый элемент ИЛИ (логический дизъюнктор); 10 - вторые элементы И (логические конъюнкторы), их m штук, первые входы в них являются управляющими или первыми вторыми входами коммутатора; 11 - первый элемент НЕ (логический инвертор); 12 и 13 - соответственно третий и четвертый элементы И. Элементы 11, 12 и 13 объединены в субблок 14, что обозначено пунктиром. Таких субблоков 14 в схеме m штук. Также показан синхронизатор 5, блок управления считыванием 4 и блоки регистров первой 1 и второй 2 памяти.

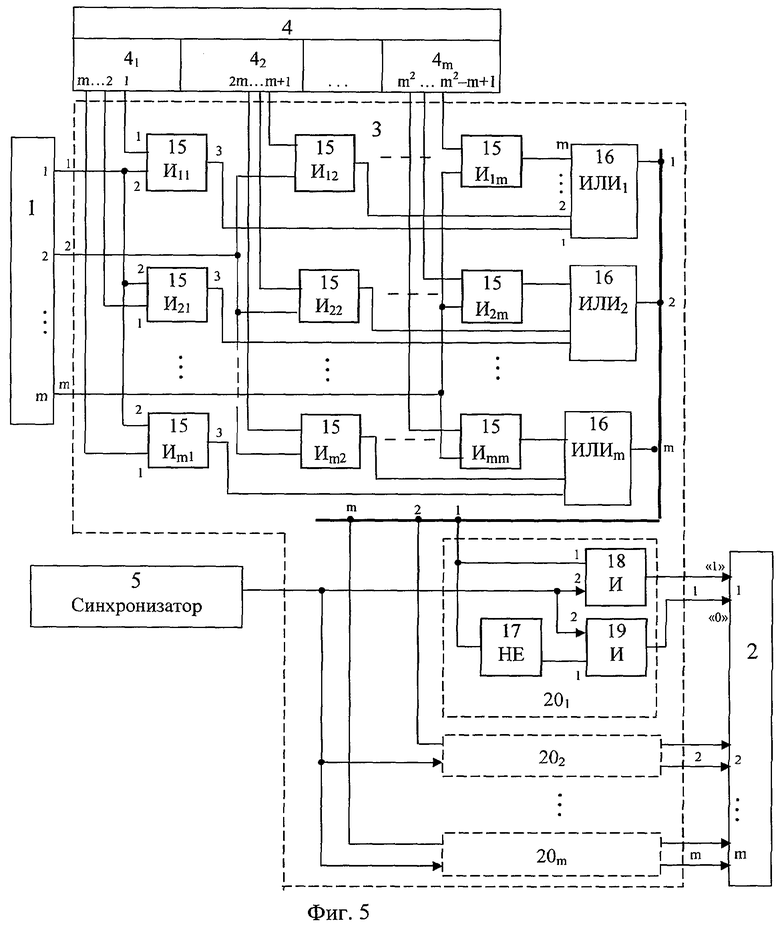

На фиг.5 показан второй вариант (или вариант 2) функциональной схемы коммутатора 3. Здесь 15 - пятые элементы И, их m2 штук, первые входы в них являются управляющими; 16 - вторые m-входовые элементы ИЛИ, всего их m штук; 17 - второй инвертор; 18 и 19 - соответственно шестой и седьмой элементы И. Элементы 17, 18 и 19 объединены в субблок 20. Таких субблоков в схеме m штук. Также показан синхронизатор 5, блок управления считыванием 4 и блоки регистров первой 1 и второй 2 памяти. Блок 4 может состоять из m одинаковых субблоков, управляющих одним соответствующим столбцом элементов 15, поэтому прямоугольник, обозначающий на чертеже блок 4, содержит внутри себя прямоугольники, соответствующие субблокам, входящим в состав блока 4. При этом показанная нумерация выходов блока 4 является общей для блока 4, а к каждому из субблоков относятся соответствующие выходы. Нумерация управляющих входов блока 3, соединенных с выходами блока 4, на фиг.5 не показана, но она полностью соответствует нумерации выходов блока 4. Жирная линия символизирует общую шину для соединения выходов элементов 16 и входов субблоков 20 (входов элементов 17 и 18) в этой шине m соединений.

"1" и "0" на фиг.2-5 обозначают цепи сдвига соответственно логического нуля и логической единицы в сдвиговом регистре. В изображениях пунктир символизирует не отображенные элементы и блоки, аналогично многоточие обозначает не показанные на чертежах входы и выходы. Нумерация входов и выходов у всех аналогичных элементов и блоков одинакова и соответствует тем обозначениям, которые показаны на примере отдельных элементов и блоков.

На фиг.3-5 у коммутатора и блока регистров второй памяти пронумерованы пары соответственно выходов и входов, а не сами соответствующие выходы и входы. Это объясняется тем, что именно пара соединений несет функциональную нагрузку, и в зависимости от значения передаваемого сигнала, логический ноль и единица, активизируется тот или другой канал в паре. В дальнейшем иногда вместо пары будет упоминаться соответственно вход или выход, когда речь будет идти о логике работы устройства в целом, без конкретизации значения передаваемого в данный момент сигнала.

На фиг.1-5 все блоки имеют входы слева, а выходы справа, за исключением блоков 4 и 5, которые имеют только выходы. Там, где имеется один вход и/или один выход, то соответственно вход и/или выход не нумеруется, например у инверторов 10 на фиг.4 не нумерованы выходы, так как у каждого из элементов 10 их по одному. Нижний индекс в названии блоков указывает на порядковый номер соответствующего блока или элемента в группе идентичных по конструкции и функциональному назначению в заявляемом устройстве элементов (блоков).

Простыми линиями на фиг.2-5 показаны соединения между элементами, передающие потенциальные сигналы, которые могут соответствовать определенным значениям электрических напряжений, присутствие такого сигнала на входе элемента поддерживает состояние последнего, соответствующего этому сигналу. Стрелки обозначают соединения, по которым передаются короткие импульсы, срабатывание элемента-приемника такого сигнала происходит по переднему фронту входного для него импульса.

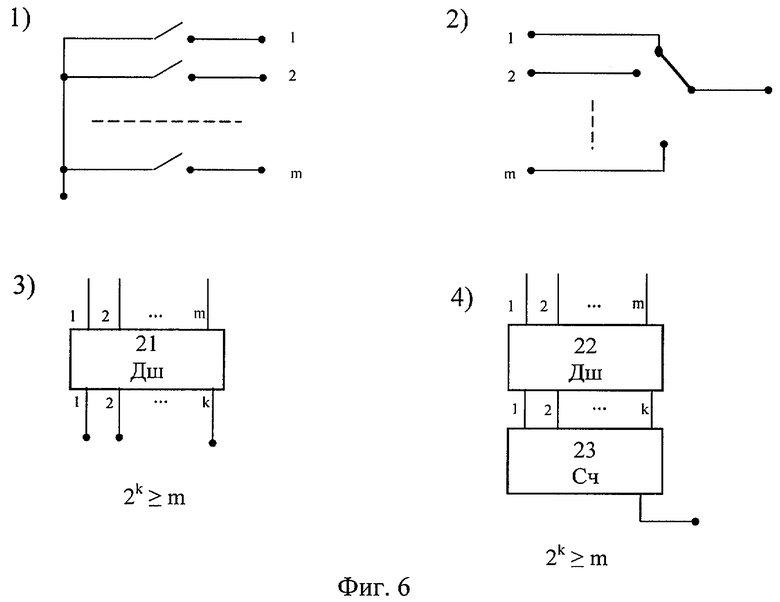

На фиг.6 показаны четыре различных возможных варианта выполнения дешифратора номера строки (столбца), входящего в состав блока 4.

Принцип работы заявленного технического решения заключается в том, что при подаче управляющих сигналов на коммутатор последний соединяет i-тую строку первой памяти с j-той строкой второй памяти. При этом осуществляется соединение строк по правилу один к одному, т.е. одна строка первой памяти может быть соединена только с одной строкой второй памяти и наоборот. Некоторые строки могут остаться и не скоммутированными, в этом случае информация из некоторой k-той строки первой памяти не будет перезаписана во вторую память, и некоторая строка t второй памяти останется пустой (нулевой) или просто неизмененной, в ней останется исходная информация, если она там была.

При подаче сдвиговых импульсов от внешнего устройства (синхронизатора 5) на вход блока 1 информация из сдвиговых регистров, соответствующих строкам массива в первой памяти (блок 1), начнет перезаписываться в сдвиговые регистры второй памяти, соответствующие строкам во второй памяти (блок 2). Осуществляется это следующим образом. Один сдвиговый (тактовый) импульс передвигает всю информацию в сдвиговом регистре, составленном из последовательности единичных сдвиговых регистров, на одну позицию. Первый импульс, таким образом, выталкивает информацию из последней ячейки сдвигового регистра одной строки на выход данного регистра. Задача коммутатора заключается в том, чтобы обеспечить подачу этой информации на вход соответствующего сдвигового регистра, т.е. требуемой строки, во второй памяти. В результате значение из последней ячейки строки в блоке 1 перезаписывается в первую ячейку соответствующей строки блока 2. Второй сдвиговый импульс продвигает всю информацию еще на одну позицию и т.д. Всего одна пачка синхроимпульсов должна содержать n сдвиговых импульсов, т.е. столько, сколько имеется ячеек в одном сдвиговом регистре, соответствующем одной строке массива.

Варианты конструкции коммутатора позволяют выполнить два разных алгоритма перезаписи строк из первой памяти во вторую.

Первый вариант предусматривает построчную перезапись. В этом случае от синхронизатора подается поочередно m пачек по n сдвиговых импульсов (синхроимпульсов) на каждую из m строк исходного массива по порядку, начиная с первой. Синхронно с началом каждой пачки импульсов на соответствующий управляющий второй вход коммутатора подается сигнал с соответствующего выхода блока 4. При этом вторые m управляющих сигналов задают номера строк с 1 по m в порядке возрастания, указывая, какая строка в данный момент перезаписывается в новую позицию, а первые m управляющих сигналов задают новые номера строк. Номер каждого из m первых управляющих сигналов соответствует номеру строки второй памяти, в которую необходимо перезаписать строку первой памяти, на которую в данный момент подана пачка синхроимпульсов. Соединение в этом случае блоков 5 и 1 показано на фиг.2 как вариант 1.

В каждый момент должен появляться только один первый управляющий сигнал и только один второй управляющий сигнал, при этом их совместное действие должно осуществляться на интервале, не меньшем длительности одной пачки синхроимпульсов и не большем периода следования этих пачек. Это необходимо для того, чтобы одна строка первой памяти могла полностью перезаписаться только в одну строку второй памяти.

Подача пачки синхроимпульсов на вход коммутатора для подачи синхросигналов и одновременная подача первого управляющего сигнала на j-тый первый управляющий вход коммутатора и второго управляющего сигнала на i-тый второй управляющий вход коммутатора приводит к перезаписи i-той строки первой памяти в j-тую строку второй памяти.

После перезаписи одной строки осуществляется перезапись следующей строки.

Такая реализация устройства делает его более простым, но увеличивает время работы, так как для перестановки строк исходного массива требуется время для подачи m пачек по n синхроимпульсов в каждой.

Другой вариант предусматривает подачу пачек синхроимпульсов одновременно на m входов первой памяти. В этом случае блок 4 подает на управляющие вторые входы коммутатора m2 управляющих сигналов, с помощью которых коммутатор перераспределяет потоки информации между строками первой и второй памяти. Соединение в этом случае блоков 5 и 1 показано на фиг.2 как вариант 2. В этом случае конструкция коммутатора оказывается сложней, но время работы устройства сокращается в m раз по сравнению с первым вариантом.

Первый вариант аналогичен сетевой технологии с общей шиной, когда пары абонентов, в роли которых выступают строки блоков памяти, коммутируются последовательно. Второй вариант аналогичен сетевой технологии, при которой происходит соединение абонентов по правилу точка-точка, когда одновременно происходит образование m пар абонентов.

Следует отметить, что блок 4 и синхронизатор 5 могут быть совмещены в одном устройстве, или блок 4 может управляться блоком 5, который будет синхронизировать выработку управляющих сигналов, подаваемых на блок 3, в блоке 4.

Единичные сдвиговые регистры (ЕСР) 6 и 7 по своей конструкции и логике работы являются совершенно идентичными. Они имеют два сдвиговых входа 1 и 2, также два сдвиговых выхода 3 и 4. Пара 1-3 служит для передачи от одного ЕСР к следующему логического нуля, пара 2-4 служит для передачи от одного ЕСР к следующему логической единицы. Изначально каждый регистр устанавливается в состояние, соответствующее логическому нулю или единице. Осуществляется это через отдельные установочные входы, которые не показаны на чертежах. Эти входы могут служить для начальной записи исходного массива в первую память. В зависимости от того, в каком состоянии в данный момент находится данный ЕСР, на выходе, названном выходом состояния, появляется значение логического нуля или логической единицы. На фиг.2 это выход 5 у блока 6, соответствующего ЕСР1n. Ниже представлена таблица истинности (функционирования) ЕСР.

В таблице в первой строке цифры обозначают номера входов и выходов согласно чертежам, Q - состояние ЕСР до поступления очередного импульса на входе 1 или 2, Q+1 - состояние ЕСР после поступления импульса на вход 1 или 2, т.е. это новое состояние ЕСР, вызванное появлением импульса на входе 1 или 2, в которое переходит ЕСР из состояния Q. Значения переменных Q и Q+1 соответствуют сигналам на выходе 5 ЕСР. Одновременное появление импульсов на входах 1 и 2 является запрещенным, ответственность за это лежит на внешних по отношению к ЕСР устройствах. В других строках таблицы, кроме первой, указаны значения логических сигналов на входах и выходах ЕСР. Появление импульса на входах 1-4 обозначено единицей, отсутствие импульсов - прочерком. Появление импульса на входе 1 или 2 вызывает в зависимости от состояния ЕСР появление импульса на выходе 3 или 4. Так как выходы 3 и 4 одного ЕСР связаны со входами 1 и 2 соответственно другого ЕСР, происходит сдвиг информации из первого ЕСР во второй. Потенциальный сигнал на выходе 5 ЕСР может соответствовать некоторому значению электрического напряжения. Он поддерживается на выходе 5 так долго, как долго данный ЕСР находится в соответствующем состоянии. Сигналы на входах 1 и 2, а также выходах 3 и 4 ЕСР являются короткими импульсами и вызывают срабатывание соответствующего элемента, на вход которого подаются, по их переднему фронту.

У блоков 6 ЕСРi1 в блоке 1 (фиг.2) импульсы поданы только на входы 1. Считаем, что в исходном состоянии ЕСР, когда в него не записана никакая информация, на его выходе 5 присутствует потенциал, соответствующий логическому нулю. Запись информации означает перевод некоторых ЕСР в единичное состояние, тогда как другие останутся в нулевом состоянии. В результате в сдвиговом регистре, составленном из ЕСР, будет записана некоторая комбинация из нулей и единиц. Ее-то и нужно будет переместить по регистру на выход. Импульсы, подаваемые на вход 1 первого ЕСР соответствующего m-го сдвигового регистра, будут продвигать данную комбинацию на выход регистра и записывать в него нули на место освобождаемых ячеек (разрядов сдвигового регистра).

Передача информации из m выходных (n-ых) ЕСР первой памяти посредством коммутатора в m 1-е ЕСР второй памяти осуществляется следующим образом. Блок 3 коммутирует выход 5 соответствующего последнего ЕСР первой памяти с соответствующей строкой, т.е. соответствующим первым ЕСР второй памяти, путем реализации логических функций, выполняемых элементами блока 3. В результате, если на выходе 5 соответствующего последнего ЕСР первой памяти находится логическая единица, то через установленную коммутацию синхроимпульс из пачки синхроимпульсов подается на вход 2 соответствующего первого ЕСР второй памяти, если на соответствующем выходе 5 ЕСР логический ноль, то синхроимпульс проходит не на второй вход, а на первый вход соответствующего первого ЕСР второй памяти. Таким образом происходит перезапись значения из соответствующего последнего ЕСР первой памяти в соответствующий первый ЕСР второй памяти. Естественно, что синхроимпульсы, подаваемые на соответствующий вход первой памяти и на соответствующий вход коммутатора для подачи на соответствующий вход второй памяти, являются синхронными, а точнее, это один и тот же импульс, так как указанные входы для подачи синхроимпульсов могут быть соединены.

Устройство работает следующим образом.

В исходном состоянии в ЕСР 6 блока 1 записаны логические нули и единицы (далее просто нули и единицы), соответствующие исходному двумерному массиву. Элементы 7 находятся в нулевом состоянии. На выходах 5 элементов 6 находятся единицы или нули. На первых входах элементов 8, 10 и 15 находятся нули, так как пока отсутствуют сигналы управления. На выходе элемента 9 - ноль. На выходах элементов 10 и 15 - нули, соответственно на выходах элементов 16 и входах элементов 11 и 17 и входах 1 элементов 12 и 18 также нули. На выходах элементов 11 и 17 находятся единицы, и соответственно на входах 1 элементов 13 и 19 находятся единицы. В отсутствие синхроимпульсов и управляющих сигналов на выходах элементов 12, 13, 18 и 19 - нули и синхросигналы на входы 1 и 2 элементов 7 не попадают. Состояние блока 2 остается неизменным.

Далее работа устройства будет рассмотрена раздельно для двух вариантов его исполнения.

Вариант 1.

При подаче первого управляющего сигнала с i-го выхода блока 4, который является одним из первых m выходов блока 4, на вход 1 i-го элемента 10 Иi последний становится прозрачным для прохождения сигнала единицы через один из элементов 8 и элемент 9 от блока 1. Второй управляющий сигнал с m+1-го выхода блока 4 подается на вход 1 элемента 8 И1, который становится прозрачным для передачи единицы на свой выход от элемента 6 ECP1n из блока 1. Другие элементы 10 и 8 заперты, на их выходах сохраняется значение 0. Если в элементе 6 ECP1n записана 1, то она попадет через элементы 8 И1, 9 и 10 Иi на вход инвертора 11 в субблоке 14i. Эта же единица будет подана на вход 1 блока 12 субблока 14i. С выхода элемента 11 на первый вход элемента 13 будет подан 0, т.е. сигнал, противоположный сигналу на первом входе элемента 12. Сигнал единицы будет подан также на входы 3 соответствующих элементов 12 и 13 субблока 14i с i-го выхода блока 4, который является одним из первых m выходов блока 4.

При подаче первого синхроимпульса первой пачки с выхода m+1 блока 5 на входы 2 элементов 12 и 13 субблока 14i этот импульс пройдет на выход либо элемента 12, либо элемента 13 субблока 14i, в результате будет подан импульс на вход 1 или 2 элемента 7 ЕСРi1 блока 2, т.е. в первую ячейку i-ой строки блока 2 будет записана 1 или 0.

Одновременно с синхроимпульсом с выхода m+1 блока 5 будет попадан синхроимпульс первой пачки на вход 1 элемента 6 ЕСР11. В результате этого произойдет движение информации по первой строке блока 1. Каждый элемент 6 ЕСР1i+1 перейдет в состояние, в котором до подачи этого импульса находился элемент 6 ЕСР1i. Первый элемент перейдет в нулевое состояние. Движение информации по сдвиговому регистру будет вызывать изменение сигнала на выходе 5 элемента 6 ECP1n. Последовательность значений этих сигналов будет соответствовать комбинации, записанной первоначально в первой строке массива. В зависимости от сигналов на выходе 5 элемента 6 ECP1n будут меняться значения сигналов на входах элементов 11 и 12 субблока 14i, и соответственно будет появляться импульс то выходе элемента 12, то на выходе элемента 13, и в элемент 7 ЕСРi1 будет записываться то 0, то 1. При этом предыдущее значение в ячейке 7 ЕСРi1 будет передвигаться в ячейку 7 ЕСРi2, а из нее в ячейку 7 ЕСРi3 и т.д.

После прохождения n синхроимпульсов первой пачки первая строка исходного массива окажется переписанной в 1-ю строку второй памяти.

Далее начинается следующий цикл для второй строки. Появляется 1 на первом входе элемента 8 И2 и управляющий сигнал на выходе j блока 4, j≠i. Всего таких циклов m. С выхода m+1 блока 5 всего подается mn импульсов сдвига, каждая порция по n импульсов появляется синхронно с одной из пачек на выходах с 1 по m.

Вариант 2.

Элементы 15 образуют квадратную матрицу размера m. В исходном состоянии сигналы с выходов блока 4 отсутствуют, значит, на выходах всех блоков 15 и 16 находятся нули. Синхроимпульсы с выхода блока 5 также не подаются, поэтому на выходах всех элементов 18 и 19 импульсов нет.

Логика работы устройства требует того, чтобы на выходах блока 4 сигналы управления появлялись таким образом, чтобы в каждом столбце элементов 15 единица на входе 1 появлялась только у одного элемента 15 из данного столбца и в каждой строке только у одного элемента из данной строки. Выход каждого элемента 6 ЕСРin соединен со всеми вторыми входами элементов 15 из 1-го столбца. Появление, например, 1 на первом входе элемента 15 И21 приведет к тому, что его выход будет повторять значение выхода 1 блока 1 и через элемент 16 ИЛИ2 и элемент 17 субблока 202 будет переключать последовательность синхроимпульсов между выходами элементов 18 и 19 субблока 202 в зависимости от изменения состояния выхода 1 блока 1. Таким образом информация из первой строки блока 1 будет продвигаться во вторую строку блока 2. Аналогичная картина будет повторяться на других выходах субблоков 20 и соответственно на входах блока 2. Вся процедура произойдет за n тактов. В данном варианте блок 5 должен выдать n сдвиговых импульсов. Эти синхроимпульсы одновременно подаются как на вход блока 4, так и на входы блока 1 с одного и того же выхода блока 5.

Устройство для сортировки двумерного массива данных выполняется из электронных дискретных элементов, выполняющих логические функции. ЕСР 6 и 7 представляют собой логические электронные элементы на базе триггера, предназначенные для хранения логического нуля или единицы. Они способны сохранять свое состояние при отсутствии входных сигналов. Изменение их состояния с нуля на единицу и наоборот происходит по переднему фронту подаваемого сигнала, поэтому они могут управляться короткими импульсами.

Сигналы на входах и выходах элементов должны иметь длительность достаточную для обеспечения переключения всех элементов в заданной цепи, т.е. превышать суммарное время переходных процессов всех элементов, которые должны поменять свое состояние в данном такте. Соответствующей должна быть и длительность тактовых (сдвиговых) импульсов или синхросигналов.

Элементы И, ИЛИ и НЕ могут быть выполнены из элементов Пирса и/или Шеффера.

Блок 4 в варианте 1 может иметь в своем составе 2 различных дешифратора номера строки, выполненных в одном из вариантов, как показано на фиг.6. Выходы одного дешифратора соответствуют первым m выходам блока 4, а выходы второго - выходам с m+1 по 2m.

Блок 4 в варианте 2 может иметь в своем составе либо дешифратор, выполненный в вариантах 1 или 2 согласно фиг.6, при этом число выходов равно не m, как показано на чертеже, а m2, или представлять собой логическое устройство, формирующее соответствующую комбинацию из m2 разрядов.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОРТИРОВКИ ДВУМЕРНОГО МАССИВА ДАННЫХ (ВАРИАНТЫ) | 2003 |

|

RU2252447C2 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СКОЛЬЗЯЩЕГО СРЕДНЕГО ЗНАЧЕНИЯ | 1990 |

|

RU2015552C1 |

| УСТРОЙСТВО СИГНАЛИЗАЦИИ | 2007 |

|

RU2335030C1 |

| СИСТЕМА ДЛЯ СЖАТИЯ ДВУХМЕРНОГО МАССИВА ИНФОРМАЦИИ | 1993 |

|

RU2046398C1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Однокристальный микропроцессор | 1978 |

|

SU734695A1 |

| Устройство параллельной обработки видеоинформации | 1989 |

|

SU1651299A1 |

| Устройство для определения текущей медианы | 1985 |

|

SU1322314A1 |

| Устройство для экстремальной фильтрации | 1988 |

|

SU1536371A1 |

| Устройство для экстремальной фильтрации | 1987 |

|

SU1425651A1 |

Изобретение относится к области вычислительной техники, а именно к устройствам обработки числовых массивов информации, и предназначено для перестановки строк двумерного массива (матрицы), хранящейся в памяти вычислительного устройства. Техническим результатом является осуществление заданной перестановки строк и/или столбцов двумерного массива. Устройство содержит матрицу единичных регистров первой памяти и матрицу единичных регистров второй памяти, которые идентичны друг другу. Между ними расположен коммутатор. Единичные регистры памяти, расположенные условно в одной строке, соединены между собой в сдвиговые строчные регистры. Коммутатор по заданному извне закону соединяет выход сдвигового регистра первой памяти, соответствующего i-ой строке, с входом сдвигового регистра второй памяти, соответствующего j-ой строке во второй памяти. После подачи пачки сдвиговых импульсов на сдвиговый вход i-ого сдвигового регистра первой памяти информация из него переместиться в j-ый сдвиговый регистр второй памяти. Таким образом, произойдет перенос i-ой строки на j-oe место в новом массиве. Перенос строк может осуществляться либо построчно, либо одновременно для всех, при этом конструкция коммутатора будет различной. Данное устройство аналогично может быть использовано для сортировки столбцов. 6 з.п. ф-лы, 6 ил., 1 табл.

| Устройство для сортировки чисел | 1990 |

|

SU1835543A1 |

| Устройство для сортировки разрядных чисел | 1976 |

|

SU637810A1 |

| Устройство для механизации обмена вагонеток | 1959 |

|

SU126240A1 |

| Устройство для сортировки чисел | 1990 |

|

SU1781680A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕБОРА ПЕРЕСТАНОВОК | 1991 |

|

RU2012054C1 |

| US 5440734 A, 08.08.1995 | |||

| US 5084815 A, 28.01.1992. | |||

Авторы

Даты

2006-06-27—Публикация

2004-11-04—Подача