1

Изобретение относится к автоматике и вычисли.тельной технике и предназначено для реализации проблемноориентированных и специализированных электронных вычислительных машин.

Известен микропроцессор, содержащий арифметико-логический блок, блок управления, блок регистров, магистраль данных адреса, блок ввода-вывода, шины информационные, шины адресные и шины управлеления 1.

Недостаток этого микропроцессора - вычислительная мош.ность в однопроцессорном варианте и сложность организации многомикропроцессорной системы, большая номенклатура дополнительных больших интегральных схем (БИС) для построения функционально-законченного вычислительного средства.

Наиболее близким к изобретению является однокристальный микропроцессор, содержаший блок ввода-вывода, блок памяти, коммутатор, дешифратор строк, дешифратор столбцов, регистр адреса, регистр кода операции, арифметико-логический блок, блок управления, причем входы блока.ввода-вывода являются входами микропроцессора.

выходы группы блока ввода-вывода являются выходами микропроцессора, информационный выход блока ввода-вывода соединен с первыми входами коммутатора, арифметико-логического блока и регистра кода операции, а управляющий выход блока ввода-вывода соединен с первым входом блока управления, второй вход которого соединен с выходом регистра кода операций, а выход блока управления соединен со вторыми входами коммутатора и арифметико-логического блока, первая и вторая группы выходов регистра адреса соединены с группами входов соответственно дешифратора строк и дешифратора столбцов, а группа входов регистра адреса соединена с первой группой выходов коммутатора, вторая группа выходов которого соединена с входами записи и считывания блока памяти 2. Кроме того, устройство содержит постоянно-запоминающее устройство, дешифраторы адреса строк и столбцов, регистры адреса строки и столб2Q ца, блок оперативных регистров.

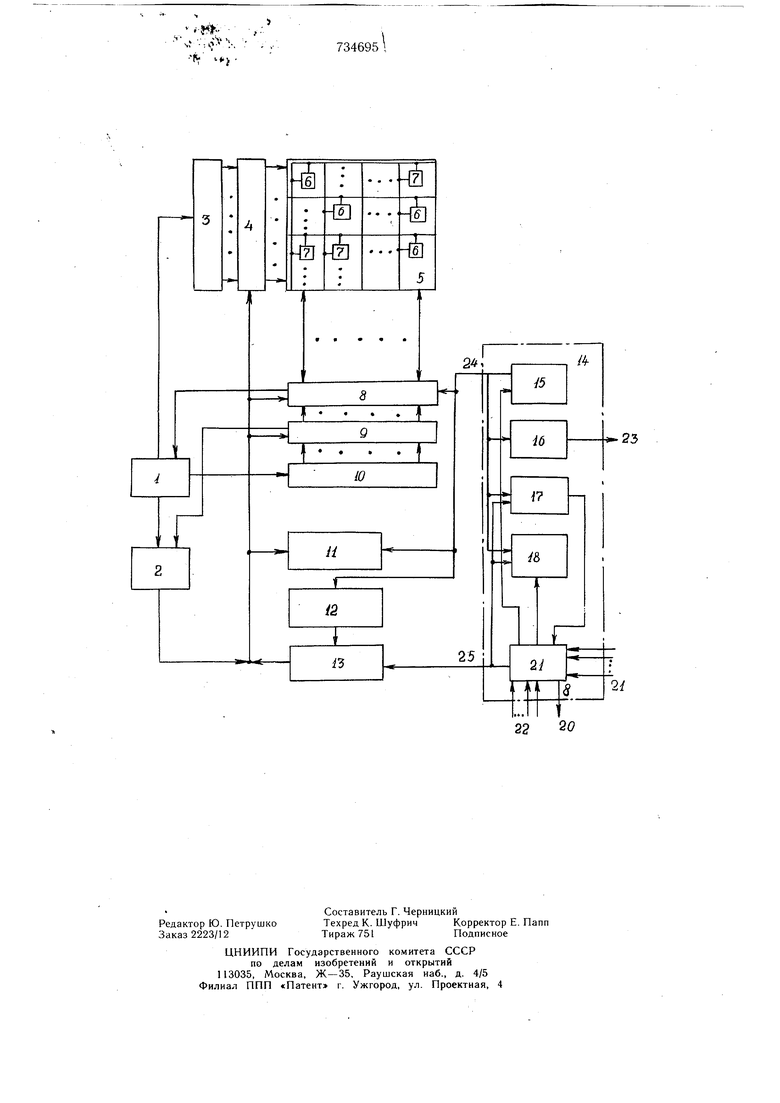

Недостаток устройства -. усложнение схем микропроцессора и наличие большой избыточности в оборудовании, что в конечном итоге снижает вычислительные возможности микропроцессора и затрудняет его размещение на одном кристалле. Цель изобретения - упрощение микропроцессора. Поставленная цель достигается тем, что он содержит схему сравнения, регистр сдвига столбцов, регистр сдвига строк, входы которого соединены с выходами дешифратора строк, а выходы подключены к входам блока памяти, входы регистра сдвига столбцов соединены с выходами дешифратора столбцов, а выходы подключены к входам группы коммутатора, управляющие входы регистра сдвига строк и регистра сдвига столбцов соединены с выходом блока управления и выходом схемы сравнения, первый вход которой соединен с выходом регистра адреса, а второй вход подключен к управляющему выходу регистра сдвига столбца. - Кроме того, блок ввода-вывода содержит регистр свертки, регистр развертки, регистр маски, схему сравнения, коммутатор, причем бходы первой группы коммутатора являются входами блока ввода-вывода, первый выход коммутатора подключен к входу регистра свертки, выход которого является информационным выходом блока ввода-вывода и соединен с информационными входами регистра развертки, регистра маски и схемы сравнения, второй выход коммутатора соединен со вторым входом схемы сравнения, третий вход которой соединен с управляющим входом регистра маски и третьим выходом коммутатора, являющимся управляющим выходом блока ввода-вывода, вход коммутатора соединен с выходом регистра маски, четвертый выход коммутатора и выход регистра развертки являются выходами группы блока ввода-вывода. При этом блок памяти содержит матрицу оперативных и постоянных ячеек памяти, причем первый вход каждой постоянной или оперативной ячейки блока памяти соединен с соответствующим входом следующей ячейки, расположенной в том же столбце, и подключен к соответствующему входу первой группы, а второй вход каждой постоянной или оперативной ячейки блока памяти соединен с соответстствующим входом следующей ячейки, расположенной в той же строке и подключен к соответствующему входу второй группы. На чертеже представлена схема предлагаемого устройства. Устройство содержит регистр 1 адреса, схему 2 сравнения, дешифратор 3 строк, регистр 4 строк, блок 5 памяти, оператИвную . ячейку 6 памяти, постоянную ячейку 7 памяти, коммутатор 8, регистр 9 сдвига столбцов, дешифратор 10 столбцов, арифметикологический блок 11, регистр 12 кода операций, блок 13 управления, блок 14 ввода-вывода, регистр 15 свертки, регистр 16 развертки, регистр 17 маски, схему 18 сравнения, коммутатор 19, первый выход группы выходов блока 20 ввода-вывода, группу входов блока 21 и 22 ввода-вывода, второй выход группы выходов блока 23 ввода-вывода, информационный выход блока 24 ввода-вывода, управляющий выход блока 25 ввода-выврда. Устройство работает следующим образом. Выполнение команд в микропроцессоре включает в себя процесс выборки п-двоичных разрядов по заданному адресу из блока 5 памяти (п-двоичных разрядов бывают либо частью программы, либо частью оперативной информации). Выборка п-двоичных разрядов осуществляется с помощью блока 9 регистра сдвига столбцов, содержащего три совмещенных сдвиговых регистра. Первый сдвиговый регистр хранит адрес столбца блока 5 памяти, соответствующий текущей команде. Второй сдвиговый регистр хранит адрес столбца считываемой из оперативной памяти информации, а третий сдвиговый регистр - записываемой. Блок 4 регистра сдвига строк также содержит три сдвиговых регистра. Их назначение аналогично назначению блока 9, только для хранения и модификации адресов строк. Для считывания п-двоичных разрядов из блока 5 памяти производится считывание информации со всех ячеек памяти в строке, адрес которой установлен на регистре 4 (на одном из сдвиговых регистров адреса строк). По шинам записи считывания содержимое оперативных и постоянных ячеек строки поступает в коммутатор 8. В коммутаторе 8 из информации всей строки выбирается п-двоичных разрядов. Адрес выбранных п-двоичных разрядов устанавливается на одном из сдвиговых регистров 9 сдвига столбцов. Для записи п-двоичных разрядов в блок 5 памяти они записываются предварительно в коммутатор 8. Затем из блока 5 памяти считывается вся строка информации, адрес которой совпадает с адресом строки записываемых п-двоичных разрядов. Затем п-двоичных разрядов подставляются в коммутатор 8 в строку информации по заданному адресу столбца и после этого информация всей строки записывается в блок 5 памяти по заданному адресу строки. Слово команды пересылки содержит код операций пересылки и адреса А1 и А2 в двоичном коде. Выполнение команды начинается со считывания кода операции в коммутатор 8, рассмотренным способом. Из коммутатора 8 код операциипересылается в регистр 12 кода операции. Здесь код операции дещифрируется и блок 13 управления вырабатывает управляющие сигналы, соответствующие этой команде. Реализация этой команды происходит следующим образом. Из блока 5 памяти выбирается следующая часть команды - адрес А1 и пересылается в регистр 1 адреса. Затем адрес А1 поступает в дешифратор 10 столбцов и в нем преобразуется в позиционный код, т. е. на вход регистра 9 столбцов поступает едийичный сигнал только по одному адресному входу. Этот сигнал записывается во втором сдвиговом регистре блока 9. Аналогично записывается адрес строки во втором сдвиговом регистре блока 4. Затем из слова команды выбирается адрес А2. Адрес А2 устанавливает третий сдвиговый регистр Э и третий сдвиговый регистр 4 аналогично адресу А1. После установления адресов строк и столбцов на соответствующих регистрах производится пересылка информации из блока 5 памяти. Для этого информация сначала считывается в коммутатор 8 по одним адресам, а затем пересылается из коммутатора в блок 5 памяти описанным способом, по другим адресам. Информация пересылается по п-двоичных разрядов до тех пор, пока не сработает схема 2 сравнения и блок 13 управления выдает соответствующие управляющие сигналы для выборки следующей команды.

Работа микропроцессора при выполнении арифметической операции, например сложение тетрад двух операндов, расположенных по адресу А1 и А2, с записью результата по адресу А2, производится следующим образом.

Слово команды при этом содержит код операции и адреса информации А1 и А2. Сначала происходит выборка команды и установление регистра сдвига строк и столбцов аналогично выполнению команды пересылки. Затем из блока 5 памяти выбирается тетрада первого операнда в коммутатор 8. Из этого блока тетрада пересылается в арифметико-логический блок 11. Затем в блок 11 аналогично пересылается тетрада второго операнда и производится сложение. Если при сложении сформировался перенос, то специальный триггер наличия переноса в арифметико-логическом блоке 11 устанавливается в «единичное состояние, в противном случае - в «нулевое.Результат сложения в блоке 11 пересылается в коммутатор 8 и затем в блок 5 памяти.

При выполнении команды передачи управления (условного перехода) осуществляется «переход в две различные точки программы в зависимости от условия - состояния триггера наличия переноса в арифметико-логическом блоке 11. Слово команды содержит код операции и адрес А1 перехода в случае «единичного состояния триггера наличия переноса. При «нулевом состоянии триггера выполняется команда, следующая за данной. Выполнение команды начинается после дешифрации кода операции команды, который записывается в регистр 12 кода операции. Затем состояние триггера наличия переноса передается в блок 13 управления. В этом блоке осуществляется анализ состояния триггера, и в зависимости от него вырабатывается та или иная последовательность управляющих сигналов. Если триггер «в единичном состоянии, то из слова команды считывается адрес перехода А1 в коммутатор 8. Адрес А1 пересылается в регистр 1 адреса. Затем этот адрес через дещифратор 10 столбцов устанавливает адрес столбца перехода в регистре 9 и через дешифратор 3 адреса строк устанавливает аа.рес Троки перехода в регистре 4. Обращение за следующей командой программы осуществляется по установленному адресу.

Если состояние триггера «нулевое, то последовательность управляющих сигналов обеспечит сдвиг адресов в регистрах 9 и 4, соответствующих команде следующей за данной, и ее выбору для выполнения. Выполнение команд, в которых осуществляется действие над словами переменной длины, осуществляется при помощи схемы 2 сравнения и блока 13 управ.тения, состоящего из врсьми тетрад, расположенных в ячейках 6 оперативной памяти с начальным адресом первой тетрады в массиве А1 в зоне памяти с начальным адресом А2. Слово команды содержит код операции и адреса А1 и А2 в двоичном коде. При выполнении данной команды назначение схемы 2 сравнения следующее. Каждый адрес выборки информации, поступающий на вход схемы 2 сравнения с выхода регистра 1 адреса (в данном случае А1) преобразуется в другой адрес, А1 , причем

АИ А1 + К,

где К - число п-разрядных слов, заключенных в оперативных ячейках 6 памяти с адресами А1 и А1 . Так, в данном примере А1 А1 + 7. Кроме того, адрес А1 в схеме 2 сравнения преобразуется из двоичного кода в позиционный. На другой вход схемы 2 сравнения поступает текущий адрес с регистра 9.

При совпадении текущего адреса и адреса (в примере А1 О сформированного в схеме 2 сравнения, на выходе схемы 2 вырабатывается сигнал сравнения в блок 13 управления.

Следует отметить, что схема 2 сравнения технологически выполняется аналогично матрице ПЗУ, что позволяет в процессе изготовления модуля фиксировать требуемое соответствие между адресами входа и преобразованными в матрице. Это позволяет менять длину обрабатываемых в модуле массивов информации.

Выполнение команды пересылки массива из восьми тетрад осуществляется следующим образом. Первое п-разрядное слово массива, расположенное по адресу А1, пересылается в оперативные ячейки б блока 5 памяти по адресу А2 аналогично выполнению команды рассмотренной ранее пересылки, но выполнение команды на этом не заканчивается. В соответствии с управляющими сигналами блока 13 управления далее осуществляется сдвиг на один разряд, в сторону увеличения адреса столбца, регистра 9 столбцов. После этого пересылается второе п-разрядное слово массива, и далее процесс пересылки продолжается до тех пор, пока на выходе схемы сравнения 2 не вырабатывается сигнал сравнения. После этого процесс выполнения данной команды заканчивается. Аналогично операции пересылки выполняются операции арифметической и логической обработки массивов информации. Наличие в модуле блока 14 ввода-вывода, состоящего из регистра 15 свертки, регистра 16 развертки, регистра 17 маски, схемы 18 сравнения и коммутатора 19, позволяется соединять микропроцессоры между собой для создания вычислительных систем на однотипных однокристальных микропроцессорах. В процессе функционирования системы микропроцессоры обмениваются между собой информацией, причем любой микропроцессор может быть и приемником и датчиком информации. Режим ввода-вывода информации осуществляется после дещифрации соответствующей команды. Вывод информации из микропроцессора осуществляется следующим образом. Сначала происходит процесс установления соединения данного микропроцессора с микропроцессором-приемником информации, Для этого по выходу 23 первой группы выходов блока ввода-вывода выдается сигнал «вызов, а из регистра 16 развертки с выхода 20 блока ввода-вывода выдается номер микропроцессора, с которым требуется установить соединение. Номер микропроцессора формируется программно. После получения ответа по соответствующему входу 21 группы входов блока ввода-вывода процесс установления соединения считается законченным. После этого информация из блока 5 памяти через коммутатор 8 пересылается по информационному выходу 24 блока ввода-вывода в регистр 16 развертки Полученная в регистре 16 п-разрядная информация преобразуется в последовательный код и в этом виде передается на выход 20 блока ввода-вывода. Процесс передачи заканчивается по инициативе либо приемного, либо передающего микропроцессора. Если после выдачи сигнала «вызов и номера микропроцессора-приемника не поступит ответный сигнал, то выдача сигнала «вызов с номером микропроцессора повторяется до получения ответного сигнала. Прием информации микропроцессором осуществляется следующим образом. В соответствии с программной микропроцессора, в регистр 17 маски засылается из блока 5 памяти код маска, разрещающий прием по тому или иному, или нескольким ВХОДНЫМ каналам. Получив сигнал «вызов на входе 21 группы входов блока ввода-вывода и номер по входу 22 группы входов блока ввода-вывода, номер пересылается в схему 18 сравнения. Совпадение номера, поступивщего на вход 22 группы входов блока ввода-вывода, с номером, установленным по программе . схеме 18, означает, что обращение с «вызовом относится к данному микропроцессору. В этом случае микропроцессор посылает ответный сигнал с выхода 23 второй группы выходов блока ввода-вывода. Процесс установления соединения закончился. После этого происходит прием информации со входа 22 группы входов блока ввода-вывода. Информация через коммутатор 19 поступает в регистр 15 свертки. В данном регистре последовательный код преобразуется в п-разрядный параллельный и затем по информационному выходу 24 блока ввода-вывода через коммутатор 8 записывается в блок 5 памяти. Наличие регистров адреса строк, столбцов и схемы сравнения в однокристальном микропроцессоре позволяет одной командой программы задавать операцию обработки массива информации, содержащего произвольное число п-разрядных слов. В известных однокристальных микропроцессорах для соверщения аналогичной операции необходима программа из ряда команд. Напри.мер, для перемещения массива информации из одной области оперативной зоны в другую необходимо выполнение программы, состоящей из следующих команд: установление адреса начальной тетрады массива, перемещение тетрады информации, увеличение адреса для формирования адреса следующей тетрады, сравнение адреса с конечным адресом массива и выход из программы в случае сравнения. Расчет показывает, что объем постоянной памяти увеличивается в 3-4 раза. Кроме того, при работе с массивами информации повышается в 2 раза быстродействие устройства за счет применения сдвиговых регистров адреса и уменьщения времени выполнения одной команды вместо . Применение в однокристальном микропроцессоре памяти с ячейками постоянной и оперативной памяти дает возможность в процессе разработки оптимально распределять память модуля на постоянную и оперативную зоны, в зависимости от требований рещаемых задач. Это позволяет минимизировать число микропроцессоров при реализации конкретного вычислительного средства. С другой стороны, фиксирование соотношения между постоянной и оперативной зонами одинаковыми во всех микропроцессорах приводит либо к увеличению числа модулей, либо к необходимости повышать степень интеграции на кристалле для увеличения общей памяти микропроцессора, что значительно повышает стоимость средства.

Использование блока ввода-вывода, позволяющего работать с другими микропроцессорами по однопроводному каналу связи, позволяет почти в 4-8 раз сократить число вводно-выводных контактов БИСа микропроцессора. Это приводит к повышению надежности устройства, а также позволяет повысить степень интеграции элементов на кристалле за счет освободившейся площади от контактов и выходных усилителей. Если площадь одного контакта эквивалентна 10-ти битам оперативной памяти, а усилитель - 15-ти, то применение предложенного блока ввода-вывода позволяет на 400 бит повысить объем оперативной или постоянной памяти.

Формула изобретения

1. Однокристальный микропроцессор, содержащий блок ввода-вывода, блок памяти, коммутатор, дещифратор строк, дешифратор столбцов, регистр адреса, регистр кода операций, арифметико-логический блок, блок управления, причем входы блока ввода-вывода являются входами микропроцессора, выходы группы блока ввода-вывода являются выходами микропроцессора, информационный выход блока вв.ода-вывода соединен с первыми входами коммутатора, арифметико-логического блока и регистра кода операции, а управляющий выход блока вводавывода соединен с первым входом блока управления, второй вход которого соединен с выходом регистра кода операций, а выход блока управления соединен с вторыми входами коммутатора и арифметико-логического блока, первая и вторая группы выходов регистра адреса соединены с группами входов соответственно дешифратора строк и дешифратора столбцов, а группа входов регистра адреса соединена с первой группой выходов коммутатора, вторая группа выходов которого соединена с входами записи и считывания блока памяти, отличающийся тем, что, с целью упрощения микропроцессора, он содержит схему сравнения, регистр сдвига столбцов, регистра сдвига строк, входы которого соединены с в.ыходами дешифратора строк, а выходы подключены к входам блока памяти, входы регистра сдвига столбцов соединены с выходами дешифратора столбцов, а выходы подключены к входам группы коммутатора, управляющие входы регистра сдвига строк и регистра сдвига столбцов соединены с выходом блока управления и выходом схемы сравнения, первый вход которой соединен с выходом регистра адреса, а второй вход подключен к управляющему выходу регистра сдвига столбца.

2.Микропроцессор по п. 1, отличающийся тем, что блок ввода-вывода, содержащий регистр свертки, регистр развертки, регистр маски, схему сравнения, коммутатор, причем входы первой группы коммутатора являются входами блока ввода-вывода, первый выход коммутатора подключен к входу регистра свертки, выход которого является информационным выходом блока ввода-вывода и соединен с информационными входами регистра развертки, регистра маски и схемы сравнения, второй выход коммутатора

соединен со вторым входом схемы сравнения, третий вход которой соединен с управляющим входом регистра маски и третьим выходом коммутатора, являющимся управляющим выходом блока ввода-вывода, вход

коммутатора соединен с выходом регистра маски, четвертый выход коммутатора и выход регистра развертки являются выходами группы блока ввода-вывода.

3.Микропроцессор по п. 1, отличающийся тем, что блок памяти содержит матрицу

оперативных и постоянных ячеек памяти, причем первый вход каждой постоянной или оперативной ячейки соединен с соответствующим входом следующей ячейки, расположенной в том же столбце и подключен к соответствующему входу первой группы, а второй вход каждой постоянной или оперативной ячейки блока памяти соединен с соответствующим входом следующей ячейки, расположенной в той же строке и подключен к соответствующему входу второй группы.

Источники информации,

принятые во внимание при экспертизе

1.Евреинов Э. В., Праигишвили И. В. Цифровые атоматы с настраиваемой структурой. М., «Энергия, 1974, с. 135-139.

2.Intel. 8048 EDN, 1976, № 21, с. 48-89 (прототип).

. ..0

734695

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для обработки нечеткой информации | 1989 |

|

SU1674145A1 |

| Устройство для формирования видеосигнала | 1990 |

|

SU1741124A1 |

| Система обработки нечеткой информации | 1987 |

|

SU1444803A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| Устройство для оценки степени оптимальности размещения в многопроцессорных кубических циклических системах при направленной передаче информации | 2020 |

|

RU2723288C1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ НА ГАЗОРАЗРЯДНОЙ ИНДИКАТОРНОЙ ПАНЕЛИ | 1993 |

|

RU2069018C1 |

| ПРОЦЕССОР ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 2000 |

|

RU2180969C1 |

| Устройство для отображения информации на газоразрядной индикаторной панели | 1989 |

|

SU1675935A1 |

Авторы

Даты

1980-05-15—Публикация

1978-02-01—Подача