Данное изобретение относится к устройству для измерения коэффициента ошибок в битах в системе связи с помощью циклического избыточного кода и решетчатого кода, более конкретно, к устройству для точного измерения коэффициента ошибок в битах с помощью декодера Витерби и повышения эффективности системы связи, использующей циклические избыточные коды и решетчатые коды, для обнаружения и исправления ошибок. В этом устройстве генерируются новые циклические избыточные коды, замещающие переданные циклические избыточные коды с использованием компонент информационных данных среди декодированных данных при прохождении через декодер Витерби; а решетчатые коды регенерируются с использованием декодированных данных, замещенных новыми циклическими избыточными кодами, и регенерированные данные сравниваются с переданными данными.

Предшествующий уровень техники

В обычных системах связи способ исправления ошибок и декодирования используется для исправления ошибок, которые генерируются при прохождении данных по каналу, в котором присутствуют шум и элементы, препятствующие осуществлению связи. К способам исправления ошибок и декодирования относятся способ блочного декодирования, в котором в блок, образованный передаваемыми данными, вносят избыточность, и способ решетчатого декодирования, в котором данные, введенные в определенном порядке, декодируют в соответствии с функцией способа декодирования.

Способ измерения коэффициента ошибок в битах будет подробно изложен со ссылками на способ обработки сигналов согласно стандарту множественного доступа с кодовым разделением каналов (МДКРК), который выбран в качестве стандартов системы цифровой сотовой телефонной связи и системы персональной радиосвязи в Корее и в котором циклические избыточные коды и решетчатые коды используют для обнаружения и исправления ошибок передачи.

Согласно стандарту МДКР речевые сигналы не передают на заданной скорости передачи, а передают в четыре этапа с использованием детектора речевой активности, который детектирует величину речевых сигналов. То есть, когда детектор речевой активности детектирует речевые сигналы, которые находятся в наиболее активном состоянии, речевые сигналы передают с максимальной скоростью передачи, равной 9600 бит/с. Но когда речевые сигналы находятся в неактивном состоянии, их передают на минимальной скорости передачи, равной 1200 бит/с, для поддержки канала между базовой станцией и оконечными устройствами. Скорости передачи в 4800 бит/с и 2400 бит/с между максимальной скоростью 9600 бит/с и минимальной скоростью 1200 бит/с, соответственно, используют при изменении речевых сигналов, переходящих из активного состояния в неактивное состояние, и при изменении речевых сигналов, переходящих из неактивного состояния в активное состояние. Передача информации на разных скоростях передачи в соответствии с состоянием речевых сигналов может поддерживать каналы связи между базовой станцией и оконечными устройствами в том случае, когда объем передаваемой информации небольшой, и поэтому можно эффективно использовать электрическую мощность, необходимую для передачи информации, при этом потребление электрической мощности оконечным устройством можно снизить, а также можно уменьшить помехи, создаваемые другим оконечным устройством пользователей данной системы связи.

Как указано выше, циклические избыточные коды данных для индикатора качества кадра добавляются к информационным данным, которые генерируются в соответствии со скоростью передачи, определяемой согласно степени активности речевых сигналов. Информационные данные обеспечивают необходимые параметры, чтобы определить, имеют ли принятые в приемном блоке кадры данных ошибку, и определить скорость для передачи принимаемых циклов. В частности, когда данные передаются на скорости 9600 бит/с, информационные данные составляют в блоки по 172 разряда и прибавляют к ним 12 битов циклических избыточных кодов. Затем кодированные остатки из 8 битов устанавливают на ноль для формирования кадра из 192 бит. Если данные передаются со скоростью передачи, равной 4800 бит/с, информационные данные составляют в блоки по 80 битов и к ним прибавляют циклические избыточные коды из 8 битов. Затем кодированные 8-битовые остатки устанавливают на ноль для создания 96-битового кадра. Аналогично, если данные передаются на скорости передачи, равной 1200 бит/с или 2400 бит/с, циклические избыточные коды к данным не прибавляют, и только имеющий ноль разряд кодированных остатков прибавляют к данным для создания кадра. Созданный указанным выше образом кадр формируется блоком из 20 мс.

Система связи с МДКР содержит решетчатые коды, имеющие длину ограничения 9 и коэффициент кодирования 1/3. Функция решетчатых кодов выражена цифрами 557, 663 и 711 по восьмеричному [коду], причем при вводе одного бита данных выводят три единицы кодированных данных.

Данные, проходящие через блок генерации циклических избыточных кодов и блок решетчатого кодирования, согласно стандарту МДКР, как указано выше, передают по радиоканалу через блок повторения символов, блок перемежения блоков данных, 64-матричный блок ортогональной модуляции, блок расширения полосы частот, блок фазовой модуляции, блок промежуточной частоты и блок радиочастоты.

Затем данные демодулируют в приемнике в обратном порядке относительно модулирования данных в передатчике. Демодулированные данные декодируют в декодере Витерби, который является декодером максимальной вероятности и декодирует данные, переданные от передатчика. Декодер Витерби определяет, есть ли ошибка в декодированных данных, посредством циклических избыточных кодов, которые им придают в передатчике. В системе связи с использованием МДКР, поскольку информация о скорости передачи, определенная в блоке детектирования речевых сигналов передатчика, к приемнику не передается, фактическую скорость для передачи определяют из числа четырех типов скорости передачи данных в зависимости от ошибки кадров.

Однако скорость передачи данных не определяется точно с помощью только коэффициента ошибок кадра указанным выше способом. Поэтому нужно определять более точную скорость передачи путем измерения коэффициента ошибок в битах демодулированных данных в приемнике до того, как демодулированные данные проходят через декодер Витерби, чтобы использовать коэффициент ошибок в битах переданных данных и циклические избыточные коды, переносимые посредством передаваемых данных.

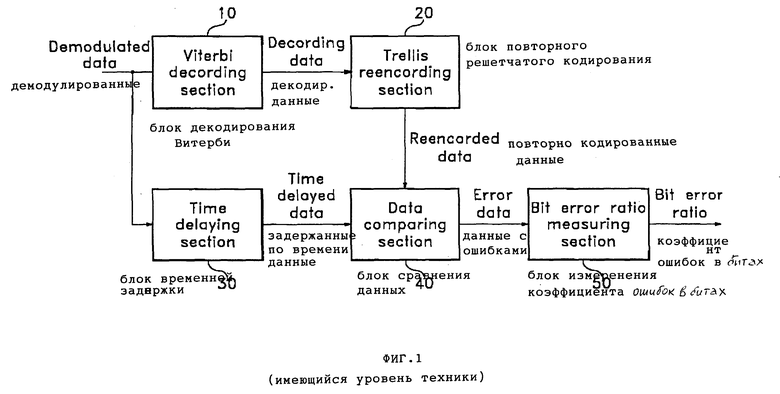

На фиг. 1 изображена блок-схема устройства для измерения коэффициента ошибок в битах, известного из предшествующего уровня техники, в котором применяют циклические избыточные коды и решетчатые коды в соответствии со скоростью передачи.

Устройство для измерения коэффициента ошибок в битах с помощью циклических избыточных кодов и решетчатых кодов в обычной системе связи содержит блок декодирования Витерби 10 для декодирования данных, которые модулируются в состоянии решетчатого кодирования с использованием способа декодирования максимальной вероятности, блок повторного кодирования 20 для повторного кодирования данных, которые вводятся от блока 10 декодирования Витерби, в решетчатые коды; блок задержки 30 для задержки демодулированных данных, введенных от демодулятора, так как эти данные на некоторое время должны быть задержаны, когда они проходят через блок декодирования Витерби 10 и блок повторного решетчатого кодирования 20, и таким образом блок задержки 30 компенсирует время задержки; блок сравнения данных 40 для сравнения повторно кодированных данных, которые являются выходными сигналами блока повторного решетчатого кодирования 20, с задержанными данными, которые проходят через блок временной задержки 30; и блок измерения 50 для измерения коэффициента ошибок в битах после приема данных с ошибками, выведенных из блока сравнения данных 40.

Работа устройства для измерения коэффициента ошибок в битах в известной системе связи с помощью циклических избыточных кодов и решетчатых кодов далее описывается подробно со ссылками на фиг.1.

Данные, демодулированные демодулятором приемного устройства, имеют вид кодированных символов, которые проходят через блок решетчатого кодирования передатчика, и имеют биты, несущие ошибки, обусловленные шумом, замиранием и помехами канала. Декодированные данные, имеющие биты с ошибками, корректируются при прохождении через блок декодирования Витерби 10, в результате чего их декодируют в виде кадра, сформированного передатчиком, как описано выше. Затем блок повторного решетчатого декодирования 20 принимает декодированные данные, содержащие речевую информацию и циклические избыточные коды в форме кадра, и выполняет повторное кодирование аналогично решетчатому кодированию в передатчике.

Поскольку ошибки, генерируемые при демодулировании, корректируются до нужного уровня, то декодированные данные, проходящие через блок декодирования Витерби 10, имеют меньше ошибок, чем демодулированные данные. Исходя из этого предполагается, что повторно кодированные решетчатым методом данные, в качестве переданных данных, находятся в состоянии, при котором не известно, являются ли данные, кодированные в блоке решетчатого кодирования передатчика, переданными данными или нет. Поэтому блок сравнения данных сравнивает повторно кодированные данные, которые рассматривают как данные из передатчика, с задержанными по времени данными, которые задерживают на то же время, на которое задерживают повторно кодированные данные при прохождении по каналу и блоку временной задержки 30, чтобы обнаружить ошибку в сигналах, которые вводятся в блок сравнения данных 10, и сформировать данные с ошибками. Блок измерения коэффициента ошибок в битах 50 делит данные с ошибками на биты, не имеющие ошибок, и биты, имеющие ошибки, тем самым вычисляя число битов, имеющих ошибки, относительно числа битов, не имеющих ошибок, среди всех введенных в него данных с ошибками, и измеряя коэффициент ошибок в битах.

Известное устройство измерения коэффициента ошибок в битах измеряет коэффициент ошибок в битах, исходя из того, что демодулированные данные являются теми же данными, которые переданы от передатчика. Поэтому, если все ошибки в демодулированных данных не исправлены декодером Витерби, то декодированные данные будут отличаться от данных, переданных от передатчика к блоку решетчатого кодирования.

Соответственно, декодированные данные будут отличаться от выходного сигнала блока решетчатого кодирования передатчика. В частности, поскольку известное устройство для измерения коэффициента ошибок в битах использует данные с ошибками как основу для выполнения измерения коэффициента ошибок в битах, оно рассматривает биты с ошибками среди демодулированных данных, вводимых в декодер Витерби, как биты без ошибок. Поэтому это устройство считывает меньшее значение коэффициента ошибок в битах, чем его действительное значение, в результате чего определяют, что переданные от передатчика данные передаются на максимальной скорости передачи несмотря на то, что их передают на некоторой иной скорости передачи.

Известно также устройство для обнаружения ошибок (см. WO 93/20620, A1, кл. H 03 M 13/12, опубл. 14.10.93, 41 стр.), содержащее на входе декодер Витерби и элемент задержки, выход которого через блок памяти подключен к первому входу блока сравнения, к второму входу которого подключен выход декодера Витерби, а также блок накопления, блок оценки ошибок.

Общими признаками с настоящим изобретением являются декодер Витерби, соединенный на входе с элементом задержки, выход декодера Витерби, соединенный со входом блока сравнения и блок сравнения.

Сущность изобретения

Задача данного изобретения заключается в устранении указанной выше проблемы известного уровня техники. Настоящее изобретение направлено на создание устройства для измерения коэффициента ошибок в битах, в котором новые циклические избыточные коды создают таким образом, что циклические избыточные коды создают в передатчике с использованием информационных данных, формирующих декодированные данные, которые являются выходными сигналами декодера Витерби, и информации из циклических избыточных кодов; и новые циклические избыточные коды вместо циклических избыточных кодов прибавляют к информационным данным для решетчатого повторного кодирования, тем самым точно измеряя коэффициент ошибок в битах, при этом определяют скорость передачи данных, переданных от передатчика, на основе коэффициента ошибок в битах, чтобы исключить принятие решения о том, что данные, переданные от передатчика, передают на максимальной скорости передачи несмотря на то, что их передают на некоторой иной скорости передачи, в результате чего обеспечивается снижение потребления электроэнергии в оконечном устройстве, и увеличивают производительность по приему данных.

Для достижения указанного результата в соответствии с изобретением устройство для измерения коэффициента ошибок в битах с помощью декодера Витерби, содержит:

блок декодера Витерби для декодирования данных, демодулированных в состояние решетчатого кодирования, методом декодирования максимальной вероятности;

блок повторного решетчатого кодирования для решетчатого кодирования тем же методом, что и в блоке кодирования, при приеме данных от блока декодирования Витерби; и

блок регенерации, включенный между блоком декодирования Витерби и блоком повторного решетчатого кодирования, для приема выходного сигнала блока декодирования Витерби, устранения декодированных данных циклических избыточных кодов и прибавления новых данных циклических избыточных кодов.

Устройство для измерения коэффициента ошибок в битах с помощью декодера Витерби согласно данному изобретению также содержит:

блок временной задержки для приема и задержки демодулированных данных для компенсации временной задержки при прохождении данных через блок декодирования Витерби, блок регенерации циклических избыточных кодов и блок повторного решетчатого кодирования;

блок сравнения для сравнения выходного сигнала блока повторного решетчатого кодирования с задержанными по времени данными, прошедшими через блок временной задержки, для формирования данных с ошибками, которые содержат биты с ошибками и биты без ошибок; и

блок измерения для приема выходного сигнала блока сравнения данных и измерения коэффициента ошибок в битах.

В устройстве для измерения коэффициента ошибок в битах с помощью декодера Витерби блок регенерации циклических избыточных кодов содержит блок выбора циклических избыточных кодов для определения числа бит, прибавленных к данным, которые кодируются в блоке кодирования, и способа генерации бит, и блок генерации циклических избыточных кодов для генерации настраиваемых циклических избыточных кодов в соответствии со способом генерации циклических избыточных кодов, определяемым в блоке выбора циклических избыточных кодов, и для прибавления циклических избыточных кодов к информационным данным.

Краткое описание чертежей

Указанные задачи и преимущества данного изобретения поясняются в излагаемом ниже подробном описании предпочтительного варианта осуществления, иллюстрируемого чертежами, на которых представлено следующее:

фиг.1 - блок-схема известного устройства измерения коэффициента ошибок в битах;

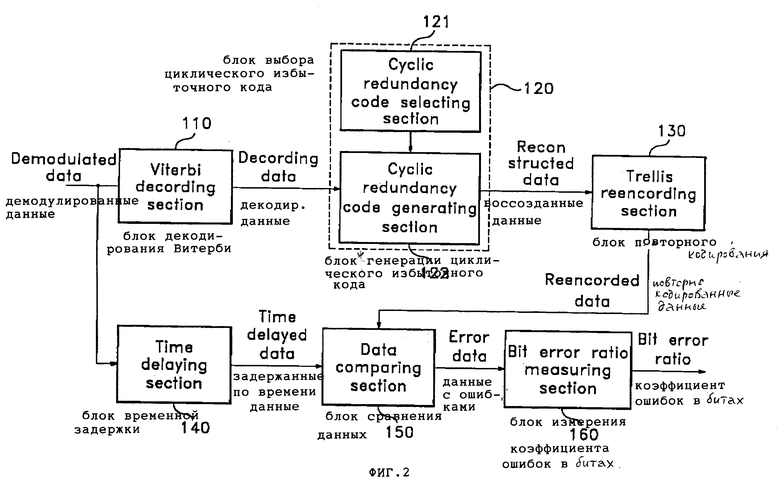

фиг.2 - блок-схема устройства измерения коэффициента ошибок в битах, выполненного согласно изобретению;

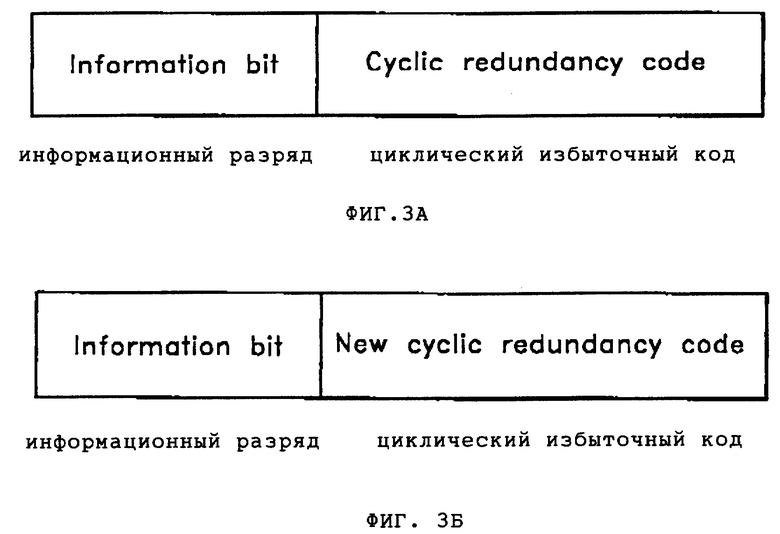

фиг. 3А и 3Б - диаграммы, иллюстрирующие работу устройства измерения коэффициента ошибок в битах, выполненного согласно изобретению.

Описание предпочтительного варианта осуществления

Предпочтительный вариант осуществления изобретения далее излагается со ссылками на чертежи.

На фиг. 2 представлена блок-схема устройства измерения коэффициента ошибок в битах согласно данному изобретению. На фиг. 2 устройство для измерения коэффициента ошибок в битах в системе связи, использующей циклические избыточные коды и решетчатые коды, содержит блок декодирования Витерби 110 для декодирования данных, демодулированных в состояние решетчатого кодирования, с помощью метода декодирования максимальной вероятности; блок 120, предназначенный для приема данных от блока декодирования Витерби 110, обеспечивающий устранение циклических избыточных кодов из данных и прибавление новых циклических избыточных кодов к данным; блок повторного решетчатого кодирования 130 для приема данных от блока регенерации циклических избыточных кодов 120 и выполнения повторного решетчатого кодирования как в передатчике, и блок временной задержки 140 для задержки демодулированных данных на время задержки, обеспечивающее компенсацию задержки данных при прохождении через блок декодирования Витерби 110, блок регенерации циклических избыточных кодов 120 и блок повторного решетчатого кодирования 130; блок сравнения данных 150 для сравнения повторно кодированных данных от блока повторного решетчатого кодирования 130 с демодулированными данными, проходящими через блок временной задержки 140, для формирования данных с ошибками, содержащих биты без ошибок, выделенные относительно битов с ошибками; и блок измерения 160 для измерения коэффициента ошибок в битах данных с ошибками, полученных от блока сравнения данных 150.

Блок регенерации циклических избыточных кодов 120 содержит блок выбора циклических избыточных кодов 121 для определения числа бит и способа генерации циклических избыточных кодов, прибавляемых к данным от передатчика, и блок генерации циклических избыточных кодов 122 для генерации настраиваемых циклических избыточных кодов в соответствии с выбранным способом генерации циклических избыточных кодов и прибавления циклических избыточных кодов к информационным данным.

Работа устройства измерения ошибок в битах в системе связи, использующей циклические избыточные коды и решетчатые коды в соответствии с данным изобретением, далее описывается со ссылками на фиг. 2 - 3Б.

Данные, демодулированные демодулятором приемника, имеют вид данных, кодированных в блоке решетчатого кодирования передатчика; они имеют биты с ошибками после прохождения по каналу. Демодулированные данные, содержащие биты с ошибками, корректируют в диапазоне коррекции во время прохождения через декодер Витерби 110, и затем данные декодируют в форме кадра, сформированного в передатчике, как указано выше. Декодированные данные (см. фиг. 3А) формируют из информационных данных и циклических избыточных кодов, которые прибавляют к информационным данным в передатчике. Блок регенерации циклических избыточных кодов 120 принимает декодированные данные и устраняет циклические избыточные коды из декодированных данных. Затем блок регенерации циклических избыточных кодов 120 создает новые циклические избыточные коды тем же способом, что и в передатчике, с помощью информационных данных и прибавляет новые циклические избыточные коды к информационным данным, чтобы сформировать кадр, как показано на фиг. 3Б. В это время блок выбора циклических избыточных кодов 121 определяет число битов и способ генерации циклических избыточных кодов, которые прибавляют к данным, а блок генерации циклических избыточных кодов 122 генерирует новые циклические избыточные коды согласно способу генерации циклических избыточных кодов, который определен в блоке выбора циклических избыточных кодов 121, и прибавляет их к информационным данным. Новые циклические избыточные коды генерируют с помощью декодированных данных от декодера Витерби 110 (фиг.2). Поэтому, когда в декодированных данных возникают ошибки, новые циклические избыточные коды могут отличаться от циклических избыточных кодов, которые добавлены к информационным данным в передатчике.

Даже если ошибка возникает в одном из битов информационных данных и циклических избыточных кодов, формирующих кадр, то блок сравнения данных определяет, что в данном кадре возникла ошибка. Поэтому, если ошибка возникает в битах циклических избыточных кодов, блок генерации циклических избыточных кодов 122 устраняет циклические избыточные коды и генерирует новые циклические избыточные коды. После этого блок генерации циклических избыточных кодов 122 прибавляет их к информационным данным, так что информационные данные аналогичны данным от передатчика. Таким образом устраняются циклические избыточные коды из информационных данных, переданных от передатчика, и прибавляются новые циклические избыточные коды к информационным данным.

Блок решетчатого кодирования 130 принимает выходной сигнал блока генерации циклических избыточных кодов 122, создавая кадр из информационных данных и новых циклических избыточных кодов, и генерирует данные, кодированные решетчатым методом, тем же способом, что и при решетчатом кодировании в передатчике.

С другой стороны, поскольку повторно кодированные данные задержаны вследствие прохождения через блок декодирования Витерби 110, блок генерации циклических избыточных кодов 120 и блок повторного решетчатого кодирования 130, то блок временной задержки 140 вводит соответствующую задержку в демодулированные данные для обеспечения обработки повторно кодированных данных. Блок сравнения данных 150 сравнивает демодулированные данные, прошедшие через блок временной задержки 140, с данными повторного решетчатого кодирования и проводит различие между битами с ошибками и битами без ошибок. Потом блок 150 сравнения данных выводит данные с ошибками. После этого блок измерения коэффициента ошибок в битах 160 принимает данные с ошибками от блока сравнения данных 150 и вычисляет число битов, имеющих ошибки.

Наконец, блок измерения коэффициента ошибок в битах 160 измеряет отношение числа битов, имеющих ошибки, к числу всех битов.

В устройстве измерения коэффициента ошибок в битах в соответствии с данным изобретением, как излагалось выше, блок измерения коэффициента ошибок в битах точно измеряет коэффициент ошибок в битах демодулированных данных, на основании которого может быть определена конкретная скорость передачи. В результате этого обеспечивается снижение потребления электроэнергии в оконечном устройстве. Кроме этого, могут быть снижены взаимные помехи, воздействующие на другое оконечное устройство.

Несмотря на то, что данное изобретение описано на примере конкретного варианта осуществления, специалистам в данной области техники понятно, что могут быть осуществлены различные изменения в рамках сущности и объема изобретения, определяемых прилагаемой формулой изобретения.

Изобретение относится к устройству для измерения коэффициента ошибок в битах в системе связи с помощью циклического избыточного кода и решетчатого кода, более конкретно к устройству для точного измерения коэффициента ошибок в битах с помощью декодера Витерби и повышении эффективности системы связи, использующий циклические избыточные коды и решетчатые коды, для обнаружения и исправления ошибок. Технический результат - повышение точности измерения коэффициента ошибок. Устройство для измерения коэффициента ошибок в битах обеспечивает генерацию новых циклических избыточных кодов тем же способом, который был использован в передатчике, для определения ошибок в битах, в системе связи, использующей циклические избыточные коды и решетчатые коды, путем декодирования информационных данных, образующих декодированные данные, являющиеся выходным сигналом декодера Витерби, и информационных данных из декодированных циклических избыточных кодов. Устройство для измерения коэффициента ошибок в битах прибавляет новые циклические избыточные коды вместо старых циклических избыточных кодов, к декодированным информационным данным, чтобы повторно кодировать новые циклические избыточные коды в виде решетчатого кода, тем самым обеспечивая точное измерение коэффициента ошибок в битах. Устройство может уменьшить вероятность неправильного определения скорости передачи как соответствующей максимальной скорости передачи путем определения скорости передачи в зависимости от коэффициента ошибок в битах, в результате чего обеспечивается снижение потребления электроэнергии в оконечном устройстве и увеличение пропускной способности при приеме. 1 з.п. ф-лы, 4 ил.

| US 5117427 A, 26.05.92 | |||

| US 5113400 A, 12.08.92 | |||

| US 4633470 A, 30.12.86 | |||

| СПОСОБ И УСТАНОВКА ДЛЯ ИЗГОТОВЛЕНИЯ ЛЕНТ И ЛИСТОВ ИЗ СТАЛИ | 2001 |

|

RU2271256C2 |

| ПЛАСТИКОВАЯ КРЫШКА С ПРОКЛАДКОЙ | 2000 |

|

RU2255882C2 |

| Выходное устройство декодера Витерби | 1990 |

|

SU1775858A1 |

| Выходное устройство декодера Витерби | 1985 |

|

SU1367165A1 |

| Станок для изготовления электрических катушек | 1973 |

|

SU510756A1 |

| Домовый номерной фонарь, служащий одновременно для указания названия улицы и номера дома и для освещения прилежащего участка улицы | 1917 |

|

SU93A1 |

Авторы

Даты

1999-11-10—Публикация

1997-10-03—Подача