Область техники

Настоящее изобретение относится к способу обеспечения безопасности, обеспечивающему детерминированность выполнения в реальном времени многозадачных приложений типа управление-регулирование в системе управления, содержащей, по меньшей мере: первичный системный таймер, вырабатывающий сигнал прерывания по истечении заданного регулируемого промежутка времени; центральный вычислительный блок, содержащий, по меньшей мере, один процессор, способный получать, по меньшей мере, указанный сигнал прерывания от таймера; основное устройство памяти и совокупность контроллеров периферийных устройств для управления входами-выходами системы управления.

Уровень техники

В многозадачной системе управления, выполняющей различные задачи (ввод-вывод, вычисления...) с различными временными масштабами, способные обмениваться данными, с синхронизацией и координацией в реальном времени всех операций обработки, желательно иметь возможность выполнять операции в реальном времени детерминированным способом, то есть при условии единственности и неизменности глобального поведения всех задач, которые взаимодействуют друг с другом и с окружением. Желательно также, чтобы была обеспечена безопасность выполнения операций в реальном времени, то есть имелась возможность обнаружения и локализации ошибок при обеспечении независимости различных задач по отношению к сбоям, при сохранении максимальной детерминированности в случае ошибок в работе.

Известны многочисленные многозадачные системы управления. Однако эти системы управления большую часть времени являются асинхронными и, следовательно, недетерминированными. Более того, устройство таких систем не препятствует распространению определенных типов сбоев.

Известен, в частности, описанный в документе FR-A-2771828 способ обеспечения безопасности многозадачного вычислительного устройства, снабженного системой обнаружения сбоев путем временного или пространственного разбиения, в котором в каждый момент времени отмечается задача, выполнение которой является законным.

В соответствии с этим документом, который касается системы с циклическим планированием, для ограничения распространения сбоев применяется разбиение на разделы, однако при этом между разделами не сохраняется связь, то есть отсутствует многозадачное управление на глобальном уровне. Более того, всегда имеется возможность распространения ошибок внутри раздела, что не позволяет обеспечить максимальную безопасность.

Таким образом, документ FR-A-2771828 показывает, что обеспечение детерминированности представляется противоречащим многозадачному управлению.

Раскрытие изобретения

Настоящее изобретение направлено на решение задачи устранения недостатков прежних систем и создания более интегрированных, мощных и надежных систем управления.

Более конкретно, настоящее изобретение направлено на то, чтобы обеспечить безопасное выполнение вычислительным устройством задач в многозадачном режиме в реальном времени детерминированным способом с локализацией ошибок и отказоустойчивостью.

Следующая задача состоит в обеспечении безопасности с высокой степенью детерминизма при выполнении в реальном времени многозадачных приложений как для циклических, так и для ациклических задач, с обменом явными и неявными сообщениями (т.е. датированными сообщениями и потоками датированных данных).

Названные задачи решаются созданием способа обеспечения безопасности, с помощью которого достигается детерминированное выполнение в реальном времени многозадачных приложений типа управления-регулирования в системе управления, содержащей:

- по меньшей мере, первичный системный таймер, вырабатывающий сигнал sh прерывания по истечении заданного регулируемого промежутка времени,

- центральный вычислительный блок, содержащий, по меньшей мере, один процессор, способный получать, по меньшей мере, сигнал sh прерывания от системного таймера;

- основное устройство памяти, и

- совокупность контроллеров периферийных устройств для управления входами-выходами системы управления.

При этом способ по изобретению характеризуется тем, что включает в себя следующие операции:

(a) запоминают для каждой из задач данного приложения все разрешенные сцепления его точек временной синхронизации, требующие обращения к системному уровню, причем эти сцепления представляются управляющим графом выполнения обращений рассматриваемой задачи к системному уровню, а каждый граф содержит совокупность узлов, каждый из которых соответствует обращению к системному уровню системы управления,

(b) для каждого узла управляющего графа каждой задачи запоминают природу обращения к системному уровню (т.е. действия, которые должен выполнить системный уровень в ответ на обращение к нему) и его параметры вызова, в том числе временные параметры, которые позволили бы обновить значения "самого раннего времени начала" d(i) и "самого позднего времени завершения" f(i),

(c) запоминают для каждой задачи начальный узел в соответствующем графе,

(d) инициализируют для данного приложения и перед запуском выполнения в реальном времени в соответствии с режимом работы с привязкой ко времени для каждой задачи начальный узел и начальный момент, представляющие начальное состояние рассматриваемой задачи,

(e) инициализируют для данного приложения и перед запуском выполнения в реальном времени в соответствии с режимом работы с привязкой ко времени порядок запуска каждой задачи путем выполнения предварительного упорядочения списков задач на уровне элементарного микроядра,

(f) устанавливают первичный системный таймер для выдачи сигнала sh прерывания таймера, содержащего обращение к микроядру, в первый момент работы приложения для запуска выполнения этого приложения в режиме работы с привязкой ко времени,

(g) в ходе нормальной работы после установки первичного системного таймера вызывают сброс первичного системного таймера микроядром при каждом обращении к микроядру; при обращении к микроядру со стороны системного уровня или при обработке сигнала sh прерывания переводят микроядро на операцию упорядоченного обновления списков задач с учетом временных характеристик задач, а именно, самого раннего времени d(i) начала и самого позднего времени f(i) завершения; вычисляют при помощи микроядра, после обновления списков задач, ближайший будущий момент времени, по истечении которого одна из задач должна быть активизирована, и устанавливают при помощи микроядра первичный системный таймер, начиная с этого ближайшего будущего момента времени, чтобы активизировать указанную задачу и выйти из микроядра,

(h) во время выполнения задачи осуществляют вызов к системному уровню, только когда будет достигнут узел управляющего графа указанной задачи, принимая в качестве аргумента номер узла; при входе в системный уровень проверяют, является ли, в соответствии с управляющим графом выполняемой задачи, разрешенным сцепление, начиная с узла, соответствующего предыдущему обращению к системному уровню, с тем чтобы запустить на системном уровне обработку ошибки, если указанное сцепление не разрешено, и продолжить выполнение, если указанное сцепление разрешено, осуществляют обновление временных параметров задачи в ходе выполнения, включающих в себя самое раннее время d(i) начала и самое позднее время f(i) завершения, при помощи обращения системного уровня к микроядру, и продолжают в нормальных условиях выполнение текущей задачи до того момента, пока она снова не достигнет узла своего управляющего графа.

С учетом изложенного следует отметить, что применительно к задачам, которые уже начали выполняться, параметры "самое раннее время начала" и "самое позднее время завершения" относятся к следующему узлу управляющего графа соответствующей задачи, в котором данная задача потребует обращения к системному уровню системы управления.

В предпочтительном варианте способ обеспечения безопасности согласно изобретению применяется к системе управления, дополнительно содержащей устройство защиты памяти для контроля за правами доступа к адресации. Это устройство защиты памяти, исходя из запрошенного адреса ad. предоставленного центральным вычислительным блоком, и из прав (С) доступа к контекстам выполнения процессора в адресуемой памяти, генерирует эксклюзивный подтвержденный адрес av, который разрешает доступ или выдает центральному вычислительному блоку сигнал se исключения неразрешенной адресации.

При этом способ обеспечения безопасности включает в себя дополнительно следующие операции:

(i) на стадии подготовки запоминают для данного приложения права доступа к каждому сегменту памяти для микроядра, а также для каждой задачи приложения и ее продолжения на системный уровень, с тем чтобы образовать первый и второй контексты выполнения в соответствии с тем, находятся ли команды собственно в коде приложения, образующего задачу, или же эти команды находятся в общем коде системного уровня, составляющем продолжение задачи на системный уровень,

(j) для данного приложения и перед запуском выполнения в реальном времени в соответствии с режимом работы с привязкой ко времени инициализируют контекст микроядра, а также первый и второй контексты выполнения для каждой задачи и ее продолжения на системный уровень,

(k) в ходе выполнения задачи осуществляют обращение к системному уровню при помощи команды перехода в привилегированный режим выполнения, который позволяет переходить из указанного первого контекста выполнения задачи в указанный второй контекст, а после проверки разрешенности сцепления, начиная с узла, соответствующего предыдущему системному вызову, и после обновления временных параметров задачи при помощи обращения системного уровня к микроядру, обеспечивают возврат в код задачи при помощи команды возврата в непривилегированный режим, который позволяет перейти от указанного второго контекста к указанному первому контексту выполнения задачи.

Контексты выполнения каждой задачи приложения являются предпочтительно попарно разделенными.

В соответствии с предпочтительной характеристикой способа согласно изобретению продолжения контекстов выполнения задач приложения в системный уровень не являются доступными для записи для контекстов выполнения задач с кодом приложения.

Кодирование управляющего графа задачи не допускает никаких сбоев, вызванных общими причинами, между механизмом контроля выполнения какой-либо задачи приложения и выполнением самой этой задачи.

Способ согласно изобретению может также включать следующие операции:

(l) в фазе подготовки запоминают для данного приложения и для всех сцеплений, разрешенных для каждой задачи, временную квоту, представляющую собой верхнюю оценку максимального времени выполнения, необходимого для перехода от одного узла к другому в управляющем графе задачи, причем каждая временная квота включает в себя время, затраченное на выполнение команд собственно задачи, а также время на выполнение общего кода системного уровня в продолжении задачи,

(m) при нормальном функционировании после установки первичного системного таймера при обращении к микроядру, вызванном сигналом sh прерывания по времени и вызывающем сброс первичного системного таймера, приступают к проверке, связан ли сигнал sh прерывания по времени, вызывающий обращение к микроядру, с попыткой нарушения временной квоты, и если это так, то запускают посредством микроядра обработку ошибки. Если же сигнал sh прерывания по времени не связан с попыткой нарушения временной квоты, то переводят микроядро на операцию обновления списков задач и после этого обновления списков задач вычисляют при помощи микроядра, с одной стороны, ближайший момент времени в будущем, когда одна из задач должна быть активизирована, и, с другой стороны, момент времени в будущем, начиная с которого временная квота, отведенная выполняемой задаче при выходе из микроядра, определенном при обновлении списков, будет исчерпана. При этом устанавливают первичный системный таймер при помощи микроядра на ближайший из этих моментов в будущем, с тем чтобы в соответствии с условиями либо активизировать задачу, либо распознать попытку нарушения временной квоты, обнаружив ошибку в функционировании, и выйти из микроядра после установки первичного системного таймера.

В случае, если в системе управления работает второй системный таймер, то согласно предпочтительному варианту изобретения микроядро получает доступ ко второму системному таймеру для контроля, путем сравнения временных сигналов, хода времени, заданного первичным системным таймером.

Способ обеспечения безопасности согласно изобретению, адаптированный для того, чтобы сделать детерминированным выполнение в реальном времени сообщающихся между собой многозадачных приложений типа управление-регулирование, может дополнительно содержать следующие операции:

(n) на стадии подготовки запоминают для каждой из задач данного приложения все разрешенные сцепления его точек временной синхронизации и связи с другими задачами, требующие обращения к системному уровню, причем эти разрешенные сцепления представляются управляющим графом выполнения обращений рассматриваемой задачи к системному уровню, а каждый граф содержит совокупность узлов, каждый из которых соответствует обращению к системному уровню,

(о) запоминают каждую буферную область, необходимую для обмена данными между задачами, указав ее размер, размер содержащихся в ней элементов, ее размещение или базовый адрес, а также связи между буферными зонами, позволяющими подтвердить достоверность обмена информацией, необходимого для связи,

(р) запоминают для каждой буферной зоны начальные значения ее элементов,

(q) инициализируют, для данного приложения и предварительно при пуске выполнения в реальном времени в соответствии с режимом работы с привязкой ко времени, значения элементов буферной зоны значениями, предварительно занесенными в память,

(r) во время выполнения задачи при обращении к системному уровню, когда будет достигнут узел управляющего графа задачи, и после проверки того, что в соответствии с управляющим графом выполняемой задачи сцепление, начиная с узла, соответствующего предыдущему обращению к системному уровню, является разрешенным, осуществляют последовательные обновления буферных зон в соответствии с природой вызова, предварительно занесенного в память, путем необходимых инкрементных обновлений временных параметров выполняемой задачи, включающих моменты самого раннего времени d(i) начала и самого позднего времени f(i) завершения.

Согласно предпочтительной характеристике изобретения на системном уровне разрешено совместное использование одних буферных зон продолжениями контекстов выполнения задач приложения. При этом буферная зона, отведенная для динамических сообщений, соответствующих отправке сообщений, может быть совместно использована только двумя продолжениями контекстов выполнения задачи. В то же время буферная зона, отведенная для статических сообщений, соответствующих потоку датированных данных, может быть совместно использована более чем двумя продолжениями контекстов выполнения задачи. Однако она по-прежнему может быть изменена только задачей-владельцем в продолжении ее контекста на системный уровень.

Способ обеспечения безопасности согласно изобретению применим к приложениям типа управление-регулирование с высоким уровнем требований к безопасности.

В частности, способ согласно изобретению может быть применен к системе управления-регулирования класса надежности 1 Е для ядерного реактора.

Перечень чертежей

Другие характеристики и преимущества изобретения станут ясны из нижеследующего описания конкретных вариантов его реализации, приводимых в качестве примеров со ссылкой на прилагаемые чертежи.

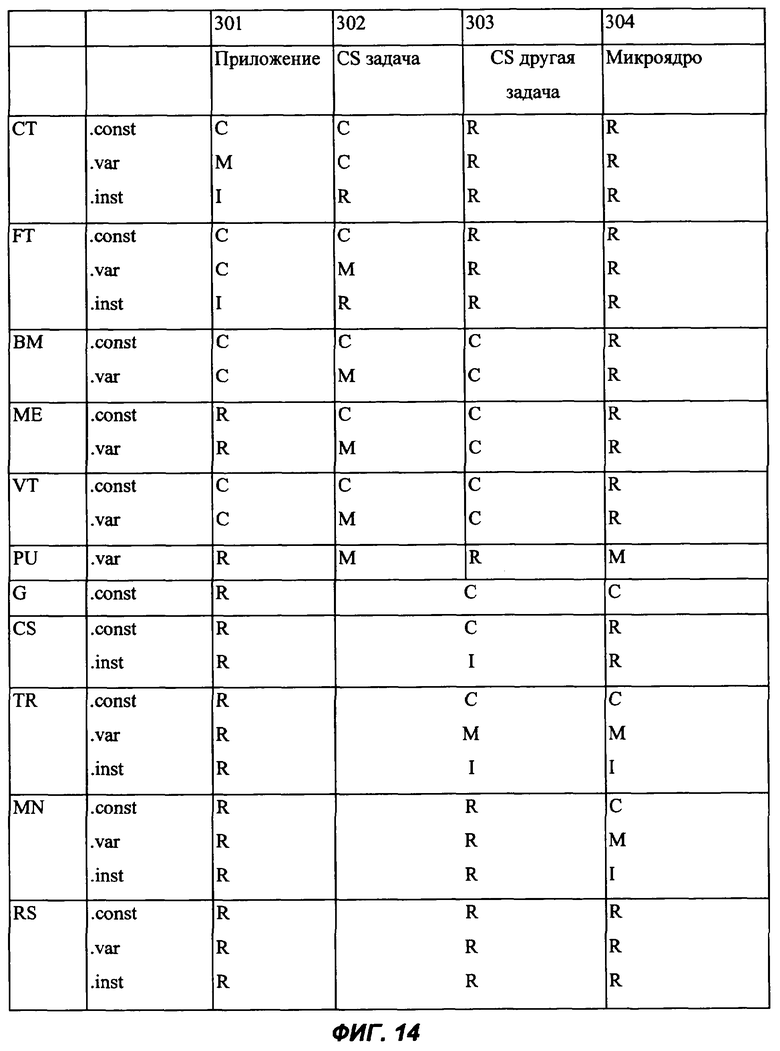

Фиг.1 - это упрощенное представление архитектуры системы управления, к которой применим способ обеспечения безопасности по настоящему изобретению.

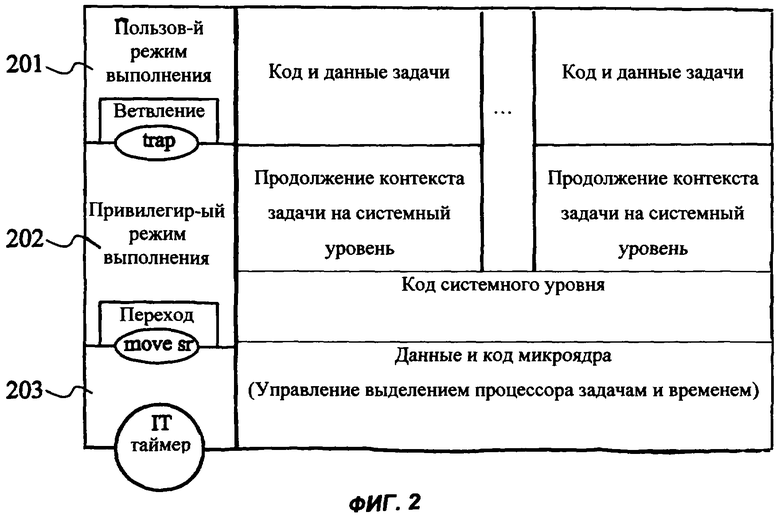

Фиг.2 представляет собой схему распределения кода по глубине по отношению к системному уровню и микроядру.

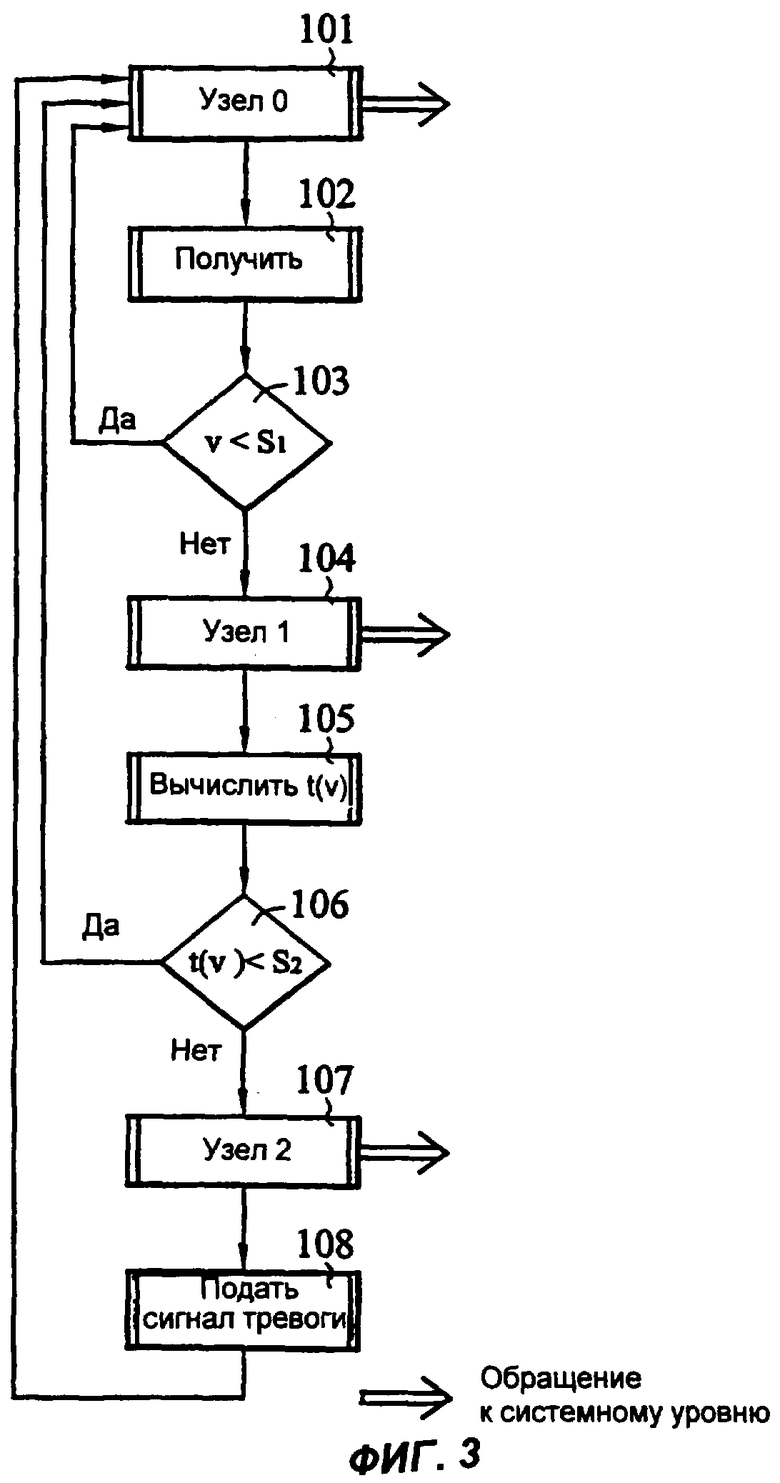

Фиг.3 представляет собой блок-схему обработки примера задачи реального времени в соответствии со способом обеспечения безопасности согласно изобретению.

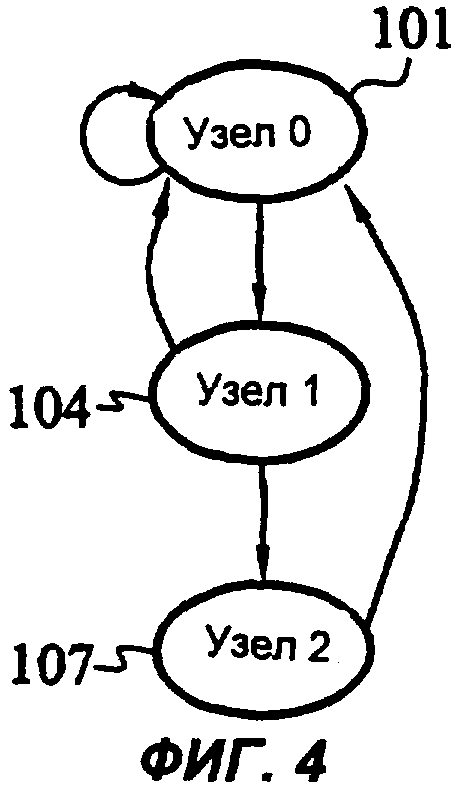

Фиг.4 - это управляющий граф, соответствующий схеме по фиг.3.

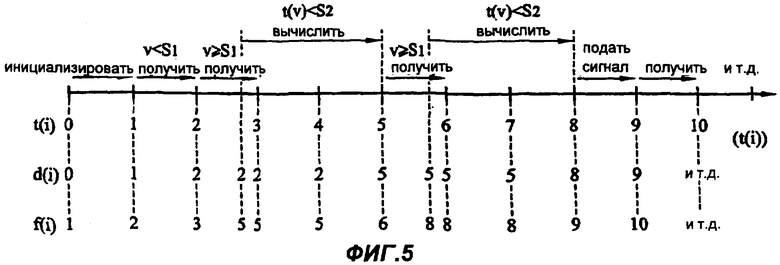

Фиг.5 содержит пример хронограммы и сопоставленных ей временных значений в ходе обработки примера задачи реального времени, представленной на фиг.3 и 4, в соответствии со способом обеспечения безопасности согласно изобретению.

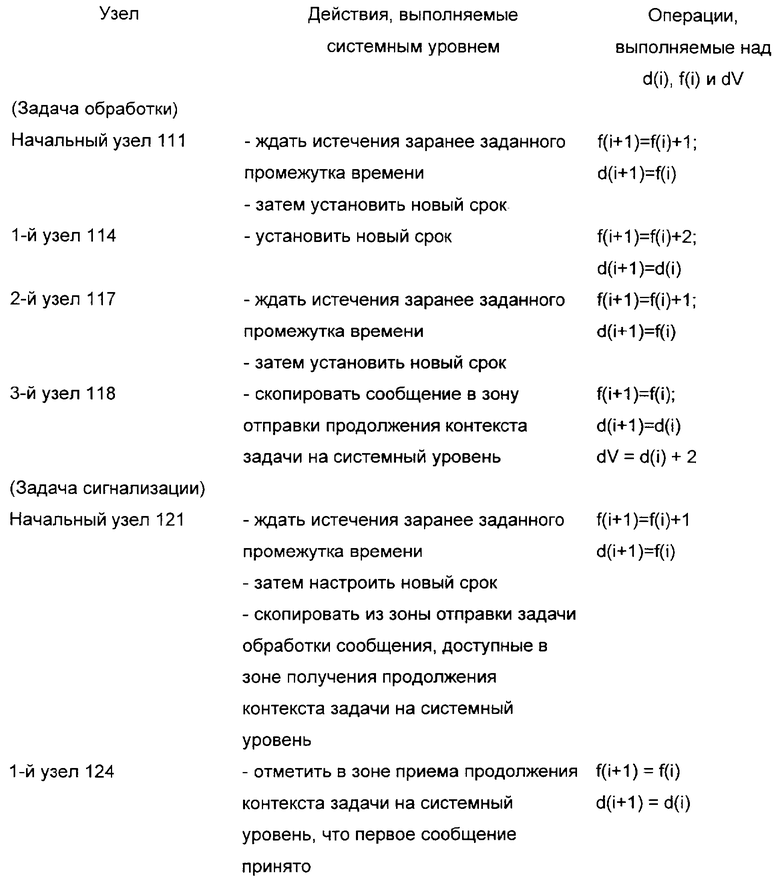

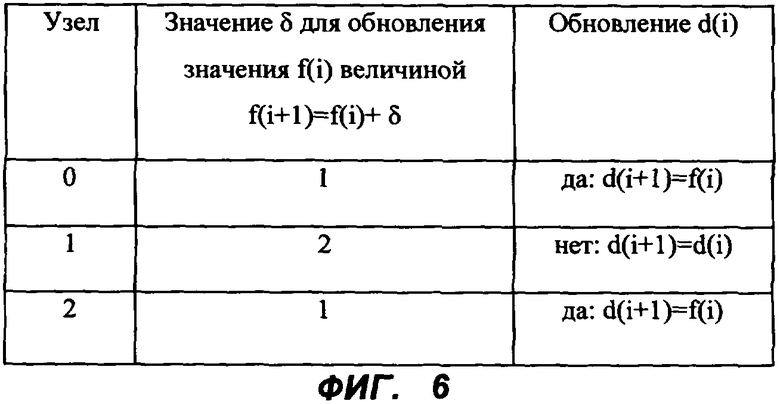

Фиг.6 содержит таблицу узлов управляющего графа по фиг.4 с описанием операций, которые необходимо выполнить над моментами самого раннего времени d(i) начала и самого позднего времени f(i) завершения.

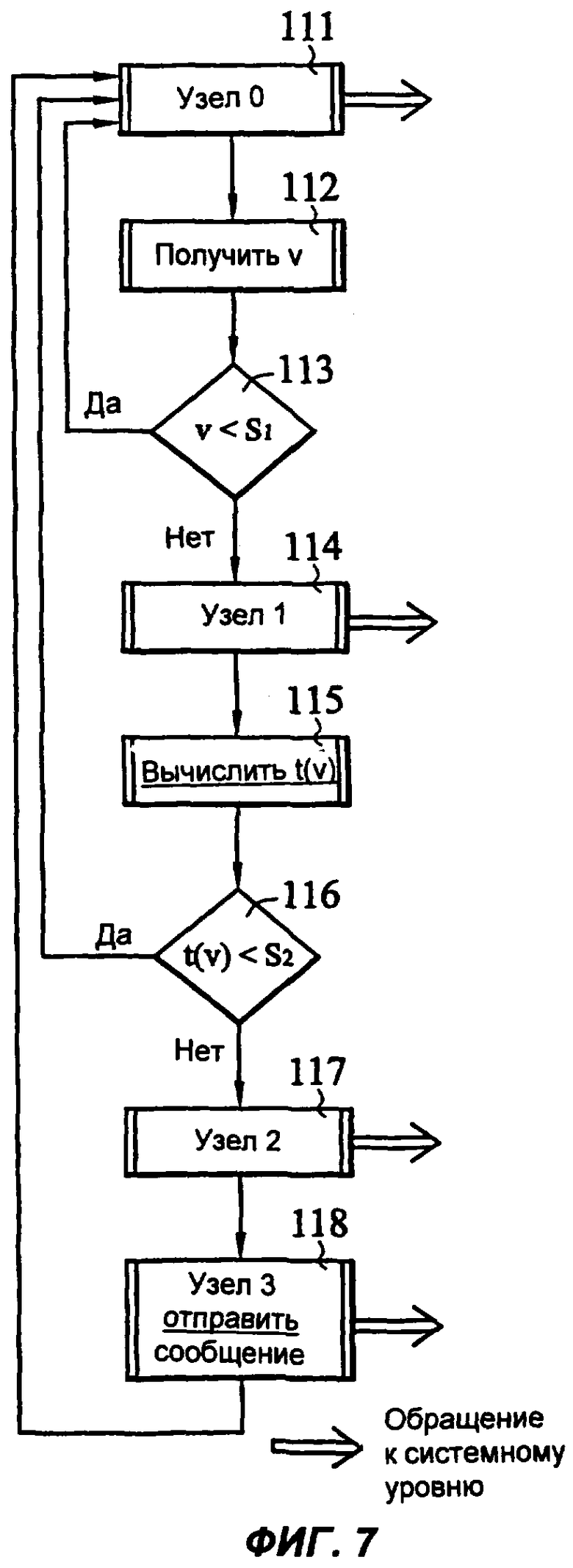

Фиг.7 представляет собой блок-схему, соответствующую обработке примера первой задачи реального времени, которая должна обмениваться информацией со второй задачей, в соответствии со способом обеспечения безопасности согласно изобретению.

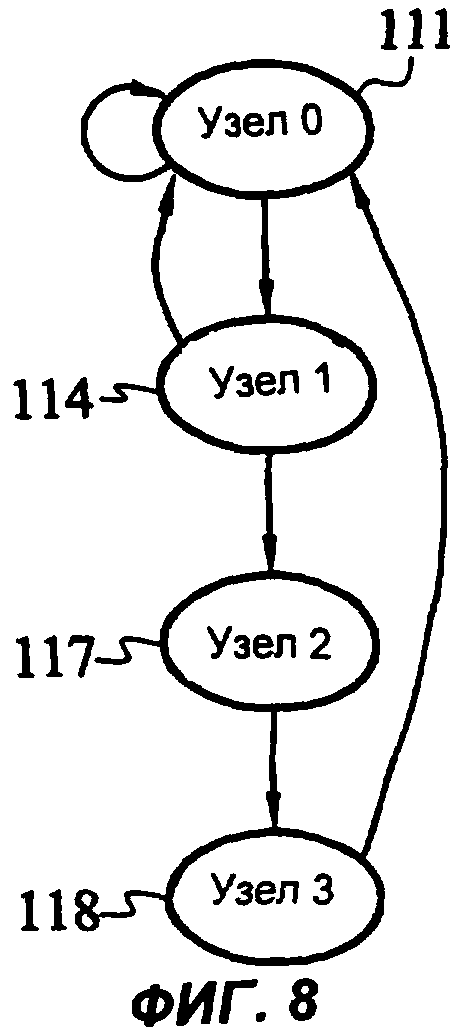

Фиг.8 - это управляющий граф, соответствующий схеме на фиг.7.

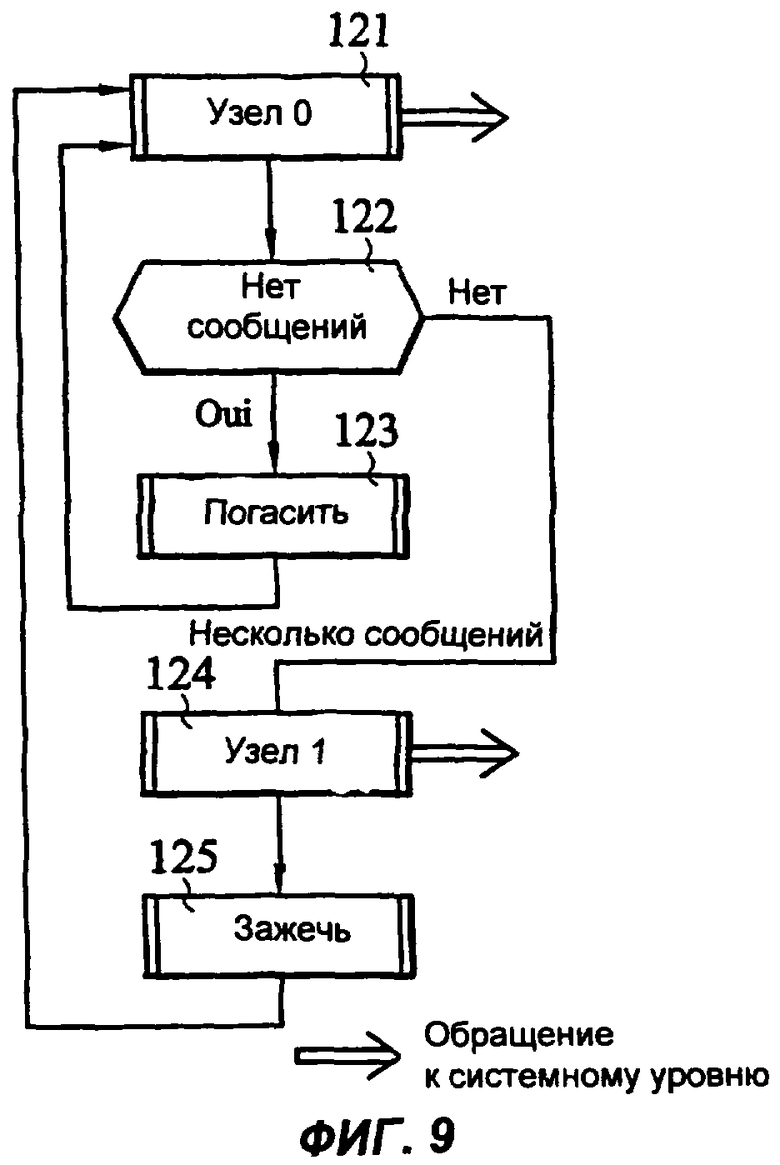

Фиг.9 представляет собой блок-схему, соответствующую обработке примера второй задачи реального времени, которая должна обмениваться информацией с первой задачей, схема которой показана на фиг.7.

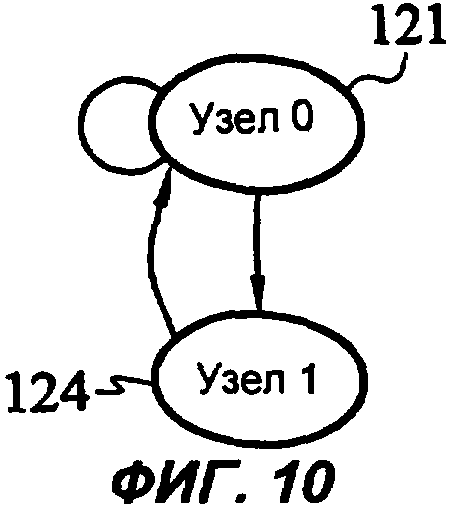

Фиг.10 - это управляющий граф, соответствующий схеме на фиг.9.

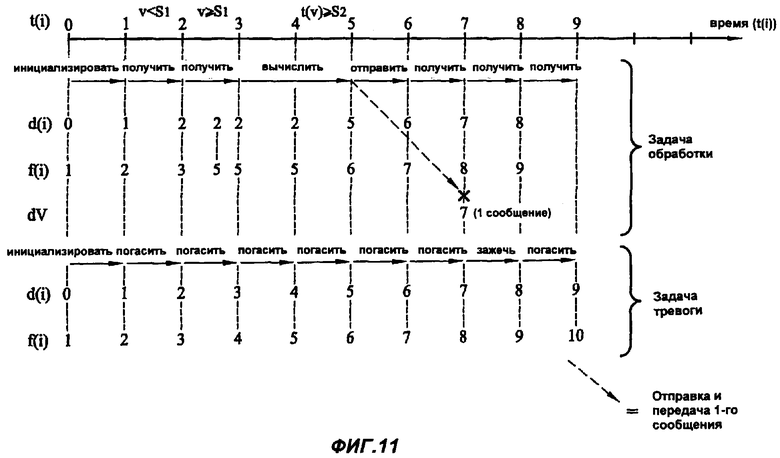

Фиг.11 представляет собой пример хронограммы и сопоставленных ей временных значений задач реального времени, представленных на фиг.7 и 10, в ходе обработки примера задач, обменивающихся информацией, в соответствии со способом обеспечения безопасности согласно изобретению.

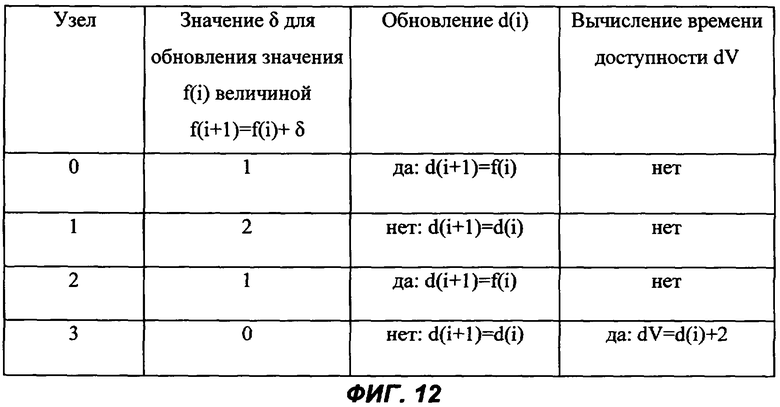

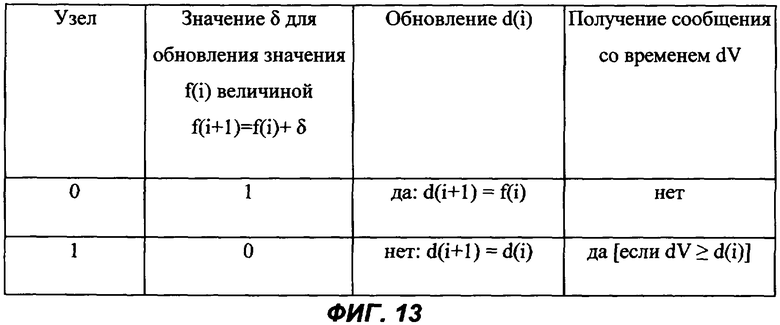

Фиг.12 и 13 суть таблицы узлов управляющих графов по фиг.8 и 10, содержащие описания операций, которые необходимо выполнить над моментами самого раннего времени d(i) начала и самого позднего времени f(i) завершения и над сообщениями.

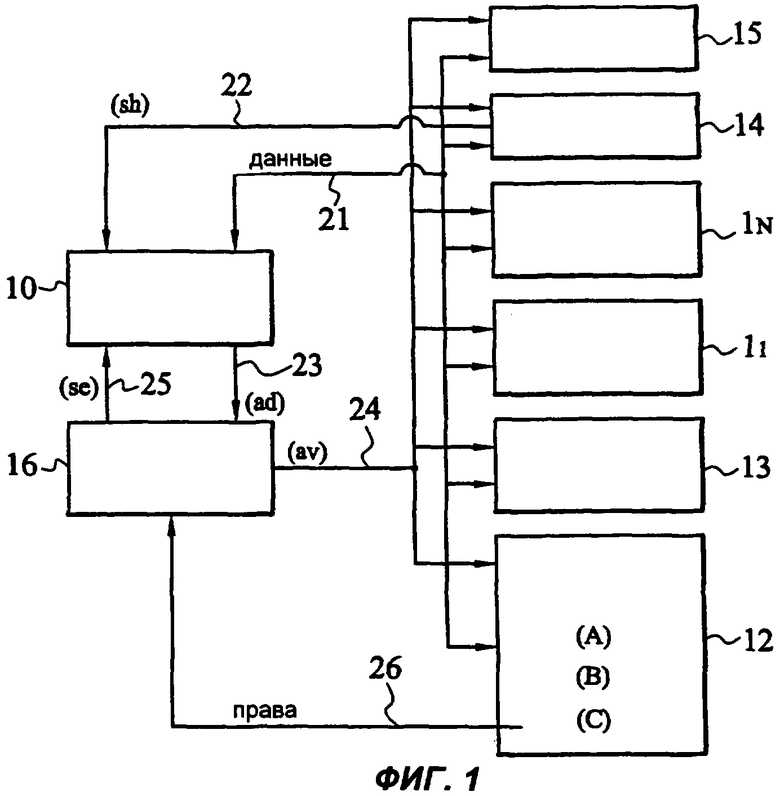

Фиг.14 представляет собой подробную таблицу, содержащую права доступа процессора к сегментам памяти, относящимся к задаче, к системному уровню и к микроядру в соответствии с примером способа согласно изобретению.

Осуществление изобретения

Опишем сначала, со ссылкой на фиг.1, пример упрощенной архитектуры системы управления, к которой применим способ обеспечения безопасности в соответствии с настоящим изобретением.

Система управления содержит, по меньшей мере, первичный системный таймер 14, который по линии 22 передает сигнал sh прерывания по истечении запрограммированного промежутка времени. Центральный вычислительный блок 10 содержит, по меньшей мере, один процессор, способный получать данные по линии 21 и сигнал sh прерывания по линии 22.

Центральный вычислительный блок 10 позволяет посылать по линиям 23 и 24 сигналы адресации в главную память, содержащую ПЗУ 12 и ОЗУ 13.

ПЗУ 12 основного устройства памяти содержит, по меньшей мере, информацию (А), содержащую программы рассматриваемых приложений, и информацию (В), содержащую данные и постоянные таблицы приложения.

ОЗУ 13 содержит рабочие переменные данные программ приложения.

Контроллеры 11-1N периферийных устройств 1-N позволяют обеспечить управление в реальном времени входами и выходами системы управления.

Может быть предусмотрен также второй системный таймер 15 для обеспечения дополнительного контроля нормального функционирования системного таймера 14.

Система управления может, кроме того, содержать устройство 16 защиты памяти, обеспечивающее контроль за правами доступа к адресации.

Исходя из запрошенного адреса ad, предоставленного центральным вычислительным блоком 10 устройству 16 защиты памяти по линии 23, и прав (С) доступа к контекстам выполнения процессора на адресуемом пространстве памяти, предоставленных по линии 26, связывающей ПЗУ 12 с устройством 16 защиты памяти, устройство 16 защиты памяти генерирует на линии 24, связанной с устройствами памяти 12, 13, с контроллерами периферийных устройств 11-1N и с таймерами 14, 15 подтвержденный эксклюзивный адрес av, который разрешает доступ, или же выдает по линии 25 центральному вычислительному блоку 10 сигнал se исключения неразрешенной адресации.

Устройство 16 защиты памяти может представлять собой механизм, присутствующий в стандартном устройстве управления памятью типа MMU ("Memory Management Unit"), причем это устройство управления памятью может быть само встроено в процессор центрального вычислительного блока 10.

Процессор центрального вычислительного блока 10, способный получать, по меньшей мере, сигнал sh прерывания системного таймера и сигнал se исключения неразрешенной адресации, обладает привилегированным режимом выполнения, доступ к которому защищен командой типа "обращение к системному уровню", например, командой ветвления ("trap").

Изобретение касается, в основном, системы управления с архитектурой с привязкой ко времени (ТТА - "Time Triggered Architecture") - многозадачной детерминированной безопасной системы реального времени с обменом как явными сообщениями (датированные сообщения), так и неявными (потоки датированных данных), причем синхронизация задач может быть как циклической, так и ациклической.

Точнее говоря, в соответствии со способом обеспечения безопасности согласно изобретению имеет место особый характер управления обращениями к системному уровню системы управления (посредством обращения к привилегированному режиму выполнения), причем этот особый характер управления позволяет обнаруживать и локализовывать ошибки с гарантией детерминированного и предсказуемого поведения.

Согласно изобретению управление обращениями к системному уровню происходит следующим образом:

i/ единственное обращение к системному уровню, разрешенное к выполнению из рассматриваемого приложения, состоит в учете изменения узла в управляющем графе рассматриваемой задачи;

ii/ системный уровень контролирует при этом законность этого вызова по отношению к пути выполнения управляющего графа, который описан в постоянных таблицах приложения;

iii/ если обращение является разрешенным, то все операции, которые системному уровню необходимо выполнить над рассматриваемым узлом, являются предопределенными постоянными таблицами соответствующего приложения системного уровня.

Предварительное планирование списков задач рассматриваемого приложения осуществляется перед выполнением в реальном времени на уровне элементарного микроядра, которое впоследствии обеспечит, будучи вызванным из системного уровня в ходе выполнения в реальном времени, обновление списков задач упорядоченным способом в соответствии с новыми временными характеристиками задач, а именно самым ранним временем d(i) начала и самым поздним временем f(i) завершения, вычисленными системным уровнем.

Основной способ обеспечения безопасности согласно изобретению включает в себя, прежде всего, следующие операции:

(а) запоминают для каждой из задач данного приложения все разрешенные сцепления ее точек временной синхронизации, требующие обращения к системному уровню, причем эти сцепления представляются управляющим графом выполнения обращений рассматриваемой задачи к системному уровню, а каждый граф содержит совокупность узлов, каждый из которых соответствует обращению к системному уровню системы управления,

(b) для каждого узла управляющего графа каждой задачи запоминают природу обращения к системному уровню и его параметры вызова, в том числе временные параметры, которые позволили бы обновить значения "самого раннего времени начала" d(i) и "самого позднего времени завершения" f(i),

(c) запоминают для каждой задачи начальный узел (Узел 0) в соответствующем графе,

(d) инициализируют для данного приложения и перед запуском выполнения в реальном времени в соответствии с режимом работы с привязкой ко времени для каждой задачи начальный узел (Узел 0) и начальный момент, представляющие начальное состояние рассматриваемой задачи,

(e) инициализируют для данного приложения и перед запуском выполнения в реальном времени в соответствии с режимом работы с привязкой ко времени порядок запуска каждой задачи путем выполнения предварительного упорядочения списков задач на уровне элементарного микроядра,

(f) устанавливают первичный системный таймер 14 для выдачи сигнала sh прерывания таймера, содержащего обращение к микроядру, в первый момент работы приложения для запуска выполнения этого приложения в режиме работы с привязкой ко времени,

(g) в ходе нормальной работы после установки первичного системного таймера 14, вызывают сброс первичного системного таймера 14 микроядром при каждом обращении к микроядру; при обращении к микроядру со стороны системного уровня или при обработке сигнала sh прерывания переводят микроядро на операцию упорядоченного обновления списков задач с учетом временных характеристик задач, а именно, самого раннего времени d(i) начала и самого позднего времени f(i) завершения; вычисляют при помощи микроядра, после обновления списков, ближайший момент времени в будущем, когда задача должна будет стать активизированной, и устанавливают при помощи микроядра первичный системный таймер 14, начиная с этого ближайшего момента времени в будущем, чтобы активизировать указанную задачу и выйти из микроядра.

(h) во время выполнения задачи осуществляют вызов к системному уровню, только когда будет достигнут узел управляющего графа указанной задачи, принимая в качестве аргумента номер узла; при входе в системный уровень проверяют, является ли, в соответствии с управляющим графом выполняемой задачи, разрешенным сцепление, начиная с узла, соответствующего предыдущему обращению к системному уровню, с тем чтобы запустить на системном уровне обработку ошибки, если указанное сцепление не разрешено, и продолжить выполнение, если указанное сцепление разрешено, осуществляют обновление временных параметров задачи в ходе выполнения, включающих в себя самое раннее время d(i) начала и самое позднее время f(i) завершения, при помощи обращения системного уровня к микроядру, и продолжают в нормальных условиях выполнение текущей задачи до того момента, пока она снова не достигнет узла своего управляющего графа.

Как было указано выше, система управления, к которой применяется способ обеспечения безопасности согласно изобретению, может содержать устройство защиты памяти и таблицы прав доступа для каждого сегмента каждого контекста, которые являются детерминированными и могут при необходимости быть помещены в ПЗУ. Для каждого из контекстов выполнения инициализация дескриптора таблиц, задающая права этого контекста, выполняется только один раз в фазе инициализации всей системы и после этой фазы инициализации системы никакая из обработок, выполняемых на центральном вычислительном устройстве, не имеет этих таблиц в своем контексте выполнения.

Способ обеспечения безопасности согласно изобретению может содержать, кроме того, следующие операции, которые добавляются к операциям, определенным ранее:

(i) на стадии подготовки для данного приложения запоминают права доступа к каждому сегменту памяти для микроядра, а также для каждой задачи приложения и ее продолжения на системный уровень, с тем чтобы образовать первый и второй контексты выполнения в соответствии с тем, находятся ли команды собственно в коде приложения, образующего задачу, или же эти команды находятся в общем коде системного уровня, составляющем продолжение задачи на системный уровень,

(j) для данного приложения и перед запуском выполнения в реальном времени в соответствии с режимом работы с привязкой ко времени инициализируют контекст микроядра, а также первый и второй контексты выполнения для каждой задачи и ее продолжения на системный уровень,

(k) в ходе выполнения задачи осуществляют обращение к системному уровню при помощи команды перехода в привилегированный режим выполнения, который позволяет переходить из контекста выполнения задачи в контекст выполнения ее продолжения на системный уровень, а после проверки разрешенности сцепления, начиная с узла, соответствующего предыдущему системному вызову, и после обновления временных параметров задачи при помощи обращения системного уровня к микроядру, обеспечивают возврат в код задачи при помощи команды возврата в непривилегированный режим, который позволяет перейти от контекста выполнения продолжения на системный уровень к контексту выполнения задачи.

Способ обеспечения безопасности согласно изобретению может также ссылаться на временные квоты и тогда содержать следующие дополнительные операции, которые добавляются к ранее определенным операциям основного процесса или модифицированного основного процесса, чтобы учитывать существование привилегированных режимов выполнения, позволяющих перейти к контексту выполнения продолжения задачи на системный уровень:

(l) в фазе подготовки запоминают для данного приложения и для всех сцеплений, разрешенных для каждой задачи, временную квоту, представляющую собой верхнюю оценку максимального времени выполнения, необходимого для перехода от одного узла к другому в управляющем графе задачи, причем каждая временная квота включает в себя время, затраченное на выполнение команд собственно задачи, а также время на выполнение общего кода системного уровня в продолжении задачи,

(m) при нормальном функционировании после установки первичного системного таймера 14 при обращении к микроядру, вызванном сигналом sh прерывания по времени и вызывающем сброс первичного системного таймера 14, приступают к проверке, связан ли сигнал sh прерывания по времени, вызывающий обращение к микроядру, с попыткой нарушения временной квоты, и если это так, то запускают посредством микроядра обработку ошибки. Если же сигнал sh прерывания по времени не связан с попыткой нарушения временной квоты, то переводят микроядро на операцию обновления списков задач и после этого обновления списков задач вычисляют при помощи микроядра, с одной стороны, ближайший момент времени в будущем, когда одна из задач должна быть активизирована, и с другой стороны, момент времени в будущем, начиная с которого временная квота, отведенная выполняемой задаче при выходе из микроядра, определенном при обновлении списков, будет исчерпана. Первичный системный таймер 14 устанавливают при помощи микроядра на ближайший из этих моментов в будущем, с тем чтобы, в соответствии с условиями, либо активизировать задачу, либо распознать попытку нарушения временной квоты, обнаружив ошибку в функционировании, и выйти из микроядра после установки первичного системного таймера 14.

Процедура обновления списков задач приложения на уровне микроядра может также быть снабжена приводимым ниже пояснением, в котором учитывается предпочтительный режим реализации с использованием временной квоты, отведенной обрабатываемой задаче, но который также может применяться к упрощенному базовому режиму реализации, если опустить ссылку на временную квоту.

Для каждого обращения к микроядру в ходе выполнения, каким бы ни было продолжение контекста выполнения рассматриваемой задачи на системный уровень, для обновления списков задач необходим учет двух параметров: самого раннего времени d(i) начала и самого позднего времени f(i) завершения. Происходит управление двумя списками задач: списком задач, готовых к выполнению, то есть задач, для которых самое раннее время d(i) начала находится в прошлом, и списком задач, не готовых к выполнению или находящихся в ожидании активизации, то есть задач, для которых самое раннее время d(i) начала находится в будущем. Список готовых к выполнению задач упорядочен по возрастанию самого позднего времени f(i) завершения; список не готовых к выполнению задач упорядочен по возрастанию самого раннего времени d(i) начала.

Любая задача, находящаяся в ожидании, гарантированно перейдет в состояние "готовности" по достижении своего самого раннего времени начала.

α) Если при обращении к микроядру время самого раннего времени d(i) начала задачи находится в будущем, то задача является не готовой к выполнению и переводится в упорядоченный список таких задач. Это время позволяет вычислить ближайший момент, когда задача сможет быть активизирована в соответствии с порядком самых ранних времен начала: ближайшее самое малое время начала явится моментом времени в будущем, когда ближайшая задача перейдет в состояние готовности (сможет стать активизированной).

β) Если, напротив, при обращении к микроядру время самого раннего времени d(i) начала рассматриваемой задачи находится в прошлом, то задача является готовой к выполнению и переводится в упорядоченный список таких задач. Микроядро тогда обращается к той готовой к выполнению задаче, которая обладает наименьшим из самых поздних времен завершения в упорядоченной последовательности самых поздних времен завершения, и вычисляет момент времени в будущем, начиная с которого временная квота, отведенная выбранной задаче, будет исчерпана (квота есть разность между ближайшим самым поздним временем завершения и текущим временем).

γ) Тем не менее, если обращение к микроядру вызвано системным таймером 14 в случае установки для временной квоты, отведенной обрабатываемой задаче, то тогда микроядро выполняет сначала действие по обработке ошибки, предусмотренное приложением, а затем действия α и β.

Микроядро, исходя из этих двух моментов (ближайший момент в будущем активизации задачи и момент в будущем исчерпания временной квоты, отведенной выбранной задаче), устанавливает системный таймер 14 так, чтобы активизировать его в ближайший из этих двух моментов (либо вовремя активизировать задачу, либо распознать попытку нарушения временной квоты, то есть ошибку в работе). После установки системного таймера 14 осуществляется выход из микроядра, возможно, с переключением.

Таким образом в ходе выполнения смена активной задачи осуществляется либо по прерыванию по времени, либо вслед за сменой узла для активной задачи.

Причиной прерывания по времени может быть как то, что задача в ожидании перешла в состояние готовности (учитывая привязку ко времени), так и то, что активная задача исчерпала свою временную квоту, причем в этом случае осуществляется контроль надежности.

Когда активная задача меняет узел на своем управляющем графе, то отодвигается или самое позднее время завершения, или самое раннее время начала. В первом случае другая задача способна активизироваться вместо нее. Во втором случае активная задача помещается в множество задач в состоянии ожидания, если ее новое самое раннее время начала находится в будущем.

Число приоритетных вытеснении является конечным и ограниченным, и можно аналитически вычислить его максимальную верхнюю границу.

С другой стороны, по мере того, как временные квоты обновляются и контролируются при каждой смене узла, можно вовремя обнаружить ошибки, с тем чтобы немедленно локализовать задачу.

В той мере, в какой принимаются только возможные перемещения по управляющему графу, поведение задачи по времени не может привести к потреблению больших ресурсов (например, ресурсов памяти для связи), чем статически оцененные при помощи того же графа.

Опишем теперь со ссылкой на фиг.3-6 пример осуществления способа обеспечения безопасности согласно изобретению для конкретной задачи в реальном времени.

В соответствии с этим примером функция задачи реального времени состоит в подаче сигнала тревоги, если измеренное значение таково, что v превышает пороговое значение s1 в течение времени t(v), превышающего пороговое значение s2.

На фиг.3 представлена блок-схема процесса обработки соответствующей задачи.

Через 101 обозначен начальный узел, или Узел 0, на уровне которого происходит обращение к системному уровню.

Обозначение 102 соответствует первой операции (первому шагу) получения измеренного значения v.

Через 103 обозначена проверка, в результате которой происходит возврат к начальному узлу 101, а затем к шагу 102, если v<s1, и, напротив, происходит переход к первому узлу (обозначенному, как 104), а затем к шагу 105, если v≥s1.

На уровне узла 104 происходит обращение к системному уровню, а на шаге 105 вычисляется длительность t(v).

После шага 105 проверка 106 позволяет вернуться к начальному узлу 101, если t(v)<s2, и перейти ко второму узлу (обозначенному, как 107), если t(v)≥s2.

После второго узла 107, где происходит обращение к системному уровню, происходит переход к шагу 108 подачи сигнала тревоги, в результате чего происходит возврат к начальному узлу 101.

На фиг.4 представлен управляющий граф с узлами 101, 104, 107 и дугами, соответствующими схеме по фиг.3.

В рассматриваемом примере сроки, отведенные для выполнения операций "получить v" (шаг 102), "вычислить t(v)" (шаг 105) и "выдать сигнал тревоги" (шаг 108) имеют следующие значения:

Для каждого из узлов 101, 104, 107 ниже указаны действия, выполняемые системным уровнем, и операции, выполненные над самым ранним временем d(i) начала и самым поздним временем f(i) завершения, учитывая то, что при инициализации самое раннее время начала d(0)=0, а самое позднее время завершения f(0)=1 в единицах времени.

ii) затем установить новый срок

ii) затем установить новый срок

Фиг.6 есть представление таблицы узлов 0, 1 и 2 с описанием операций, которые необходимо выполнить над моментами самого раннего времени d(i) начала и самого позднего времени f(i) завершения.

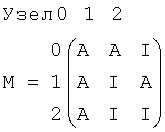

С другой стороны, управляющий граф задачи, соответствующей фиг.4, может быть представлен для вышеуказанного примера в матричной форме следующим образом:

где mij=А, если перемещение из узла i в узел j разрешено, и

mij=I, если перемещение из узла i в узел j запрещено.

На фиг.5 представлена хронограмма примера задачи реального времени, описанной выше, в которой фигурируют соответствующие временные значения. Числа от 1 до 10 означают реальное время, выраженное в единицах времени, с момента начала работы в режиме с привязкой ко времени.

В ходе нормальной работы после установки первичного системного таймера 14 вызывают сброс первичного системного таймера 14 микроядром при каждом обращении к микроядру. При обращении к микроядру со стороны системного уровня или при обработке сигнала sh прерывания переводят микроядро на операцию упорядоченного обновления списков задач с учетом временных характеристик задач, а именно, самого раннего времени d(i) начала и самого позднего времени f(i) завершения. Далее, вычисляют при помощи микроядра, после обновления списков задач, ближайший будущий момент времени, по истечении которого одна из задач должна будет стать активизированной, и устанавливают при помощи микроядра первичный системный таймер 14, начиная с этого ближайшего будущего момента времени, чтобы активизировать указанную задачу и выйти из микроядра.

Во время выполнения задачи осуществляют вызов к системному уровню, только когда будет достигнут узел управляющего графа указанной задачи, принимая в качестве аргумента номер узла. При входе в системный уровень проверяют, является ли, в соответствии с управляющим графом выполняемой задачи, разрешенным сцепление, начиная с узла, соответствующего предыдущему обращению к системному уровню, с тем чтобы запустить на системном уровне обработку ошибки, если указанное сцепление не разрешено, и продолжить выполнение, если указанное сцепление разрешено. При этом осуществляют обновление временных параметров самое позднее время f(i) завершения, при помощи обращения системного уровня к микроядру, и продолжают в нормальных условиях выполнение текущей задачи до того момента, пока она снова не достигнет узла своего управляющего графа.

Способ обеспечения безопасности согласно изобретению адаптирован также к тому, чтобы сделать детерминированным выполнение в реальном времени многозадачных приложений, обменивающихся сообщениями между собой.

В этом случае процесс включает в себя следующие специфические операции, которые добавляются к операциям, описанным ранее для случая основного процесса с многозадачными приложениями без указания на обмен сообщениями между задачами:

n) на стадии подготовки запоминают для каждой из задач данного приложения все разрешенные сцепления его точек временной синхронизации и связи с другими задачами, требующие обращения к системному уровню, причем эти разрешенные сцепления представляются управляющим графом выполнения обращений рассматриваемой задачи к системному уровню, а каждый граф содержит совокупность узлов, каждый из которых соответствует обращению к системному уровню,

о) запоминают каждую буферную область, необходимую для обмена данными между задачами, указав ее размер, размер содержащихся в ней элементов, ее размещение или базовый адрес, а также связи между буферными зонами, позволяющими подтвердить достоверность обмена информацией, необходимого для связи,

р) запоминают для каждой буферной зоны начальные значения ее элементов,

q) инициализируют, для данного приложения и предварительно при пуске выполнения в реальном времени в соответствии с режимом работы с привязкой ко времени, значения элементов буферной зоны значениями, предварительно занесенными в память,

r) во время выполнения задачи при обращении к системному уровню, когда будет достигнут узел управляющего графа задачи, и после проверки того, что в соответствии с управляющим графом выполняемой задачи сцепление, начиная с узла, соответствующего предыдущему обращению к системному уровню, является разрешенным, осуществляют последовательные обновления буферных зон в соответствии с природой вызова, предварительно занесенного в память, а также необходимые инкрементные обновления временных параметров выполняемой задачи, включающих моменты самого раннего времени d(i) начала и самого позднего времени f(i) завершения.

В случае, если первый или второй контексты выполнения определены для каждой задачи приложения и ее продолжения на системный уровень, имеют место, кроме того, следующие особенности.

На системном уровне разрешено совместное использование одних буферных зон продолжениями контекстов выполнения задач приложения, а буферная зона, отведенная для динамических сообщений, соответствующих отправке сообщений, может быть совместно использована только двумя продолжениями контекстов выполнения задачи, в то время как буферная зона, отведенная для статических сообщений, соответствующих потоку датированных данных, может быть совместно использована более чем двумя продолжениями контекстов выполнения задачи, однако по-прежнему она может быть записана или изменена только одним контекстом.

Опишем теперь со ссылкой на фиг.7-13 пример применения способа обеспечения безопасности согласно изобретению к реализации двух задач реального времени, обменивающихся сообщениями.

В этом простом примере реализованная функция состоит в зажигании сигнальной лампы, если измеренное значение v таково, что v превышает пороговое значение s1, и если длительность t(v) превышения порога s1 измеренной величиной v сама превышает пороговое значение s2.

Задача обработки осуществляет, таким образом, получение значения v и отправляет при необходимости сообщение задаче сигнализации, которая зажигает указанную лампу.

На фиг.7 представлена блок-схема задачи обработки для рассматриваемого примера.

Через 111 обозначен начальный узел, или Узел 0, для которого происходит обращение к системному уровню.

Первый шаг 112 представляет собой операцию получения значения измеренной величины v, с которой связана проверка 113, где значение v сравнивается с пороговым значением s1.

Если v<s1, то происходит возврат к начальному узлу 111, а в случае v≥s1 происходит переход к первому узлу (обозначенному, как 114), на котором происходит обращение к системному уровню.

На втором шаге 115, следующем за узлом 114, вычисляется длительность t(v).

В процессе проверки 116, связанной с шагом 115, происходит сравнение длительности t(v) с пороговым значением s2.

Если t(v)<s2, то происходит возврат к начальному узлу 111, а если t(v)≥s2, то происходит переход ко второму узлу (обозначенному, как 117), который осуществляет обращение к системному уровню.

После узла 117 происходит переход к третьему узлу (обозначенному, как 118), на котором происходит обращение к системному уровню, и выполняется третий шаг, состоящий в подаче сигнала тревоги перед возвращением в начальный узел 111.

На фиг.8 представлен управляющий граф, соответствующий блок-схеме на фиг.7, с разрешенными узлами и дугами.

На фиг.9 представлена схема, соответствующая выполнению задачи сигнализации из рассматриваемого примера.

Через 121 обозначен начальный узел, или Узел 0, для которого происходит обращение к системному уровню.

Проверка 122 определяет, было ли получено сообщение.

Если никакое сообщение не было получено, то происходит переход к шагу 123 выключения сигнальной лампы и возврата к начальному узлу 121.

Если имеется одно или несколько сообщений, то происходит переход к первому узлу 124 с обращением к системному уровню, и переход к шагу 125 зажигания сигнальной лампы перед возвратом к начальному узлу 121.

На фиг.10 представлен управляющий граф, соответствующий блок-схеме на фиг.9, с разрешенными узлами и дугами.

В рассматриваемом примере сроки, отведенные для выполнения операций "получить t(v)", "вычислить t(v)", "отправить сообщение", "погасить", "зажечь", соответствующие операциям 112, 115, 118, 123 и 125, имеют следующие значения:

Ниже для каждого узла каждой из двух задач указаны действия, выполняемые системным уровнем, и операции, выполненные над самым ранним временем d(i) начала и самым поздним временем f(i) завершения, (с начальными значениями d(0)=0 и f(0)=1), а также время dV доступности сообщений.

На фиг.12 и 13 представлены, соответственно для задачи обработки и задачи сигнализации из рассматриваемого примера, таблицы узлов, содержащие описание операций, которые необходимо выполнить над самым ранним времени d(i) начала, самым поздним временем f(i) завершения и временем доступности dV.

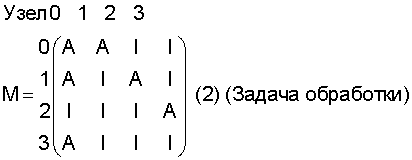

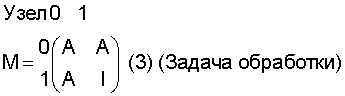

Управляющие графы задачи обработки и задачи сигнализации могут кодироваться в матричной форме следующим образом:

где mij=А, если перемещение из узла i в узел j разрешено, и

mij=I, если перемещение из узла i в узел j запрещено.

Фиг.11 представляет собой хронограмму реализации двух описанных сообщающихся между собой задач с отображением соответствующих временных значений. Цифры от 1 до 10 означают реальное время, выраженное в единицах времени, с момента начала работы в режиме с привязкой ко времени.

В данной очереди сообщений находятся сообщения единственного и уникального типа. Время dV доступности сообщения сопоставляется каждому отправляемому сообщению. Время dV уточняет момент в будущем, начиная с которого получатель может принять сообщение. Сообщения принимаются по порядку времени доступности dV, затем по имени отправителя и, наконец, по порядку отправки, что позволяет полностью упорядочить сообщения для их получения.

Для каждой очереди сообщений существуют зона отправки в контексте каждого отправителя и зона получения для владельца соответствующей очереди сообщений.

Наличие у каждого автора (отправителя) своей зоны отправки исключает проблему конфликта между двумя отправками сообщений двумя задачами.

С другой стороны, как было указано, сегментация памяти позволяет ограничить влияние сбоев задачи на ее собственное пространство памяти. Поэтому распространение сбоя задачи на другие задачи приложения невозможно.

Использование сегментации памяти позволяет, с другой стороны, получить следующее свойство: в пределах временного интервала привязки (ТТ) задачи ко времени контекст выполнения этой задачи не меняется между началом новой команды и завершением предшествующей ей команды.

Сегментация памяти применяется к самому системному уровню, с тем чтобы разграничить его изнутри, а также отделить микроядро от остальной части системного уровня.

Устройство 16 защиты памяти представляет собой физическое устройство, позволяющее производить проверку того, что сегментация памяти действительно осуществлена с точки зрения физической архитектуры.

На фиг.2 представлено распределение по глубине кода, порожденного от уровня 201 приложения в пользовательском режиме выполнения, или непривилегированном режиме, до микроядра 203, включая системный уровень 202 с привилегированным режимом выполнения.

Доступ к системному уровню 202 в привилегированном режиме выполнения защищен командой ветвления типа "trap", а переход от системного уровня к микроядру 203 порождается командой типа перехода.

Системный таймер 14 обеспечивает привязку ко времени и вырабатывает сигнал sh прерывания таймера по истечении заданного регулируемого промежутка времени.

Таким образом, из фиг.2 можно видеть, что на уровне 201 приложений содержатся код и данные различных задач, тогда как на системном уровне 202 находятся, с одной стороны, продолжения контекстов задач на системный уровень, и, с другой стороны, код системного уровня. На уровне микроядра 203 находятся данные и код микроядра для управления распределением ресурсов процессора по задачам, а также для управления временем.

Дадим теперь, со ссылкой на фиг.14, подробную таблицу прав различных сегментов на примере реализации способа обеспечения безопасности с сегментированной памятью согласно изобретению.

Как уже было показано, многозадачное приложение содержит собственный код, задачи, потоки временных переменных, буфера связи, системный уровень, обеспечивающий передачу информации между задачами, устройство выполнения графа, контролирующее перемещения задач в коде приложения, и микроядро, обеспечивающее управление по времени и распределение ресурсов процессора.

Память делится на сегменты с правами доступа, зависящими от контекста выполнения процессора.

В пояснение таблицы на фиг.14 дадим следующие определения:

.inst: набор последовательных команд в памяти;

.const: набор последовательных данных с постоянными значениями;

.var: набор последовательных данных, изменяемых при помощи команд;

I: право на выполнение команд сегмента;

М: право на изменение и чтение сегмента;

С: право доступа к сегменту ограничено чтением;

R: право доступа к сегменту отсутствует.

Сегменты сгруппированы в зоны в соответствии с тем, являются ли они специфичными для приложения или связаны с моделью согласно изобретению на вычислительном устройстве 10 с его процессором.

Для каждой задачи имеются последовательные зоны приложений СТ, FT, ВМ, ME, VT и PU. Описание этих зон приложения следует ниже:

Зона СТ расчетов задачи:

.const и.var: данные задачи со стеком в непривилегированном режиме;

.inst: расчеты задачи.

Зона FT функционирования задачи:

.const: описание функционирования задачи (граф выполнения, описание узлов, сроки выполнения, верхние оценки времени расчета центральным вычислительным блоком);

.var: зона перехода аргументов на системный уровень;

.inst: функции запроса к системному уровню на изменение узла.

Зона ВМ буфера связи:

.const: характеристики каждого буфера связи задачи, в том числе связей с зонами отправки (зонами ME);

.var: множество сообщений, доступных задаче в текущий момент.

Зона ME хранения сообщений:

.const: описание зон хранения сообщений, отправленных задачей и недоступных задачам-получателям;

.var: сами зоны хранения сообщений.

Зона VT временных переменных:

.const: описание зон хранения для задачи, значений потоков временных переменных, доступных для задачи, в том числе связей с зонами производителей значений;

.var: зоны хранения для задачи прошлых доступных значений.

Зона PU:

.var: временные рабочие значения, необходимые для процессора, текущий контекст задачи, стековая память в привилегированном режиме.

Имеется также Глобальная зона приложения, общая для задач, описание которой приводится ниже:

Глобальная зона G:

.const: описание глобальных констант приложения (число задач, ссылки на дескрипторы задач, описания таймеров...) и констант интерфейса с системным уровнем.

Сам системный уровень включает зону CS.

Зона CS системного уровня:

.const: для памяти;

.var: пустая (прошлое записано в сегменте.var зоны PU);

.inst: команды выполнения графа, управления буферами связи, предоставления прошлых значений потоков временных переменных и команд управления таймерами и расчета сроков выполнения.

Описание зоны передачи TR, общей с системным уровнем:

Зона передачи TR:

.const: для памяти;

.var: идентификация активной задачи

.inst: команды смены прав доступа к памяти для аппаратных средств и подключения к системному уровню или микроядру.

Микроядро включает зоны MN и RS.

Зона MN:

.const: для памяти;

.var: данные, необходимые для управления аппаратными средствами (управление временем, управления командами "trap"...)

.inst: команды управления множествами задач, готовых или находящихся в состоянии покоя в зависимости от сроков выполнения, сохранения и изменения аппаратного контекста, управления прерыванием по системному таймеру для прав доступа на исчерпавший возможности процессор, а также приведения в действие защиты памяти, доступной на вычислительном устройстве.

Зона RS:

.const: для памяти;

.var: пустая;

.inst: команды инициализации вычислительного устройства и программного обеспечения, которые выполняются без защиты памяти.

В заданный момент времени процессор выполняет команды либо для задачи в коде приложений (в непривилегированном режиме), либо для задачи в системном уровне (в привилегированном режиме), либо в микроядре.

Таблица на фиг.14 представляет собой расположенные в линию сегменты задачи, затем сегменты системного уровня и, наконец, сегменты микроядра, как это было определено выше. Столбцы представляют собой права доступа к памяти в соответствии с тем, выполняет ли процессор команды кода приложения данной задачи (столбец 301), кода системного уровня для данной задачи (столбец 302), кода системного уровня для другой задачи (столбец 303), кода для микроядра после инициализации вычислительного устройства (столбец 304).

В целом память может быть разбита на страницы, а страница может быть защищенной от записи, отсутствовать или быть доступной. В этом случае размер сегментов будет округлен до целого числа страниц,.const и.var будут объединены и защищены от записи, а страницы с правами R будут либо отсутствовать, либо изъяты из описания.

Настоящее изобретение относится к способу обеспечения безопасности, обеспечивающему детерминированность выполнения в реальном времени многозадачных приложений типа управление-регулирование в системе управления. Технический результат заключается в одновременном обеспечении детерминированности и многозадачности. Способ реализован в системе управления с архитектурой с привязкой ко времени. Единственное обращение к системному уровню, разрешенное для выполнения из рассматриваемого приложения, состоит в учете изменения узла в управляющем графе рассматриваемой задачи. Все операции, которые необходимо выполнить системному уровню на рассматриваемом узле, являются предопределенными постоянными таблицами соответствующего приложения системного уровня. Предварительное упорядочение списков задач приложения осуществляется на уровне микроядра, которое затем обеспечит, будучи вызванным из системного уровня, упорядоченное обновление списка задач в соответствии с новыми временными характеристиками задач: самым ранним временем d(i) начала и самым поздним временем f(i) завершения, вычисленными системным уровнем. 8 з.п. ф-лы, 14 ил., 1 табл.

а) для каждой из задач данного приложения запоминают все разрешенные сцепления его точек временной синхронизации, требующие обращения к системному уровню, причем эти сцепления представляются управляющим графом выполнения обращений рассматриваемой задачи к системному уровню, а каждый граф содержит совокупность узлов, каждый из которых соответствует обращению к системному уровню системы управления,

b) для каждого узла управляющего графа каждой задачи запоминают природу обращения к системному уровню и его параметры вызова, в том числе временные параметры, которые позволили бы обновить значения "самого раннего времени начала" d(i) и "самого позднего времени завершения" f(i),

c) запоминают для каждой задачи начальный узел (Узел 0) в соответствующем графе,

d) инициализируют для данного приложения и перед запуском выполнения в реальном времени в соответствии с режимом работы с привязкой ко времени для каждой задачи начальный узел (Узел 0) и начальный момент, представляющие начальное состояние рассматриваемой задачи,

e) инициализируют для данного приложения и перед запуском выполнения в реальном времени в соответствии с режимом работы с привязкой ко времени порядок запуска каждой задачи путем выполнения предварительного упорядочения списка задач на уровне элементарного микроядра,

f) устанавливают первичный системный таймер (14) для выдачи сигнала (sh) прерывания таймера, содержащего обращение к микроядру, в первый момент работы приложения для запуска выполнения этого приложения в режиме работы с привязкой ко времени,

g) в ходе нормальной работы после установки первичного системного таймера (14) вызывают сброс первичного системного таймера (14) микроядром при каждом обращении к микроядру; при обращении к микроядру со стороны системного уровня или при обработке сигнала (sh) прерывания переводят микроядро на операцию упорядоченного обновления списков задач в соответствии с учетом временных характеристик задач, а именно, самого раннего времени d(i) начала и самого позднего времени f(i) завершения; вычисляют при помощи микроядра, после обновления списков задач ближайший будущий момент времени, по истечении которого одна из задач должна будет стать активизированной, и устанавливают при помощи микроядра первичный системный таймер (14), начиная с этого ближайшего будущего момента времени, чтобы активизировать указанную задачу и выйти из микроядра,

h) во время выполнения задачи осуществляют вызов к системному уровню, только когда будет достигнут узел управляющего графа указанной задачи, принимая в качестве аргумента номер узла; при входе в системный уровень проверяют, является ли, в соответствии с управляющим графом выполняемой задачи, разрешенным сцепление, начиная с узла, соответствующего предыдущему обращению к системному уровню, с тем, чтобы запустить на системном уровне обработку ошибки, если указанное сцепление не разрешено, и продолжить выполнение, если указанное сцепление разрешено, осуществляют обновление временных параметров задачи в ходе выполнения, включающих в себя самое раннее время d(i) начала и самое позднее время f(i) завершения, при помощи обращения системного уровня к микроядру, и продолжают в нормальных условиях выполнение текущей задачи до того момента, пока она снова не достигнет узла своего управляющего графа.

i) на стадии подготовки запоминают для данного приложения права доступа к каждому сегменту памяти для микроядра, а также для каждой задачи приложения и его продолжения на системный уровень для того, чтобы образовать первый и второй контексты выполнения в соответствии с тем, находятся ли команды собственно в коде приложения, образующего задачу, или же эти команды находятся в общем коде системного уровня, составляющем продолжение задачи на системный уровень,

j) для данного приложения и перед запуском выполнения в реальном времени в соответствии с режимом работы с привязкой ко времени инициализируют контекст микроядра, а также первый и второй контексты выполнения для каждой задачи и ее продолжения на системный уровень,

k) в ходе выполнения задачи осуществляют обращение к системному уровню при помощи команды перехода в привилегированный режим выполнения, который позволяет переходить из указанного первого контекста выполнения задачи в указанный второй контекст выполнения ее продолжения на системный уровень, а после проверки разрешенности сцепления, начиная с узла, соответствующего предыдущему системному вызову, и после обновления временных параметров задачи при помощи обращения системного уровня к микроядру, обеспечивают возврат в код задачи при помощи команды возврата в непривилегированный режим, который позволяет перейти от контекста выполнения продолжения на системный уровень к контексту выполнения задачи.

l) в фазе подготовки запоминают для данного приложения и для всех сцеплений, разрешенных для каждой задачи, временную квоту, представляющую собой верхнюю оценку максимального времени выполнения, необходимого для перехода от одного узла к другому в управляющем графе задачи, причем каждая временная квота включает в себя время, затраченное на выполнение команд собственно задачи, а также время на выполнение общего кода системного уровня в продолжении задачи,

m) при нормальном функционировании после установки первичного системного таймера (14) при обращении к микроядру, вызванном сигналом (sh) прерывания по времени и вызывающем сброс первичного системного таймера (14), приступают к проверке, связан ли сигнал (sh) прерывания по времени, вызывающий обращение к микроядру, с попыткой нарушения временной квоты, и если это так, то запускают посредством микроядра обработку ошибки, а если сигнал (sh) прерывания по времени не связан с попыткой нарушения временной квоты, то переводят микроядро на операцию обновления списков задач и после этого обновления списков задач, вычисляют при помощи микроядра, с одной стороны, ближайший будущий момент времени, по истечении которого задача должна быть активизирована, и с другой стороны, момент времени в будущем, начиная с которого временная квота, отведенная выполняемой задаче при выходе из микроядра, определенном при обновлении списков, будет исчерпана, и устанавливают первичный системный таймер (14) при помощи микроядра на ближайший из этих моментов в будущем для того, чтобы в соответствии с условиями либо активизировать задачу, либо распознать попытку нарушения временной квоты, обнаружив ошибку в функционировании, и выйти из микроядра после установки первичного системного таймера (14).

n) на стадии подготовки запоминают для каждой из задач данного приложения все разрешенные сцепления его точек временной синхронизации и связи с другими задачами, требующие обращений к системному уровню, причем эти разрешенные сцепления представляются управляющим графом выполнения обращений рассматриваемой задачи к системному уровню, а каждый граф содержит совокупность узлов, каждый из которых соответствует обращению к системному уровню,

о) запоминают каждую буферную область, необходимую для обмена данными между задачами, указав ее размер, размер содержащихся в ней элементов, ее размещение или базовый адрес, а также связи между буферными зонами, позволяющими подтвердить достоверность обмена информацией, необходимого для связи,

р) запоминают для каждой буферной зоны начальные значения ее элементов,

q) инициализируют для данного приложения и предварительно при пуске выполнения в реальном времени в соответствии с режимом работы с привязкой ко времени значения элементов буферной зоны значениями, предварительно занесенными в память,

r) во время выполнения задачи при обращении к системному уровню, когда будет достигнут узел управляющего графа задачи, и после проверки того, что в соответствии с управляющим графом выполняемой задачи сцепление, начиная с узла, соответствующего предыдущему обращению к системному уровню, является разрешенным, осуществляют последовательные обновления буферных зон в соответствии с природой вызова, предварительно занесенного в память, а также необходимые инкрементные обновления временных параметров выполняемой задачи, включающих моменты самого раннего времени d(i) начала и самого позднего времени f(i) завершения.

| DAVID V | |||

| ет al | |||

| Safety properties ensured by the OASIS model for safety critical real-time systems | |||

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

| Дорожная спиртовая кухня | 1918 |

|

SU98A1 |

| Heidelberg, Germany | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для формирования кода текущего состояния критической ситуации технического объекта | 1990 |

|

SU1797098A1 |

| СПОСОБ КОНТРОЛЯ И ОТЛАДКИ ПРОГРАММ РЕАЛЬНОГО ВРЕМЕНИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2050588C1 |

| СЛИТЫЕ БЕЛКИ, РЕКОМБИНАНТНЫЕ БАКТЕРИИ И СПОСОБЫ ПРИМЕНЕНИЯ РЕКОМБИНАНТНЫХ БАКТЕРИЙ | 2015 |

|

RU2771828C2 |

Авторы

Даты

2006-10-20—Публикация

2001-11-13—Подача