Изобретение относится к вычислительной технике и может быть использовано при контроле и отладке программ реального времени бортовых ЭВМ.

Известны способы отладки программ, основанные на написании и проверке ряда утверждений, ожидаемых в каждой точке программы при помощи формальных математических методов (верификация программ) [1] Реализация этих способов затруднительна для программ большого объема и сложности, к которым можно отнести программы бортовых ЭВМ.

Наиболее близким по технической сущности является способ отладки программ методом тестирования, основанный на многократном повторении трех этапов: обнаружения, локализации и исправлении ошибки [2]

При указанном способе отладки программ производится выполнение контрольного теста, измерение и анализ полученных результатов на этапе обнаружения ошибки. На этапе локализации ошибки используются устройства для отладки программ. Исправление ошибки производится путем изменения содержимого памяти ЭВМ. Для программ реального времени бортовых ЭВМ выполнение теста, измерение и анализ полученных результатов, например, можно представить как включение ЭВМ в работу; подключение к входным аналого-цифровым преобразователям ЭВМ определенных последовательностей напряжений; измерение выходных напряжений ЭВМ и сравнение их с эталонными. Локализация ошибки заключается в настройке устройства отладки программ на выбранный режим работы и фиксации с помощью устройства момента проявления ошибки путем, например, останова ЭВМ. Изменение содержимого памяти ЭВМ при исправлении ошибки производится, например, путем перекладки проводников из одних магнитных сердечников в другие или, например, прожигом микросхем памяти. Для программ реального времени бортовых ЭВМ выполнение теста это решение на ЭВМ взаимосвязанных контрольных задач в течение определенного времени. Частота решения этих задач (работа в реальном времени) определяется, как правило, тактирующими прерываниями, поступающими в ЭВМ из аппаратуры.

Во время отладки программ с целью сохранения реального масштаба времени производится измерение минимального количества результатов, а их анализ производится по окончании теста. Это приводит к тому, что определение источника ошибки на основании полученных результатов производится приближенно. Поэтому этап локализации ошибки включает повторное выполнение контрольного теста с предварительной настройкой устройства отладки программ на локализацию ошибки. Процедуры этапа локализации ошибки повторяются до тех пор, пока ошибка не будет локализована. Многократные повторы выполнения теста снижают производительность отладки.

Известны устройства для отладки программ, содержащие схемы анализа магистралей ЭВМ, узлы сравнения заданных точек анализа с текущим состоянием программ, позволяющие производить останов ЭВМ в заданной точке программы и выполнение процедур локализации ошибки. Недостатком известных устройств является нарушение реального времени выполнения программ из-за потерь времени на останов ЭВМ, или затрат времени на работу прерывающей программы.

Наиболее близким по технической сущности является устройство для формирования сигнала прерывания при отладке программ, содержащее регистры, узлы сравнения, группы элементов ИЛИ, группы элементов И, позволяющие прерывать отлаживаемую программу без остановов ЭВМ с переходом на прерывающую программу при обращении отлаживаемой программы к определенной ячейке памяти ЭВМ, при выполнении команды, адрес которой заранее указан, при обращении к определенному регистру процессора ЭВМ, при выполнении команд перехода, т.е. производить локализацию ошибки [3] При этом время, затрачиваемое на работу прерывающей программы и на локализацию ошибки, не учитывается.

Недостатком известного способа и устройства являются большие затраты времени, приводящие к искажению реального времени выполнения программы. Поэтому при отладке производится разделение процедур обнаружения и локализации ошибки. Такое разделение, проводимое с целью сохранения масштаба реального времени, приводит к необходимости многократного повторения контрольного теста для локализации одной ошибки. Все это снижает производительность отладки.

Цель изобретения повышение производительности отладки программ путем сокращения повторов выполнения контрольного теста.

Это достигается совмещением во времени процедур обнаружения и локализации ошибки за счет разбиения процедуры выполнения контрольного теста на интервалы. Производится измерение результатов после каждого интервала и при необходимости локализация ошибки на данном интервале. Это позволяет сузить зону проявления ошибки во времени, производить локализацию ошибки в момент ее обнаружения на основании измеренных в момент обнаружения результатов. С целью сохранения масштаба реального времени при обнаружении и локализации ошибки производится подсчет времени выполнения отлаживаемых программ, времени, оставшегося до выработки очередного тактирующего прерывания, и формирование тактирующего прерывания. В этом случае паузы между интервалами выполнения контрольного теста могут быть любой длительности, столько, сколько потребуется времени на локализацию ошибки, при этом величина времени локализации ошибки не имеет значения.

Цель также достигается тем, что в устройство для отладки программ, содержащее первый, второй и третий регистры, первый, второй и третий узлы сравнения, группу элементов ИЛИ, первый, второй и третий элементы ИЛИ, управляющий регистр, первую, вторую и третью группы элементов И, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой элементы И и элемент НЕ, причем выходы первого и второго регистров соединены соответственно с первыми входами первого и второго узлов сравнения, первый информационный вход устройства соединен с вторыми входами первого и второго узлов сравнения, первый выход управляющего регистра соединен с первыми входами первого элемента И, первого элемента ИЛИ и первыми входами элементов И первой группы, второй выход управляющего регистра соединен с первыми входами второго элемента И, с первыми входами элементов И второй группы и вторым входом первого элемента ИЛИ, третий выход управляющего регистра соединен с первым входом третьего элемента И, первыми входами элементов И третьей группы и с третьим входом элемента ИЛИ, выход которого соединен с первым входом четвертого элемента И, четвертый выход управляющего регистра соединен с первым входом пятого элемента И, выход которого соединен с первым входом шестого элемента И, пятый выход управляющего регистра соединен с вторым входом шестого элемента И, первым входом седьмого элемента И и входом элемента НЕ, выход которого соединен с первым входом восьмого элемента И, выходы первого, второго и третьего элементов И соединены с входами второго элемента ИЛИ, выход которого соединен с управляющим входом третьего узла сравнения, выходы каждого элемента И первой, второй и третьей групп соединены с соответствующими входами элементов ИЛИ группы, выходы третьего регистра и выходы элементов ИЛИ группы соединены соответственно с первой и второй группами информационных входов третьего узла сравнения, выход которого соединен с вторым входом четвертого элемента И, выход которого соединен с вторыми входами седьмого и восьмого элементов И, выход восьмого элемента И соединен с первым управляющим выходом устройства, выходы шестого и седьмого элементов И соединены соответственно с первым и вторым входами третьего элемента ИЛИ, выход которого соединен с вторым управляющим выходом устройства, первый, второй, третий и четвертый управляющие входы устройства соединены соответственно с вторыми входами первого, второго, третьего и пятого элементов И, первый информационный вход устройства соединен с вторыми входами элементов И второй группы, второй и третий информационные входы устройства соединены с вторыми входами элементов И первой и третьей группы, введены триггер, генератор импульсов, девятый элемент И, счетчик, четвертый регистр, элемент задержки, управляющие выходы первого и второго узлов сравнения соединены соответственно с первым и вторым входами триггера, выход триггера соединен с первым входом девятого элемента И, второй вход девятого элемента И соединен с выходом генератора импульсов, выход девятого элемента И соединен со счетным входом счетчика, выход четвертого регистра соединен с информационным входом счетчика, выход переполнения которого соединен с третьим управляющим выходом устройства и входом элемента задержки, выход элемента задержки соединен с установочным входом счетчика, второй управляющий вход устройства соединен с управляющими входами первого и второго узлов сравнения.

Положительный эффект достигается тем, что после выполнения интервала контрольного теста в ЭВМ устройство обеспечивает прерывание выполнения программ и вклинивание прерывающей программы, с помощью которой производится измерение результатов и обнаружение ошибки. В случае обнаружения ошибки устройство настраивается на ее локализацию и локализация проводится на данном интервале выполнения контрольного теста либо на последующем. В результате происходит совмещение во времени процедур обнаружения и локализации ошибки. В большинстве случаев не требуется повторного запуска контрольного теста для проведения локализации ошибки. За счет этого производительность отладки повышается. Масштаб реального времени при этом полностью сохраняется, так как при переходе на прерывающую программу автоматически прекращается счет реального времени в счетчике, который одновременно служит и генератором тактирующих прерываний для ЭВМ. Этот счет автоматически возобновляется при передаче управления на отлаживаемую программу. Аналогично счет реального времени прекращается при переходе на прерывающую программу во время проведения отладки с помощью устройства, а также в случае останова ЭВМ с целью измерения результатов.

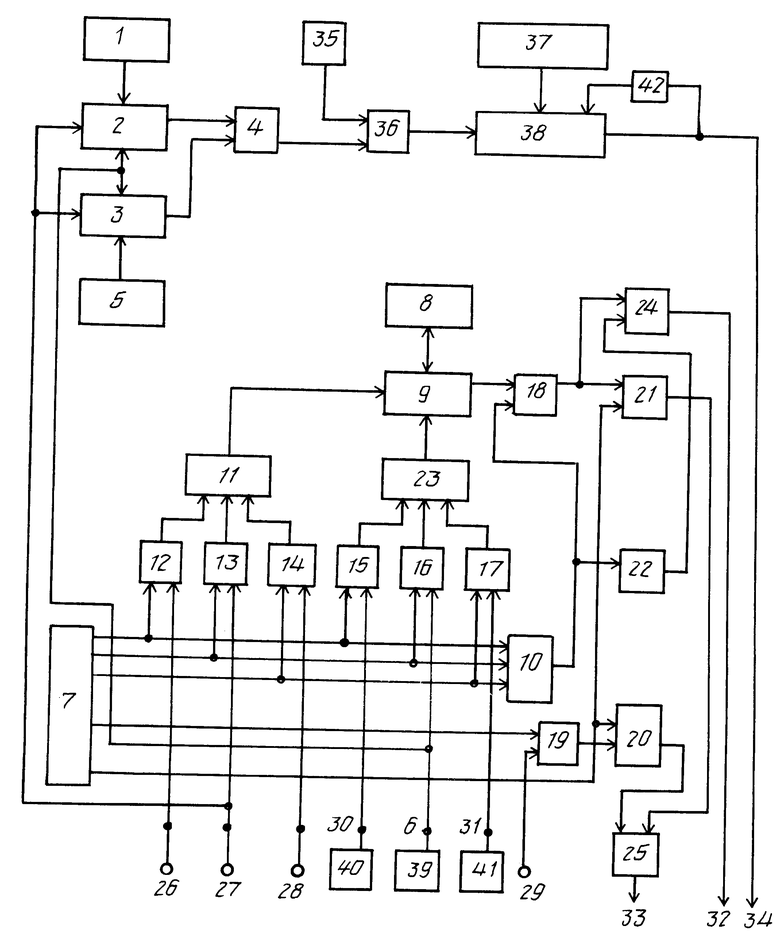

На чертеже представлена схема устройства.

Устройство содержит первый регистр 1, первый узел 2 сравнения, второй узел 3 сравнения, триггер 4, второй регистр 5, входы первого 1 и второго 5 регистров соединены соответственно с первыми входами первого 2 и второго 3 узлов сравнения, выходы которых соединены соответственно с первым и вторым входами триггера 4. Первый информационный вход 6 устройства соединен с вторыми входами первого и второго узлов сравнения. Устройство содержит также управляющий регистр 7, третий регистр 8, третий узел 9 сравнения, первый элемент ИЛИ 10, второй элемент ИЛИ 11, первый, второй и третий элементы И 12-14, первую, вторую и третью группы элементов И 15-17, четвертый, пятый, шестой, седьмой элементы И 18-21, элемент НЕ 22, группу элементов ИЛИ 23, восьмой элемент И 24, третий элемент ИЛИ 25, первый, второй, третий и четвертый управляющие входы 26-29, второй и третий информационные входы 30 и 31, первый, второй и третий управляющие выходы 32-34, генератор 35 импульсов, девятый элемент И 36, четвертый регистр 37, счетчик 38.

Кроме того, на чертеже показаны регистр 39 номера команды, регистр 40 адреса ячейки, регистр 41 сумматора, являющиеся частью ЭВМ, которые не входят в состав предлагаемого устройства, а служит лишь для пояснения его работы. Устройство содержит элемент задержки 42. Первый выход управляющего регистра 7 соединен с первыми входами первого элемента И 12, первого элемента ИЛИ 10 и всех элементов И 15 первой группы. Второй выход управляющего регистра 7 соединен с первыми входами второго элемента И 13, всех элементов И 16 второй группы и с вторым входом первого элемента ИЛИ 10. Третий выход управляющего регистра 7 соединен с первыми входами третьего элемента И 14, всех элементов И 17 третьей группы и с третьим входом первого элемента ИЛИ 10, выход которого соединен с первым входом четвертого элемента И 18. Четвертый выход управляющего регистра 7 соединен с первым входом пятого элемента И 19, выход которого соединен с первым входом шестого элемента И 20. Пятый выход управляющего регистра 7 соединен с вторым входом шестого элемента И 20, первым входом седьмого элемента И 21 и через элемент НЕ 22 с первым входом восьмого элемента И 24. Выходы первого, второго и третьего элементов И 12-14 соединены с входами второго элемента ИЛИ 11, выход которого соединен с управляющим входом третьего узла 9 сравнения.

Выходы каждого элемента И 15-17 соответственно первой, второй и третьей групп соединены с входами соответствующих элементов ИЛИ группы 23. Выходы третьего регистра 8 и выходы группы элементов ИЛИ 23 соединены соответственно с первой и второй группами информационных входов третьего узла 9 сравнения, выход которой соединен с вторым входом четвертого элемента И 18, выход которого соединен с вторыми входами седьмого и восьмого элементов И 21 и 24. Выход 32 восьмого элемента И 24 является первым управляющим выходом устройства. Выходы шестого и седьмого элементов И 20 и 21 соединены соответственно с первым и вторым входами третьего элемента ИЛИ 25, выход 33 которого соединен с вторым управляющим выходом устройства. Первый, второй, третий и четвертый входы 26-29 устройства соединен соответственно с вторыми входами первого, второго, третьего и пятого элементов И 12-14 и 19. Второй управляющий вход 27 устройства соединен с управляющими входами первого и второго узлов сравнения. Выход триггера 4 соединен с первым входом элемента И 36, выход которого соединен со счетным входом счетчика 38. Выход генератора 35 импульсов соединен с вторым входом элемента И 36, выход четвертого регистра 37 соединен с информационным входом счетчика 38, выход которого соединен с третьим управляющим выходом 34 устройства и входом элемента задержки 42, выход элемента задержки соединен с установочным входом счетчика 38. Первый информационный вход 6 устройства соединен с вторыми входами элементов И 16 второй группы. Второй и третий информационные входы 30 и 31 устройства соединены соответственно с вторыми входами элементов И 15 и 17 первой и третьей групп. Регистры 1, 5, 7, 8 и 37 являются тумблерными регистрами.

Работа устройства во всех режимах начинается с установки на регистрах 1 и 5 начального и конечного адресов команд прерывающей программы. На регистре 37 устанавливается код периода основного такта обработки информации в ЭВМ. Этот код определяет длительность очередного шага выполнения отлаживаемых программ. Время очередного шага выполнения программ отсчитывается счетчиком 38. По окончании счета устройство вырабатывает сигнал на управляющем выходе 34, который поступает в систему прерывания ЭВМ.

Во время выполнения прерывающей программы реальное время счетчиком не отсчитывается, и масштаб реального времени, определяемый периодом основного такта обработки информации в ЭВМ, не нарушается.

Устройство может работать в одном из четырех режимов локализации ошибки. В режиме "1" при обращении к ячейке, адрес которой (содержимое регистра 40) совпадает с адресом, набранным на тумблерном регистре 8, устройство вырабатывает сигнал на выходе 33, который также поступает в систему прерывания ЭВМ. Этот выход устройства (в отличие от выхода 34) используется для того, чтобы прерывающая программа могла отличить прерывание режима отладки от тактирующего, так как режим отладки может выполняться в любом месте внутри очередного шага выполнения отлаживаемых программ. Но и в этом случае потери времени на прерывающую программу, в том числе и на анализ, проводимый программистом, полностью учитывается счетчиком и реальный масштаб времени не нарушается.

Аналогично устройство работает в режиме "2". При совпадении адреса выполняемой команды (содержимое регистра 39) с содержимым регистра 8 на выходе 33 устройства вырабатывается управляющий сигнал.

Режим "3" отличается от режима "1" только тем, что сравнивается не содержимое регистра 40, а содержимое регистра 42 и сигнал прерывания вырабатывается не при обращении к ячейке, а при совпадении определенного числа, записанного в регистре 8, с содержимым регистра сумматора 41. В режиме "4" устройство вырабатывает сигнал на выходе 33 при выполнении команды перехода.

Работа устройства во всех режимах происходит следующим образом.

При работе ЭВМ на регистре 39 адреса команды присутствует адрес выполняемой команды, который через первый информационный вход 6 устройства поступает на вторые входы первого и второго узлов 2 и 3 сравнения. На выходе первого узла 2 сравнения появляется импульс при совпадении начального адреса прерывающей программы с адресом, набранным на первом регистре 1, а на выходе второго узла 3 сравнения при совпадении конечного адреса прерывающей программы с адресом, набранным на втором регистре 5.

Включение каждой команды сопровождается управляющим сигналом, поступающим на вход 27. Этот сигнал приходит на управляющие входы узлов сравнения 2 и 3 для опроса узлов сравнения. На выходе триггера 4 появляется сигнал, равный по длительности времени выполнения прерывающей программы со всеми задержками, вызываемыми вмешательством программиста. Этот сигнал запрещает прохождение импульсов с генератора 35 на счетный вход счетчика 38 и, наоборот, разрешает работу счетчика при функционировании устройства в зоне рабочих отлаживаемых программ. На тумблерном регистре 37 набирается обратный код периода тактирующих прерываний, который перезаписывается на счетчик 38 в момент выработки последним сигнала переполнения. Сигнал переполнения поступает на третий управляющий выход 34 устройства.

Работа устройства в отладочном режиме "1" проходит следующим образом.

Программист, проводящий отладку программ, устанавливает на регистре 7 управления режим "1" и режим отладки. При этом на первом и пятом выходах регистра 7 появляются одиночные потенциалы. Каждая команда обращения в ОЗУ сопровождается управляющим потенциалом, который поступает из процессора через первый управляющий вход 26 устройства на второй вход элемента И 12, на первый вход которого поступает продолжительный потенциал первого выхода управляющего регистра 7. С выхода первого элемента И 12 положительный потенциал через второй элемент ИЛИ 11 поступает на управляющий вход третьего узла сравнения и тем самым разрешает сравнение информации, набранной на третьем регистре 8, с содержимым регистра 40 адреса ячейки. Содержимое регистра 40 адреса ячейки ОЗУ через первую группу элементов И 15 и элементов ИЛИ 23 поступает на второй информационный вход третьего узла 9 сравнения. При совпадении содержимого третьего регистра 8 с содержимым регистра 40 адреса ячейки на выходе узла 9 сравнения будет выработан разрешающий потенциал, который поступает на первый вход четвертого элемента И 18, на второй вход которого поступает разрешающий потенциал с выхода первого элемента ИЛИ 10. Сигнал с выхода четвертого элемента И 18 через седьмой элемент И 21 и третий элемент ИЛИ 25 поступает на второй управляющий выход 33 устройства, который соединен с регистром устройства ЭВМ.

Аналогично работает устройство и в других режимах.

В режиме "2" устройство вырабатывает сигнал прерывания при совпадении адреса команды, набранного на третьем регистре 8, с адресом на регистре 39 адреса команды. Управляющий сигнал, поступающий на вход 27 устройства, проходит через элемент И 13 и элемент ИЛИ 11 на опрос третьего узла 9 сравнения.

В режиме "3" устройство вырабатывает сигнал прерывания при обращении к одному из регистров общего назначения ЭВМ, номер которого совпадает с номером, набранным на третьем регистре 8. При обращении к регистру общего назначения ЭВМ вырабатывает управляющий сигнал на входе 26, который через элемент И 14 и элемент ИЛИ 11 поступает на опрос схемы сравнения, на второй вход которой с регистра 41 через вход 31, группу элементов ИЛИ 23 поступает номер регистра общего назначения.

В режиме "4" устройство вырабатывает сигнал прерывания при исполнении команды перехода. На четвертом и пятом выходах управляющего регистра 7 устанавливаются разрешающие потенциалы. При выполнении команды перехода на второй вход элемента ИЛИ 10 через четвертый управляющий вход 29 устройства поступает потенциал. Выходной сигнал через элемент И 20 и элемент ИЛИ 25 поступает в систему прерывания ЭВМ.

Предлагаемый способ и устройство для его осуществления позволяет совмещать во времени процедуры обнаружения и локализации ошибки. При обнаружении ошибки момент ее проявления фиксируется. При этом промежуточная информация, имеющаяся в преобразователях ЭВМ на данном интервале выполнения отлаживаемых программ, также фиксируется и может быть измерена. Это позволяет уже при первом выполнении теста локализовать ошибку, либо выбрать правильную версию об источнике ошибки, настроить устройство на один из отладочных режимов и сделать первую попытку для локализации ошибки на следующем интервале.

Таким образом, предлагаемый способ и устройство позволяют как минимум на один сократить количество повторов тестов при локализации ошибки. Кроме того, устройство позволяет проводить отладку без нарушения масштаба реального времени, что приближает отладку программ ЭВМ максимально к работе в реальных условиях. Тем самым предлагаемый способ и устройство для его осуществления обеспечивает повышение производительности отладки программ в 1,5-2 раза по сравнению с прототипом, взятым в качестве базового объекта.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программно-аппаратных комплексов | 1990 |

|

SU1795464A1 |

| Устройство для прерывания при отладке программ | 1984 |

|

SU1171799A2 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для прерывания при отладке программ | 1980 |

|

SU962945A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

| Устройство для формирования сигналов прерывания при отладке программ | 1986 |

|

SU1405061A2 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| Устройство для отладки программ | 1987 |

|

SU1462327A1 |

| Устройство для отладки программ | 1988 |

|

SU1624461A1 |

Изобретение относится к вычислительной технике. Цель изобретения повышение производительности отладки путем сокращения повторов выполнения контрольного теста. Способ основан на измерении результатов по окончании этапа обнаружения ошибки, локализации ошибки, включающей повторное выполнение теста, и исправлении ошибки. Новым является измерение результатов в процессе обнаружения ошибки путем разбиения выполнения контрольного теста на интервалы, локализация ошибки производится на данном интервале или при выполнении последующего интервала контрольного теста. 2 с. и 3 з. п. ф-лы, 1 ил.

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для прерывания при отладке программ | 1980 |

|

SU962945A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-12-20—Публикация

1991-03-13—Подача