Область техники

Настоящее изобретение относится к электронному блоку управления, имеющему ядро, работающее в режиме реального времени и управляющее разбиением на разделы. Настоящее изобретение предназначено, в частности, для применения в авиации.

Уровень техники

В данной области применения блок управления, именуемый электронно-цифровой системой управления двигателем (FADEC), содержит микроконтроллер, включающий в себя операционную систему для управления выполнением компьютерных приложений. Эти приложения могут быть выполнены полностью или частично с использованием режима одновременного выполнения. Операционная система включает в себя ядро, работающее в режиме реального времени, т.е. является операционной системой реального времени (RTOS) для управления выполнением приложений, и гарантирующую маршрутизацию данных между двумя приложениями, либо между программными приложениями и аппаратной частью. Разбиение на разделы обеспечивает выделение каждому приложению раздела, что позволяет избежать взаимного влияния приложений друг на друга во время их выполнения. В области авиации подобное разбиение регулирует стандарт ARINC 653, обеспечивающий пространственное разбиение, которое гарантирует, что приложение не может записывать в область памяти, соответствующую разделу другого приложения, а разбиение на временные разделы гарантирует, что каждому приложению будет выделено некоторое время для его выполнения. Подобное разбиение на разделы позволяет использовать приложения от разных поставщиков и/или имеющих разную степень критичности. Тем не менее, ядра, работающие в режиме реального времени и совместимые со стандартом ARINC 653, являются сложными и имеют недостаток, касающийся способа разбиения на разделы, который выполнен исключительно программными средствами, что приводит к неэффективной работе приложений, выполняющихся без управления ядром, работающим в режиме реального времени.

Более того, в случае многозадачных ядер, если планировщик ядра отдает команду на переключение с первой задачи на вторую, необходимо создать резервную копию контекста первой задачи (т.е. всех значений состояния микроконтроллера, необходимых для выполнения задачи и записанных, в частности, в регистрах памяти микроконтроллера), в то время как контекст второй задачи должен быть найден и восстановлен. Таким образом, изменение контекста является относительно затратным в отношении используемого времени, поскольку микроконтроллеры, в частности, имеют все возрастающее количество регистров, для которых необходимо делать резервные копии. По этим же самым причинам, изменения в разделах становятся более длительными. Это оказывает негативное влияние на многозадачные ядра, совместимые со стандартом ARINC 653.

Раскрытие изобретения

Предметом настоящего изобретения является блок управления, обеспечивающий жесткое пространственное и временное разбиение на разделы.

В данном случае, в настоящем изобретении предложен электронный блок управления, содержащий микроконтроллер, имеющий как постоянное запоминающее устройство (ROM), содержащее программный код операционной системы со встроенным ядром, работающим в режиме реального времени и предназначенным для выполнения вычислительных задач, так и оперативное запоминающее устройство (RAM), содержащее значения переменных, связанных с указанными задачами. ROM и RAM имеют области, соответствующие разделам, один из которых выделен под ядро, работающее в режиме реального времени, в то время как каждый из остальных разделов выделен по меньшей мере для одной из задач. ROM и RAM связаны с адресной шиной, которая физически запрограммирована так, чтобы, во-первых, не допускать запись в другие области RAM, и, во-вторых, не допускать выполнение кодов из других областей ROM, а ядро, работающее в режиме реального времени, связано с таймером для выделения времени исполнения кода каждому разделу.

Таким образом, адресная шина физически запрограммирована так, что задача, выполняемая в любом из разделов, не имеет аппаратных средств для записи данных или исполнения кода ни в каком другом разделе, кроме как выделенном данной задаче. Обмен данными между разделами не может быть осуществлен без вовлечения ядра, работающего в режиме реального времени, посредством программирования адресной шины. Таким образом, ядро, работающее в режиме реального времени, гарантирует целостность данных в разделах, отличных от разделов, используемых в данный момент. Ядро, работающее в режиме реального времени, также гарантирует, что каждая задача может быть выполнена в выделенном для этого временном окне. Вследствие этого, задачи могут выполняться одновременно, но, в то же время, минимизируется любой риск взаимного влияния, вытекающего из результата их выполнения.

Предпочтительно, ядро, работающее в режиме реального времени, выполнено с возможностью вызывать исполнение разделов во время цикла исполнения, который является замкнутым, и, более предпочтительно, цикл исполнения может включать в себя некоторый раздел несколько раз.

Такой цикл прост в управлении.

Также предпочтительно, чтобы цикл исполнения включал в себя резервный интервал времени.

Такой резерв времени позволяет достаточно просто добавить одну или более задач без полной реорганизации цикла исполнения.

Первой особенно полезной характеристикой настоящего изобретения является то, что раздел, выделенный для ядра, работающего в режиме реального времени, содержит страницы памяти, каждая из которых выделена задаче и содержит значения регистров каждой задачи, причем ядро, работающее в режиме реального времени, выполнено с возможностью управления указателем задач, содержащего адрес страницы задачи, выполняемой в данный момент времени.

Это позволяет ускорить изменение значений, содержащихся в регистрах, из-за отсутствия необходимости резервного копирования значений из регистров для текущей задачи в заданную адресную область и последующее восстановление регистров для задачи, которая подлежит выполнению. Это приводит к относительно быстрому изменению контекста в течение времени, не зависящего от числа регистров. Это также делает возможным обеспечить разделение регистров в соответствии с требованиями к необходимому управлению указателем задач в целях доступа к регистру.

В соответствии со второй особенной полезной характеристикой настоящего изобретения, раздел, выделенный под ядро, работающее в режиме реального времени, содержит список задач, готовых к выполнению и организованный пораздельно, и ядро, работающее в режиме реального времени, выполнено с возможностью управления указателем раздела для доступа к списку готовых для выполнения задач, и, предпочтительно, список задач, готовых к выполнению, является замкнутым списком, содержащим адреса контекста первой и последней задач, готовых к выполнению.

Это позволяет осуществлять быструю смену раздела посредством только лишь обновлением указателя раздела.

Краткое описание чертежей

Другие свойства и преимущества настоящего изобретения будут более понятны после прочтения нижеследующего описания конкретных вариантов осуществления настоящего изобретения, но никак его не ограничивающих.

В нижеследующем описании сделаны ссылки на сопроводительные чертежи, где:

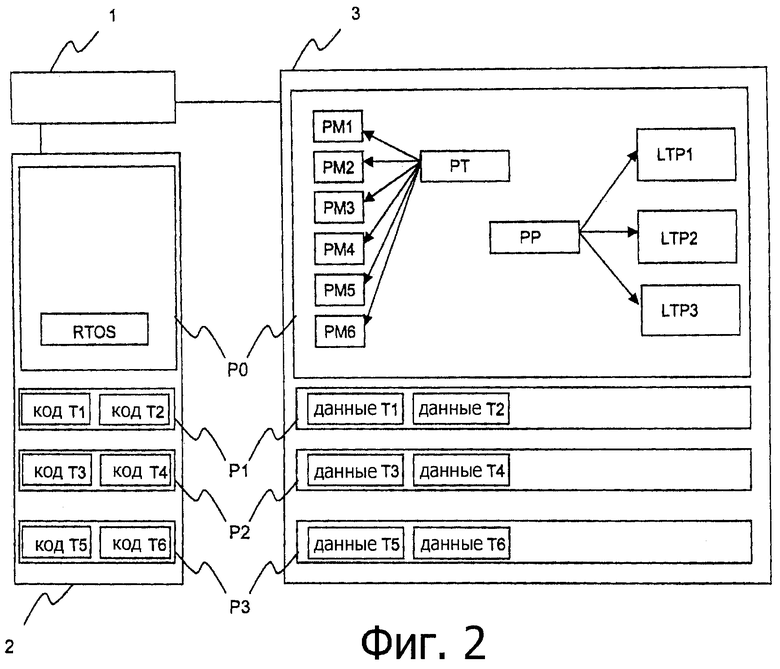

На фиг.1 схематически изображено пространственное разделение ROM и RAM;

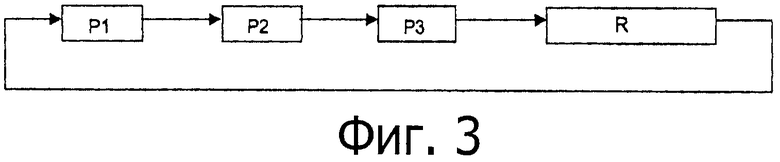

На фиг.2 схематически изображен блок управления согласно настоящему изобретению, показывающий, в частности, как организовано разделение RAM; и

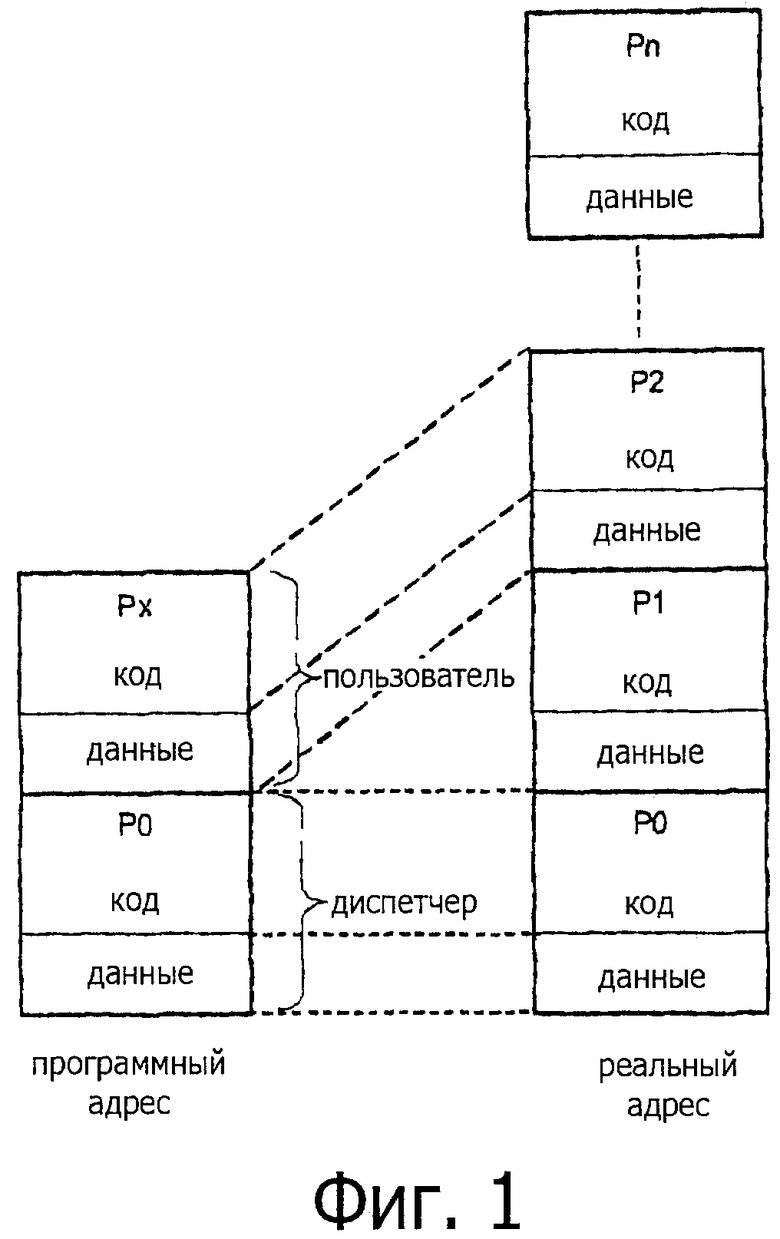

На фиг.3 схематически изображено упорядоченное расположение разделов.

Осуществление изобретения

Настоящее изобретение, описанное в данном документе, относится к авиации и предназначено для управления одним или более авиационными двигателями. В данном примере, блок управления является блоком типа FADEC и удовлетворяет требованиям стандарта ARTNC 653.

В соответствии со ссылками на фигуры, блок управления, согласно настоящему изобретению, является микросхемой типа "система на микросхеме" (SOC), включающей в себя программные инструкции для микроконтроллера и его периферии. Блок управления также может быть выполнен в виде программируемой вентильной матрицы (FPGA). В качестве примера, микроконтроллер может быть реализован с использованием языка VHDL и он может быть перепрограммируемым. (Язык VHDL является языком описания для интегральных схем с очень высокой скоростью производительности.)

Таким образом, блок управления содержит микроконтроллер 1, имеющий ROM 2 и RAM 3. Блок управления также включает в себя определенные средства (не показаны) для соединения с датчиками, размещенными на каждом двигателе, и элементами управления, размещенными в кабине пилота летательного аппарата.

ROM 2 имеет области, соответствующие разделам (Р0 - Р3), один из которых выделен для программного кода операционной системы, а другие разделы выделены для программного кода приложений или компьютерных программ, выполняющих определенные задачи. ROM 2 связан с адресной шиной, которая физически запрограммирована так, что каждый раздел предназначен для выполнения кода из области памяти ROM 2, которая не включает в себя области, не соответствующие данному разделу. В программное обеспечение операционной системы встроено ядро, работающее в режиме реального времени с функциями планирования задач, гарантирующих, что заданные временные ограничения совместимы с исполняемыми задачами. Таким образом, раздел Р0 соответствует коду ядра, работающего в режиме реального времени, в то время как другие разделы (в данном случае, разделы Р1 - Р3), соответствуют коду одной или более задач (в данном случае, задачам T1 - Т6).

RAM 3 имеет области, соответствующие разделам Р0 - Р3, одна из которых выделена для ядра, работающего в режиме реального времени, в то время как каждая из других областей выделена, по меньшей мере, для одной задачи, и RAM связана с адресной шиной, которая физически запрограммирована так, что любой раздел является непригодным для записи в область RAM, за исключением соответствующей ему области. Раздел Р0, таким образом, выделен для данных и других переменных ядра, работающего в режиме реального времени, в то время как другие разделы (Р1 - Р3) выделены для данных одной или более задач (T1 - Т6).

Таким образом, это обеспечивает пространственное разделение, которое реализовано посредством механизма виртуальной адресации, управляемой контроллером памяти, встроенным в микроконтроллер, и который управляет адресной шиной и шиной данных (по аналогии с обычной виртуальной адресацией, где запрограммированный адрес соответствует виртуальному адресу, а реальный адрес соответствует физическому адресу - см. фиг.1). Буферы (известные также как буферы быстрого преобразования адреса (TLB) в микроконтроллерах типа МРС 5554) предусмотрены для программирования адреса трансляции, что делает возможным переход от запрограммированного адреса к реальному адресу. Таким образом, микроконтроллер управляет четырьмя буферами для двух разделов, которые могут быть выполнены в любой данный момент:

- буфер для кода и буфер для данных раздела Р0, выделенного для ядра, работающего в режиме реального времени; и

- буфер для кода и буфер для данных раздела РХ, выделенного для задачи, которая является активной в данный момент.

Любой доступ к коду и данным осуществляют через буферы: и если буфер обнулен, доступ к физическому адресу невозможен. Таким образом, при использовании четырех буферов, только два заданных раздела являются доступными (ядро, работающее в режиме реального времени, и выбранная задача). Другие разделы будут недоступны.

Кроме того, можно дать диспетчеру и пользователю права для доступа к буферам, чтобы защитить раздел Р0 (режим диспетчера), выделенный для ядра, работающего в режиме реального времени, от нежелательного доступа из раздела с приложением, исполняемым в режиме пользователя.

Ядро, работающее в режиме реального времени, также выполнено с возможностью синхронизации для выделения времени каждому из разделов Р1 - Р3. Синхронизация организована как множество базовых циклов, синхронизированных с прерываниями от таймера микроконтроллера, и задача, активируемая по прерыванию, вызывает процедуру управления временем в ядре, работающем в режиме реального времени, так что данное ядро берет на себя управление при каждом прерывании, чтобы определить, должно ли быть приостановлено исполнение текущего раздела. В данном конкретном примере, ядро, работающее в режиме реального времени, выполнено с возможностью управления исполнением разделов, и, соответственно, задач в области выполнения цикла, который является замкнутым. Исполнительный цикл включает в себя интервал R резерва времени, позволяющий добавить новые разделы посредством изъятия времени их выполнения из резерва времени.

Раздел Р0, выделенный для ядра, работающего в режиме реального времени, содержит в себе страницы памяти (РМ1 - РМ6), каждая из которых выделена для соответствующей задачи (T1 - Т6) и содержит значения регистров каждой из задач, и ядро, работающее в режиме реального времени, выполнено с возможностью управления указателем (РТ) задач, содержащим адрес страницы задачи, выполняемой в данный момент.

Раздел Р0, выделенный для ядра, работающего в режиме реального времени, содержит в себе список задач, готовых к выполнению и организованных в виде разделов (LTP1 - LTP3), и ядро, работающее в режиме реального времени, выполнено с возможностью управления указателем (РР) раздела для доступа к списку готовых к выполнению задач (LTP1 - LTP3).

Каждый список готовых задач (LTP1 - LTP3) является замкнутым списком, содержащим контекстные адреса первой и последней задачи, готовых к выполнению. Ядро, работающее в режиме реального времени, содержит обновляемый список задач, готовых к выполнению, как функции возникновения событий (например, вызовы функции или прерывания), что служит механизмом запуска вышеуказанных задач. Кроме того, ядро, работающее в режиме реального времени, учитывает приоритеты, которые могут быть назначенных для каждой из задач с целью сортировки списка подготовленных задач.

Когда выполнение задач, готовых к выполнению для каждого раздела, запущено, ядро, работающее в реальном режиме времени, запускает отсчет лимита времени, и в конце данного лимита времени приостанавливает выполнение задачи для раздела, чтобы запустить готовые к выполнению задачи из следующего раздела.

Изменение разделов осуществляют посредством обновления указателя разделов.

Изменение контекста перед выполнением новой задачи осуществляют при помощи загрузки в указатель РТ задач адреса страницы памяти, содержащей регистры задачи, которую нужно выполнить. Вышеописанная структура блока управления и способ, согласно настоящему изобретению, позволяет эффективно осуществлять изменение контекста, в особенности, при изменении программных команд для микроконтроллера и периферийных устройств.

Изменение контекста (задачи или раздела) является быстрым и одинаковым по продолжительности. Продолжительность не зависит, во-первых, от количества внутренних регистров микроконтроллера, и, во-вторых, от количества подготовленных задач или количества управляемых разделов.

Таким образом, хотя данное изобретение дает возможность микроконтроллеру выполнять многозадачные действия в режиме реального времени, оно, тем не менее, соответствует стандарту ARINC 653, и в то же время ограничивает стоимость блока управления.

Обычно, раздел Р0 выделяют для ядра, работающего в режиме реального времени, и содержит другие связанные списки для управления другими ресурсами ядра, работающего в режиме реального времени (задержки времени, очереди,…).

Очевидно, что настоящее изобретение не ограничено описанными вариантами осуществления и охватывает любые возможные изменения, попадающие в пределы объема настоящего изобретения, определенного формулой изобретения.

В частности, размеры разделов могут совпадать или быть разными.

Цикл исполнения может включать в себя выполнение любого заданного раздела один или более раз.

Могут быть предусмотрены различные средства, позволяющие избежать создания резервных копий и последующего восстановления регистров:

- изменение команд доступа к регистрам для доступа к ним в индексном режиме, с использованием индекса, представленным указателем задач, вместо доступа к ним в прямом режиме;

- когда адрес области регистров является конфигурируемым, авторизацию динамического реконфигурирования (не только при запуске) с использованием указателя задач (без изменения команд); и

- создание адресной шины, выделенной для регистров, в которой область адреса может быть динамически сконфигурирована с использованием указателя задач.

Электронный блок может иметь структуру, отличающуюся от приведенной в данном документе. Например, ROM 2 может быть электрически стираемым перепрограммируемым постоянным запоминающим устройством (EEPROM) или энергонезависимой памятью (NVM).

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМЫ И СПОСОБЫ ПРЕДОТВРАЩЕНИЯ НЕСАНКЦИОНИРОВАННОГО ПЕРЕМЕЩЕНИЯ СТЕКА | 2014 |

|

RU2629442C2 |

| АКТИВНЫЙ АППАРАТНЫЙ СТЕК ПРОЦЕССОРА | 2013 |

|

RU2530285C1 |

| СИСТЕМЫ И СПОСОБЫ ПРОВЕРКИ АДРЕСА ВОЗВРАТА ПРОЦЕДУРЫ | 2014 |

|

RU2628163C2 |

| СПОСОБ ОРГАНИЗАЦИИ ПЕРСИСТЕНТНОЙ КЭШ ПАМЯТИ ДЛЯ МНОГОЗАДАЧНЫХ, В ТОМ ЧИСЛЕ СИММЕТРИЧНЫХ МНОГОПРОЦЕССОРНЫХ КОМПЬЮТЕРНЫХ СИСТЕМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2002 |

|

RU2238584C2 |

| СПОСОБ РАЗРЕШЕНИЯ КОНФЛИКТОВ ПО АДРЕСНОМУ ПРОСТРАНСТВУ МЕЖДУ МОНИТОРОМ ВИРТУАЛЬНЫХ МАШИН И ГОСТЕВОЙ ОПЕРАЦИОННОЙ СИСТЕМОЙ | 2001 |

|

RU2259582C2 |

| ИНСТРУКЦИЯ И ЛОГИКА ДЛЯ ДОСТУПА К ПАМЯТИ В КЛАСТЕРНОЙ МАШИНЕ ШИРОКОГО ИСПОЛНЕНИЯ | 2013 |

|

RU2662394C2 |

| Программируемые устройства для обработки запросов передачи данных памяти | 2016 |

|

RU2690751C2 |

| СПОСОБ ОБРАБОТКИ ЦИФРОВЫХ ДАННЫХ | 2005 |

|

RU2294010C1 |

| КОМАНДА И ЛОГИЧЕСКАЯ СХЕМА ДЛЯ СОРТИРОВКИ И ВЫГРУЗКИ КОМАНД СОХРАНЕНИЯ | 2014 |

|

RU2663362C1 |

| СПОСОБ, УСТРОЙСТВО И СИСТЕМА УМЕНЬШЕНИЯ ВРЕМЕНИ ВОЗОБНОВЛЕНИЯ РАБОТЫ ДЛЯ КОРНЕВЫХ ПОРТОВ И КОНЕЧНЫХ ТОЧЕК, ИНТЕГРИРОВАННЫХ В КОРНЕВЫЕ ПОРТЫ | 2014 |

|

RU2586022C2 |

Группа изобретений относится к электронным блокам управления. Технический результат заключается в повышении быстродействия электронных блоков управления. Для этого предложен электронный блок управления, содержащий микроконтроллер, снабженный RAM, содержащим переменные данные, и ROM, связанным с программным кодом операционной системы со встроенным ядром, работающим в режиме реального времени, для выполнения вычислительных задач, при этом ROM и RAM включают в себя области, соответствующие разделам, один из которых выделен под ядро, работающее в режиме реального времени, а каждый из остальных разделов выделен по меньшей мере для одной из задач, ROM и RAM связаны с адресной шиной, которая физически запрограммирована так, чтобы не допускать запись в другой из областей RAM и не допускать выполнение другой из областей ROM, причем ядро, работающее в режиме реального времени, связано с таймером для выделения времени выполнения для каждого раздела, при этом электронный блок управления выполнен так, что только два раздела могут выполняться в данный момент, а микроконтроллер выполнен с возможностью управления только четырьмя буферами для указанных двух разделов: буфером для кода и буфером для данных раздела, выделенного для ядра, работающего в режиме реального времени; и буфером для кода и буфером для данных раздела, выделенного для задачи, которая является активной в указанный момент. 2 н. и 8 з.п. ф-лы, 3 ил.

1. Электронный блок управления, содержащий микроконтроллер, имеющий постоянное запоминающее устройство (ROM), содержащее программный код операционной системы со встроенным ядром, работающим в режиме реального времени, для выполнения вычислительных задач, и оперативное запоминающее устройство (RAM), содержащее переменные данные, относящиеся к ядру, работающему в режиме реального времени, и указанным задачам, причем ROM и RAM включают в себя области, соответствующие разделам, один из которых выделен под ядро, работающее в режиме реального времени, а каждый из остальных разделов выделен по меньшей мере для одной из задач, при этом ROM и RAM связаны с адресной шиной, физически запрограммированной для недопущения для каждого раздела записи в другую из областей RAM и недопущения для каждого раздела выполнения другой из областей ROM, причем ядро, работающее в режиме реального времени, связано с таймером для выделения времени выполнения для каждой задачи.

2. Блок по п.1, в котором ядро, работающее в режиме реального времени, выполнено с возможностью вызывать выполнение разделов в цикле выполнения, который является замкнутым.

3. Блок по п.2, в котором цикл выполнения включает в себя выполнение некоторого раздела несколько раз.

4. Блок по п.2, в котором цикл выполнения включает в себя интервал резерва времени.

5. Блок по п.1, в котором раздел, выделенный под ядро, работающее в режиме реального времени, содержит страницы памяти, каждая из которых выделена под задачу и содержит регистры каждой задачи, при этом ядро, работающее в режиме реального времени, выполнено с возможностью управления указателем задач, содержащим адрес страницы задачи, выполняемой в данный момент времени.

6. Блок по п.1, в котором раздел, выделенный под ядро, работающее в режиме реального времени, содержит список задач, готовых к выполнению и упорядоченных по разделам, а ядро, работающее в режиме реального времени, выполнено с возможностью управления указателем разделов для доступа к списку задач, готовых к выполнению.

7. Блок по п.6, в котором список задач, готовых к выполнению, имеет форму замкнутого списка, содержащего контекстные адреса первой и последней задач, готовых к выполнению.

8. Блок по п.1, в котором блок управления является микросхемой, включающей в себя набор команд для микроконтроллера и периферийных устройств, связанных с микроконтроллером.

9. Блок по п.1, в котором микроконтроллер является программируемой логической матрицей.

10. Электронный блок управления, содержащий микроконтроллер, имеющий постоянное запоминающее устройство (ROM), содержащее программный код операционной системы со встроенным ядром, работающим в режиме реального времени, для выполнения вычислительных задач, и оперативное запоминающее устройство (RAM), содержащее переменные данные, относящиеся к ядру, работающему в режиме реального времени, и указанным задачам, причем ROM и RAM включают в себя области, соответствующие разделам, один из которых выделен под ядро, работающее в режиме реального времени, а каждый из остальных разделов выделен по меньшей мере для одной из задач, при этом ROM и RAM связаны с адресной шиной, физически запрограммированной для недопущения для каждого раздела записи в другую из областей RAM и недопущения для каждого раздела выполнения другой из областей ROM, причем ядро, работающее в режиме реального времени, связано с таймером для выделения времени выполнения для каждой задачи, при этом электронный блок управления выполнен так, что только два раздела могут выполняться в данный момент, а микроконтроллер выполнен с возможностью управления только четырьмя буферами для указанных двух разделов:

буфером для кода и буфером для данных раздела, выделенного для ядра, работающего в режиме реального времени; и

буфером для кода и буфером для данных раздела, выделенного для задачи, которая является активной в указанный момент.

Авторы

Даты

2014-07-27—Публикация

2010-10-19—Подача