Изобретение относится к области вычислительной техники и может быть использовано в системах обмена данными и локальных вычислительных сетях (ЛВС).

Известно многоканальное устройство с динамическим изменением приоритета по авт. св. СССР №1562912, G 06 F 9/46, 1990, бюл. №17, содержащее N≥2 абонентских блоков, счетчик, элемент И, генератор тактовых импульсов, делитель, блок анализа приоритетов и блок наращивания приоритета.

Недостатком данного устройства является относительно большое время обслуживания запросов абонентов вычислительной системы с низким приоритетом.

Известно устройство обслуживания запросов пользователей вычислительной системы, содержащее N≥2 абонентских блоков, счетчик, элемент И, генератор тактовых импульсов, делитель, N-входовый элемент ИЛИ-НЕ, мультиплексор и инвертор (см. авт. св. СССР №2140666, G 06 F 9/46, 1999, бюл. №30).

Однако данное устройство имеет относительно невысокую надежность и низкое быстродействие, обусловленные большим количеством взаимоувязанных элементов, входящих в его состав.

Наиболее близким по технической сущности к заявляемому устройству (прототипом) является устройство обслуживания разноприоритетных запросов абонентов вычислительной системы (см. патент РФ №2186420, G 06 F 9/46, 2002, бюл. №21), содержащее N≥2 абонентских блоков, генератор тактовых импульсов, первый и второй N-входовые элементы И-НЕ, первый и второй шифраторы приоритетов, элемент ИЛИ, элемент И-НЕ и селектор-мультиплексор. При этом выход генератора тактовых импульсов подключен к тактовым входам каждого из N абонентских блоков. Запросные входы и К-разрядные входы "Код максимального времени ожидания" каждого из N абонентских блоков, где К≥2 - разрядность кода максимального времени ожидания обслуживания запросов, являются соответствующими запросными входами и К-разрядными входами "Код максимального времени ожидания" устройства. Входы "Обнуление" каждого из N абонентских блоков являются соответствующими входами "Обнуление" устройства. Каждый из N входов первого и второго N-входовых элементов И-НЕ подключены к соответствующим N инверсным входам соответственно первого и второго шифраторов приоритетов. Выходы первого и второго N-входовых элементов И-НЕ подключены соответственно к второму и первому входам элемента ИЛИ. Каждый и, n=1, 2, ..., N, инверсный вход первого и второго шифраторов приоритетов подключен соответственно к первому и второму сигнальному выходу ((N+1)-n)-го абонентского блока. Выход элемента ИЛИ подключен к второму входу элемента И-НЕ, первый вход которого является опросным входом устройства, а выход элемента И-НЕ подключен к инверсному разрешающему входу селектора-мультиплексора и является разрешающим выходом устройства. Управляющий вход селектора-мультиплексора подключен к второму входу элемента ИЛИ. Каждый из J, где J=]log2N[, инверсных выходов первого и второго шифраторов приоритетов подключены к соответствующим J первичным входам и соответствующим J вторичным входам селектора-мультиплексора, J-разрядный выход селектора-мультиплексора является J-разрядным выходом "Код подлежащего обслуживанию абонента" устройства.

В прототипе реализуется возможность повышения быстродействия и надежности за счет сокращения количества элементов, входящих в состав устройства обслуживания разно-приоритетных запросов абонентов вычислительной системы.

Однако прототип имеет недостаток - относительно низкую достоверность аутентификации абонента, инициирующего сигнал запроса в ходе одновременного доступа большого числа абонентов к ресурсам реально функционирующей вычислительной системы в различных условиях априорной неопределенности, в частности, в условиях недостоверности (недостаточности, неполноты и противоречивости) результатов определения наименьшего номера абонента. Данное устройство позволяет с высокой достоверностью обслуживать разноприоритетные запросы абонентов вычислительной системы в ситуациях, в которых абонент однозначно аутентифицирован - наивысший приоритет абонента в общем потоке разноприоритетных запросов количественно задан и непротиворечив, в то время как в подавляющем большинстве ситуаций, реально возникающих в рамках реального процесса функционирования систем обмена данными с множественным доступом, наивысший приоритет абонента может быть в текущем масштабе времени распознан (определен) лишь качественно (на качественном уровне - недостоверно, недостаточно, неполно), и в динамике функционирования вычислительной системы достоверные решения о наименьшем номере абонента (т.е. о его наивысшем приоритете) в таких ситуациях традиционно принимаются, опираясь на математические методы принятия решений в слабоструктурированных задачах.

Под "аутентификацией" абонента понимается динамическое распознавание (определение) приоритета абонента - принятие решения о наименьшем номере абонента в динамике функционирования вычислительной системы (в режиме реального времени), с учетом возможного перераспределения приоритетов, смены полномочий и иных дестабилизирующих факторов.

Под "обслуживанием" понимается совокупность действий вычислительной системы, включающая выборку запроса из очереди, выделение ему ресурса, а также проведение завершающих операций. Запрос - посылка сигнала, инициирующего ответ. Входное сообщение, содержащее требование к системе на выделение ресурса.

Под "приоритетом" понимается число, предписанное задаче, процессу или операции, определяющее очередность их выполнения или обслуживания. Чем меньше число, тем выше уровень приоритета.

Целью предлагаемого изобретения является создание устройства обслуживания разноприоритетных запросов абонентов вычислительной системы, обеспечивающего повышение достоверности аутентификации абонентов, генерирующих сигналы запросов к ресурсам вычислительной системы в условиях, присущих реальной динамике процесса функционирования систем обмена данными и ЛВС, т.е. в условиях неопределенности (недостоверности, недостаточности, неполноты и противоречивости) данных об истинном номере абонента, устройства, способного в текущем масштабе времени определить приоритет абонента, номер которого может быть распознан как количественно, так и качественно - недостоверно, недостаточно, неполно.

Указанная цель достигается тем, что в известное устройство обслуживания разноприоритетных запросов абонентов вычислительной системы, содержащее N≥2 абонентских блоков, генератор тактовых импульсов, первый и второй N-входовые элементы И-НЕ, первый и второй шифраторы приоритетов, элемент ИЛИ, элемент И-НЕ и селектор-мультиплексор, J-разрядный, где J=]log2N[, выход которого является J-разрядным выходом «Код подлежащего обслуживанию абонента» устройства, выход генератора тактовых импульсов подключен к тактовьм входам каждого из N абонентских блоков, запросные входы и K-разрядные входы «Код максимального времени ожидания» каждого из N абонентских блоков, где К≥2 - разрядность кода максимального времени ожидания обслуживания запросов, являются соответствующими N запросными входами и N K-разрядными входами «Код максимального времени ожидания» устройства, входы «Обнуление» каждого из N абонентских блоков являются соответствующими N входами «Обнуление» устройства, N входов первого и второго N-входовых элементов И-НЕ подключены к соответствующим N инверсным входам соответственно первого и второго шифраторов приоритетов, выходы первого и второго N-входовых элементов И-НЕ подключены соответственно к второму и первому входам элемента ИЛИ, выход которого подключен к второму входу элемента И-НЕ, первый вход которого является опросным входом устройства, выход элемента И-НЕ подключен к инверсному разрешающему входу селектора-мультиплексора и является разрешающим выходом устройства, управляющий вход селектора-мультиплексора подключен к второму входу элемента ИЛИ, n-е инверсные входы первого и второго шифраторов приоритетов, где n=1, 2, ..., N, подключены соответственно к первому и второму сигнальным выходам ((N+1)-n)-го абонентского блока, дополнительно включены первый и второй анализаторы приоритетов, предназначенные для предварительного анализа данных об истинном приоритете абонента для очереди разноприоритетных запросов соответственно первого и второго порядка и аутентификатор приоритетов, предназначенный для записи, хранения результатов анализа приоритетов и математически корректной верификации абонента с наивысшим приоритетом, путем преобразования распознанных неоднозначно исходных данных, характеризующих приоритет абонентов, к виду, пригодному для однозначного принятия достоверного решения об уровне приоритета конкретного абонента вычислительной системы. При этом каждый из J инверсных выходов первого и второго шифраторов приоритетов подключены к J входам соответственно первого и второго анализаторов приоритетов, J-разрядные выходы которых соединены соответственно с вторым и первым J-разрядными входами аутентификатора приоритетов. Контрольные выходы первого и второго анализаторов приоритетов подключены соответственно к второму и первому контрольным входам аутентификатора приоритетов, первая группа J выходов и вторая группа J выходов которого соединены с соответственно с первой и второй группами J информационных входов селектора-мультиплексора и подключены к группам J прямых выходов соответственно второго и первого анализаторов приоритетов.

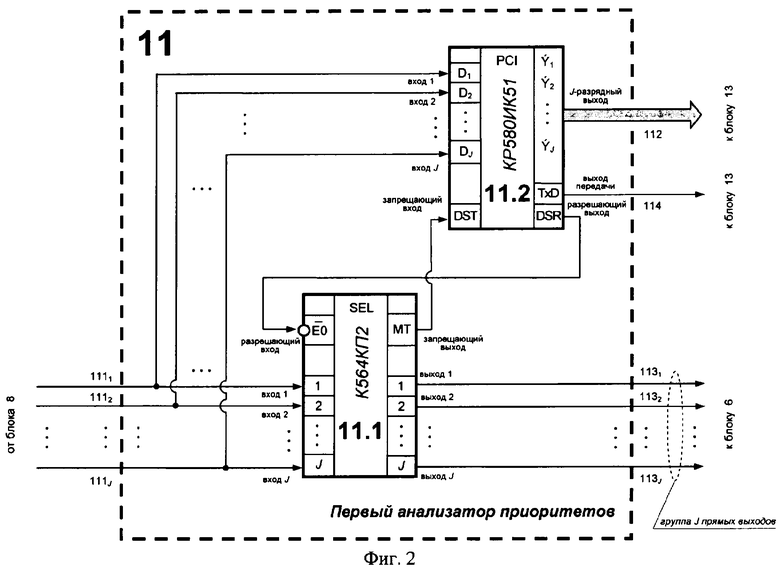

Первый анализатор приоритетов состоит из первого селектора и первого преобразователя, предназначенного для регистрации данных, характеризующих приоритет абонентов для очереди первого порядка и преобразования этих данных из параллельного кода в последовательный. При это J-разрядный выход первого преобразователя является J-разрядным выходом первого анализатора приоритетов, выход передачи первого преобразователя является контрольным выходом первого анализатора приоритетов, разрешающий выход первого преобразователя соединен с инверсным разрешающим входом первого селектора, J выходов которого являются группой соответствующих J прямых выходов первого анализатора приоритетов. Запрещающий вход первого преобразователя подключен к запрещающему выходу первого селектора, J входов которого соединены с соответствующими J входами первого преобразователя и являются соответствующими J входами первого анализатора приоритетов.

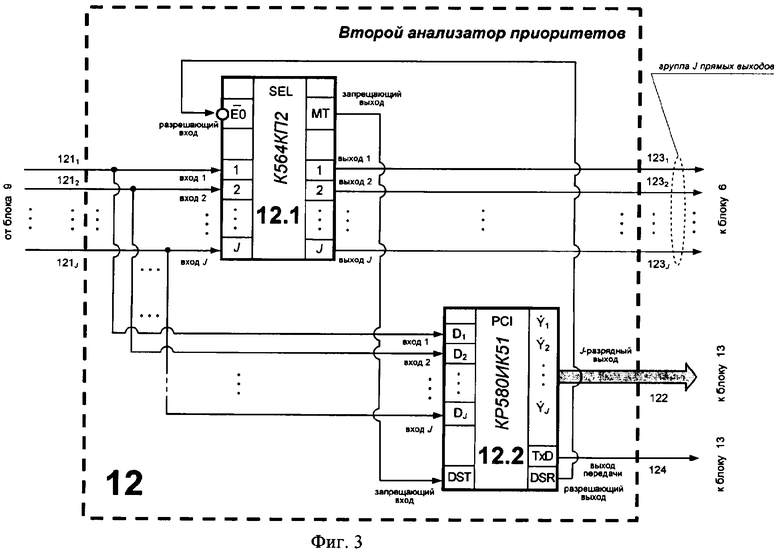

Второй анализатор приоритетов состоит из второго селектора и второго преобразователя, предназначенного для регистрации данных, характеризующих приоритет для очереди второго порядка и преобразования этих данных из параллельного кода в последовательный. При этом J-разрядный выход второго преобразователя является J-разрядным выходом второго анализатора приоритетов, выход передачи второго преобразователя является контрольным выходом второго анализатора приоритетов, разрешающий выход второго преобразователя соединен с инверсным разрешающим входом второго селектора, J выходов которого являются группой соответствующих J прямых выходов второго анализатора приоритетов. Запрещающий вход второго преобразователя подключен к запрещающему выходу второго селектора, J входов которого соединены с соответствующими J входами второго преобразователя и являются соответствующими J входами второго анализатора приоритетов.

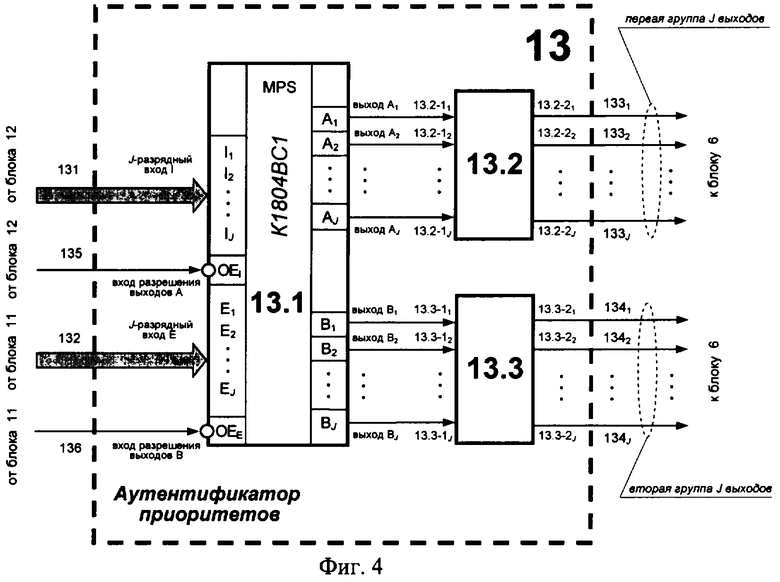

Аутентификатор приоритетов состоит из программируемого вычислителя, первого и второго запоминающих элементов, предназначенных для записи и хранения кода, содержащего верифицированные результаты анализа приоритетов - кода, соответствующего наименьшему номеру абонентского блока, содержащему сигнал запроса из очереди соответственно второго и первого порядка. При этом J-разрядный вход I и J-разрядный вход Е программируемого вычислителя являются соответственно первым и вторым J-разрядными входами аутентификатора приоритетов, вход разрешения выходов А и вход разрешения выходов В программируемого вычислителя являются соответственно первым и вторым контрольными входами аутентификатора приоритетов, J выходов А и J выходов В программируемого вычислителя соединены соответственно с J входами первого и J входами второго запоминающих элементов. Причем J выходов первого и J выходов второго запоминающих элементов являются соответствующими J выходами соответственно первой и второй групп J выходов аутентификатора приоритетов.

Благодаря новой совокупности существенных признаков, за счет введения первого и второго анализатора приоритетов, обеспечивающих, соответственно, анализ данных об истинном номере абонента для очереди первого и второго порядка, с точки зрения достоверности распознавания приоритета абонента и за счет введения аутентификатора приоритетов, обеспечивающего математически корректную поддержку принятия (в динамике функционирования вычислительной системы) достоверного решения о наименьшем номере абонента (т.е. о его наивысшем приоритете), в заявленном устройстве достигается возможность предварительного анализа и верификации номера абонента, обуславливающая повышение достоверности аутентификации абонентов в условиях, присущих реальной динамике процесса функционирования систем обмена данными и ЛВС - в условиях недостоверности (недостаточности, неполноты, а зачастую и противоречивости) данных, характеризующих приоритет конкретного абонента при обслуживании разноприоритетных запросов.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественных всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного устройства условию патентоспособности «новизна».

Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности «изобретательский уровень».

Заявленное устройство поясняется чертежами, на которых представлены:

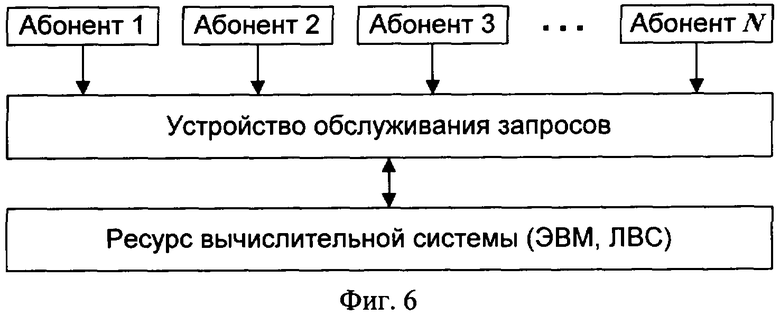

на фиг.1 - структурная схема устройства обслуживания разноприоритетных запросов абонентов вычислительной системы;

на фиг.2 - структурная схема первого анализатора приоритетов;

на фиг.3 - структурная схема второго анализатора приоритетов;

на фиг.4 - структурная схема аутентификатора приоритетов;

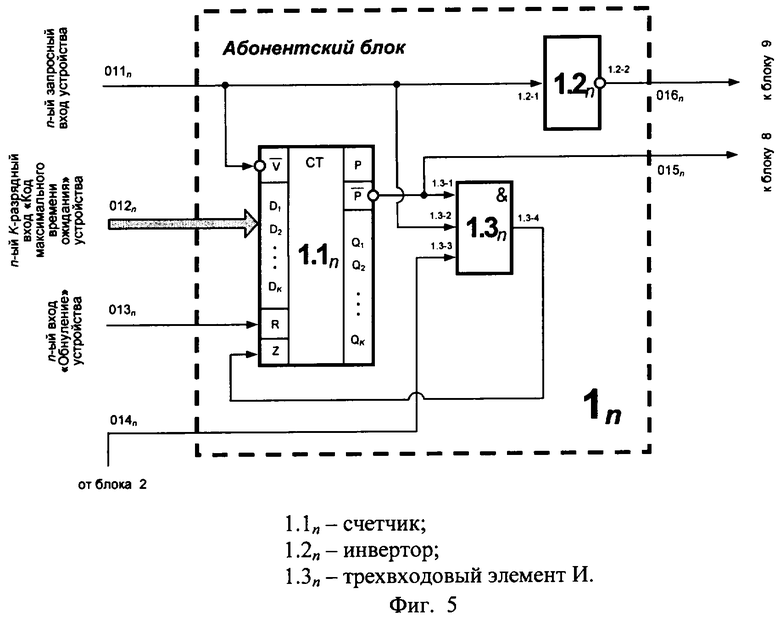

на фиг.5 - структурная схема абонентского блока;

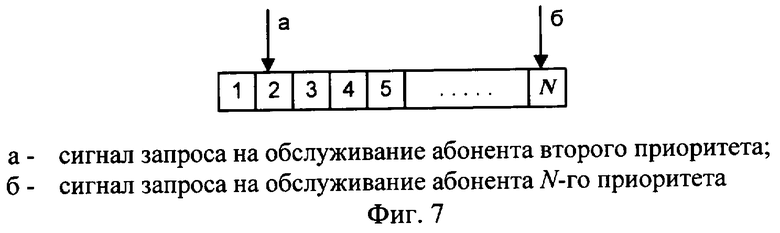

на фиг.6 - структура вычислительной системы;

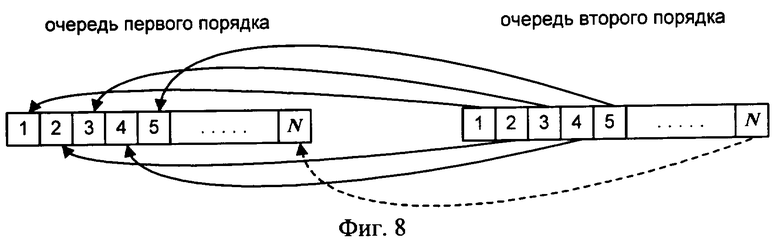

на фиг.7 - размещение сигналов запросов в очереди второго порядка;

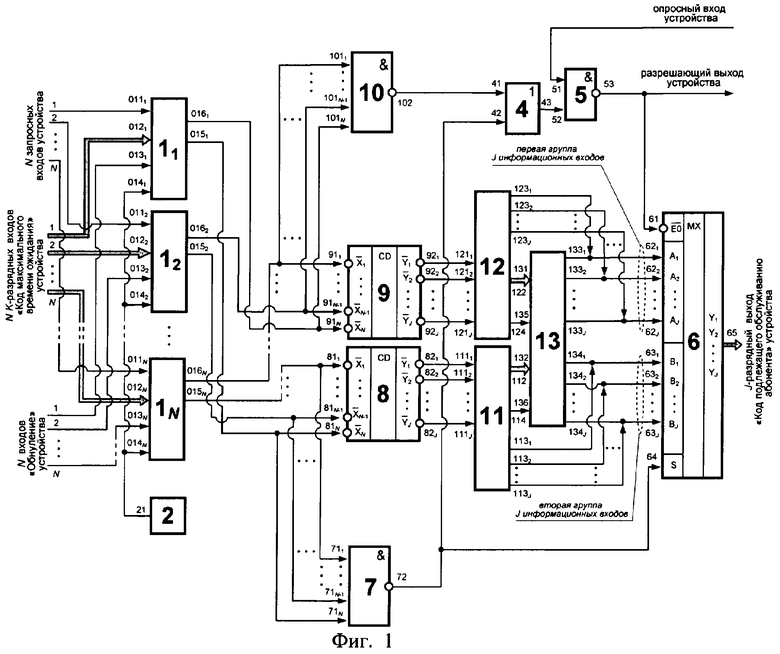

на фиг.8 - порядок переноса запросов из очереди второго порядка в очередь первого порядка.

Устройство обслуживания разноприоритетных запросов абонентов вычислительной системы, изображенное на фиг.1, состоит из N≥2 абонентских блоков 11-1N (АБ), генератора тактовых импульсов 2, элемента ИЛИ 4, элемента И-НЕ 5, селектора-мультиплексора 6, первого 7 и второго 10 N-входовых элементов И-НЕ, первого 8 и второго 9 шифраторов приоритетов, первого 11 и второго 12 анализаторов приоритетов, аутентификатора приоритетов 13. При этом J-разрядный, где J=]log2N[, выход 65 селектора-мультиплексора 6 является J-разрядным выходом «Код подлежащего обслуживанию абонента» устройства. Выход 21 генератора тактовых импульсов 2 подключен к тактовым входам 0141-014N каждого из N абонентских блоков 11-1N, запросные входы 0111-011N и K-разрядные входы «Код максимального времени ожидания» 0121-012N каждого из N абонентских блоков 11-1N, где К≥2 - разрядность кода максимального времени ожидания обслуживания запросов, являются соответствующими N запросными входами и N K-разрядными входами «Код максимального времени ожидания» устройства. Входы «Обнуление» 0131-013N каждого из N абонентских блоков 11-1N являются соответствующими N входами «Обнуление» устройства. Каждый из N входов первого 7 и второго 10 N-входовых элементов И-НЕ (соответственно 711-71N и 1011-101N) подключены к соответствующим N инверсным входам (811-81N и 911-91N) соответственно первого 8 и второго 9 шифраторов приоритетов. Выходы первого 7 и второго 10 N-входовых элементов И-НЕ (соответственно 72 и 102) подключены соответственно к второму 42 и первому 41 входам элемента ИЛИ 4, выход 43 которого подключен к второму входу 52 элемента И-НЕ 5, первый вход 51 которого является опросным входом устройства. Выход 53 элемента И-НЕ 5 подключен к инверсному разрешающему входу 61 селектора-мультиплексора 6 и является разрешающим выходом устройства. Управляющий вход 64 селектора-мультиплексора 6 подключен к второму входу 42 элемента ИЛИ 4. При этом n-е, где n=1, 2, ..., N, инверсные входы (соответственно n-й вход 81n из 811-81N и n-й вход 91n из 911-91N) первого 8 и второго 9 шифраторов приоритетов подключены соответственно к первому 015(N-1)n и второму 016(N+1)-n сигнальным выходам ((N+1)-n)-го абонентского блока 1(N-1)-n. Каждый из J инверсных выходов (соответственно 821-82J и 921-91J) первого 8 и второго 9 шифраторов приоритетов подключены к J входам (1111-111J и 1211-121J) соответственно первого 11 и второго 12 анализаторов приоритетов, J-разрядные выходы 112 и 122 которых соединены соответственно с вторым 132 и первым 131 J-разрядными входами аутентификатора приоритетов 13. Контрольные выходы 114 и 124 первого 11 и второго 12 анализаторов приоритетов подключены соответственно к второму 136 и первому 135 контрольным входам аутентификатора приоритетов 13. При этом J выходов первой 1331-133J и второй 1341-134J группы J выходов аутентификатора приоритетов 13 соединены с соответствующими J входами соответственно первой 621-62J и второй 631-63J групп J информационных входов селектора-мультиплексора 6 и подключены к соответствующим J прямым выходам (1231-123J и 1131-113J) групп J прямых выходов соответственно второго 12 и первого 11 анализаторов приоритетов.

Число «N, (N≥2)» (абонентских блоков, входов, выходов и т.п.) определяется в соответствии с возможным количеством абонентов вычислительной системы и, как правило, составляет от 2 (двух) до 50 (пятидесяти). Число «K, (К≥2)» характеризует разрядность кода максимального времени ожидания обслуживания запросов абонентов и, как правило, составляет от 2 (двух) до 10 (десяти).

Первый анализатор приоритетов 11 (фиг.2) предназначен для предварительного анализа данных об истинном номере (приоритете) абонента для очереди разноприоритетных запросов первого порядка. Первый анализатор приоритетов 11 состоит из первого селектора 11.1 и первого преобразователя 11.2, J-разрядный выход которого является J-разрядным выходом 112 первого анализатора приоритетов 11. Выход передачи T×D первого преобразователя 11.2 является контрольным выходом 114 первого анализатора приоритетов 11. Разрешающий выход DSR первого преобразователя 11.2 соединен с инверсным разрешающим входом  первого селектора 11.1, J выходов которого являются соответствующими J прямыми выходами группы J прямых выходов 1131-113J первого анализатора приоритетов 11. Запрещающий вход DST первого преобразователя 11.2 подключен к запрещающему выходу МТ первого селектора 11.1, J входов которого соединены с соответствующими J входами первого преобразователя 11.2 и являются соответствующими J входами 1111-111J первого анализатора приоритетов 11.

первого селектора 11.1, J выходов которого являются соответствующими J прямыми выходами группы J прямых выходов 1131-113J первого анализатора приоритетов 11. Запрещающий вход DST первого преобразователя 11.2 подключен к запрещающему выходу МТ первого селектора 11.1, J входов которого соединены с соответствующими J входами первого преобразователя 11.2 и являются соответствующими J входами 1111-111J первого анализатора приоритетов 11.

Первый селектор 11.1 первого анализатора приоритетов 11 предназначен для осуществления процедуры селекции данных об истинном номере (приоритете) абонента для очереди разноприоритетных запросов первого порядка и принятия решения о математической природе этих данных - данные, характеризующих приоритет конкретного абонента определены (распознаны) однозначно или неоднозначно (недостоверно, неполно) и нуждаются в верификации. Первый селектор 11.1 может быть технически реализован в виде серийно выпускаемого селектора на КМДП-структурах с одним инверсным разрешающим входом и одним запрещающим выходом, на базе интегральной микросхемы серии 564 (например, SEL К564КП2), как показано в литературе [Мальцев П.П., Долидзе Н.С.и др. Цифровые интегральные микросхемы: справочник. - М.: Радио и связь, 1994. С.28-33].

Первый преобразователь 11.2 первого анализатора приоритетов 11 предназначен для регистрации данных, характеризующих приоритет абонентов для очереди разноприоритетных запросов первого порядка и преобразования этих данных из параллельного кода в последовательный. Первый преобразователь 11.2 может быть технически реализован в виде универсального программируемого синхронно-асинхронного приемопередатчика на базе интегральной микросхемы PCI КР580ИК51, описанной в [Гришин Г.Г., Мошков А.А., Ольшанский О.В. и др. Микропроцессоры: Справочное пособие для разработчиков судовой РЭА. 2-е изд. - Л.: Судостроение, 1988. С.66-74, рис.3.14].

Второй анализатор приоритетов 12 (фиг.3) предназначен для предварительного анализа данных об истинном номере (приоритете) абонента для очереди разноприоритетных запросов второго порядка. Второй анализатор приоритетов 12 состоит из второго селектора 12.1 и второго преобразователя 12.2, J-разрядный выход которого является J-разрядным выходом 122 второго анализатора приоритетов 12. Выход передачи T×D второго преобразователя 12.2 является контрольным выходом 124 второго анализатора приоритетов 12. Разрешающий выход DSR второго преобразователя 12.2 соединен с инверсным разрешающим входом  второго селектора 12.1, J выходов которого являются соответствующими J прямыми выходами группы J прямых выходов 1231-123J второго анализатора приоритетов 12. Запрещающий вход DST второго преобразователя 12.2 подключен к запрещающему выходу МТ второго селектора 12.1, J входов которого соединены с соответствующими J входами второго преобразователя 12.2 и являются соответствующими J входами 1211-121J второго анализатора приоритетов 12.

второго селектора 12.1, J выходов которого являются соответствующими J прямыми выходами группы J прямых выходов 1231-123J второго анализатора приоритетов 12. Запрещающий вход DST второго преобразователя 12.2 подключен к запрещающему выходу МТ второго селектора 12.1, J входов которого соединены с соответствующими J входами второго преобразователя 12.2 и являются соответствующими J входами 1211-121J второго анализатора приоритетов 12.

Второй селектор 12.1 второго анализатора приоритетов 12 предназначен для осуществления процедуры селекции данных об истинном номере (приоритете) абонента для очереди разноприоритетных запросов второго порядка и принятия решения о математической природе этих данных - данные, характеризующие приоритет конкретного абонента, определены (распознаны) однозначно или неоднозначно (недостоверно, неполно) и нуждаются в верификации. Второй селектор 12.1 представляет собой серийно выпускаемый селектор на КМДП-структурах с одним инверсным разрешающим входом и одним запрещающим выходом, реализуемый на базе интегральной микросхемы серии 564 (например, SEL К564КП2), как показано в литературе [Мальцев П.П., Долидзе И.С.и др. Цифровые интегральные микросхемы: справочник. - М.: Радио и связь, 1994. С.28-33].

Второй преобразователь 12.2 второго анализатора приоритетов 12 предназначен для регистрации данных, характеризующих приоритет абонентов для очереди разноприоритетных запросов второго порядка и преобразования этих данных из параллельного кода в последовательный. Техническая реализация второго преобразователя 12.2 может быть осуществлена в виде типового универсального программируемого синхронно-асинхронного приемопередатчика, на базе интегральной микросхемы PCI КР580ИК51, описанной в [Гришин Г.Г., Мошков А.А., Ольшанский О.В. и др. Микропроцессоры: Справочное пособие для разработчиков судовой РЭА. 2-е изд. - Л.: Судостроение, 1988. С.66-74, рис.3.14].

Аутентификатор приоритетов 13, структурная схема которого приведена на фиг.4, предназначен для записи, хранения результатов анализа приоритетов и математически корректной верификации наименьшего номера абонента (верификации абонента с наивысшим приоритетом) путем преобразования определенных (распознанных) неоднозначно (недостоверно, неполно) исходных данных, характеризующих приоритет абонентов, к виду, пригодному для однозначного принятия достоверного решения об уровне приоритета конкретного абонента вычислительной системы.

Аутентификатор приоритетов 13 состоит из программируемого вычислителя 13.1, первого 13.2 и второго 13.3 запоминающих элементов. При этом J-разрядный вход I и J-разрядный вход Е программируемого вычислителя 13.1 являются соответственно первым 131 и вторым 132 J-разрядными входами аутентификатора приоритетов 13. Вход OEI разрешения выходов А и вход ОЕE разрешения выходов В программируемого вычислителя 13.1 являются соответственно первым 135 и вторым 136 контрольными входами аутентификатора приоритетов 13, J выходов А (A1-AJ) и J выходов В (B1-BJ) программируемого вычислителя 13.1 соединены соответственно с J входами 13.2-11-13.2-1J первого 13.2 и J входами 13.3-11-13.3-1J второго 13.3 запоминающих элементов. Причем J выходов 13.2-21-13.2-2J первого 13.2 и J выходов 13.3-21-13.2-2J второго 13.3 запоминающих элементов являются соответствующими J выходами соответственно первой 1331-133J и второй 1341-134J групп J выходов аутентификатора приоритетов 13.

Программируемый вычислитель 13.1 аутентификатора приоритетов 13 предназначен для осуществления процедуры преобразования определенных (распознанных) неоднозначно (недостоверно, неполно) исходных данных, характеризующих приоритет абонентов, к виду, пригодному для однозначного принятия достоверного решения об уровне приоритета конкретного абонента.

Программируемый вычислитель 13.1 представляет собой серийно выпускаемую микропроцессорную секцию (МПС или MPS - Micro-Processoring Section) типа MPS K1804BC1, подробно описанную в [Гришин Г.Г., Мошков А.А., Ольшанский О.В. и др. Микропроцессоры: Справочное пособие для разработчиков судовой РЭА. 2-е изд. - Л.: Судостроение, 1988. С.243-281, рис.7.1 и 7.2]. Программируемый вычислитель 13.1 в виде микропроцессорной секции MPS K1804BC1 используется как программируемое параллельное арифметико-логическое устройство (АЛУ), обладающее возможностью наращивания разрядности и имеющее два J-разрядных входа, где J=]log2N[, два входа разрешения выходов и две группы выходов по J выходов в каждой группе.

Первый 13.2 и второй 13.3 запоминающие элементы аутентификатора приоритетов 13 аналогичны по структуре, функциональному предназначению и служат для записи и хранения кода, содержащего верифицированные результаты анализа приоритетов - кода, соответствующего наименьшему номеру АБ, содержащему сигнал запроса из очереди соответственно второго и первого порядка. Первый 13.2 и второй 13.3 запоминающие элементы могут быть технически реализованы на базе серийно выпускаемого программируемого запоминающего устройства с J входами и J выходами в соответствии с описанием, представленным в работе [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С.197-199, рис.6.10].

Абонентские блоки 11-1N, входящие в общую структурную схему, предназначены для контроля поступления сигналов запросов, контроля оставшегося времени ожидания, а также выработки управляющих сигналов по истечении установленного времени ожидания для каждого запроса. Принцип действия и структурная схема (фиг.5) любого n-го АБ (1n) из N абонентских блоков аналогичны, известны и подробно описаны в прототипе (см. патент РФ №2186420, G 06 F 9/46, 2002, бюл. №21).

Генератор тактовых импульсов 2, входящий в общую структурную схему, предназначен для выработки синхронизирующей последовательности импульсов. Техническая реализация генератора тактовых импульсов 2 возможна на базе серийно выпускаемого генератора тактовых импульсов, описанного в работе [Шило В.Л. Популярные цифровые микросхемы. Справочник. - М.: Радио и связь, 1987. С.50-53].

Элемент ИЛИ 4, входящий в общую структурную схему, предназначен для объединения выходных сигналов определенного логического уровня, поступающих с выходов первого 7 и второго 10 N-входовых элементов И-НЕ. Элемент ИЛИ 4 может быть технически реализован на базе серийно выпускаемого элемента ИЛИ, подробно описанного в [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С.24-26, рис.1.7].

Элемент И-НЕ 5, входящий в общую структурную схему, предназначен для выработки сигналов низкого либо высокого логического уровня и соответственно разрешения либо запрещения трансляции данных селектору-мультиплексору 6. Элемент И-НЕ 5 может быть технически реализован на основе серийно выпускаемого элемента И-НЕ, как показано в [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С.26-28, рис.1.9(а)].

Селектор-мультиплексор 6, входящий в общую структурную схему, предназначен для коммутации либо J первичных 621-62J либо J вторичных 631-63J входов селектора-мультиплексора 6 на его J-разрядный выход 65. Частный случай технической реализации селектора-мультиплексора 6 описан в [Мальцев П.П., Долидзе Н.С.и др. Цифровые интегральные микросхемы: справочник. - М.: Радио и связь, 1994. С.34-35].

Первый 7 и второй 10 N-входовые элементы И-НЕ, входящие в общую структурную схему, аналогичны по структуре и принципу действия, предназначены для установления высокого уровня выходного сигнала при наличии в очереди (соответственно первого и второго порядка) хотя бы одного сигнала запроса. Первый 7 и второй 10 N-входовые элементы И-НЕ могут быть технически реализованы на основе серийно выпускаемого многовходового элемента И-НЕ, как показано в [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С.26-28, рис.1.9(б)].

Первый 8 и второй 9 шифраторы приоритетов, входящие в общую структурную схему, аналогичны по структуре и принципу действия, предназначены для преобразования сигнала низкого уровня на одном из их входов в двоичный код на выходе, причем преобразование осуществляется с учетом предварительных приоритетов сигналов, соответствующих начальным (не верифицированным) номерам входов. Первый 8 и второй 9 шифраторы приоритетов могут быть технически реализованы на базе серийно выпускаемых шифраторов, как показано в [Шило В.Л. Популярные цифровые микросхемы. Справочник. - М.: Радио и связь, 1987. С.147-148].

Устройство обслуживания разноприоритетных запросов абонентов вычислительной системы функционирует следующим образом. Известно [1-5], что с точки зрения верификации абонента с наивысшим приоритетом, существует возможность распознавания (определения) данных, характеризующих приоритет абонентов, заданных как количественно, так и качественно (недостоверно, неполно, противоречиво). Эта возможность реализуется с использованием нейросетевых вычислительных методов и алгоритмов, позволяющих путем последовательных нейросетевых преобразований данных, характеризующих приоритет абонентов, осуществить переход от недостоверно (недостаточно, неполно) распознанных (определенных) данных, к виду данных, пригодному для однозначного принятия достоверного решения об уровне приоритета конкретного абонента вычислительной системы.

При этом начальный номер (приоритет) абонента, под которым он запросил ресурс вычислительной системы, может быть верифицирован на основе математических методов принятия решений в слабоструктурированных задачах - нейросетевых вычислительных методов и алгоритмов, которые достаточно просто могут быть аппаратно реализуемы.

Нейросетевые вычислительные методы и алгоритмы работают на основе экспертных оценок, а для решения задачи объединения мнений экспертов, знания которых используются для верификации приоритета абонента, используется один из типовых вычислительных алгоритмов теории нейронных сетей - нейросетевой экстраполирующий вычислительный алгоритм или так называемая экстраполирующая нейронная сеть (ЭНС), являющаяся разновидностью известных вычислительных моделей ассоциативной памяти [1-5].

Вычислительный нейросетевой алгоритм (экстраполирующая нейронная сеть) такого класса состоит из двух слоев вычислителей (нейронов) - входного слоя Sa и выходного слоя Sb. Входной слой Sa состоит из Jвх нейронов, обладающих набором прямых и обратных связей с Jвых нейронами выходного слоя Sb, причем количество входных и выходных образов J равно (J=Jвх=Jвых=]log2N[) и зависит от количества экспертов и соответствующего количества входов устройств аппаратной реализации нейросетевого алгоритма. В нашем случае J может принимать значения от 2 (двух) до 20 (двадцати), соответствующие количеству входов микропроцессорной секции MPS K1804BC1, на базе которой построен программируемый вычислитель 13.1 аутентификатора приоритетов 13.

В ЭНС используется так называемая когнитивная карта, полностью задаваемая матрицей связей и характеризующая причинно-следственные отношения текущих приоритетов абонентов, влияющих на принятие в устройстве достоверного решения об уровне приоритета конкретного абонента вычислительной системы. Когнитивная карта формулируется экспертами, принцип формирования когнитивных карт подробно описан в работах [2, 3]. При этом J ветвей алгоритма отвечают за преобразование мнений экспертов о недостоверно (неполно) распознанных (определенных) приоритетах абонентов к виду, пригодному для однозначного распознавания приоритета.

На вход вычислительного нейросетевого алгоритма (ЭНС) поступает входной образ - данные, характеризующие приоритет абонентов и распознанные (определенные) как количественно, так и качественно (недостоверно, неполно, противоречиво). Определяется, какие из данных, характеризующих приоритет абонентов в данный момент времени, распознаны количественно, а какие данные идентифицированы неопределенно (недостоверно, неточно). В целях верификации абонента с наивысшим приоритетом необходимо математически корректно, используя ЭНС, преобразовать распознанные недостоверно (неполно) данные.

Этапы функционирования вычислительного нейросетевого алгоритма (ЭНС) подробно, алгоритмически и аналитически описаны в [3].

На выходе вычислительного нейросетевого алгоритма (ЭНС) имеем выходной образ - данные, которые полностью (достоверно) характеризуют интегрированное мнение экспертов о принадлежности приоритета конкретного абонента к пространству достоверных, верифицированных приоритетов высшего порядка.

Рассмотренный в [1, 2, 5] и детально описанный в [3] вычислительный нейросетевой алгоритм позволяет устранить неопределенность (недостоверность, неполноту) данных, характеризующих приоритет абонентов, позволяет однозначно распознать (верифицировать) истинный приоритет конкретного абонента в текущий момент времени, а в конечном итоге, повысить достоверность аутентификации абонентов в условиях, присущих реальной динамике процесса функционирования систем обмена данными и ЛВС - в условиях неопределенности (недостоверности, недостаточности, неполноты и противоречивости) данных об истинном номере абонента.

С учетом этого осуществляется достоверная аутентификация (распознавание приоритетов) и, в соответствии с верифицированным приоритетом, реализация потребностей абонентов в вычислительном ресурсе в заявленном устройстве. Перед началом работы устройства с его K-разрядных входов «Код максимального времени ожидания» через K-разрядные входы 0121-012N абонентских блоков 11-1N на информационные входы D1-DK счетчиков 1.11-1.1N (см. фиг.5) поступают значения кода, задающие максимальное время ожидания обслуживания запросов. Тем самым обеспечивается инициализация счетчиков 1.11-1.1N АБ 11-1N. Причем наименьшему времени ожидания соответствует наибольший код, являющийся дополнением до максимального числа, представимого в K-разрядном коде.

В начальный период, когда запросы на обслуживание отсутствуют, на всех N запросных входах устройства и на соответствующих запросных входах 0111-011N абонентских блоков 11-1N установлены низкие логические уровни. Трехвходовые элементы И 1.31-1.3N всех АБ закрыты, тактовые импульсы от генератора тактовых импульсов 2 через трехвходовые элементы И 1.31-1.3N на счетные входы Z счетчиков 1.11-1.1N АБ 11-1N не поступают. Со стороны вычислительного ресурса (ЭВМ, ЛВС) отсутствует сигнал об освобождении ресурса (на опросном входе устройства установлен низкий логический уровень). На вторых 0161-016N и первых 0151-015N сигнальных выходах АБ 11-1N установлены высокие логические уровни. Соответственно, на выходе 72 первого N-входового элемента И-НЕ 7 и выходе 102 второго N-входового элемента И-НЕ 10 установлены низкие логические уровни. При этом J-разрядный выход 65 селектора-мультиплексора 6 разомкнут, поскольку на его инверсном разрешающем входе 61 ( ) через элемент ИЛИ 4 и элемент И-НЕ 5 установлен высокий логический уровень. Устройство готово к работе и ожидает сигналы запросов, вырабатываемые абонентами вычислительной системы (см. фиг.6).

) через элемент ИЛИ 4 и элемент И-НЕ 5 установлен высокий логический уровень. Устройство готово к работе и ожидает сигналы запросов, вырабатываемые абонентами вычислительной системы (см. фиг.6).

При возникновении потребности в вычислительном ресурсе абонентами вычислительной системы генерируются сигналы запросов, которые поступают на устройство обслуживания запросов и помещаются в очередь второго порядка. Сигналом запроса от абонента считается сигнал высокого уровня, установленный на любом из запросных входов 0111-011N соответствующего АБ 11-1N. При этом на вторых сигнальных выходах 0161-016N этих АБ через инверторы 1.21-1.2N установятся сигналы низкого уровня. Совокупность сигналов низкого уровня на вторых сигнальных выходах 0161-016N АБ образует очередь второго порядка. Положение сигнала запроса в очереди второго порядка определяется его начальным (не верифицированным) приоритетом: сигнал запроса, поступивший от абонента с наименьшим начальным (не верифицированным) номером, обладает предварительным наивысшим приоритетом (см. фиг.7). На счетные входы Z счетчиков 1.11-1.1N АБ 11-1N, содержащих сигналы запросов, поступают импульсы с выхода 21 генератора тактовых импульсов 2 по цепи: тактовые входы 0141-014N АБ 11-1N, открытые трехвходовые элементы И 1.31-1.3N АБ 11-1N. Счетчики 1.11-1.1N каждого АБ выполняют функцию таймеров, которые контролируют истечение допустимого времени нахождения запросов в очереди второго порядка путем суммирования поступающих на их счетный вход Z тактовых импульсов и формируют сигнал переполнения на инверсных выходах  счетчиков 1.11-1.1N через установленный интервал времени, определяемый кодами начального заполнения счетчиков и частотой тактовых импульсов.

счетчиков 1.11-1.1N через установленный интервал времени, определяемый кодами начального заполнения счетчиков и частотой тактовых импульсов.

Сигналы с вторых сигнальных выходов 0161-016N АБ 11-1N поступают на инверсные входы 911-91N второго шифратора приоритетов 9, обеспечивающего преобразование сигналов запросов в J-разрядный код, соответствующий номеру АБ с учетом его начального (не верифицированного) приоритета. При этом сигнал с второго сигнального выхода 0161 первого АБ (11) поступает на N-й инверсный вход 91N второго шифратора приоритетов 9, сигнал с второго сигнального выхода 0162 второго АБ (12) поступает на (N-1)-й инверсный вход 91N-1 второго шифратора приоритетов 9, сигнал с второго сигнального выхода 016n n-го АБ (In) поступает на ((N+1)-n)-й инверсный вход 91(N-1)-n второго шифратора приоритетов 9, сигнал с второго сигнального выхода 016N N-го АБ (1N) поступает на первый инверсный вход 911 второго шифратора приоритетов 9. Указанный способ подключения вторых сигнальных выходов 0161-016N АБ обусловлен тем, что выходы 921-92J второго шифратора приоритетов 9 инверсные, то есть для получения на его J инверсных выходах кода, соответствующего АБ с начальным наименьшим номером (не верифицированным наибольшим приоритетом) из числа тех АБ 11-1N, на вторых сигнальных выходах 0161-016N которых установлены низкие логические уровни (сигналы запросов), следует подключить вторые сигнальные выходы АБ к входам 911-91N второго шифратора приоритетов 9 в обратном порядке. При наличии в очереди второго порядка хотя бы одного сигнала запроса, на выходе 102 второго N-входового элемента И-НЕ 10 установится высокий уровень.

С инверсных выходов 921-92J второго шифратора приоритетов 9 код, соответствующий АБ с начальным наименьшим номером, т.е. код абонента, который априори (изначально, до верификации) аутентифицирован как абонент высшего приоритета, поступает на J входов 1211-121J второго анализатора приоритетов 12. Предварительный анализ данных в интересах определения истинного номера (приоритета) абонента в рамках очереди разно-приоритетных запросов второго порядка осуществляется во втором анализаторе приоритетов 12 следующим образом. С входов 1211-121J второго анализатора приоритетов 12 код, соответствующий АБ с начальным наименьшим номером, поступает на J входов второго селектора 12.1 и на J входов второго преобразователя 12.2 (см. фиг.3).

Процедура селекции данных об истинном номере (приоритете) абонента для очереди разноприоритетных запросов второго порядка и принятие решения о математической природе этих данных осуществляется во втором селекторе 12.1 следующим образом. Код абонента, который априори (изначально, до верификации) аутентифицирован как абонент высшего приоритета, поступает на J входов второго селектора 12.1, который рассчитан на хранение в каждой ячейке пяти разрядов поступающей информации.

Если число разрядов кода, соответствующего АБ с начальным наименьшим номером, превышает данное количество, значит, с точки зрения математики - эта кодовая последовательность содержит избыточность, обусловливающую недостоверность (неполноту) данных, характеризующих приоритет конкретного абонента при обслуживании разноприоритетных запросов в очереди второго порядка. В этом случае с запрещающего выхода МТ второго селектора 12.1 на запрещающий вход DST второго преобразователя 12.2 поступает в двоичном коде команда, инициирующая начало регистрации данных, характеризующих приоритет абонентов для очереди разноприоритетных запросов второго порядка и начало преобразования этих данных из параллельного кода в последовательный. Второй преобразователь 12.2 регистрирует полученные через свои J входов данные, признанные вторым селектором 12.1 недостоверными (неполными, неоднозначными), и преобразовывает их из параллельного кода в последовательный. При этом с разрешающего выхода DSR второго преобразователя 12.2 на инверсный разрешающий вход  второго селектора 12.1 поступает в двоичном коде команда, инициирующая запрет трансляции информации с J выходов второго селектора 12.1 на соответствующие прямые выходы группы J прямых выходов 1231-123J второго анализатора приоритетов 12. Последовательный код абонента, который недостоверно (неполно, неоднозначно) аутентифицирован как абонент высшего приоритета, с J-разрядного выхода второго преобразователя 12.2 через J-разрядный выход 122 второго анализатора приоритетов 12 поступает на первый 131 J-разрядный вход аутентификатора приоритетов 13. С выхода передачи T×D второго преобразователя 12.2 через контрольный выход 124 второго анализатора приоритетов 12 на первый контрольный вход 135 аутентификатора приоритетов 13 поступает команда, инициирующая начало процедуры верификации приоритета.

второго селектора 12.1 поступает в двоичном коде команда, инициирующая запрет трансляции информации с J выходов второго селектора 12.1 на соответствующие прямые выходы группы J прямых выходов 1231-123J второго анализатора приоритетов 12. Последовательный код абонента, который недостоверно (неполно, неоднозначно) аутентифицирован как абонент высшего приоритета, с J-разрядного выхода второго преобразователя 12.2 через J-разрядный выход 122 второго анализатора приоритетов 12 поступает на первый 131 J-разрядный вход аутентификатора приоритетов 13. С выхода передачи T×D второго преобразователя 12.2 через контрольный выход 124 второго анализатора приоритетов 12 на первый контрольный вход 135 аутентификатора приоритетов 13 поступает команда, инициирующая начало процедуры верификации приоритета.

Если с входов 1211-121J второго анализатора приоритетов 12 на J входов второго селектора 12.1 и на J входов второго преобразователя 12.2 поступает код в количестве пяти разрядов, значит данный код не нуждается в верификации, достоверно (полно, однозначно) соответствует АБ с наименьшим номером (абоненту высшего приоритета). В этом случае, не получая на свой запрещающий вход DST соответствующую команду, второй преобразователь 12.2 запирает свой J-разрядный выход и выход передачи T×D, а второй селектор 12.1 транслирует параллельный код, однозначно соответствующий наименьшему номеру АБ, содержащему сигнал запроса из очереди второго порядка, со своих J выходов через соответствующие прямые выходы группы J прямых выходов 1231-123J второго анализатора приоритетов 12 на соответствующие входы первой группы J информационных входов 621-62J селектора-мультиплексора 6.

Данные, характеризующие приоритет конкретного абонента в очереди второго порядка, определенные (распознанные) во втором анализаторе приоритетов 12 как неоднозначные (недостоверные, неполные) и нуждающиеся в верификации, поступают с J-разрядного выхода 122 второго анализатора приоритетов 12 на первый 131 J-разрядный вход аутентификатора приоритетов 13, который осуществляет запись, хранение результатов анализа приоритетов и математически корректную верификацию наименьшего номера абонента (верификации абонента с наивысшим приоритетом). Преобразование определенных (распознанных) неоднозначно (недостоверно, неполно) исходных данных, характеризующих приоритет абонентов, к виду, пригодному для однозначного принятия достоверного решения об уровне приоритета конкретного абонента вычислительной системы, осуществляется в программируемом вычислителе 13.1 аутентификатора приоритетов 13 следующим образом.

Программируемый вычислитель 13.1 аутентификатора приоритетов 13 (см. фиг.4) технически реализуется на базе программируемой (с точки зрения матрицы весов - причинно-следственных когнитивных мнений о приоритете, формулируемых экспертами) микропроцессорной секции, выполняющей роль программируемого параллельного АЛУ, реализующего вычислительный нейросетевой алгоритм (ЭНС), описанный в работе [3]. Если информации на первом 131 J-разрядном входе аутентификатора приоритетов 13 и на J-разрядном входе I программируемого вычислителя 13.1 нет, соответственно не поступает команда, инициирующая начало процедуры верификации приоритета, на первый контрольный вход 135 аутентификатора приоритетов 13 и на вход разрешения выходов A (OEI) программируемого вычислителя 13.1. В этом случае J выходов А (A1-AJ) программируемого вычислителя 13.1, а значит и J выходов 13.2-21-13.2-2J первого запоминающего элемента 13.2 заблокированы. В противном случае есть сигнал на входе разрешения выходов А (OEI) программируемого вычислителя 13.1 и неоднозначно (недостоверно, неполно) определенные исходные данные, характеризующие приоритет абонентов, поступают на J-разрядный вход I программируемого вычислителя 13.1, реализующего функции программируемого параллельного АЛУ.

Программируемый вычислитель 13.1, реализующий функции программируемого параллельного АЛУ, опираясь на запрограммированные значения элементов матрицы весов - аналитически описанные причинно-следственные когнитивные мнения о приоритете, формулируемые экспертами, осуществляет процедуру вычисления (экстраполяции) в соответствии с вычислительным нейросетевым алгоритмом, подробно описанным в работе [3]. При этом входные ячейки I1-IJ соответствуют разряду (1, ..., J) последовательного кода, поступающего на J-разрядный вход I программируемого вычислителя 13.1, и являются равноправными J входами (Jвх) вычислителей (нейронов) входного слоя Sa ЭНС, на которую подаются значения J разрядов кода, имеющего физический смысл неоднозначно (недостоверно, неполно) определенного приоритета абонента. Набор прямых и обратных связей Jвх с Jвых ЭНС, программно реализованный в рамках программируемого вычислителя 13.1, позволяет учитывать весовые коэффициенты приоритетов для очереди второго порядка, сформулированные экспертами, и получать на J выходах А (A1-AJ) программируемого вычислителя 13.1 экстраполированные значения J разрядов параллельного кода, имеющего физический смысл верифицированного (математически корректно проверенного) наименьшего номера АБ, т.е. наивысшего приоритета абонента в очереди второго порядка, определенного на основе верифицированных (достоверных, полных) исходных данных. При этом подача на j-й, где j=1, 2, ..., J, вход (Ij) программируемого вычислителя 13.1 значения разряда кода, характеризующего неоднозначно (недостоверно, неполно) определенный приоритет абонента, инициирует выдачу с соответствующего j-го выхода (Аj) программируемого вычислителя 13.1 (выхода j-го нейрона выходного слоя Sb) запрограммированного, согласно вычислительному нейросетевому алгоритму, описанному в [3], значения, математически корректно преобразованного относительно достоверного разряда кода, характеризующего истинный приоритет абонента для очереди второго порядка.

В результате на J выходах A (A1-AJ) программируемого вычислителя 13.1 и на соответствующих J входах 13.2-11-13.2-1J первого запоминающего элемента 13.2 получаем информацию, характеризующую (на основе анализа полученного в рамках ЭНС интегрированного мнения экспертов) истинный приоритет абонента для очереди второго порядка, преобразованный (верифицированный) в интересах повышения достоверности аутентификации данного абонента.

Первый запоминающий элемент 13.2 записывает, хранит и выдает со своих J выходов 13.2-21-13.2-2J через соответствующие выходы первой группы J выходов 1331-133J аутентификатора приоритетов 13 на соответствующие входы первой группы J информационных входов 621-61J селектора-мультиплексора 6 код, содержащий верифицированные результаты анализа приоритетов - код, однозначно соответствующий наименьшему номеру АБ, содержащему сигнал запроса из очереди второго порядка.

По мере освобождения вычислительного ресурса (ресурса ЭВМ, ЛВС) вырабатывается сигнал высокого уровня, который поступает на опросный вход устройства и далее на первый вход 51 элемента И-НЕ 5. При наличии хотя бы одного запроса в очереди второго порядка на выходе 53 элемента И-НЕ 5 установится сигнал низкого уровня, который разрешит трансляцию данных селектору-мультиплексору 6. На управляющем входе 64 (входе S) селектора-мультиплексора 6 установлен низкий уровень (на первых сигнальных выходах 0151-015N всех АБ - высокий уровень), следовательно, на J-разрядный, где J=]log2N[, выход 65 селектора-мультиплексора 6 и на J-разрядный выход «Код подлежащего обслуживанию абонента» устройства будет скоммутирован верифицированный код, достоверно характеризующий приоритет абонента для очереди второго порядка. Эти данные поступают с выходов первой группы J выходов 1331-133J аутентификатора приоритетов 13 на соответствующие входы первой группы J информационных входов 621-62N (входов A1-AJ) селектора-мультиплексора 6 и однозначно соответствуют наименьшему номеру АБ, содержащему сигнал запроса из очереди второго порядка.

После удовлетворения потребности в вычислительном ресурсе n-й абонент снимает сигнал запроса с соответствующего n-го запросного входа устройства, с запросного входа 011n соответствующего АБ (1n), и производит сброс счетчика 1.1n соответствующего АБ 1n по n-му входу «Обнуление» устройства и входу «Обнуление» 013n соответствующего АБ 1n (см. фиг.5). При этом на первом и втором сигнальных выходах 015n и 016n соответствующего АБ 1n будут высокие уровни.

В случае, если один или несколько запросов в результате создавшейся очереди достигли максимального времени ожидания, происходит переполнение счетчиков 1.11-1.1N соответствующих АБ 11-1N, формирование на их инверсных выходах переполнения  , а следовательно, и на первых сигнальных выходах 0151-015N соответствующих АБ 11-1N сигналов низкого уровня, что соответствует переносу запросов в очередь первого порядка на места, соответствующие их изначальным (не верифицированным) приоритетам (см. фиг.6), в целях их дальнейшего внеочередного, по отношению к очереди второго порядка, обслуживания. При этом запираются соответствующие трехвходовые элементы И 1.31-1.3N (фиг.5), запрещая поступление тактовых импульсов на счетные входы Z соответствующих счетчиков 1.11-1.1N. Совокупность сигналов низкого уровня на первых сигнальных выходах 0151-015N соответствующих АБ 11-1N образует очередь первого порядка. Обслуживание запросов из очереди первого порядка осуществляется с учетом достоверной аутентификации (определения их истинных и однозначно распознанных приоритетов), аналогично запросам из очереди второго порядка. Сигналы запросов для очереди первого порядка с первых сигнальных выходов 0151-015N соответствующих АБ 11-1N поступают (в обратном порядке) на инверсные входы 811-81N первого шифратора приоритетов 8. При этом формирование кода, соответствующего наименьшему номеру АБ, содержащему сигнал запроса из верифицированной очереди первого порядка, осуществляется первым шифратором приоритетов 8 тем же способом, что и для очереди второго порядка.

, а следовательно, и на первых сигнальных выходах 0151-015N соответствующих АБ 11-1N сигналов низкого уровня, что соответствует переносу запросов в очередь первого порядка на места, соответствующие их изначальным (не верифицированным) приоритетам (см. фиг.6), в целях их дальнейшего внеочередного, по отношению к очереди второго порядка, обслуживания. При этом запираются соответствующие трехвходовые элементы И 1.31-1.3N (фиг.5), запрещая поступление тактовых импульсов на счетные входы Z соответствующих счетчиков 1.11-1.1N. Совокупность сигналов низкого уровня на первых сигнальных выходах 0151-015N соответствующих АБ 11-1N образует очередь первого порядка. Обслуживание запросов из очереди первого порядка осуществляется с учетом достоверной аутентификации (определения их истинных и однозначно распознанных приоритетов), аналогично запросам из очереди второго порядка. Сигналы запросов для очереди первого порядка с первых сигнальных выходов 0151-015N соответствующих АБ 11-1N поступают (в обратном порядке) на инверсные входы 811-81N первого шифратора приоритетов 8. При этом формирование кода, соответствующего наименьшему номеру АБ, содержащему сигнал запроса из верифицированной очереди первого порядка, осуществляется первым шифратором приоритетов 8 тем же способом, что и для очереди второго порядка.

С инверсных выходов 821-82J первого шифратора приоритетов 8 код, соответствующий АБ с начальным наименьшим номером, т.е. код абонента, который априори (изначально, до верификации) аутентифицирован в очереди первого порядка как абонент высшего приоритета, поступает на J входов 1111-111J первого анализатора приоритетов 11. В первом анализаторе приоритетов 11 осуществляется процедура предварительного анализа данных об истинном номере (приоритете) абонента для очереди разноприоритетных запросов первого порядка, аналогичная описанной ранее процедуре, осуществляемой во втором анализаторе приоритетов 12 для очереди второго порядка. Параллельный код, однозначно соответствующий наименьшему номеру АБ, содержащему сигнал запроса из очереди первого порядка, с выходов группы J прямых выходов 1131-113J первого анализатора приоритетов 11 поступает на соответствующие входы второй группы J информационных входов 631-63J селектора-мультиплексора 6. В противном случае последовательный код, неоднозначно (недостоверно, неполно) характеризующий наименьший номер АБ, содержащий сигнал запроса из очереди первого порядка, с J-разрядного выхода 112 первого анализатора приоритетов 11 поступает на второй J-разрядный вход 132 аутентификатора приоритетов 13, а разрешающий сигнал поступает с контрольного выхода 114 первого анализатора приоритетов 11 на второй контрольный вход 136 аутентификатора приоритетов 13.

Аналогично аутентификации абонентов из очереди второго порядка запись, хранение результатов анализа приоритетов для очереди первого порядка и преобразование определенных (распознанных) неоднозначно (недостоверно, неполно) исходных данных, характеризующих приоритет абонентов, к виду, пригодному для однозначного принятия достоверного решения об уровне приоритета конкретного абонента вычислительной системы, осуществляется в аутентификаторе приоритетов 13. Это происходит после того, как с контрольного выхода 114 первого анализатора приоритетов 11 через второй контрольный вход 136 аутентификатора приоритетов 13 получен сигнал на вход разрешения выходов В (ОЕE) программируемого вычислителя 13.1 и неоднозначно (недостоверно, неполно) определенные исходные данные, характеризующие приоритет абонентов в очереди первого порядка, поступают с J-разрядного выхода 112 первого анализатора приоритетов 11 через вторичный J-разрядный вход 132 аутентификатора приоритетов 13 на J-разрядный вход Е программируемого вычислителя 13.1, реализующего функции программируемого параллельного АЛУ в соответствии с запрограммированным нейросетевым алгоритмом.

На J выходах В (B1-BJ) программируемого вычислителя 13.1 и на соответствующих J входах 13.3-11-13.3-1J второго запоминающего элемента 13.3 получаем информацию, характеризующую (на основе анализа полученного в рамках ЭНС интегрированного мнения экспертов) истинный приоритет абонента для очереди первого порядка, преобразованный (верифицированный) в интересах повышения достоверности аутентификации данного абонента. Второй запоминающий элемент 13.3 записывает, хранит и выдает со своих J выходов 13.3-21-13.3-2J через соответствующие выходы второй группы J выходов 1341-134J аутентификатора приоритетов 13 на соответствующие входы второй группы J информационных входов 631-63J селектора-мультиплексора 6 код, содержащий верифицированные результаты анализа приоритетов - код, однозначно соответствующий наименьшему номеру АБ, содержащему сигнал запроса из очереди первого порядка.

В итоге, на J входах первой группы J информационных входов 621-62J и на J входах второй группы J информационных входов 631-63J селектора-мультиплексора 6 имеем достоверный (верифицированный) код, однозначно характеризующий приоритет абонентов для очереди второго и первого порядка соответственно, полученный на основе математически корректного, в рамках аппарата теории нейронных вычислительных сетей, анализа интегрированного мнения экспертов об истинном приоритете этих абонентов.

При наличии запроса с однозначно распознанным приоритетом в очереди первого порядка их внеочередное, по отношению к запросам из очереди второго порядка, обслуживание обеспечивается сигналом высокого уровня на выходе 72 первого N-входового элемента И-НЕ 7, который, поступая на управляющий вход 64 (вход S) селектора-мультиплексора 6, коммутирует на J-разрядный выход 65 селектора-мультиплексора 6 и на J-разрядный выход «Код подлежащего обслуживанию абонента» устройства код, поступивший на J входов второй группы J информационных входов 631-63N (входов B1-BJ) селектора-мультиплексора 6 и соответствующий верифицированному (достоверно определенному) наименьшему номеру АБ, содержащему сигнал запроса из очереди первого порядка. Сигнал высокого уровня на выходе 72 первого N-входового элемента И-НЕ 7 будет до тех пор, пока в очереди первого порядка есть хотя бы один запрос.

После освобождения ресурса, выделенного в интересах очередного запроса абонента с соответствующим верифицированным приоритетом из очереди первого порядка (с истекшим временем ожидания), каждый n-й абонент снимает сигнал запроса с запросного входа 011n соответствующего АБ (1n) и производит сброс счетчика 1.1n соответствующего АБ 1n по n-му входу «Обнуление» устройства и входу «Обнуление» 013n АБ 1n. Это предопределяет установление высокого уровня на выходе  счетчика 1.1n соответствующего АБ 1n, что, в свою очередь, обуславливает установку на первом и втором сигнальных выходах 015n и 016n этого АБ 1n высоких уровней. Это позволяет устройству после выполнения всех запросов абонентов соответствующего верифицированного приоритета с истекшим временем ожидания перейти к обслуживанию вновь поступивших либо ждущих своей очереди запросов в порядке, определенном логикой работы устройства.

счетчика 1.1n соответствующего АБ 1n, что, в свою очередь, обуславливает установку на первом и втором сигнальных выходах 015n и 016n этого АБ 1n высоких уровней. Это позволяет устройству после выполнения всех запросов абонентов соответствующего верифицированного приоритета с истекшим временем ожидания перейти к обслуживанию вновь поступивших либо ждущих своей очереди запросов в порядке, определенном логикой работы устройства.

Таким образом, в рамках верификации абонента с наивысшим приоритетом в очереди второго порядка, на J выходах группы J прямых выходов 1231-123J второго анализатора приоритетов 12 либо на J выходах первой группы J выходов 1331-133J аутентификатора приоритетов 13, а значит, и на соответствующих J входах первой группы J информационных входов 621-61J селектора-мультиплексора 6 имеем достоверный (верифицированный) код, однозначно характеризующий приоритет абонентов для очереди второго порядка. В рамках верификации абонента с наивысшим приоритетом в очереди первого порядка, на J выходах группы J прямых выходов 1131-113J первого анализатора приоритетов 11 либо на J выходах второй группы J выходов 1341-134J аутентификатора приоритетов 13, а значит, и на соответствующих J входах второй группы J информационных входов 631-63J селектора-мультиплексора 6 имеем достоверный (верифицированный) код, однозначно характеризующий приоритет абонентов для очереди первого порядка.

Анализ принципа работы заявленного устройства обслуживания разноприоритетных запросов абонентов вычислительной системы показывает очевидность того факта, что наряду с сохраненными и описанными в прототипе возможностями по повышению быстродействия и надежности устройство способно в текущем масштабе времени, математически корректно и более достоверно идентифицировать наименьший номер АБ (наивысший приоритет абонента), инициирующего сигнал запроса в условиях, присущих реальной динамике процесса функционирования систем обмена данными и ЛВС.

Данное устройство обеспечивает повышение достоверности аутентификации абонентов в условиях недостоверности (недостаточности, неполноты, а зачастую и противоречивости) данных, характеризующих приоритет конкретного абонента при обслуживании разно-приоритетных запросов, что существенно расширяет область применения устройства, расширяет функциональные возможности подсистем массового обслуживания в рамках систем обмена данными и локальных вычислительных сетей, где заявленное устройство обслуживания разноприоритетных запросов абонентов вычислительной системы будет использовано.

ИСТОЧНИКИ ИНФОРМАЦИИ

1. Уоссермен Ф. Нейрокомпьютерная техника: Теория и практика. - М.: Мир, 1992. - 240 с.

2. Kosko В. Fuzzy cognitive maps // International Journal of Man-Machine Studies. V.24. N.Y., 1986. P.16-22.

3. Щербаков М.А. Искусственные нейронные сети. - Пенза: ПГТУ, 1996. - 44 с.

4. Трахтенгерц Э.А. Компьютерная поддержка принятия решений. - М.: СИНТЕГ, 1998. - 342 с.

5. Горбань А.Н., Россиев Д.А. Нейронные сети на персональном компьютере. - Новосибирск: Наука. Сибирская издательская фирма РАН, 1996. - 146 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ОБСЛУЖИВАНИЯ РАЗНОПРИОРИТЕТНЫХ ЗАПРОСОВ АБОНЕНТОВ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 2005 |

|

RU2287179C1 |

| УСТРОЙСТВО ОБСЛУЖИВАНИЯ РАЗНОПРИОРИТЕТНЫХ ЗАПРОСОВ АБОНЕНТОВ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 2005 |

|

RU2296361C1 |

| УСТРОЙСТВО ОБСЛУЖИВАНИЯ РАЗНОПРИОРИТЕТНЫХ ЗАПРОСОВ АБОНЕНТОВ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 2015 |

|

RU2589363C1 |

| УСТРОЙСТВО ОБСЛУЖИВАНИЯ РАЗНОПРИОРИТЕТНЫХ ЗАПРОСОВ АБОНЕНТОВ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 2001 |

|

RU2186420C1 |

| СПОСОБ ОБСЛУЖИВАНИЯ РАЗНОПРИОРИТЕТНЫХ ЗАПРОСОВ АБОНЕНТОВ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 2001 |

|

RU2179737C1 |

| Устройство поиска информации | 2017 |

|

RU2656736C1 |

| ГЕНЕРАТОР СЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2022 |

|

RU2797406C1 |

| Генератор случайной последовательности | 2016 |

|

RU2635898C1 |

| ГЕНЕРАТОР СЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2019 |

|

RU2717629C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2014 |

|

RU2553093C1 |

Изобретение относится к области вычислительной техники и может быть использовано в системах обмена данными и локальных вычислительных сетях. Техническим результатом является повышение достоверности аутентификации абонентов, генерирующих сигналы запросов к ресурсам вычислительной системы в условиях, присущих реальной динамике процесса функционирования систем обмена данными и локальных вычислительных сетей, т.е. в условиях неопределенности данных об истинном номере абонента. Устройство содержит N≥2 абонентских блоков, генератор тактовых импульсов, элемент ИЛИ, элемент И-НЕ, селектор-мультиплексор, N-входовые элементы И-НЕ, шифраторы приоритетов, анализаторы приоритетов, аутентификатор приоритетов. 3 з.п. ф-лы, 8 ил.

| УСТРОЙСТВО ОБСЛУЖИВАНИЯ РАЗНОПРИОРИТЕТНЫХ ЗАПРОСОВ АБОНЕНТОВ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 2001 |

|

RU2186420C1 |

| СПОСОБ ОБСЛУЖИВАНИЯ ЗАПРОСОВ ПОЛЬЗОВАТЕЛЕЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ (ВАРИАНТЫ) | 1998 |

|

RU2140666C1 |

| Многоканальное устройство с динамическим изменением приоритета | 1988 |

|

SU1562912A1 |

| DE 3334123 A1, 11.04.1985 | |||

| JP 62065137 A, 24.03.1987. | |||

Авторы

Даты

2006-12-27—Публикация

2005-05-19—Подача