Изобретение относится к вычислительной технике и предназначено для генерации случайной последовательности значений из заданного множества значений с требуемыми характеристиками генерируемой последовательности.

Известен генератор случайной последовательности по патенту РФ №2250489 «Генератор случайной последовательности», МПК G06F 7/58, H03K 3/84 опубликованный 20.04.2005, Бюл. №11, включающий источник случайных чисел, N-разрядный селектор-мультиплексор, оперативное запоминающее устройство, блок контроля интервалов, блок контроля количества генераций, J-входовый элемент ИЛИ, блок элементов И. Этот аналог обеспечивает формирование конечной последовательности заданных значений набора данных по заданному в интервальном виде закону распределения со случайной частостью появления значений в пределах интервалов.

Недостатком данного устройства является формирование ограниченной последовательности заданных значений набора данных, что обусловлено реализованным в устройстве подходе к заданию закона распределения, который предполагает указание абсолютных значений требуемого числа наблюдений элементов заданного набора данных на выходе устройства для каждого из интервалов.

Известен генератор случайной последовательности по патенту РФ №2313125 «Генератор случайной последовательности» МПК G06F 7/58, H03K 3/84, G07C 15/00, опубликованный 20.12.2007, Бюл. №35. Это устройство содержит источник случайных чисел, оперативное запоминающее устройство, N-разрядный селектор-мультиплексор, K Р-разрядных регистров, K блоков сравнения, шифратор приоритетов, N инверторов. Устройство обеспечивает формирование неограниченной последовательности заданных значений набора данных, частность появления которых определяется только заданным законом распределения.

Однако данное устройство имеет недостаток - узкую область применения, ограниченную возможностью моделирования дискретных случайных процессов, характеризующихся отсутствием вероятностной связи между состояниями случайного процесса (между генерируемыми значениями заданного набора данных), отсутствием вероятностной зависимости каждого очередного состояния случайного процесса от предыдущего.

Из известных наиболее близким аналогом (прототипом), по своей технической сущности, заявленному устройству является генератор случайной последовательности по патенту РФ №2542903 «Генератор случайной последовательности», МПК G06F 7/58, G06F 1/02, опубликованный 27.02.2015, Бюл. №6. Устройство-прототип содержит источник случайных чисел, оперативное запоминающее устройство, первый и второй селекторы-мультиплексоры, K блоков хранения границ интервалов, K блоков сравнения, шифратор приоритетов, N инверторов, первый и второй регистр. Устройство-прототип обеспечивает формирование значений элементов случайного процесса, учитывая вероятностные связи между состояниями этого процесса.

Однако прототип имеет недостаток - относительно низкую достоверность генерируемой последовательности заданных значений набора данных в условиях, характерных для случайных процессов, протекающих в реальных системах, в реальной вычислительной технике, когда значения элементов случайного процесса зависят не только от вероятностных, но и от недостоверных (недостаточно, неполно и противоречиво заданных) связей между состояниями этого процесса.

Данное устройство позволяет получать текущие вероятностно-временные значения элементов заданного набора данных с учетом наличия вероятностной (заданной количественно) связи каждого очередного значения с предыдущим, в то время как при исследовании многих случайных процессов, протекающих в реальных системах, широкое применение находят нейросетевые модели [1], объективно основанные на недостоверно (недостаточно, неоднозначно, неполно и противоречиво) заданных значениях параметров случайного процесса, где связь каждого очередного значения с предыдущим (вероятности переходов) из последовательности генерируемых значений носит не только количественный вероятностный (достоверно идентифицируемый), но и неоднозначный (неполный и противоречивый) характер, традиционно описываемый с привлечением математики искусственных нейронных сетей.

Целью изобретения является разработка устройства, обеспечивающего повышение достоверности генерируемой последовательности за счет обеспечения возможности генерации заданных значений набора данных с учетом наличия не только вероятностной, но и неоднозначной (неполной, противоречивой) связи каждого очередного значения с предыдущим, создание генератора случайной последовательности, способного с высокой достоверностью формировать значения элементов случайного процесса, характеризующего реальное поведение сложной вычислительной системы - когда взаимосвязи параметров случайного процесса, взаимосвязи каждого очередного из последовательности генерируемых значений с предыдущим значением имеют как количественно (вероятностно), так и качественно (неоднозначно, неполно и противоречиво) выраженный физический смысл.

Указанная цель достигается тем, что в известный генератор случайной последовательности, содержащий K блоков сравнения, где K≥2 - максимально возможная мощность заданного множества генерируемых значений, первый селектор-мультиплексор, второй селектор-мультиплексор, оперативное запоминающее устройство, шифратор приоритетов, N инверторов, где N=[log2K] - число двоичных разрядов, достаточное для адресации элементов заданного множества генерируемых значений, K блоков хранения границ интервалов, выполненных в виде оперативных запоминающих устройств, первый регистр, второй регистр и источник случайных чисел, дополнительно включены блок проверки значений вероятностей переходов, предназначенный для предварительного анализа, выявления (селекции) неоднозначно (неполно, противоречиво) идентифицируемых значений вероятностей переходов случайного процесса из состояния в состояние, и блок коррекции значений вероятностей переходов, предназначенный для трансформирования исходных данных (значений вероятностей переходов случайного процесса из состояния в состояние), заданных в неоднозначной (неполной, противоречивой) форме к виду, позволяющему достоверно (однозначно, полно, непротиворечиво) идентифицировать и трактовать значения вероятностей переходов случайного процесса из состояния в состояние. При этом Р-разрядный, где P>N, выход «Случайное число» источника случайных чисел соединен с Р-разрядными входами «Случайное число» K блоков сравнения, Р-разрядный выход k-го блока хранения границ интервалов, где K=1, 2, …, K, соединен с Р-разрядным входом «Верхняя граница» k-го блока сравнения. Выход «Результат сравнения» k-го блока сравнения соединен с k-м инверсным входом шифратора приоритетов, n-й инверсный выход которого, где n=1, 2, …, N, соединен с входом n-го инвертора. Вход выбора первого селектора-мультиплексора соединен с управляющим входом источника случайных чисел и является управляющим входом генератора, первый N-разрядный информационный вход первого селектора-мультиплексора является первым N-разрядным адресным входом генератора, N-разрядный выход первого селектора-мультиплексора соединен с N-разрядным адресным входом оперативного запоминающего устройства, инверсные входы «Чтение/запись» и «Выбор кристалла» которого являются соответственно первым входом «Чтение/запись» и первым входом «Выбор кристалла» генератора. Причем М-разрядный выход оперативного запоминающего устройства, где М≥2 - количество разрядов, достаточное для представления максимального значения из числа значений, входящих в состав заданного множества генерируемых значений, является М-разрядным выходом «Результат» генератора, М-разрядный информационный вход оперативного запоминающего устройства является М-разрядным информационным входом генератора. При этом Р-разрядный информационный вход k-го блока хранения границ интервалов является k-м Р-разрядным информационным входом генератора, n-й разряд N-разрядного информационного входа второго регистра соединен с инверсным выходом n-го инвертора, a N-разрядный выход второго регистра соединен с N-разрядным входом блока проверки значений вероятностей переходов, N-разрядный корректировочный выход которого подключен к N-разрядному корректировочному входу блока коррекции значений вероятностей переходов, контрольный вход которого соединен с контрольным выходом блока проверки значений вероятностей переходов, N-разрядный прямой выход которого соединен с N-разрядным прямым выходом блока коррекции значений вероятностей переходов и подключен ко второму N-разрядному информационному входу первого селектора-мультиплексора и ко второму N-разрядному информационному входу второго селектора-мультиплексора, первый N-разрядный вход которого является вторым N-разрядным адресным входом генератора, а его N-разрядный выход соединен с N-разрядным информационным входом первого регистра, N-разрядный выход которого соединен с N-разрядными адресными входами каждого из K блоков хранения границ интервалов, соответствующие инверсные входы «Выбор кристалла» и «Чтение/запись» которых объединены между собой и являются соответственно вторым входом «Выбор кристалла» и вторым входом «Чтение/запись» генератора. Вход выбора второго селектора-мультиплексора соединен с управляющим входом источника случайных чисел, входы инициализации первого и второго регистров являются соответственно первым и вторым входом «Установка» генератора, а входы сброса первого и второго регистров объединены и являются входом «Обнуление» генератора.

Блок проверки значений вероятностей переходов, предназначенный для предварительного анализа (селекции) данных об истинных значениях вероятностей переходов случайного процесса из состояния в состояние и принятия решения о математической природе этих данных - данные, характеризующие значения вероятностей переходов идентифицированы (определены) однозначно или неоднозначно (неполно, противоречиво) и нуждаются в верификации, а также для регистрации данных, характеризующих значения вероятностей переходов и преобразования этих данных из параллельного кода в последовательный, состоит из селектора значений вероятностей переходов и преобразователя значений вероятностей переходов, N-разрядный выход которого является N-разрядным корректировочным выходом блока проверки значений вероятностей переходов, выход передачи преобразователя значений вероятностей переходов является контрольным выходом блока проверки значений вероятностей переходов, разрешающий выход преобразователя значений вероятностей переходов соединен с инверсным разрешающим входом селектора значений вероятностей переходов, N-разрядный выход которого является N-разрядным прямым выходом блока проверки значений вероятностей переходов, запрещающий вход преобразователя значений вероятностей переходов подключен к запрещающему выходу селектора значений вероятностей переходов, N-разрядный вход которого соединен с N-разрядным входом преобразователя значений вероятностей переходов и является N-разрядным входом блока проверки значений вероятностей переходов.

Блок коррекции значений вероятностей переходов, предназначенный для преобразования исходных данных (значений вероятностей переходов случайного процесса из состояния в состояние), заданных в неоднозначной (неполной, противоречивой) форме к виду, позволяющему достоверно (однозначно, полно, непротиворечиво) идентифицировать и трактовать значения вероятностей переходов случайного процесса из состояния в состояние, для записи и хранения верифицированных результатов анализа значений вероятностей переходов, а также для преобразования этих данных из последовательного кода в параллельный, состоит из программируемого вычислителя и запоминающего элемента, при этом N-разрядный вход I программируемого вычислителя является N-разрядным корректировочным входом блока коррекции значений вероятностей переходов, вход разрешения выходов программируемого вычислителя является контрольным входом блока коррекции значений вероятностей переходов, N выходов программируемого вычислителя соединены с соответствующими N входами запоминающего элемента, N-разрядный выход которого является N-разрядным прямым выходом блока коррекции значений вероятностей переходов 12.

Благодаря новой совокупности существенных признаков, за счет введения блока проверки значений вероятностей переходов, обеспечивающего предварительное выявление (селекцию) неоднозначно (недостоверно, неполно) идентифицируемых значений вероятностей переходов и принятие решения об их математической природе, а также блока коррекции значений вероятностей переходов, обеспечивающего запись, хранение результатов анализа значений вероятностей переходов и математически корректное вычислительное преобразование (распознавание) этих значений с использованием нейроматематических методов, в заявленном генераторе случайной последовательности достигается возможность повышения достоверности генерируемой последовательности заданных значений набора данных за счет обеспечения возможности генерации последовательности из заданного множества значений с учетом наличия не только вероятностной, но и неоднозначной (неполной, противоречивой) связи каждого очередного значения с предыдущим.

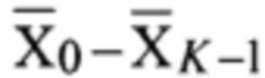

Заявленное устройство поясняется чертежами, на которых:

на фиг. 1 - структурная схема генератора случайной последовательности;

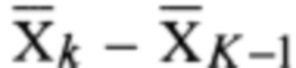

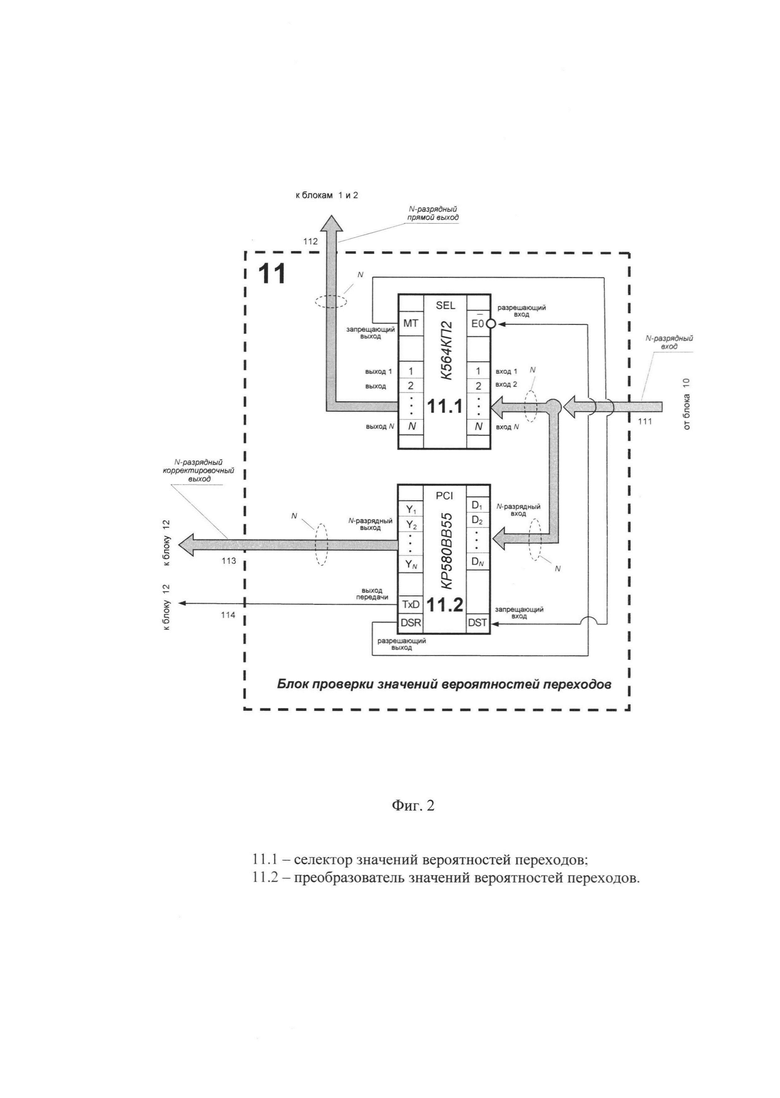

на фиг. 2 - структурная схема блока проверки значений вероятностей переходов 11;

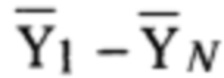

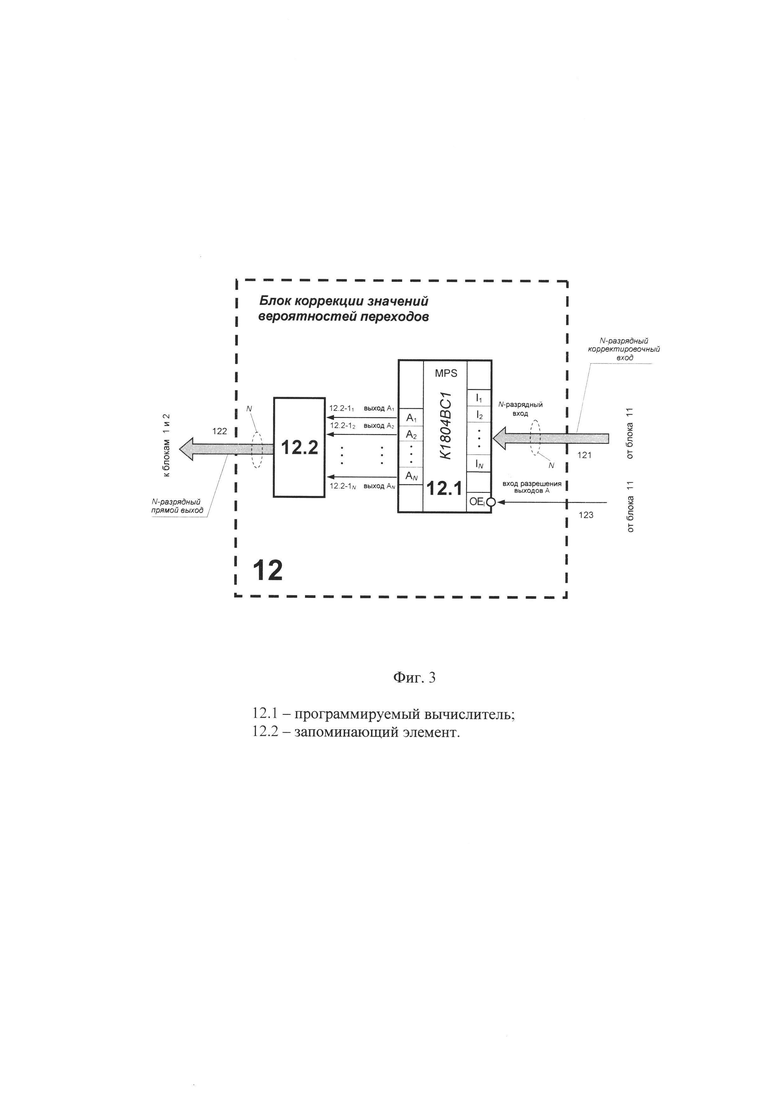

на фиг. 3 - структурная схема блока коррекции значений вероятностей переходов 12;

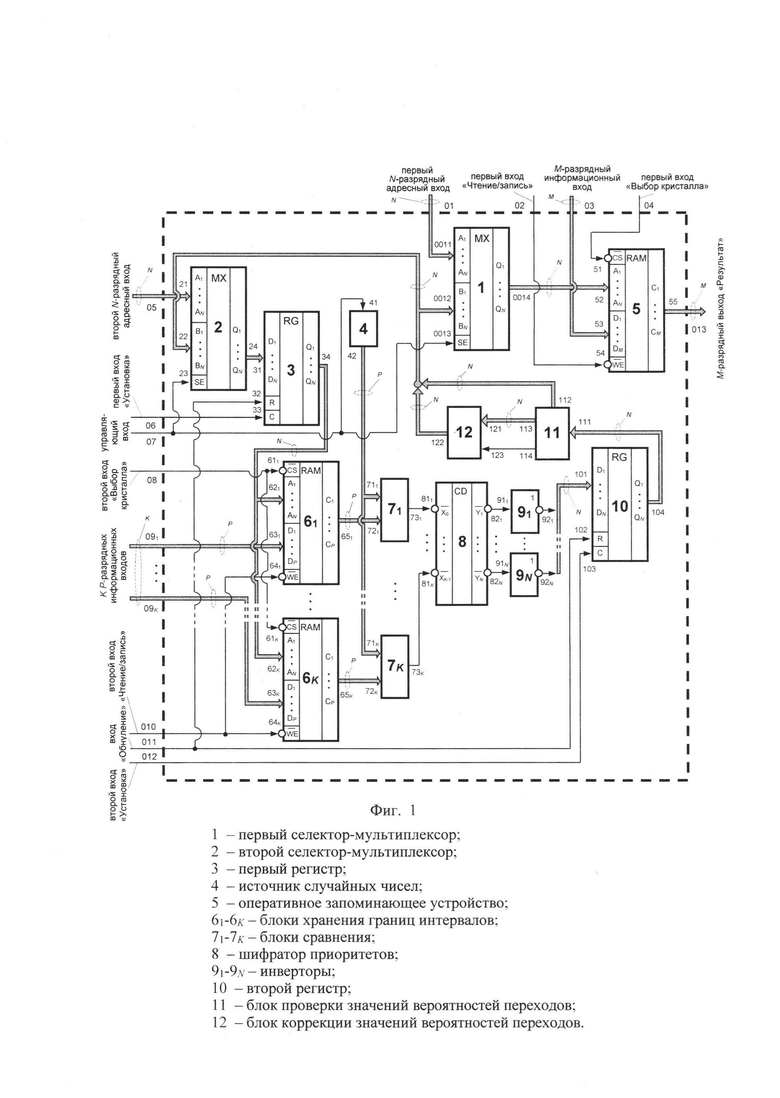

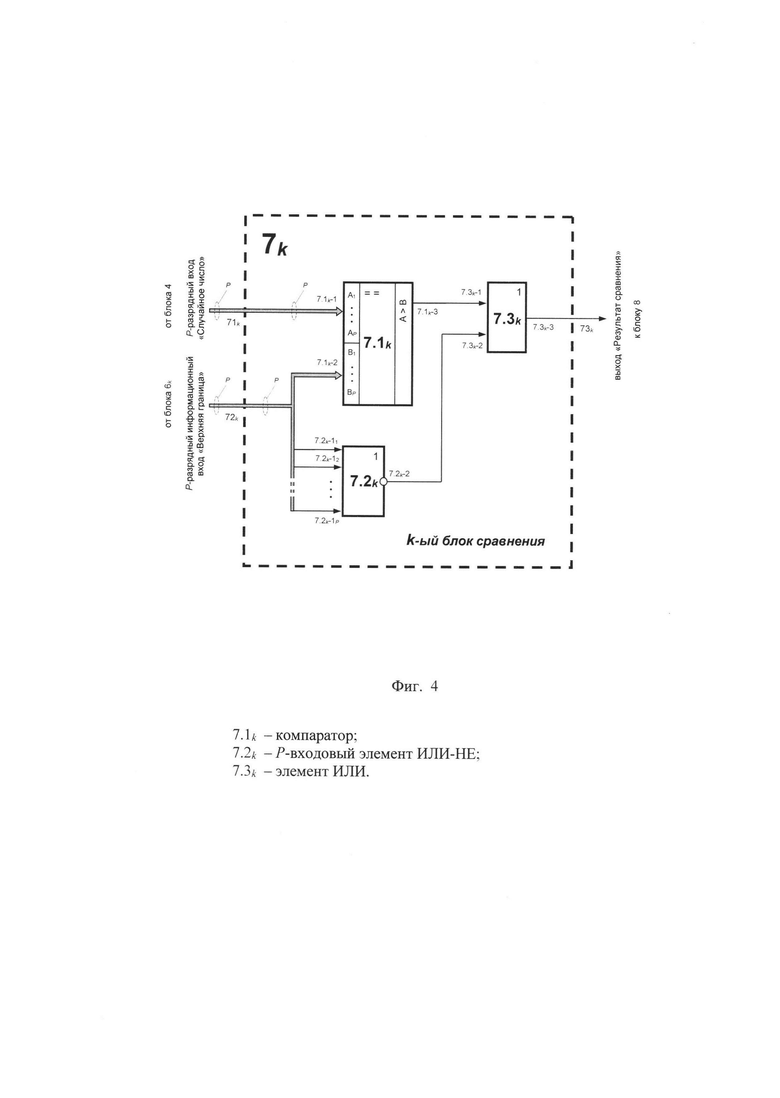

на фиг. 4 - структурная схема блока сравнения.

Генератор случайной последовательности (см. фиг. 1) состоит из первого селектора-мультиплексора 1, второго селектора-мультиплексора 2, первого регистра 3, источника случайных чисел 4, оперативного запоминающего устройства 5, K блоков хранения границ интервалов 61-6K, K блоков сравнения 71-7K, шифратора приоритетов 8, N инверторов 91-9N, второго регистра 10, блока проверки значений вероятностей переходов 11 и блока коррекции значений вероятностей переходов 12.

Элементы соединены между собой следующим образом (см. фиг. 1). Р-разрядный выход «Случайное число» 42 источника случайных чисел 4 соединен с Р-разрядными входами «Случайное число» 711-71K K блоков сравнения 71-7K, Р-разрядный выход 65k k-го блока хранения границ интервалов 6k, где k=1, 2, …, K, соединен с Р-разрядным входом «Верхняя граница» 72k k-го блока сравнения 7k. Выход «Результат сравнения» 73k k-го блока сравнения 7k соединен с k-ым инверсным входом 81k шифратора приоритетов 8, n-й инверсный выход 82n которого, где n=1, 2, …, N, соединен с входом 91n n-го инвертора 9n. Вход выбора 0013 (вход SE) первого селектора-мультиплексора 1 соединен с управляющим входом 41 источника случайных чисел 4 и является управляющим входом 07 генератора, первый N-разрядный информационный вход 0011 (вход для разрядов A1-AN) первого селектора-мультиплексора 1 является первым N-разрядным адресным входом 01 генератора, N-разрядный выход 0014 (выход для разрядов Q1-QN) первого селектора-мультиплексора 1 соединен с N-разрядным адресным входом 52 (входом для разрядов A1-AN) оперативного запоминающего устройства 5, инверсные входы «Чтение/запись» 54 (вход  ) и «Выбор кристалла» 51 (вход

) и «Выбор кристалла» 51 (вход  ) которого являются соответственно первым входом «Чтение/запись» 02 и первым входом «Выбор кристалла» 04 генератора. Причем М-разрядный выход 55 (выход для разрядов C1-СМ) оперативного запоминающего устройства 5 является М-разрядным выходом «Результат» 013 генератора, М-разрядный информационный вход 53 (вход для разрядов D1-DM) оперативного запоминающего устройства 5 является М-разрядным информационным входом 03 генератора. При этом Р-разрядный информационный вход 63k (вход для разрядов D1-DP) k-го блока хранения границ интервалов 6k является k-м Р-разрядным информационным входом 09k генератора, n-й разряд N-разрядного информационного входа 101 второго регистра 10 соединен с инверсным выходом 92n n-го инвертора 9n, а N-разрядный выход 104 второго регистра 10 соединен с N-разрядным входом 111 блока проверки значений вероятностей переходов 11, N-разрядный корректировочный выход 113 которого подключен к N-разрядному корректировочному входу 121 блока коррекции значений вероятностей переходов 12, контрольный вход 123 которого соединен с контрольным выходом 114 блока проверки значений вероятностей переходов 11, N-разрядный прямой выход 112 которого соединен с N-разрядным прямым выходом 122 блока коррекции значений вероятностей переходов 12 и подключен ко второму N-разрядному информационному входу 0012 (входу для разрядов B1-BN) первого селектора-мультиплексора 1 и ко второму N-разрядному информационному входу 22 (входу для разрядов B1-BN) второго селектора-мультиплексора 2, первый N-разрядный вход 21 которого является вторым N-разрядным адресным входом 05 генератора, а его N-разрядный выход 24 соединен с N-разрядным информационным входом 31 первого регистра 3, N-разрядный выход 34 которого соединен с N-разрядными адресными входами 621-62K K блоков хранения границ интервалов 61-6K, соответствующие инверсные входы «Выбор кристалла» 611-61K (входы

) которого являются соответственно первым входом «Чтение/запись» 02 и первым входом «Выбор кристалла» 04 генератора. Причем М-разрядный выход 55 (выход для разрядов C1-СМ) оперативного запоминающего устройства 5 является М-разрядным выходом «Результат» 013 генератора, М-разрядный информационный вход 53 (вход для разрядов D1-DM) оперативного запоминающего устройства 5 является М-разрядным информационным входом 03 генератора. При этом Р-разрядный информационный вход 63k (вход для разрядов D1-DP) k-го блока хранения границ интервалов 6k является k-м Р-разрядным информационным входом 09k генератора, n-й разряд N-разрядного информационного входа 101 второго регистра 10 соединен с инверсным выходом 92n n-го инвертора 9n, а N-разрядный выход 104 второго регистра 10 соединен с N-разрядным входом 111 блока проверки значений вероятностей переходов 11, N-разрядный корректировочный выход 113 которого подключен к N-разрядному корректировочному входу 121 блока коррекции значений вероятностей переходов 12, контрольный вход 123 которого соединен с контрольным выходом 114 блока проверки значений вероятностей переходов 11, N-разрядный прямой выход 112 которого соединен с N-разрядным прямым выходом 122 блока коррекции значений вероятностей переходов 12 и подключен ко второму N-разрядному информационному входу 0012 (входу для разрядов B1-BN) первого селектора-мультиплексора 1 и ко второму N-разрядному информационному входу 22 (входу для разрядов B1-BN) второго селектора-мультиплексора 2, первый N-разрядный вход 21 которого является вторым N-разрядным адресным входом 05 генератора, а его N-разрядный выход 24 соединен с N-разрядным информационным входом 31 первого регистра 3, N-разрядный выход 34 которого соединен с N-разрядными адресными входами 621-62K K блоков хранения границ интервалов 61-6K, соответствующие инверсные входы «Выбор кристалла» 611-61K (входы  ) и «Чтение/запись» 641-64K (входы

) и «Чтение/запись» 641-64K (входы  ) которых объединены между собой и являются соответственно вторым входом «Выбор кристалла» 08 и вторым входом «Чтение/запись» 010 генератора. Вход выбора 23 (вход SE) второго селектора-мультиплексора 2 соединен с управляющим входом 41 источника случайных чисел 4, входы инициализации 33 и 103 (входы С) первого 3 и второго 10 регистров являются соответственно первым 06 и вторым 012 входом «Установка» генератора, а входы сброса 32 и 102 (входы R) первого 3 и второго 10 регистров объединены и являются входом «Обнуление» 011 генератора.

) которых объединены между собой и являются соответственно вторым входом «Выбор кристалла» 08 и вторым входом «Чтение/запись» 010 генератора. Вход выбора 23 (вход SE) второго селектора-мультиплексора 2 соединен с управляющим входом 41 источника случайных чисел 4, входы инициализации 33 и 103 (входы С) первого 3 и второго 10 регистров являются соответственно первым 06 и вторым 012 входом «Установка» генератора, а входы сброса 32 и 102 (входы R) первого 3 и второго 10 регистров объединены и являются входом «Обнуление» 011 генератора.

Число «N, (N=[log2K]; N≥1)» (блоков, разрядов, входов, выходов и т.п.) определяется в соответствии с количеством двоичных разрядов, достаточных для адресации элементов заданного множества генерируемых значений случайной последовательности (т.е. для адресации элементов набора данных) и, как правило, составляет от 2 (двух) до 10 (десяти).

Число «K, (K≥2)» характеризует максимально возможную мощность заданного множества генерируемых значений случайной последовательности (т.е. количество элементов в заданном наборе данных) и, как правило, составляет от 2 (двух) до 500 (пятисот).

Число «М, (М≥2)» характеризует количество двоичных разрядов, достаточное для представления максимального значения из числа значений, входящих в состав заданного множества генерируемых значений случайной последовательности (т.е. для представления значений элементов заданного набора данных) и, как правило, составляет от 2 (двух) до 10 (десяти).

Число «Р, (Р>N)» характеризует разрядность информационных входов генератора и определяется в соответствии с количеством, большим, чем количество двоичных разрядов, достаточных для адресации элементов заданного множества генерируемых значений случайной последовательности и, как правило, составляет от 3 (трех) до 11 (одиннадцати).

Блок проверки значений вероятностей переходов 11, изображенный на фиг. 2, предназначен для предварительного анализа (селекции) данных об истинных значениях вероятностей переходов случайного процесса из состояния в состояние и принятия решения о математической природе этих данных - данные, характеризующие значения вероятностей переходов идентифицированы (определены) однозначно или неоднозначно (неполно, противоречиво) и нуждаются в верификации, а также для регистрации данных, характеризующих значения вероятностей переходов и преобразования этих данных из параллельного кода в последовательный.

Блок проверки значений вероятностей переходов 11 (фиг. 2) состоит из селектора значений вероятностей переходов 11.1 и преобразователя значений вероятностей переходов 11.2, N-разрядный выход которого является N-разрядным корректировочным выходом 113 блока проверки значений вероятностей переходов 11, выход передачи TxD преобразователя значений вероятностей переходов 11.2 является контрольным выходом 114 блока проверки значений вероятностей переходов 11, разрешающий выход DSR преобразователя значений вероятностей переходов 11.2 соединен с инверсным разрешающим входом  селектора значений вероятностей переходов 11.1, N-разрядный выход которого является N-разрядным прямым выходом 112 блока проверки значений вероятностей переходов 11. Запрещающий вход DST преобразователя значений вероятностей переходов 11.2 подключен к запрещающему выходу МТ селектора значений вероятностей переходов 11.1, N-разрядный вход которого соединен с N-разрядным входом преобразователя значений вероятностей переходов 11.2 и является N-разрядным входом 111 блока проверки значений вероятностей переходов 11.

селектора значений вероятностей переходов 11.1, N-разрядный выход которого является N-разрядным прямым выходом 112 блока проверки значений вероятностей переходов 11. Запрещающий вход DST преобразователя значений вероятностей переходов 11.2 подключен к запрещающему выходу МТ селектора значений вероятностей переходов 11.1, N-разрядный вход которого соединен с N-разрядным входом преобразователя значений вероятностей переходов 11.2 и является N-разрядным входом 111 блока проверки значений вероятностей переходов 11.

Селектор значений вероятностей переходов 11.1 блока проверки значений вероятностей переходов 11 предназначен для осуществления процедуры предварительного анализа (селекции) данных об истинных значениях вероятностей переходов случайного процесса из состояния в состояние и принятия решения о математической природе этих данных - данные, характеризующие значения вероятностей переходов идентифицированы (определены) однозначно или неоднозначно (неполно, противоречиво) и нуждаются в верификации. Селектор значений вероятностей переходов 11.1 может быть технически реализован в виде серийно выпускаемого селектора на КМОП (КМДП) структурах с одним инверсным разрешающим входом и одним запрещающим выходом, на базе интегральной микросхемы серии 564 (например, SEL К564КП2), как показано в литературе [Шило В.П. Популярные микросхемы КМОП. Справочник. - М.: Горячая линия Телеком, 2001. - 116 с. С. 68-73].

Преобразователь значений вероятностей переходов 11.2 блока проверки значений вероятностей переходов 11 предназначен для регистрации данных о значениях вероятностей переходов случайного процесса из состояния в состояние и преобразования этих данных из параллельного кода в последовательный. Преобразователь значений вероятностей переходов 11.2 может быть технически реализован в виде микросхемы программируемого параллельного интерфейса КР580ВВ55, описанной в [Микропроцессорная техника. Версия 1.0 [Электронный ресурс]: электрон, учеб. пособие / В.Б. Молодецкий, М.В. Кривенков, А.Н. Пахомов и др. - Электрон, дан. - Красноярск: ИПК СФУ, 2008. - 126 с. С. 41-43, рис. 8.5]

Блок коррекции значений вероятностей переходов 12, изображенный на фиг. 3, предназначен для преобразования исходных данных (значений вероятностей переходов случайного процесса из состояния в состояние), заданных в неоднозначной (неполной, противоречивой) форме к виду, позволяющему достоверно (однозначно, полно, непротиворечиво) идентифицировать и трактовать значения вероятностей переходов случайного процесса из состояния в состояние, для записи и хранения верифицированных результатов анализа значений вероятностей переходов, а также для преобразования этих данных из последовательного кода в параллельный.

Блок коррекции значений вероятностей переходов 12 (фиг. 3) состоит из программируемого вычислителя 12.1 и запоминающего элемента 12.2. При этом N-разрядный вход I программируемого вычислителя 12.1 является N-разрядным корректировочным входом 121 блока коррекции значений вероятностей переходов 12. Вход OEI разрешения выходов А программируемого вычислителя 12.1 является контрольным входом 123 блока коррекции значений вероятностей переходов 12, N выходов A (A1-AN) программируемого вычислителя 12.1 соединены с соответствующими N входами 12.2-11-12.2-1N запоминающего элемента 12.2, N-разрядный выход которого является N-разрядным прямым выходом 122 блока коррекции значений вероятностей переходов 12.

Программируемый вычислитель 12.1 блока коррекции значений вероятностей переходов 12 предназначен для осуществления процедуры преобразования исходных данных (значений вероятностей переходов случайного процесса из состояния в состояние), заданных в неоднозначной (неполной, противоречивой) форме к виду, позволяющему достоверно (однозначно, полно, непротиворечиво) идентифицировать и трактовать значения вероятностей переходов случайного процесса из состояния в состояние. Программируемый вычислитель 12.1 представляет собой серийно выпускаемую микропроцессорную секцию (МПС или MPS - Micro-Processoring Section) типа MPS К1804ВС1, описанную, например, в [Гришин Г.Г., Мошков А.А., Ольшанский О.В. и др. Микропроцессоры: Справочное пособие для разработчиков судовой РЭА. 2-е изд. - Л.: Судостроение, 1988. С. 243-281, рис. 7.1 и 7.2] и в [Угрюмов Е.П. Цифровая схемотехника: учеб. пособие для вузов. - 3-е изд., перераб. и доп.- СПб.: БХВ-Петербург, 2010. - 816 с., С. 371-376, рис. 6.14].

Запоминающий элемент 12.2 блока коррекции значений вероятностей переходов 12 предназначен для записи и хранения верифицированных результатов анализа значений вероятностей переходов, а также для преобразования этих данных из последовательного кода в параллельный. Запоминающий элемент 12.2 может быть технически реализован на базе серийно выпускаемого программируемого динамического оперативного запоминающего устройства с N входами и N-разрядным выходом, в соответствии с описанием, представленным в работе [Основы электроники: учебник для СПО / О.В. Миловзоров, И.Г. Панков. - 5-е изд., перераб. и доп. - М.: Издательство Юрайт, 2016. - 407 с. С. 229-231, рис. 4.3.2].

Первый селектор-мультиплексор 1, входящий в общую структурную схему генератора случайной последовательности, предназначен для коммутации на свой N-разрядный выход сигналов одной из двух групп: с первого N-разрядного информационного входа 0011 (входа для разрядов A1-AN) либо со второго N-разрядного информационного входа 0012 (входа для разрядов B1-BN). Схема построения первого селектора-мультиплексора 1 известна, он может быть технически реализован на базе серийно выпускаемого N-разрядного мультиплексора, как показано в [Угрюмов Е.П. Цифровая схемотехника: учеб. пособие для вузов. - 3-е изд., перераб. и доп. - СПб.: БХВ-Петербург, 2010. - 816 с., С. 94-95].

Второй селектор-мультиплексор 2, входящий в общую структурную схему генератора случайной последовательности, предназначен для коммутации на свой N-разрядный выход сигналов одной из двух групп: с первого N-разрядного входа 21 (входа для разрядов A1-AN) либо со второго N-разрядного информационного входа 22 (входа для разрядов B1-BN). Он отвечает за запись новых значений (для данного шага) верхних границ интервалов, на которые разбивается множество адресов заданного набора данных, определяемых на каждом последующем шаге заданными верифицированными (с помощью нейросетевого алгоритма) вероятностями переходов случайного процесса из состояния в состояние [1]. Схема построения второго селектора-мультиплексора 2 известна и аналогична схеме первого селектора-мультиплексора 1. Он может быть технически реализован на базе серийно выпускаемого N-разрядного мультиплексора, как показано в [Угрюмов Е.П. Цифровая схемотехника: учеб. пособие для вузов. - 3-е изд., перераб. и доп. - СПб.: БХВ-Петербург, 2010. - 816 с., С. 94-95].

Первый регистр 3, входящий в общую структурную схему генератора случайной последовательности, предназначен для регистрации и хранения двоичных кодов, определяющих генерацию последовательности верифицированных (с помощью нейросетевого алгоритма) значений из заданного множества значений с учетом наличия связи каждого очередного значения с предыдущим. Он отвечает за регистрацию и хранение значений новых (для каждого последующего шага) верхних границ интервалов, величина которых динамично изменяется по методам марковских цепей, зависит от вероятности перехода случайного процесса из состояния в состояние и соответствует значениям требуемых на данном шаге вероятностей наблюдения соответствующих элементов заданного набора данных. Описание работы и схема таких регистров известны и приведены, например, в книге [Аверченков О.Е. Схемотехника: аппаратура и программы. - М.: ДМК Пресс, 2012. - 588 с., С. 443-445].

Источник случайных чисел 4, входящий в общую структурную схему генератора случайной последовательности, предназначен для генерирования P-разрядных случайных чисел, известен, и может быть технически реализован, как показано, например, в [Угрюмов Е.П. Цифровая схемотехника: учеб. пособие для вузов. - 3-е изд., перераб. и доп. - СПб.: БХВ-Петербург, 2010. - 816 с., С. 260-261].

Оперативное запоминающее устройство 5, входящее в общую структурную схему генератора случайной последовательности, предназначено для хранения значений элементов заданного набора данных. Схема построения оперативного запоминающего устройства известна, он может быть технически реализован на базе серийно выпускаемого оперативного запоминающего устройства, как показано в [Аверченков О.Е. Схемотехника: аппаратура и программы. - М.: ДМК Пресс, 2012. - 588 с., С. 246-247].

Блоки хранения границ интервалов 61-6K, входящие в общую структурную схему генератора случайной последовательности, предназначены для хранения двоичных кодов, определяющих граничные значения вероятности появления соответствующих элементов заданного набора данных (набора данных в заданном интервале). Они выполненных в виде оперативных запоминающих устройств, структура их построения известна, они могут быть технически реализованы на базе серийно выпускаемых оперативных запоминающих устройств, как показано в [Аверченков О.Е. Схемотехника: аппаратура и программы. - М.: ДМК Пресс, 2012. - 588 с., С. 246-247].

Блоки сравнения 71-7K, входящие в общую структурную схему генератора случайной последовательности, предназначены для сравнения случайного значения, генерируемого источником случайных чисел, и значения на выходе соответствующего регистра, а также для формирования результата сравнения. Блок сравнения 7k может быть технически реализован, как показано на фиг. 4, содержит компаратор 7.1k, Р-входовый элемент ИЛИ-НЕ 7.2k и элемент ИЛИ 7.3k первый вход 7.3k-1 которого подключен к выходу «Неравенство» 7.1k-3 (выходу А>В) компаратора 7.1k. Второй вход 7.3k-2 элемента ИЛИ 7.3k подключен к инверсному выходу 7.2k-2 Р-входового элемента ИЛИ-НЕ 7.2k, выход 7.3k-3 элемента ИЛИ 7.3k является выходом «Результат сравнения» 73k блока сравнения 7k. Р входов (входов A1-АР) первой группы 7.1k-1 информационных входов компаратора 7.1k являются Р-разрядным входом «Случайное число» 71k блока сравнения 7k, Р входов (входов B1-BP) второй группы 7.1k-2 информационных входов компаратора 7.1k соединены с соответствующими входами 7.2k-11-7.2k-1P Р-входового элемента ИЛИ-НЕ 7.2k и являются вторым Р-разрядным информационным входом «Верхняя граница» 72k блока сравнения 7k.

Компаратор 7.1k блока сравнения 7k предназначен для сравнения двух Р-разрядных чисел и формирования результата сравнения. Описание работы и схема компаратора известны, приведены, например, в книге [Аверченков О.Е. Схемотехника: аппаратура и программы. - М.: ДМК Пресс, 2012. - 588 с., С. 428-429].

Элемент ИЛИ-НЕ 7.2k блока сравнения 7k предназначен для формирования на своем выходе значения логического нуля, если на всех разрядах второго Р-разрядного входа «Верхняя граница» 72k блока сравнения 7k установлены значения логической единицы. Элемент ИЛИ-НЕ 7.2k может быть реализован технически на базе серийно выпускаемого элемента ИЛИ-НЕ, как показано в [Угрюмов Е.П. Цифровая схемотехника: учеб. пособие для вузов. - 3-е изд., перераб. и доп. - СПб.: БХВ-Петербург, 2010. - 816 с., С. 308-309].

Элемент ИЛИ 7.3k блока сравнения 7k предназначен для формирования на своем выходе значения логической единицы, если на одном из его входов имеется значение логической единицы, схема реализации такого элемента ИЛИ известна и описана, например, в [Аверченков О.Е. Схемотехника: аппаратура и программы. - М.: ДМК Пресс, 2012. - 588 с., С. 39-40].

Шифратор приоритетов 8, входящий в общую схему генератора случайной последовательности, предназначен для преобразования значения логического нуля на одном из его входов в соответствующий двоичный код на его выходе, причем преобразование осуществляется с учетом приоритетов, определяемых номером входа. Схема реализации шифратора приоритетов известна и подробно описана, например, в [Аверченков О.Е. Схемотехника: аппаратура и программы. - М.: ДМК Пресс, 2012. - 588 с., С. 414-418].

Инверторы 91-9N, входящие в общую схему генератора случайной последовательности, предназначены для инвертирования сигналов с инверсных выходов шифратора приоритетов. Схема реализации инвертора известна и подробно описана, например, в [Аверченков О.Е. Схемотехника: аппаратура и программы. - М.: ДМК Пресс, 2012. - 588 с., С. 426].

Второй регистр 10, входящий в общую схему генератора случайной последовательности, предназначен для хранения двоичных кодов, определяющих вероятности появления соответствующих элементов заданного набора данных. Он отвечает за регистрацию и хранение значений предыдущих (для прошлого шага) верхних границ интервалов (полученных с учетом наличия не только вероятностной, но и неоднозначной (неполной, противоречивой) связи каждого очередного значения с предыдущим), величина которых динамично изменяется по методам марковских цепей, зависит от вероятности перехода случайного процесса из состояния в состояние и соответствует значениям требуемых на прошедшем шаге вероятностей наблюдения соответствующих элементов заданного набора данных. Он аналогичен первому регистру 3, описание работы и схема таких регистров известны и приведены, например, в книге [Аверченков О.Е. Схемотехника: аппаратура и программы. - М.: ДМК Пресс, 2012. - 588 с., С. 443-445].

В заявленном устройстве генерирование заданных значений набора данных с учетом как вероятностной, так и неоднозначной (неполной, противоречивой) связи каждого очередного значения с предыдущим, осуществляется поэтапно, первым этапом является учет вероятностной связи каждого очередного значения с предыдущим, реализуемое на основе закона распределения, который задается путем указания требуемой вероятности появления соответствующего элемента заданного набора данных. При этом применяется подход [2], основанный на использовании источника случайных чисел, распределенных равномерно в диапазоне [0; 1). Данный диапазон разбивается на совокупность интервалов, количество которых соответствует количеству элементов в заданном наборе данных. Величины интервалов соответствуют значениям требуемых вероятностей наблюдения соответствующих элементов заданного набора данных. Вероятность попадания случайного числа, сформированного источником случайных чисел, внутрь каждого интервала равна его длине. Номер интервала используется в качестве адреса для извлечения элемента заданного набора данных из оперативного запоминающего устройства, а для задания интервалов указываются их верхние границы.

Исходное задание начальных вероятностей появления элементов заданного набора данных, на первом шаге - без учета наличия вероятностной связи каждого очередного значения с предыдущим, осуществляется следующим образом.

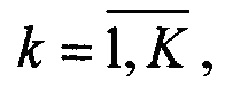

Пусть Н={h1, h2, …, hk, …, hK} - множество требуемых вероятностей появления элементов заданного набора данных, где  K - количество элементов заданного набора данных, а В={b1, b2, …, bk, …, bK} - множество соответствующих значений начальных верхних границ интервалов. Тогда начальное значение верхней границы k-го интервала будет равно сумме значений вероятностей появления элементов из заданного набора данных от 1-го до k-го:

K - количество элементов заданного набора данных, а В={b1, b2, …, bk, …, bK} - множество соответствующих значений начальных верхних границ интервалов. Тогда начальное значение верхней границы k-го интервала будет равно сумме значений вероятностей появления элементов из заданного набора данных от 1-го до k-го:

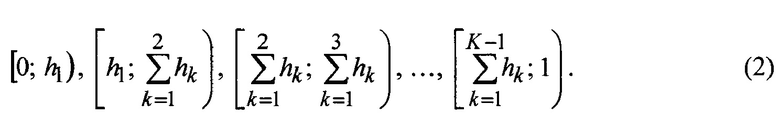

Таким образом, диапазон [0; 1) на первом шаге генерации будет разбит на следующие интервалы:

Используется Р-разрядный источник случайных чисел с равномерным законом распределения. При этом Р-разрядный двоичный код, формируемый на выходе источника случайных чисел, и Р-разрядный двоичный код, используемый для задания начальной (для первого шага) верхней границы интервала, рассматриваются как числа из диапазона [0; 1) без указания целой части.

Например, задано множество требуемых вероятностей появления элементов заданного набора данных Н={0,125; 0,125; 0,25; 0,5}. Тогда значения верхних границ интервалов будут равны соответственно 0,125, 0,25, 0,5 и 1. В соответствии с правилами перевода [3] правильных десятичных дробей в двоичное представление данные значения в четырехразрядном коде представляются соответственно в виде чисел 0,0010, 0,0100, 0,1000, 0,1111. А в устройство заносятся только дробная часть этих чисел: соответственно значения 0010, 0100,1000 и 1111.

Аналогичным образом, если источник случайных чисел сформировал значение 1101 (в десятичном представлении 0,8125), то, представляя это значение как дробную часть числа из диапазона [0; 1), т.е. как 0,1101, и учитывая множество начальных верхних границ интервалов из предыдущего абзаца, видно, что случайное значение попало в интервал, ограниченный числами 0,1000 и 0,1111.

Для того, чтобы генератор случайной последовательности был способен моделировать дискретные случайные процессы, протекающие в реальных системах, с учетом вероятностной (на первом этапе) и с учетом неоднозначной, неполной и противоречивой (на втором этапе) связи между состояниями случайного процесса (между генерируемыми значениями заданного набора данных), в соответствии с теорией марковских процессов [4], задают начальные значения вероятности переходов случайного процесса из состояния в состояние.

При этом, на каждом последующем шаге функционирования генератора, вероятности появления элементов заданного набора данных будут иметь новые, определяемые в соответствии с марковской моделью, значения верхних границ интервалов, и генерируемые случайные значения на каждом новом шаге будет попадать в новый (лишь для этого шага) интервал. Данное пошаговое уточнение, идентификация значений вероятности переходов марковской цепи [4] и соответствующее пошаговое уточнение (пошаговая коррекция) множества верхних границ интервалов позволяет получать значения элемента из заданного набора данных с учетом наличия вероятностной и неоднозначной (неполной и противоречивой) связи каждого очередного значения с предыдущим.

Учет не только вероятностной, но и неоднозначной (неполной и противоречивой) связи каждого очередного значения с предыдущим, реализуемое в предложенном генераторе случайной последовательности, является вторым этапом, который основан на известных результатах исследований в области теории искусственных нейронных сетей, изложенных в работах [1, 5-9]. Анализ работ [1, 5-9] позволяет сформировать математически корректный алгоритм приведения неполно заданных, неоднозначно (противоречиво) идентифицированных исходных данных (значений вероятности переходов марковской цепи и соответствующих значений верхних границ интервалов) к ближайшему полному (однозначному заданному) множеству. Таким образом, в рамках моделирования дискретных случайных процессов, формируемых с учетом как количественно (вероятностно), так и качественно (неоднозначно, неполно и противоречиво) идентифицированных связей каждого очередного значения с предыдущим, ряд характеристик генерируемого процесса моделируется на основе параметрически (вероятностно) заданных исходных данных, традиционными методами, а моделирование неоднозначно, неполно и противоречиво заданных параметров связей каждого очередного значения с предыдущим (элементы множества значений вероятностей переходов случайного процесса из состояния в состояние, которые определяют значение верхней границы интервала), путем последовательных преобразований с использованием методов теории искусственных нейронных сетей, сводится к возможности их относительно параметрического моделирования, т.е. осуществляется переход от неоднозначно, неполно и противоречиво поставленной задачи к параметрической.

Известно [1, 5-9], что с точки зрения верификации значений вероятности переходов марковской цепи, существует возможность распознавания (определения) этих значений, заданных как количественно, так и качественно (неоднозначно, неполно и противоречиво). Эта возможность реализуется с использованием нейросетевых вычислительных методов и алгоритмов, позволяющих путем последовательных нейросетевых преобразований, осуществить переход от неоднозначно, неполно и противоречиво распознанных (определенных) значений вероятности переходов к виду, пригодному для однозначного принятия достоверного решения о значениях этих вероятностей.

При этом значения вероятности переходов марковской цепи могут быть верифицированы на основе математических методов принятия решений в слабоструктурированных задачах - нейросетевых вычислительных методов и алгоритмов, которые достаточно просто могут быть аппаратно реализуемы. Нейросетевые вычислительные методы и алгоритмы работают на основе экспертных оценок, а для решения задачи объединения мнений экспертов, знания которых используются, например, для верификации значений вероятности переходов, используется один из типовых вычислительных алгоритмов теории искусственных нейронных сетей - нейросетевой экстраполирующий вычислительный алгоритм, или, так называемая, экстраполирующая нейронная сеть (ЭНС), являющаяся разновидностью известных вычислительных моделей ассоциативной памяти [5-9].

Вычислительный нейросетевой алгоритм (экстраполирующая нейронная сеть) такого класса состоит из двух слоев вычислителей (нейронов) - входного слоя Ua и выходного слоя Ub. Входной слой Ua состоит из Nвх нейронов, обладающих набором прямых и обратных связей с Nвых нейронами выходного слоя Ub, причем количество входных и выходных образов N соответствует коду адресации элементов набора данных, равно N=[log2K] и зависит от количества двоичных разрядов, достаточных для адресации элементов заданного множества генерируемых значений случайной последовательности, от количества экспертов и соответствующего количества входов устройств аппаратной реализации нейросетевого алгоритма.

В нашем случае N может принимать значения от 2 (двух) до 10 (десяти), соответствующие количеству входов микропроцессорной секции MPS К1804ВС1, на базе которой построен программируемый вычислитель 12.1 блока коррекции значений вероятностей переходов 12.

В ЭНС используется так называемая когнитивная карта, полностью задаваемая матрицей связей и характеризующая причинно-следственные отношения текущих значений вероятностей переходов, влияющих на получения однозначных (достоверных) результатов генерации значений случайной последовательности. Когнитивная карта формулируется экспертами, принцип формирования когнитивных карт подробно описан в работах [5, 7]. При этом N ветвей алгоритма отвечают за преобразование мнений экспертов о неоднозначно (неполно и противоречиво) распознанном (определенном) значении вероятностей переходов к виду, позволяющему достоверно (однозначно, полно, непротиворечиво) идентифицировать и трактовать значения вероятностей переходов случайного процесса из состояния в состояние.

На вход вычислительного нейросетевого алгоритма (ЭНС) поступает входной образ - данные, характеризующие значения вероятностей переходов и распознанные (определенные) как количественно, так и качественно (неоднозначно, неполно и противоречиво). Определяется, какие из данных, характеризующих значения вероятностей переходов, в данный момент времени распознаны количественно, а какие данные идентифицированы неоднозначно (неполно и противоречиво). В целях верификации значений вероятностей переходов, необходимо математически корректно, используя ЭНС, преобразовать распознанные неоднозначно (неполно) данные.

Этапы функционирования вычислительного нейросетевого алгоритма (ЭНС) подробно, алгоритмически и аналитически описаны в [5]. На выходе вычислительного нейросетевого алгоритма (ЭНС) имеем выходной образ - данные, которые достоверно (однозначно, полно, непротиворечиво) характеризуют интегрированное мнение экспертов о принадлежности значений вероятностей переходов к пространству достоверных, верифицированных значений.

Рассмотренный в [1, 6, 8] и детально описанный в [5] вычислительный нейросетевой алгоритм позволяет устранить неопределенность (неоднозначность, неполноту и противоречивость) данных, характеризующих значения вероятностей переходов, позволяет однозначно распознать (верифицировать) истинные значения вероятностей переходов генерируемого случайного процесса из состояния в состояние, а в конечном итоге, повысить достоверность формирования значения элементов случайного процесса, характеризующего реальное поведение сложной вычислительной системы - когда взаимосвязи параметров случайного процесса, взаимосвязи каждого очередного из последовательности генерируемых значений с предыдущим значением имеют как количественно (вероятностно), так и качественно (неоднозначно, неполно и противоречиво) выраженный физический смысл.

Иными словами, анализ рассмотренного в [1, 6, 8] и детально описанного в [5] вычислительного нейросетевого алгоритма позволяет сделать вывод о технической возможности реализации полной и непротиворечивой идентификации существенных параметров генерируемого потока случайных событий (с количественно, параметрически (вероятностно) и неоднозначно, неполно и противоречиво заданными параметрами) - значений вероятностей переходов и соответствующих значений верхних границ интервалов. Это позволяет снизить неопределенность, а, следовательно, повысить достоверность генерируемой последовательности заданных значений набора данных.

С учетом этого в заявленном устройстве осуществляется генерирование заданных значений набора данных с учетом наличия не только вероятностной, но и неоднозначной (неполной и противоречивой) связи каждого очередного значения с предыдущим.

Техническая реализация принципа повышения достоверности распознавания значений вероятностей переходов и соответствующих значений верхних границ интервалов в заявленном устройстве осуществлена путем введения предварительного анализа (выявления) неоднозначно (неполно и противоречиво) идентифицируемых элементов множества значений вероятностей переходов, а также верификации этих значений с использованием нейроматематических методов к виду, позволяющему однозначно (полно, непротиворечиво) идентифицировать и трактовать эти значения (в заявленном устройстве реализованы соответственно в рамках блока проверки значений вероятностей переходов 11 и блока коррекции значений вероятностей переходов 12).

Генератор случайной последовательности работает следующим образом.

В исходном положении на управляющем входе 07, перовом 06 и втором 012 входах «Установка» установлены значения логического нуля, а на первом 02 и втором 010 входах «Чтение/запись» и на первом 04 и втором 08 входах «Выбор кристалла» - значения логической единицы. Генератор работает в следующих режимах: режим подготовки к генерации; режим генерации.

Режим работы генератора с учетом не только вероятностной, но и неоднозначной (неполной и противоречивой) связи между состояниями случайного процесса, определяется комбинацией сигналов на управляющем входе 07, первом 06 и втором 012 входах «Установка», первом 02 и втором 010 входах «Чтение/запись», а также на первом 04 и втором 08 входах «Выбор кристалла». Для перевода устройства в режим подготовки необходимо на управляющий вход 07 генератора, первый 04 и второй 08 входы «Выбор кристалла», первый 02 и второй 010 входы «Чтение/запись» подать значения логического нуля, а на первый 06 и второй 012 входы «Установка» - значение логической единицы.

В режиме генерации на управляющем входе генератора 07, первом 02 и втором 010 входах «Чтение/запись» устанавливаются значения логической единицы, а на первом 04 и втором 08 входах «Выбор кристалла» и первом 06 и втором 012 входах «Установка» -значения логического нуля.

В режиме подготовки генератора к работе выполняются следующие шаги.

Первый шаг - занесение множества А={а1, а2, …, aK} значений элементов заданного набора данных в оперативное запоминающее устройство, при этом:

0≤ak≤2M-1 - элемент заданного набора данных, где

М≥2 - количество двоичных разрядов, достаточное для представления значений элементов заданного набора данных;

K≥2 - количество элементов в заданном наборе данных;

N≥1 - количество двоичных разрядов, достаточное для адресации элементов набора данных.

Второй шаг - установка множества В={b1, b2, …, bK} значений начальных верхних границ интервалов, на которые разбивается все множество адресов заданного набора данных А.

Третий шаг - установка множества количественно или С={с1, с2, …, cK} или неоднозначно (неполно и противоречиво) заданных значений новых (для данного шага) верхних границ интервалов, на которые разбивается множество адресов заданного набора данных А, определяемых на каждом последующем шаге вероятностями переходов случайного процесса из состояния в состояние [4].

Первый шаг подготовки генератора к работе включает следующие действия. По первому N-разрядному адресному входу 01 генератора на первую группу информационных входов 0011 (группу входов A1-AN) первого селектора мультиплексора 1 подается N-разрядный адрес, по которому должно быть записано значение первого элемента а1. На управляющем входе 07 генератора устанавливают значение логического нуля, который поступает на вход 0013 (вход SE) первого селектора-мультиплексора 1, что приводит к коммутации адреса, установленного на входе 0011 (входах A1-AN) первого селектора-мультиплексора 1, на N-разрядный адресный вход 52 (вход для разрядов A1-AN) оперативного запоминающего устройства 5. По М-разрядному информационному входу 03 генератора на информационные входы 53 (входы D1-DM) оперативного запоминающего устройства 5 подается значение первого элемента а1 заданного набора данных, которое записывается в оперативное запоминающее устройство 5 при поступлении на его входы 51  и 54

и 54  значений логического нуля по первым входам «Выбор кристалла» 04 и «Чтение/запись» 02 соответственно. Затем, по первому N-разрядному адресному входу 01 генератора на первую группу информационных входов 0011 (группу входов A1-AN) первого селектора мультиплексора 1 подается N-разрядный адрес, по которому должно быть записано значение второго элемента а2, а по М-разрядному информационному входу 03 генератора на информационные входы 53 (входы D1-DM) оперативного запоминающего устройства 5 подают значение элемента а2 и, путем установки значений логического нуля на первых входах «Выбор кристалла» 04 и «Чтение/запись» 02, записывают значение а1 в оперативное запоминающее устройство 5. Аналогичным образом в оперативное запоминающее устройство 5 заносятся все K значений элементов заданного набора данных. После чего на первом входе «Чтение/запись» 02 генератора устанавливают значение логической единицы.

значений логического нуля по первым входам «Выбор кристалла» 04 и «Чтение/запись» 02 соответственно. Затем, по первому N-разрядному адресному входу 01 генератора на первую группу информационных входов 0011 (группу входов A1-AN) первого селектора мультиплексора 1 подается N-разрядный адрес, по которому должно быть записано значение второго элемента а2, а по М-разрядному информационному входу 03 генератора на информационные входы 53 (входы D1-DM) оперативного запоминающего устройства 5 подают значение элемента а2 и, путем установки значений логического нуля на первых входах «Выбор кристалла» 04 и «Чтение/запись» 02, записывают значение а1 в оперативное запоминающее устройство 5. Аналогичным образом в оперативное запоминающее устройство 5 заносятся все K значений элементов заданного набора данных. После чего на первом входе «Чтение/запись» 02 генератора устанавливают значение логической единицы.

Второй шаг подготовки генератора к работе выполняется следующим образом. На K Р-разрядных информационных входах «Верхняя граница» 091-09K генератора устанавливают начальные значения верхних границ интервалов. При этом, на вход 091 устанавливают значение b1, которое поступает на группу информационных входов 631 (группу D1-DP) блока хранения границ интервалов 61, на вход 092 - значение b2, которое поступает на группу информационных входов 632 блока хранения границ интервалов 62, на вход 09K - значение bK, которое поступает на группу информационных входов 63K блока хранения границ интервалов 6K. Для записи начальных значений верхних границ интервалов в блоки хранения границ интервалов 61-6K на вторых входах «Выбор кристалла» 08 и «Чтение/запись» 010 устройства устанавливают значение логической единицы, которая поступает на входы 61k  и 64k

и 64k  каждого k-ого блока хранения границ интервалов 6k. По окончании записи начальных значений верхних границ интервалов в соответствующие блоки хранения границ интервалов на вторых входах «Выбор кристалла» 08 и «Чтение/запись» 010 устройства устанавливают значение логического нуля.

каждого k-ого блока хранения границ интервалов 6k. По окончании записи начальных значений верхних границ интервалов в соответствующие блоки хранения границ интервалов на вторых входах «Выбор кристалла» 08 и «Чтение/запись» 010 устройства устанавливают значение логического нуля.

Третий шаг подготовки генератора к работе выполняется следующим образом. По второму N-разрядному адресному входу 05 генератора на первый N-разрядный вход 21 (входов разрядов A1-AN) второго селектора мультиплексора 2 подается N-разрядный адрес, по которому должно быть записано значение первого элемента, определяющее новое значение верхней границы данного (первого) интервала исходя из параметрически (количественно) либо неоднозначно (неполно и противоречиво) заданных вероятностей переходов генерируемого случайного процесса из состояния в состояние. Аналогичным образом во второй селектор-мультиплексор 2 заносятся все K новых N-разрядных значений количественно либо неоднозначно (неполно и противоречиво) заданных верхних границ интервалов. На управляющем входе 07 генератора устанавливают значение логического нуля, который поступает на вход 23 (вход SE) второго селектора-мультиплексора 2, что приводит к коммутации адреса, записанного в двоичном коде и установленного на входе 21 второго селектора-мультиплексора 2 на N-разрядный информационный вход 31 (вход регистров D1-DN) первого регистра 3. В режиме подготовки генератора к работе на входы сброса 32 и 102 (входы R) первого 3 и второго 10 регистров соответственно поданы значения логической единицы. На второй N-разрядный информационный вход 22 (вход для разрядов B1-BN) второго селектора-мультиплексора 2 с N-разрядных прямых выходов 112 и 122 блоков проверки значений вероятностей переходов 11 и коррекции значений вероятностей переходов 12 соответственно подается предыдущее (с прошлого шага), количественное или верифицированное, преобразованное (с помощью нейросетевого алгоритма) значение первого элемента с1 из множества значений вероятностей переходов случайного процесса из состояния в состояние, которое определяет новое значение верхней границы данного интервала. Это значение первого элемента с1 записывается в первый регистр 3, причем для записи новых (для данного шага) значений верхних границ интервалов в первый регистр 3 на первом входе «Установка» 06 устройства устанавливают значение логической единицы, которая поступает на вход инициализации 33 (вход С) первого регистра 3. По окончании записи в первый регистр 3 новых (для данного шага) значений верхних границ интервалов в первый регистр 3 на первом входе «Установка» 06 устройства устанавливают значение логического нуля.

После вышеописанных действий генератор готов к работе.

В режиме генерации работа устройства с учетом не только вероятностной, но и неоднозначной (неполной и противоречивой) связи между состояниями случайного процесса происходит следующим образом (см. фиг. 1). На управляющий вход 07 генератора подают значение логической единицы, которое поступает на вход выбора 0013 (вход SE) первого селектора-мультиплексора 1, что обеспечивает коммутацию верифицированного адреса, поступающего с выхода 104 второго регистра 10, через блок проверки значений вероятностей переходов 11 и блок коррекции значений вероятностей переходов 12 на N-разрядный адресный вход 52 (вход для разрядов A1-AN) оперативного запоминающего устройства 5.

Источник случайных чисел 4 при наличии на управляющем входе 07 генератора значения логической единицы формирует Р-разрядное случайное значение адреса, которое поступает одновременно на Р-разрядные входы «Случайное число» 711-71K K блоков сравнения 71-7K, где происходит сравнение случайного значения адреса с начальными значениями верхних границ заданных интервалов В={b1, b2, …, bK} (см. фиг. 4). В случае если поступившее значение адреса принадлежит k-му интервалу, т.е. оно меньше либо равно значения верхней границы k-го интервала, то на выходе «Неравенство» (выходе А>В) компараторов 7.11-7.1k-1 формируются значения логической единицы, а на выходах «Неравенство» остальных компараторов значения логического нуля.

Сигналы с выходов «Неравенство» каждого компаратора 7.11-7.1K через элементы ИЛИ 7.31-7.3K и выходы «Результат сравнения» 731-73K K блоков сравнения 71-7K поступают на соответствующие инверсные входы 811-81K (входы регистров  ) шифратора приоритетов 8.

) шифратора приоритетов 8.

Таким образом (см. фиг. 1), при выполнении условия bk-1<ak<bk, на входах 811-81K (входах регистров  ) шифратора приоритетов 8 будут установлены значения логической единицы, а на входах 81k-1-81K (входах регистров

) шифратора приоритетов 8 будут установлены значения логической единицы, а на входах 81k-1-81K (входах регистров  ) - значения логического нуля. В этом случае на N инверсных выходах 821-82N (выходах

) - значения логического нуля. В этом случае на N инверсных выходах 821-82N (выходах  ) шифратора приоритетов 8 будет сформирован двоичный код в инверсном представлении, соответствующий значению первого номера входа

) шифратора приоритетов 8 будет сформирован двоичный код в инверсном представлении, соответствующий значению первого номера входа  с установленным значением логического нуля, т.е. код соответствующий числу k - номеру интервала, которому принадлежит значение ak. Полученный код после инвертирования в элементах 91-9N поступает на N-разрядный информационный вход 101 второго регистра 10, здесь регистрируется как код предыдущего шага, затем поступает на N-разрядный вход 111 блока проверки значений вероятностей переходов 11.

с установленным значением логического нуля, т.е. код соответствующий числу k - номеру интервала, которому принадлежит значение ak. Полученный код после инвертирования в элементах 91-9N поступает на N-разрядный информационный вход 101 второго регистра 10, здесь регистрируется как код предыдущего шага, затем поступает на N-разрядный вход 111 блока проверки значений вероятностей переходов 11.

Значения кода предыдущего шага с разрядов N-разрядного выхода 104 второго регистра 10 поступают на соответствующие разряды N-разрядного входа 111 блока проверки значений вероятностей переходов 11. При этом код, содержащий во всех разрядах значения логического нуля, поступает на N-разрядный вход селектора значений вероятностей переходов 11.1 и на N-разрядный вход (D1-DK) преобразователя значений вероятностей переходов 11.2 (см. фиг. 2), что обеспечивает транзитное преобразование (перезапись) значений кода в селекторе значений вероятностей переходов 11.1 ив преобразователе значений вероятностей переходов 11.2 и установку значений логического нуля на всех разрядах N-разрядного выхода селектора значений вероятностей переходов 11.1 и на соответствующих разрядах N-разрядного прямого выхода 112 блока проверки значений вероятностей переходов 11, а также на всех разрядах N-разрядного выхода Y (Y1-YN) преобразователя значений вероятностей переходов 11.2 и на соответствующих разрядах N-разрядного корректировочного выхода 113 блока проверки значений вероятностей переходов 11.

Поступление значений логического нуля с разрядов N-разрядного корректировочного выхода 113 блока проверки значений вероятностей переходов 11 на N-разрядный корректировочный вход 121 блока коррекции значений вероятностей переходов 12 и на соответствующие разряды N-разрядного входа I (I1-IN) программируемого вычислителя 12.1 происходят по соответствующей разрешительной (отпирающей) команде, поступающей с выхода передачи TxD преобразователя значений вероятностей переходов 11.2 через контрольный выход 114 блока проверки значений вероятностей переходов 11 на контрольный вход 123 блока коррекции значений вероятностей переходов 12 и на вход разрешения выходов A (OEI) программируемого вычислителя 12.1 (см. фиг. 3), что обеспечивает установление значений логического нуля на всех N (A1-AN) выходах 12.1-11 - 12.1-1N программируемого вычислителя 12.1 и, как следствие, после записи в ячейки памяти, установление значений логического нуля на всех разрядах N-разрядного выхода запоминающего элемента 12.2 и на соответствующих разрядах N-разрядного прямого выхода 122 блока коррекции значений вероятностей переходов 12.

Значения логического нуля с разрядов N-разрядных прямых выходов 112 и 122 блока проверки значений вероятностей переходов 11 и блока коррекции значений вероятностей переходов 12 соответственно, поступают на соответствующие разряды второго N-разрядного информационного входа 0012 (входа для разрядов B1-BN) первого селектора-мультиплексора 1 и второго N-разрядного информационного входа 22 (входа для разрядов B1-BN) второго селектора-мультиплексора 2. Затем со второго N-разрядного информационного входа 0012 (входа для разрядов B1-BN) первого селектора-мультиплексора 1 полученный и инвертированный код поступает на N-разрядный адресный вход 52 (вход для разрядов A1-AN) оперативного запоминающего устройства 5. При этом по первому входу «Выбор кристалла» 04 генератора на вход 51 (вход  ) оперативного запоминающего устройства 5 подают значение логического нуля, а по первому входу «Чтение/запись» 02 генератора на вход 54 (вход

) оперативного запоминающего устройства 5 подают значение логического нуля, а по первому входу «Чтение/запись» 02 генератора на вход 54 (вход  ) оперативного запоминающего устройства 5 подают значение логической единицы, что соответствует операции чтения данных. Таким образом, в соответствии со случайными адресами, формируемыми источником случайных чисел, происходит чтение начальных (для первого шага работы генератора) значений элементов А={а1, а2, …, aK} заданного набора данных из оперативного запоминающего устройства 5, которые через выход 55 поступают на М-разрядный выход «Результат» 013 генератора.

) оперативного запоминающего устройства 5 подают значение логической единицы, что соответствует операции чтения данных. Таким образом, в соответствии со случайными адресами, формируемыми источником случайных чисел, происходит чтение начальных (для первого шага работы генератора) значений элементов А={а1, а2, …, aK} заданного набора данных из оперативного запоминающего устройства 5, которые через выход 55 поступают на М-разрядный выход «Результат» 013 генератора.

На втором и последующих шагах генерирования значений дискретного случайного процесса работа устройства осуществляется с учетом не только вероятностной, но и неоднозначной (неполной и противоречивой) связи между состояниями случайного процесса (между генерируемыми значениями заданного набора данных) следующим образом.

После регистрации значения предыдущих (для прошлого шага), количественно и неоднозначно (неполно и противоречиво) заданных верхних границ интервалов (величина которых динамично изменяется по методам марковских цепей, зависит от вероятности перехода случайного процесса из состояния в состояние и соответствует значениям требуемых на прошедшем шаге вероятностей наблюдения соответствующих элементов заданного набора данных) с выхода 104 второго регистра 10 поступают на N-разрядный вход 111 блока проверки значений вероятностей переходов 11 (см. фиг. 2).

Предварительный анализ данных в интересах определения (верификации) истинных значений кода, характеризующего вероятности перехода случайного процесса из состояния в состояние и определяющего новые (для каждого последующего шага) верхние границы интервалов, а также выявление (селекция) неоднозначно (неполно и противоречиво) идентифицируемых значений этого кода осуществляется в блоке проверки значений вероятностей переходов 11 следующим образом. С N-разрядного входа 111 блока проверки значений вероятностей переходов 11, требующие дополнительной верификации значения кода, характеризующего вероятности перехода случайного процесса из состояния в состояние и новые верхние границы интервалов, поступают на соответствующие разряды N-разрядного входа селектора значений вероятностей переходов 11.1 и на соответствующие разряды N-разрядного входа (D1-DN) преобразователя значений вероятностей переходов 11.2 (см. фиг. 2).

Процедура выявления (селекции) данных об истинных значениях этого кода и принятие решения о математической природе этих данных осуществляется в селекторе значений вероятностей переходов 11.1 следующим образом. Код, характеризующий вероятности перехода случайного процесса из состояния в состояние и определяющий новые (для каждого последующего шага) верхние границы интервалов, поступает на N-разрядный вход селектора значений вероятностей переходов 11.1, который рассчитан на хранение в каждой ячейке (разряде) одного двоичного числа (бита) поступающей информации - этого вполне достаточно для хранения однозначно (полно и непротиворечиво) заданных значений этого кода. Если количество двоичных чисел, характеризующих любой из N разрядов этого кода, превышает единицу, значит, с точки зрения математики - эта кодовая последовательность содержит избыточность, обусловливающую неоднозначность (неполноту и противоречивость) данных, характеризующих вероятности перехода случайного процесса из состояния в состояние и определяющих новые (для каждого последующего шага) верхние границы интервалов.

В этом случае (см. фиг. 2) с запрещающего выхода МТ селектора значений вероятностей переходов 11.1 на запрещающий вход DST преобразователя значений вероятностей переходов 11.2 поступает в двоичном коде команда, инициирующая начало регистрации данных, характеризующих вероятности перехода случайного процесса из состояния в состояние и определяющих новые (для каждого последующего шага) верхние границы интервалов и начало преобразования этих данных из параллельного кода в последовательный. Преобразователь значений вероятностей переходов 11.2 регистрирует полученные через свой N-разрядный вход (D1-DN) данные, признанные селектором значений вероятностей переходов 11.1 неоднозначными (неполными и противоречивыми) и преобразовывает их из параллельного кода в последовательный. При этом с разрешающего выхода DSR преобразователя значений вероятностей переходов 11.2 на инверсный разрешающий вход  селектора значений вероятностей переходов 11.1 поступает в двоичном коде команда, инициирующая запрет трансляции информации с N-разрядного выхода селектора значений вероятностей переходов 11.1 на соответствующие разряды N-разрядного прямого выхода 112 блока проверки значений вероятностей переходов 11. Последовательный код, характеризующий вероятности перехода случайного процесса из состояния в состояние и определяющий новые (для каждого последующего шага) верхние границы интервалов, который неоднозначно (неполно и противоречиво) идентифицирован, с N-разрядного выхода Y (Y1-YN) преобразователя значений вероятностей переходов 11.2 через N-разрядный корректировочный выход 113 блока проверки значений вероятностей переходов И поступает на N-разрядный корректировочный вход 121 блока коррекции значений вероятностей переходов 12. С выхода передачи TxD преобразователя значений вероятностей переходов 11.2 через контрольный выход 114 блока проверки значений вероятностей переходов 11 на контрольный вход 123 блока коррекции значений вероятностей переходов 12 поступает команда, инициирующая начало процедуры верификации кода, характеризующего значения вероятностей перехода случайного процесса из состояния в состояние и определяющего новые (для каждого последующего шага) верхние границы интервалов.

селектора значений вероятностей переходов 11.1 поступает в двоичном коде команда, инициирующая запрет трансляции информации с N-разрядного выхода селектора значений вероятностей переходов 11.1 на соответствующие разряды N-разрядного прямого выхода 112 блока проверки значений вероятностей переходов 11. Последовательный код, характеризующий вероятности перехода случайного процесса из состояния в состояние и определяющий новые (для каждого последующего шага) верхние границы интервалов, который неоднозначно (неполно и противоречиво) идентифицирован, с N-разрядного выхода Y (Y1-YN) преобразователя значений вероятностей переходов 11.2 через N-разрядный корректировочный выход 113 блока проверки значений вероятностей переходов И поступает на N-разрядный корректировочный вход 121 блока коррекции значений вероятностей переходов 12. С выхода передачи TxD преобразователя значений вероятностей переходов 11.2 через контрольный выход 114 блока проверки значений вероятностей переходов 11 на контрольный вход 123 блока коррекции значений вероятностей переходов 12 поступает команда, инициирующая начало процедуры верификации кода, характеризующего значения вероятностей перехода случайного процесса из состояния в состояние и определяющего новые (для каждого последующего шага) верхние границы интервалов.

Если с N-разрядного входа 111 блока проверки значений вероятностей переходов 11 на N-разрядный вход селектора значений вероятностей переходов 11.1 и на N-разрядный вход (D1-DN) преобразователя значений вероятностей переходов 11.2 поступает одно двоичное число, характеризующее любой из N разрядов значений вероятностей переходов, значит данный код не нуждается в верификации, достоверно, однозначно (полно и непротиворечиво) характеризует вероятности перехода случайного процесса из состояния в состояние и достоверно определяет новые (для каждого последующего шага) верхние границы интервалов. В этом случае, не получая на свой запрещающий вход DST соответствующую команду, преобразователь значений вероятностей переходов 11.2 запирает свой N-разрядный выход Y (Y1-YN) и выход передачи TxD, а селектор значений вероятностей переходов 11.1 транслирует параллельный код, однозначно (полно и непротиворечиво) характеризующий вероятности перехода случайного процесса из состояния в состояние, со своего N-разрядного выхода через соответствующие разряды N-разрядного прямого выхода 112 блока проверки значений вероятностей переходов 11 на соответствующие разряды второго N-разрядного информационного входа 0012 (входа для разрядов B1-BN) первого селектора-мультиплексора 1 и второго N-разрядного информационного входа 22 (входа для разрядов B1-BN) второго селектора-мультиплексора 2.

Данные, характеризующие вероятности перехода случайного процесса из состояния в состояние и новые (для каждого последующего шага) верхние границы интервалов, определенные (распознанные) в блоке проверки значений вероятностей переходов 11 как неоднозначные (неполные и противоречивые) и нуждающиеся в нейросетевой верификации, поступают с N-разрядного корректировочного выхода 113 блока проверки значений вероятностей переходов 11 на N-разрядный корректировочный вход 121 блока коррекции значений вероятностей переходов 12, который осуществляет запись, хранение результатов анализа кода, характеризующего вероятности перехода случайного процесса из состояния в состояние и новые (для каждого последующего шага) верхние границы интервалов, и математически корректную нейросетевую верификацию значений этого кода. Преобразование этих определенных (распознанных) неоднозначно (неполно и противоречиво) данных, к виду, пригодному для однозначного принятия достоверного решения о значениях вероятности перехода случайного процесса из состояния в состояние и новых (для каждого последующего шага) верхних границах интервалов, осуществляется в программируемом вычислителе 12.1 блока коррекции значений вероятностей переходов 12 следующим образом.

Программируемый вычислитель 12.1 блока коррекции значений вероятностей переходов 12 (см. фиг. 3) технически реализуется на базе программируемой (с точки зрения матрицы весов - причинно-следственных когнитивных мнений о значениях вероятностей переходов, формулируемых экспертами) микропроцессорной секции, выполняющей роль программируемого параллельного АЛУ, реализующего вычислительный нейросетевой алгоритм (ЭНС), описанный в работе [5]. Если информации на N-разрядном корректировочном входе 121 блока коррекции значений вероятностей переходов 12 и на N-разрядном входе I (I1-IN) программируемого вычислителя 12.1 нет, соответственно не поступает команда, инициирующая начало процедуры верификации на контрольный вход 123 блока коррекции значений вероятностей переходов 12 и на вход разрешения выходов A (OEI) программируемого вычислителя 12.1. В этом случае N выходов A (A1-AN) программируемого вычислителя 12.1, а значит и N-разрядный выход запоминающего элемента 12.2 заблокированы. В противном случае есть сигнал на входе разрешения выходов A (OEI) программируемого вычислителя 12.1 и неоднозначно (неполно и противоречиво) определенные исходные данные, характеризующие вероятности перехода случайного процесса из состояния в состояние и новые (для каждого последующего шага) верхние границы интервалов, поступают на N-разрядный вход I (I1-IN) программируемого вычислителя 12.1, реализующего функции программируемого параллельного АЛУ.

Программируемый вычислитель 12.1, реализующий функции программируемого параллельного АЛУ, опираясь на запрограммированные значения элементов матрицы весов - аналитически описанные причинно-следственные когнитивные мнения о значениях вероятностей переходов, формулируемые экспертами, осуществляет процедуру вычисления (экстраполяции) в соответствии с вычислительным нейросетевым алгоритмом, подробно описанным в работе [5]. При этом входные разряды (ячейки) I1-IN N-разрядного входа I соответствуют разряду (1, …, N) последовательного кода, поступающего на N-разрядный вход I программируемого вычислителя 12.1 и являются равноправными N входами (Nвх) вычислителей (нейронов) входного слоя Ua ЭНС, на которую подаются значения N разрядов кода, имеющего физический смысл неоднозначно (неполно и противоречиво) определенного значения вероятностей переходов. Набор прямых и обратных связей Nвх с Nвых ЭНС, программно реализованный в рамках программируемого вычислителя 12.1, позволяет учитывать весовые коэффициенты значений вероятностей переходов, сформулированные экспертами, и получать на N выходах A (A1-AN) программируемого вычислителя 12.1 экстраполированные значения N разрядов параллельного кода, имеющего физический смысл верифицированного (математически корректно проверенного) значения вероятностей переходов, определенного на основе верифицированных (достоверных, полных) исходных данных. При этом подача на n-ый, где n=1, 2, …, N, вход (In) N-разрядного входа I программируемого вычислителя 12.1 значения разряда кода, характеризующего неоднозначно (неполно и противоречиво) определенные вероятности перехода случайного процесса из состояния в состояние и новые (для каждого последующего шага) верхние границы интервалов, инициирует выдачу с соответствующего n-го выхода (An) программируемого вычислителя 12.1 (выхода n-го нейрона выходного слоя Ub) запрограммированного, согласно вычислительного нейросетевого алгоритма, описанного в [5], значения математически корректно преобразованного, относительно достоверного разряда кода, характеризующего истинные значения вероятностей перехода случайного процесса из состояния в состояние и определяющего новые (для каждого последующего шага) верхние границы интервалов.

В результате, на N выходах A (A1-AN) программируемого вычислителя 12.1, на соответствующих разрядах N-разрядный выхода запоминающего элемента 12.2 и на соответствующих разрядах N-разрядного прямого выхода 122 блока коррекции значений вероятностей переходов 12 получаем информацию, характеризующую (на основе анализа полученного в рамках ЭНС интегрированного мнения экспертов) истинные значения вероятностей перехода случайного процесса из состояния в состояние, определяющую новые (для каждого последующего шага) верхние границы интервалов и преобразованную (верифицированную) в интересах повышения достоверности реализации генерируемой последовательности.