Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов с широким динамическим диапазоном, в структуре аналоговых микросхем различного функционального назначения (например, быстродействующих операционных усилителях (ОУ)).

Известны схемы дифференциальных усилителей (ДУ) на n-p-n и p-n-p транзисторах с так называемой «архитектурой входного каскада операционного усилителя μA741» [1-30]. На их модификации выдано более 50 патентов для ведущих микроэлектронных фирм мира. Дифференциальные усилители данного класса наряду с типовым параллельно-балансным каскадом [29-30] стали основным усилительным элементом многих аналоговых интерфейсов. Предлагаемое изобретение относится к данному подклассу устройств.

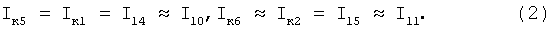

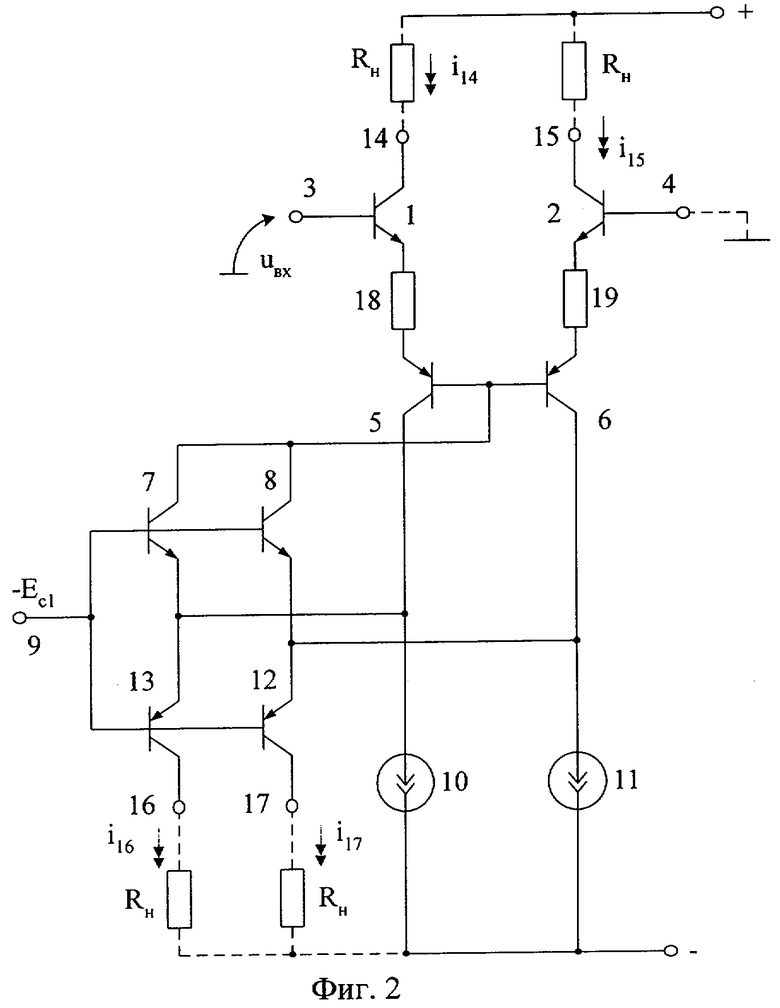

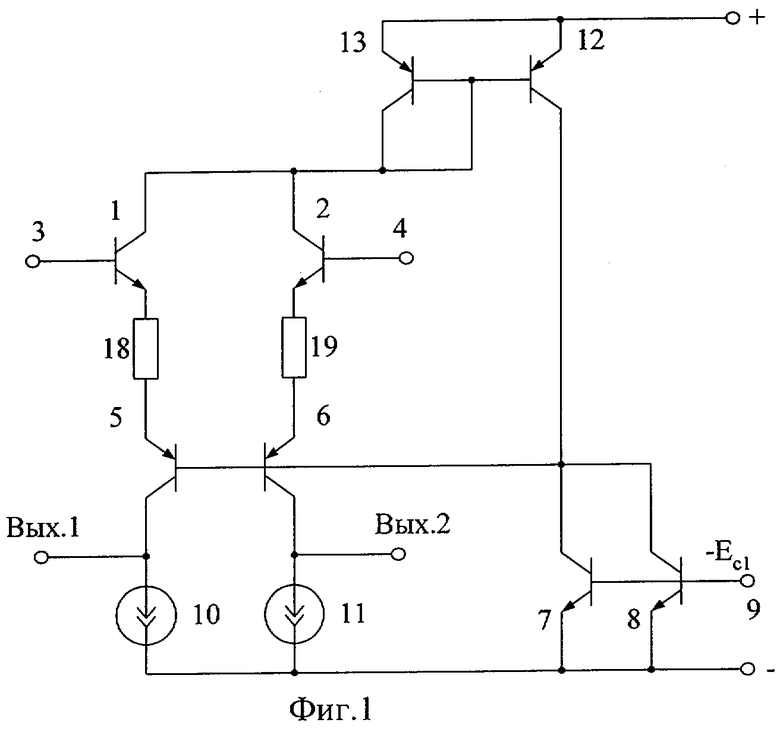

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте США №4.030.044, а также в [1-14], содержащий первый 1 и второй 2 входные транзисторы, базы которых соединены со входами ДУ 3 и 4, а эмиттеры связаны с первым 5 и вторым 6 выходными транзисторами противоположного типа проводимости, причем базы первого 5 и второго 6 выходных транзисторов соединены друг с другом и подключены к коллекторам первого 7 и второго 8 вспомогательных транзисторов, базы которых соединены друг с другом, а также источником опорного напряжения 9, причем коллекторы первого 5 и второго 6 выходных транзисторов соединены с первым 10 и вторым 11 источниками опорного тока, а базы третьего 12 и четвертого 13 вспомогательных транзисторов, тип проводимости которых противоположен типу проводимости первого 7 и второго 8 вспомогательных транзисторов, объединены друг с другом.

Существенный недостаток известного ДУ состоит в том, что он имеет:

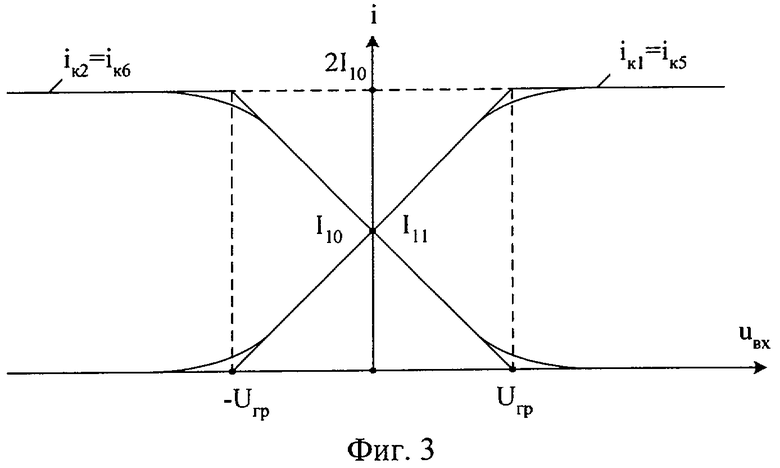

- крайне узкий динамический диапазон линейного усиления сигналов (±Uгр≈100÷150 мВ, фиг.3);

- сравнительно большой ток потребления в статическом режиме. Это связано с наличием в схеме ДУ (фиг.1) «лишней» токопотребляющей ветви, содержащей транзисторы 12, 7, 8. Действительно, суммарный ток потребления ДУ (фиг.1),

где Iк12 - ток коллектора транзистора 12. Причем Iк12=I10+I11.

То есть половина тока Iп, потребляемого ДУ от источников питания, используется для вспомогательных целей - обеспечения работы цепи стабилизации статического режима ДУ, которая не используется для непосредственного усиления сигнала.

Кроме этого, известный ДУ не может иметь диапазон изменения входных синфазных сигналов положительной полярности, близкий к напряжению питания из-за наличия в коллекторной цепи транзисторов 1 и 2 p-n перехода 13.

Основная цель предлагаемого изобретения состоит в расширении диапазона активной работы и снижении суммарного тока, потребляемого дифференциальным усилителем от источника питания.

Поставленная цель достигается тем, что в дифференциальный усилитель фиг.1, содержащий первый 1 и второй 2 входные транзисторы, базы которых соединены со входами ДУ 3 и 4, а эмиттеры связаны с первым 5 и вторым 6 выходными транзисторами противоположного типа проводимости, причем базы первого 5 и второго 6 выходных транзисторов соединены друг с другом и подключены к коллекторам первого 7 и второго 8 вспомогательных транзисторов, базы которых соединены друг с другом, а также источником опорного напряжения 9, причем коллекторы первого 5 и второго 6 выходных транзисторов соединены с первым 10 и вторым 11 источниками опорного тока, а базы третьего 12 и четвертого 13 вспомогательных транзисторов, тип проводимости которых противоположен типу проводимости первого 7 и второго 8 вспомогательных транзисторов, объединены друг с другом, вводятся новые связи - базы третьего 12 и четвертого 13 вспомогательных транзисторов соединены с базами первого 7 и второго 8 вспомогательных транзисторов, эмиттеры первого 7 и четвертого 13 вспомогательных транзисторов связаны с коллектором первого 5 выходного транзистора, эмиттеры второго 8 и третьего 12 вспомогательных транзисторов связаны с коллектором второго 6 выходного транзистора.

Схема усилителя-прототипа представлена на фиг.1. На фиг.2 показано заявляемое устройство в соответствии с п.1 формулы изобретения. На фиг.3 представлена проходная характеристика ДУ фиг.1, а на фиг.4 - теоретическая проходная характеристика заявляемого ДУ фиг.2.

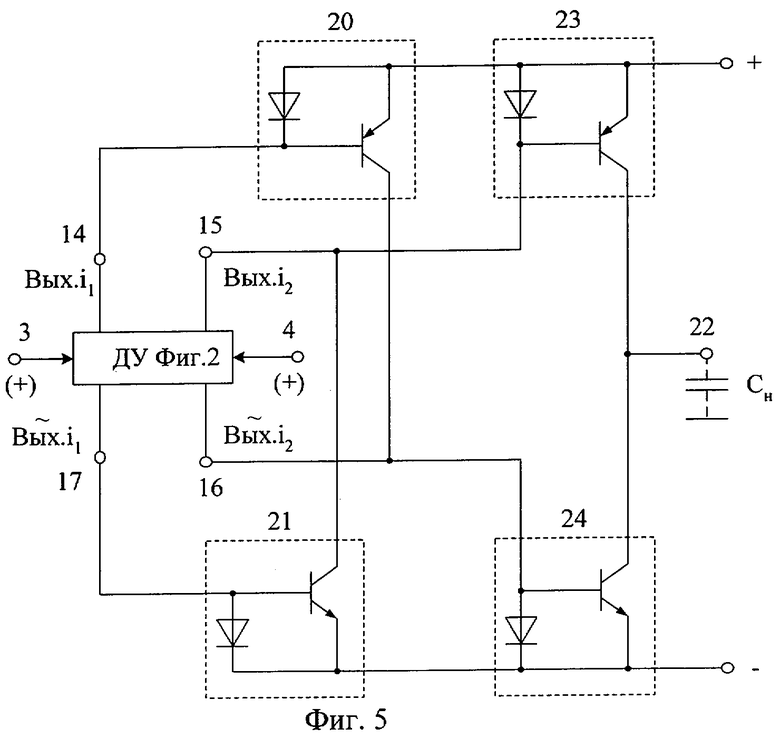

Схема заявляемого устройства в соответствии с п.2 формулы изобретения показана на фиг.5.

На фиг.6 показана схема заявляемого ДУ фиг.2 в среде PSpice на транзисторах ФГУП «Пульсар» (г.Москва) при подаче на входы дифференциального сигнала uвх. На фиг.7, фиг.9 приведены результаты ее компьютерного моделирования в мелком (фиг.7) и крупном (фиг.9) масштабах для выходных токов i14=Iout1, i15=Iout2 при разных значениях сопротивлений резисторов 18 (R2) и 19 (R4) (R2=R4=R).

Графики фиг.8, фиг.10 соответствуют проходным характеристикам для токовых выходов 16 и 17 i16=Iout3, i17=Iout4) в мелком (фиг.8) и крупном (фиг.10) масштабах.

Частотная зависимость крутизны преобразования ДУ фиг.6 для токовых выходов 14 и 15 показана на чертеже фиг.11. Причем

Дифференциальный усилитель (фиг.2) содержит первый 1 и второй 2 входные транзисторы, базы которых соединены со входами ДУ 3 и 4, а эмиттеры связаны с первым 5 и вторым 6 выходными транзисторами противоположного типа проводимости, причем базы первого 5 и второго 6 выходных транзисторов соединены друг с другом и подключены к коллекторам первого 7 и второго 8 вспомогательных транзисторов, базы которых соединены друг с другом, а также источником опорного напряжения 9, причем коллекторы первого 5 и второго 6 выходных транзисторов соединены с первым 10 и вторым 11 источниками опорного тока, а базы третьего 12 и четвертого 13 вспомогательных транзисторов, тип проводимости которых противоположен току проводимости первого 7 и второго 8 вспомогательных транзисторов, объединены друг с другом. Базы третьего 12 и четвертого 13 вспомогательных транзисторов соединены с базами первого 7 и второго 8 вспомогательных транзисторов, эмиттеры первого 7 и четвертого 13 вспомогательных транзисторов связаны с коллектором первого 5 выходного транзистора, эмиттеры второго 8 и третьего 12 вспомогательных транзисторов связаны с коллектором второго 6 выходного транзистора. Выходами усилителя 14, 15, 16, 17 являются коллекторы транзисторов 1, 2, 13, 12. Эмиттеры транзисторов 1 и 2 связаны с эмиттерами транзисторов 5 и 6 через низкоомные резисторы 18 и 19, функции которых в ряде случаев могут выполнять объемные сопротивления эмиттерных областей.

В дифференциальном усилителе (фиг.5) коллектор 14 первого входного транзистора 1 связан с коллектором 16 четвертого вспомогательного транзистора 13 через первое токовое зеркало (20), коллектор 17 третьего вспомогательного транзистора 12 связан с коллектором 15 второго входного транзистора 2 через второе токовое зеркало 21, причем коллектор 15 второго входного транзистора 2 связан с выходом дифференциального усилителя 22 через третье токовое зеркало 23, а коллектор 16 четвертого вспомогательного транзистора 13 связан с выходом дифференциального усилителя 22 через четвертое токовое зеркало 24.

Рассмотрим работу заявляемого ДУ (фиг.2).

В статическом режиме транзисторы 12 и 13 закрыты, а коллекторные токи транзисторов 7 и 8 (за счет отрицательной обратной связи по петле «эмиттер транзистора 7 (8)» - «база транзистора 5 (6)» - «коллектор транзистора 5 (6))» равны токам базы транзисторов 5 и 6. При этом коллекторные токи этих транзисторов, а также транзисторов 1 и 2 практически равны токам I10 и I11 источников опорного тока 10 и 11.

Стабильность статического режима (точка 1, фиг.4) рассматриваемой схемы определяется стабильностью токов I10 и I11, которая для современного уровня развития схемотехники может быть достаточно высокой. Таким образом, погрешность установления статического режима в заявляемом устройстве не хуже, чем в известном ДУ-прототипе.

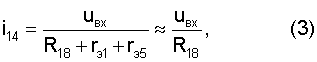

Если на вход 3 ДУ (фиг.2) подается положительное приращение входного напряжения uвх, то это вызывает начальное увеличение коллекторного тока транзистора 1 (5) и уменьшение коллекторного тока транзистора 2 (6) (участок 1-2 фиг.4). Как следствие, транзистор 7 запирается, а транзистор 13, наоборот, входит в активный режим. Его эмиттерный ток и, следовательно, выходной ток ДУ i16 будет теперь равен разности между iк5 и I10. С другой стороны, указанная выше отрицательная обратная связь, начиная с этого уровня входного сигнала uвх=Uвкл, будет стабилизировать ток коллектора транзистора 6 на уровне тока I11. Поэтому напряжения эмиттер-база транзисторов 6 и 2, а также напряжение на резисторе 19 не будут изменяться, а все дальнейшее приращение uвх прикладывается к участку цепи «вход 3 - база транзистора 5». Поэтому коллекторный ток транзистора 1, а также токи выходов 14 и 16 будут в дальнейшем изменяться пропорционально uвх (участок 2-3, фиг.4) и не имеют традиционных ограничений, характерных для известного ДУ:

где R18 - сопротивление резистора 18;

rэ5,rэ5 - сопротивление эмиттерных переходов транзисторов 1 и 5.

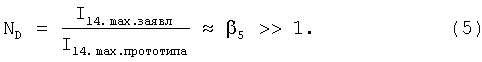

Рост токов выхода 14 (пропорциональный uвх), а также токов выхода 16 будет продолжаться до тех пор, пока весь ток I11 не поступит в эмиттер транзистора 8. Данный граничный (максимально возможный) ток определяется по формуле

где β5 - коэффициент усиления по току базы транзистора 5.

Таким образом, в сравнении с ДУ-прототипом выигрыш по диапазону линейного изменения выходного тока в заявляемом устройстве достигает значений

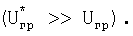

С другой стороны, в сравнении с прототипом входное напряжение  (фиг.4), при котором происходят ограничения входных токов ДУ на уровне Imax, существенно возрастает

(фиг.4), при котором происходят ограничения входных токов ДУ на уровне Imax, существенно возрастает

Угол наклона γ2 характеристики i14=f(uвх) (фиг.4) определяются резистором 18. Если резистор 18 (19) исключить, то проходная характеристика ДУ (фиг.4) будет иметь экспоненциальный характер, но величина максимального тока i14 (i16) останется прежней (4).

При отрицательном приращении uвх в схеме фиг.2 стабилизируется коллекторный ток транзистора 5 на уровне тока источника 10. Как следствие, все отрицательное приращение uвх прикладывается к участку цепи «база транзистора 6» - «база транзистора 4». Поэтому выходные токи i15 и i17 не ограничиваются и пропорциональны uвх.

Результаты компьютерного моделирования ДУ (фиг.2) на графиках фиг.7-10 подтверждают полученные выше теоретические выводы.

В соответствии с п.2 формулы изобретения предлагаемый ДУ может использоваться в структуре быстродействующих операционных усилителей различного функционального назначения. Особенность схемы фиг.5 состоит в том, что сигналы на токовых выходах 16 и 17 при малых входных напряжениях могут отсутствовать (фиг.10), но в то же время они достигают больших значений при включении в работу транзисторов 13, 12 и эффективно форсируют процесс перезаряда емкостей на выходе 22 ДУ (фиг.5).

За счет исключения одной из токопотребляющих ветвей между источниками питания статический ток ДУ (фиг.2) (в сравнении с прототипом) уменьшается в два раза.

Библиографический список

1. Патент США №3.786.362

2. Патент США №4.030.044

3. Патент США №4.059.808, фиг.5

4. Патент США №4.286.227

5. Авт. свид. СССР №375754, H 03 F 3/38

6. Авт. свид. СССР №843164, H 03 F 3/30

7. Авт. свид. СССР №1107281

8. Авт. свид. СССР №1107279

9. Патент РФ №2930041, H 03 F 1/32

10. Патент Японии №57-5364, H 03 F 3/343

11. Патент ЧССР №134845, кл. 21a2 18/08

12. Патент ЧССР №134849, кл. 21a2 18/08

13. Патент ЧССР №135326, кл. 21а2 18/08

14. Авт. свид. СССР №1720146, H 03 F 3/45

15. Патент Англии №1543361, Н3Т

16. Патент США №5.521.552 (фиг.3а)

17. Патент США №4.059.808

18. Патент США №5.789.949

19. Патент США №4.453.134

20. Патент США №4.760.286

21. Авт. свид. СССР №1283946

22. Патент РФ №2019019

23. Патент США №4.389.579

24. Патент США №4.453.092

25. Патент США №3.566.289

26. Патент США №4.059.808 (фиг.2)

27. Патент США №3.649.926

28. Патент США №4.714.894 (фиг.1)

29. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989.

30. М.Херпи. Аналоговые интегральные схемы. - М.: Радио и связь, 1983, стр.174, рис.5.52.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ СИНФАЗНОГО СИГНАЛА | 2006 |

|

RU2319287C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319296C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2011 |

|

RU2458455C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ВХОДНЫМ СОПРОТИВЛЕНИЕМ | 2009 |

|

RU2394360C1 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2012 |

|

RU2509406C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412529C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ АКТИВНОЙ РАБОТЫ | 2007 |

|

RU2331971C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2394362C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2307458C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2005 |

|

RU2293433C1 |

Изобретение относится к радиотехнике и связи для усиления аналоговых сигналов с широким динамическим диапазоном в структуре аналоговых микросхем различного функционального назначения, например, быстродействующих операционных усилителях (ОУ). Технический результат заключается в расширении диапазона линейного усиления сигналов. Дифференциальный усилитель (ДУ) (фиг.2) содержит входные транзисторы (Т) (1, 2), эмиттеры которых связаны с выходными Т (5, 6), базы которых соединены друг с другом и подключены к коллекторам вспомогательных Т (7, 8), базы которых соединены друг с другом, а также источником опорного напряжения (ИОН) 9, причем коллекторы выходных Т (5, 6) соединены с источниками опорного тока (ИОТ) (10, 11), а базы вспомогательных Т (12, 13) объединены друг с другом, коллекторы которых соединены с базами вспомогательных Т (7, 8). Эмиттеры вспомогательных Т (7, 13) связаны с коллектором выходного Т (5), эмиттеры вспомогательных Т (8, 12) связаны с коллектором выходного Т (6). 1 з.п. ф-лы, 11 ил.

| US 4030044, 14.06.1977 | |||

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 0 |

|

SU375754A1 |

| Усилитель низкой частоты | 1977 |

|

SU843164A1 |

| Дифференциальный усилитель | 1982 |

|

SU1107281A1 |

| US 4059808, 22.11.1977. | |||

Авторы

Даты

2007-01-27—Публикация

2005-07-19—Подача