Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления высокочастотных аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в операционных усилителях (ОУ), быстродействующих компараторах двух напряжений и т.п.).

Известны схемы дифференциальных усилителей (ДУ), у которых входной сигнал подается в цепь эмиттеров транзисторов входной дифференциальной пары. Такие ДУ в сравнении с классическими параллельно-балансными каскадами, у которых сигнал подается в цепь базы входных транзисторов, имеют ряд существенных преимуществ при усилении быстроизменяющихся и СВЧ-сигналов. Например, они оказываются лучше по полосе пропускания, которая достигает максимальных значений для схем с общей базой, а также по величине входного сопротивления, которое (для согласования с источником сигнала) может быть установлено на уровне небольших волновых сопротивлений линий связи. Следует также заметить, что в таких ДУ отсутствует эффект Миллера (умножение емкости коллектор-база транзисторов), что также положительно сказывается на их полосе пропускания.

Все известные усилители с эмиттерным входом [1-60], которые объединяются в особый класс «токовых усилителей», можно также разбить на следующие подклассы - усилители с дифференциальными токовыми входами (ДТУ) [1-37], дифференциальные усилители напряжения на основе дифференциальных усилителей с токовыми входами, которые в качестве обязательных элементов схемы включают входные прецизионные резисторы, осуществляющие предварительное преобразование входных напряжений во входные токи ДТУ [38-44] и усилители с единственным токовым входом [45-51]. Большая группа дифференциальных усилителей с токовыми входами выполнена с применением входных разделительных конденсаторов, что является вынужденной мерой по обеспечению их работосопособности [52-60].

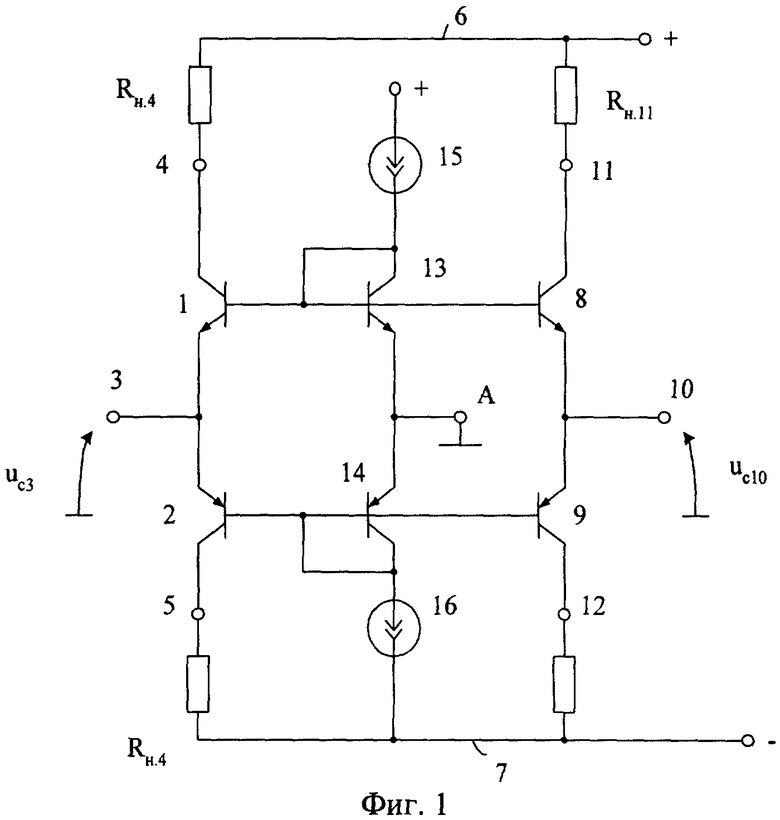

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте США №5734294, содержащий первый 1 и второй 2 входные транзисторы разного типа проводимости, эмиттеры которых связаны друг с другом и подключены к первому 3 входу дифференциального усилителя, коллекторы соединены с первым 4 и вторым 5 выходами для большого сигнала, согласованными соответственно с шинами положительного 6 и отрицательного 7 источников питания, третий 8 и четвертый 9 входные транзисторы разного типа проводимости, эмиттеры которых связаны друг с другом и подключены ко второму 10 входу дифференциального усилителя, коллекторы соединены с третьим 11 и четвертым 12 выходами для большого сигнала, согласованными соответственно с шинами положительного 6 и отрицательного 7 источников питания, первый 13 и второй 14 вспомогательные транзисторы, причем база первого входного транзистора 1 связана с первым источником опорного тока 15, а база четвертого входного транзистора 9 связана со вторым источником опорного тока 16.

Существенный недостаток известного устройства состоит в том, что оно не работоспособно, если напряжение источников сигналов изменяется в широком диапазоне, а сами источники характеризуются малыми (или нулевыми) внутренними сопротивлениями. По существу, известный ДУ является дифференциальным усилителем двух входных токов. Если входные напряжения Uc3 и Uc10 (фиг.1) изменяются в диапазоне от напряжения питания положительного источника 6 до напряжения питания отрицательного источника 7, то «жесткая привязка» потенциала баз входных транзисторов 1, 2, 8, 9 (узел А) не позволяет обеспечить во всем диапазоне сигналов активный режим данного ДУ. Известное устройство работоспособно только с очень малыми входными напряжениями (Uс3<20÷25 мВ, Uc10<20÷25 мВ), либо с токовыми сигналами, которые могут быть получены из больших потенциальных сигналов Uc3, Uc10 за счет включения между источниками этих сигналов и входами 3, 10 соответствующих резистивных преобразователей «напряжение-ток» [38-44]. Однако входные резистивные преобразователи отрицательно влияют на погрешность известного ДУ и его быстродействие.

Основная цель предлагаемого изобретения состоит в расширении диапазона изменения входного синфазного сигнала (Uс.max). При этом увеличение Uс.max обеспечивается в заявляемой схеме при изменении внутреннего сопротивления источников сигналов в широких пределах, вплоть до нулевых значений.

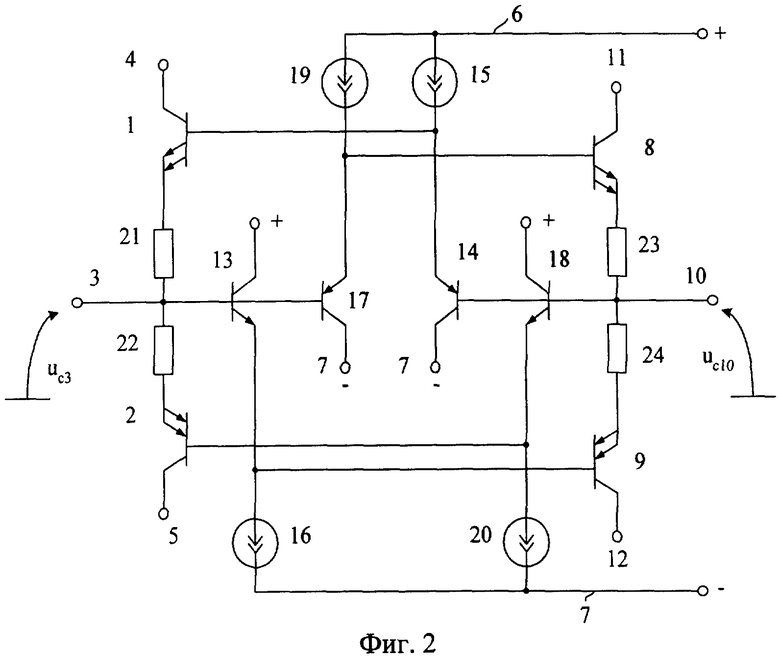

Поставленная цель достигается тем, что в дифференциальном усилителе фиг.1, содержащем первый 1 и второй 2 входные транзисторы разного типа проводимости, эмиттеры которых связаны друг с другом и подключены к первому 3 входу дифференциального усилителя, коллекторы соединены с первым 4 и вторым 5 выходами для большого сигнала, согласованными соответственно с шинами положительного 6 и отрицательного 7 источников питания, третий 8 и четвертый 9 входные транзисторы разного типа проводимости, эмиттеры которых связаны друг с другом и подключены ко второму 10 входу дифференциального усилителя, коллекторы соединены с третьим 11 и четвертым 12 выходами для большого сигнала, согласованными соответственно с шинами положительного 6 и отрицательного 7 источников питания, первый 13 и второй 14 вспомогательные транзисторы, причем база первого входного транзистора 1 связана с первым источником опорного тока 15, а база четвертого входного транзистора 9 связана со вторым источником опорного тока 16, предусмотрены новые элементы и связи, в схему введены первый 17 и второй 18 дополнительные транзисторы, а также первый 19 и второй 20 дополнительные источники опорного тока, причем первый дополнительный источник опорного тока 19 соединен с эмиттером первого дополнительного транзистора 17 и базой третьего входного транзистора 8, второй дополнительный источник опорного тока 20 соединен с базой второго входного транзистора 2 и эмиттером второго дополнительного транзистора 18, база первого дополнительного транзистора 17 соединена с первым входом 3 дифференциального усилителя, база второго дополнительного транзистора 18 соединена со вторым входом 10 дифференциального усилителя, эмиттер первого вспомогательного транзистора 13 соединен с базой четвертого выходного транзистора 9, его база подключена к первому входу 3 дифференциального усилителя, эмиттер второго вспомогательного транзистора 14 подключен к базе первого входного транзистора 1, его база связана со вторым входом 10 дифференциального усилителя. При этом коллекторы второго вспомогательного транзистора 14 и первого дополнительного транзистора 17 подключены к отрицательной шине источника питания 7 или используются в качестве соответствующих малосигнальных второго 32 и третьего 33 токовых выходов дифференциального усилителя, а коллекторы первого вспомогательного транзистора 13 и второго дополнительного транзистора 18 подключены к шине положительного источника питания 6 или используются в качестве соответствующих малосигнальных первого 31 и четвертого 34 токовых выходов дифференциального усилителя.

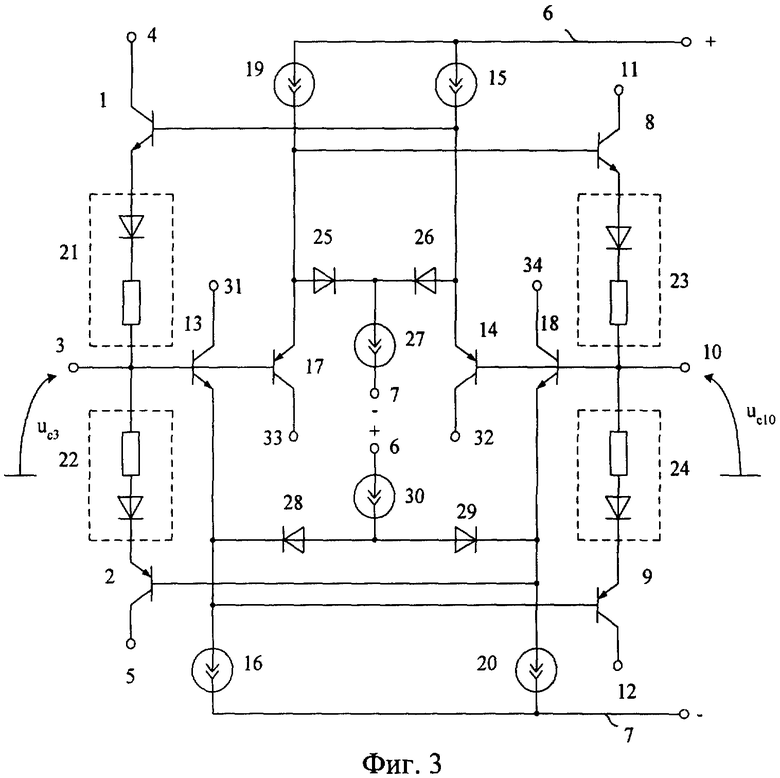

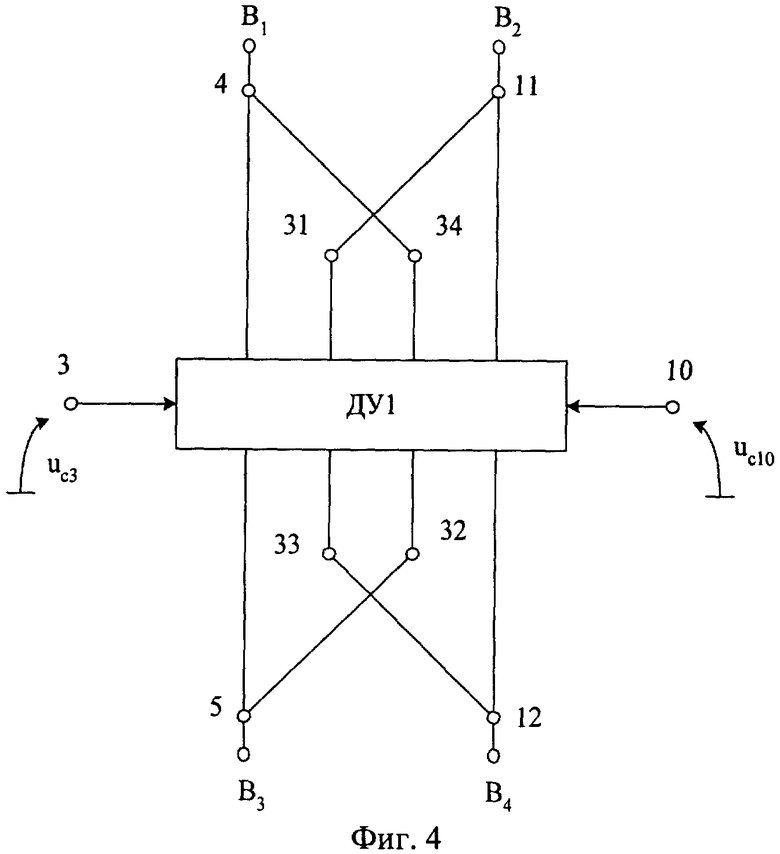

Схема заявляемого устройства, соответствующая п.1 и п.2 формулы изобретения, приведена на фиг.2. На фиг.3 показан заявляемый ДУ в соответствии с п.3 и п.4 формулы изобретения. На фиг.4 представлен заявляемый ДУ, в котором синфазные выходы для большого и малого сигналов связаны друг с другом.

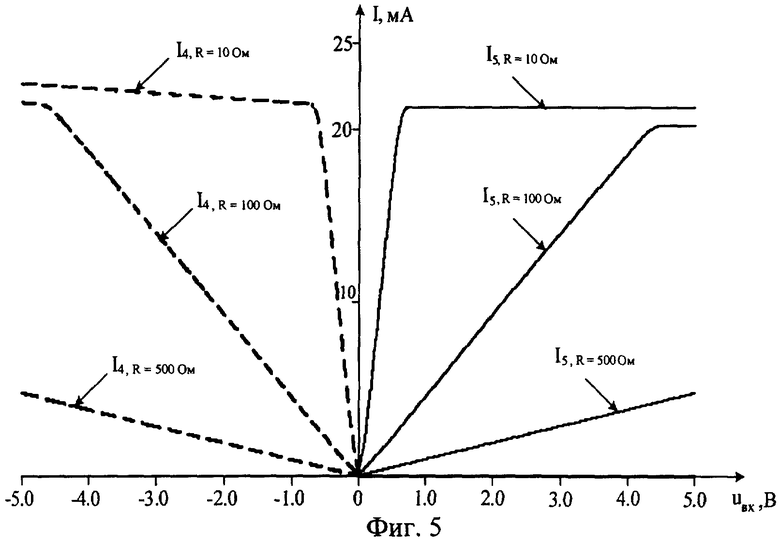

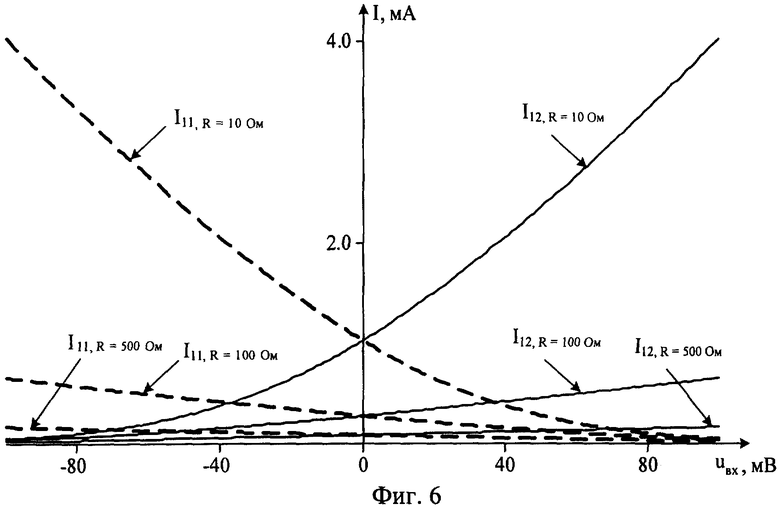

На фиг.5 и фиг.6 изображены проходные характеристики заявляемого устройства фиг.2 для выходов 4, 5 и 11, 12 при разных значениях сопротивления R двухполюсников 21-24, полученные авторами в среде PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

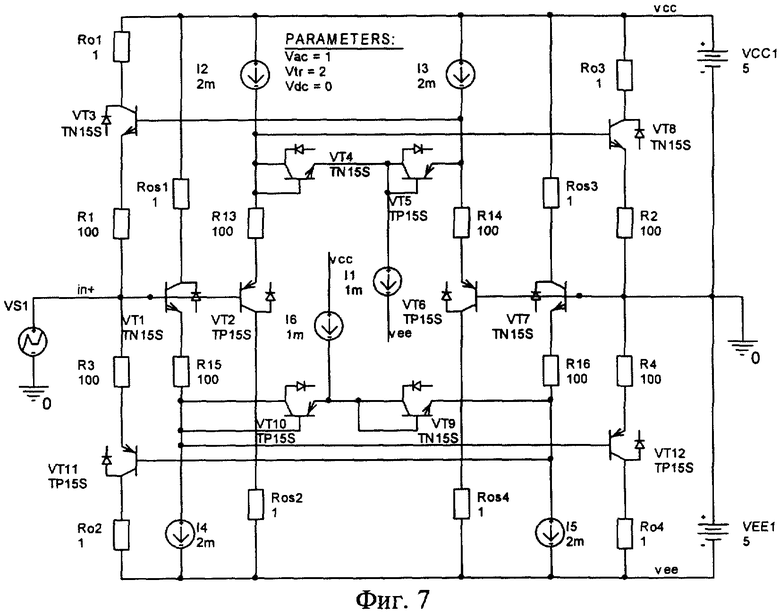

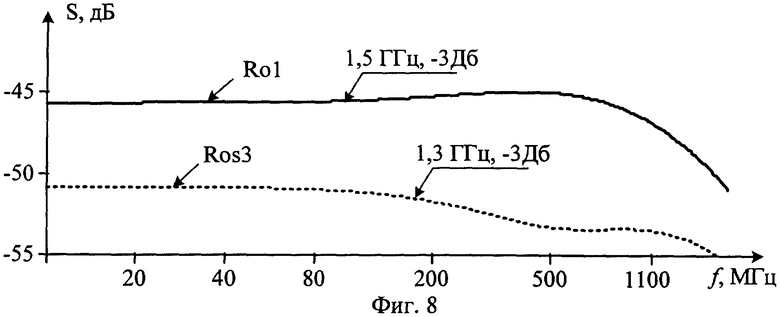

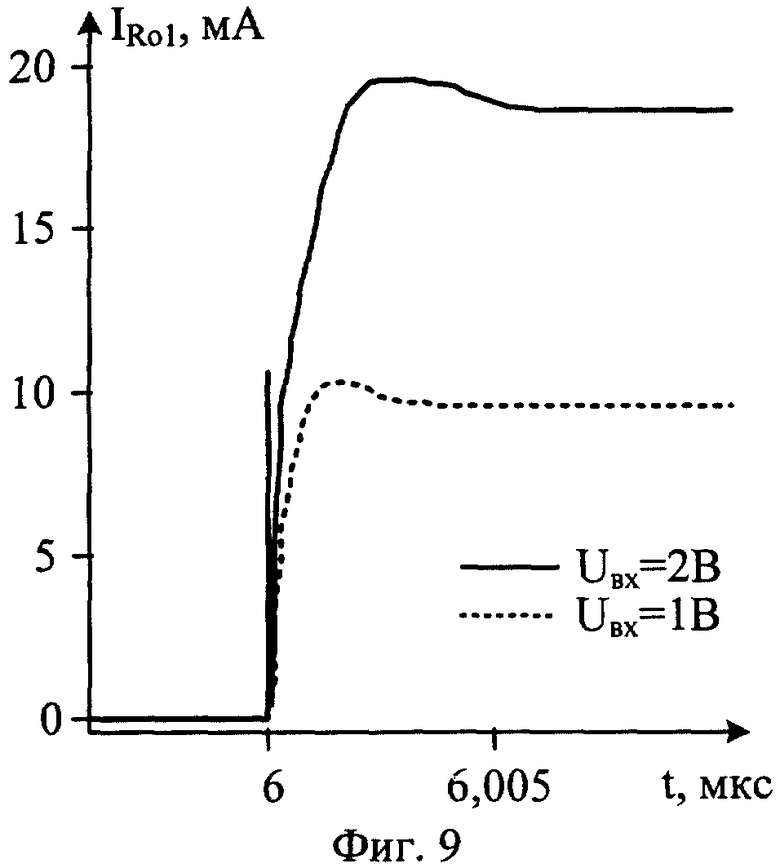

На фиг.7 показана также схема фиг.3 в среде PSpice, результаты исследования которой приведены на фиг.8 (зависимость крутизны S от частоты для выходов 4 и 34, фиг.3 и на фиг.9 (для разных амплитуд дифференциальных входных сигналов (Uвх=1 В, Uвх=2 В)).

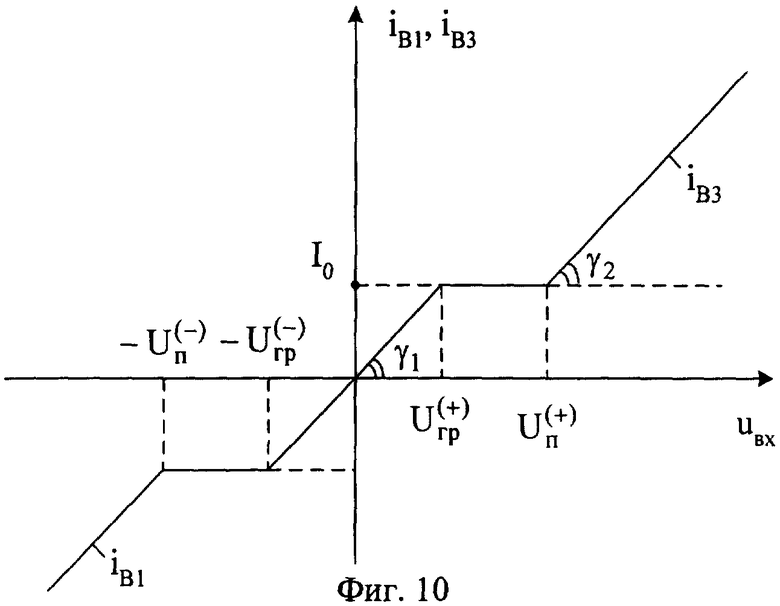

Типовая теоретическая зависимость суммарных токов для выходов B1-В4 (схема фиг.4) показана на фиг.10.

Дифференциальный усилитель фиг.2 содержит первый 1 и второй 2 входные транзисторы разного типа проводимости, эмиттеры которых связаны друг с другом и подключены к первому 3 входу дифференциального усилителя, коллекторы соединены с первым 4 и вторым 5 выходами для большого сигнала, согласованными соответственно с шинами положительного 6 и отрицательного 7 источников питания, третий 8 и четвертый 9 входные транзисторы разного типа проводимости, эмиттеры которых связаны друг с другом и подключены ко второму 10 входу дифференциального усилителя, коллекторы соединены с третьим 11 и четвертым 12 выходами для большого сигнала, согласованными соответственно с шинами положительного 6 и отрицательного 7 источников питания, первый 13 и второй 14 вспомогательные транзисторы, причем база первого входного транзистора 1 связана с первым источником опорного тока 15, а база четвертого входного транзистора 9 связана со вторым источником опорного тока 16. В схему введены первый 17 и второй 18 дополнительные транзисторы, а также первый 19 и второй 20 дополнительные источники опорного тока, причем первый дополнительный источник опорного тока 19 соединен с эмиттером первого дополнительного транзистора 17 и базой третьего входного транзистора 8, второй дополнительный источник опорного тока 20 соединен с базой второго входного транзистора 2 и эмиттером второго дополнительного транзистора 18, база первого дополнительного транзистора 17 соединена с первым входом 3 дифференциального усилителя, база второго дополнительного транзистора 18 соединена со вторым входом 10 дифференциального усилителя, эмиттер первого вспомогательного транзистора 13 соединен с базой четвертого выходного транзистора 9, его база подключена к первому входу 3 дифференциального усилителя, эмиттер второго вспомогательного транзистора 14 подключен к базе первого входного транзистора 1, его база связана со вторым входом 10 дифференциального усилителя. При этом коллекторы второго вспомогательного транзистора 14 и первого дополнительного транзистора 17 подключены к отрицательной шине источника питания 7 или используются в качестве соответствующих малосигнальных второго 32 и третьего 33 токовых выходов дифференциального усилителя, а коллекторы первого вспомогательного транзистора 13 и второго дополнительного транзистора 18 подключены к шине положительного источника питания 6 или используются в качестве соответствующих малосигнальных первого 31 и четвертого 34 токовых выходов дифференциального усилителя.

Для обеспечения широкого диапазона активной работы заявляемого ДУ (фиг.2) эмиттеры первого 1 и второго 2 входных транзисторов связаны друг с другом через первый 21 и второй 22 дополнительные двухполюсники, общий узел которых соединен с первым 3 входом дифференциального усилителя, а эмиттеры третьего 8 и четвертого 9 входных транзисторов связаны друг с другом через третий 23 и четвертый 24 дополнительные двухполюсники, общий узел которых соединен со вторым 10 входом дифференциального усилителя. В частном случае каждый из дополнительных двухполюсников 21, 22, 23 и 24 может быть выполнен в виде последовательно соединенных р-n - перехода и резистора. Это позволяет регулировать зону нечувствительности на проходных характеристиках ДУ (фиг.10, напряжения  ,

,  ).

).

Для организации четырех малосигнальных токовых выходов ДУ фиг.2 эмиттеры первого дополнительного 17 и второго вспомогательного 14 транзисторов соединены друг с другом через первый 25 и второй 26 встречно включенные дополнительные прямосмещенные р-n - переходы, общий узел которых соединен с третьим 27 дополнительным источником опорного тока, а эмиттеры первого вспомогательного 13 и второго дополнительного 18 транзисторов соединены друг с другом через третий 28 и четвертый 29 встречно включенные прямосмещенные p-n - переходы, общая точка которых соединена с четвертым 30 дополнительным источником опорного тока, причем коллекторы первого 13 и второго (14) вспомогательных транзисторов, а также коллекторы первого 17 и второго 18 дополнительных транзисторов используются в качестве соответствующих малосигнальных первого 31 и второго 32, третьего 33 и четвертого 34 токовых выходов дифференциального усилителя.

Соединение выходов для малого сигнала и выходов для большого сигнала заявляемого ДУ (фиг.4) позволяет реализовать быстродействующее устройство, которое одинаково хорошо обрабатывает как малые сигналы (uвх<50 мВ), так и большие сигналы (uвх>>50 мВ). Для этой цели первый выход для большого сигнала 4 соединен с четвертым 34 малосигнальным токовым выходом дифференциального усилителя, второй выход для большого сигнала 5 соединен со вторым малосигнальным токовым выходом 32, третий выход для большого сигнала 11 соединен с первым малосигнальным токовым выходом 31, четвертый выход для большого сигнала 12 соединен с третьим 33 малосигнальным токовым выходом.

Рассмотрим работу заявляемого ДУ на примере анализа схемы фиг.2.

При нулевых значениях сигналов на входах 3 и 10 статический режим по току всех транзисторов устанавливается источниками опорного тока 15, 16, 19 и 20. В том случае, когда необходимо обеспечить не нулевые значения токов эмиттеров транзисторов 1, 2, 8 и 9, близкие по величине к токам I15=I16=I19=I20 при наличии резисторов 21, 22, 23 и 24, в качестве транзисторов 1, 2, 8 и 9 рекомендуется использовать транзисторы с большей площадью эмиттерных p-n - переходов, чем у соответствующих транзисторов 14, 18, 17, 13. За счет применения более сложных вариантов построения двухполюсников 21, 22, 23, 24 (фиг.3) можно обеспечить также режим отсечки транзисторов 1, 2, 8, 9, то есть их «включение» в работу при вполне определенных уровнях дифференциального сигнала uвх=uc3-uc10>Uп, где Uп - зона нечувствительности проходной характеристики фиг.10. Так, в схеме фиг.3 переход транзисторов 1, 2, 8, 9 в активный режим будет происходить при uвх>Uп≈0,5÷0,6. Наличие зоны нечувствительности, которая регулируется структурой двухполюсников 21-24, создает в схеме фиг.3 условия, при которых минимизируется влияние транзисторов 1, 2, 8, 9 на малый сигнал и статический режим ДУ (его входные токи, дрейф эдс смещения нуля, коэффициент ослабления синфазных сигналов и т.п.). В этом случае выходы для большого сигнала 4, 5, 11, 12 будут активны только при uвх>Uп≈0,5÷0,6, что вполне допустимо во многих применениях ДУ.

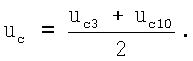

Заявляемый ДУ может работать как от дифференциальных сигналов uвх=uc3-uc10, так и при наличии в этих сигналах синфазной составляющей

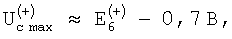

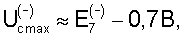

Действительно, увеличение, например на 5 В, синфазного сигнала на входах 3 и 10 (uс3=uc10=5 B) передается на базы транзисторов 1 и 2 через эмиттерные повторители на транзисторах 14 и 18 и на базы транзисторов 8 и 9 через эмиттерные повторители на транзисторах 17 и 13. Как следствие, токи через транзисторы 1, 2, 8 и 9 не изменяются, то есть схема фиг.2 (в отличие от ДУ-прототипа) работоспособна при синфазном изменении входных сигналов uс3, uc10 - она обеспечивает преобразование разности uс3-uc10 в широком диапазоне uc=(uc3+uc10)/2, близком к напряжению питания 6 и 7. При идеальных источниках опорного тока 15, 16, 19 и 20

где  - напряжения источников питания 6 и 7.

- напряжения источников питания 6 и 7.

Существенное отличие схемы фиг.3 от схемы фиг.2 состоит в организации еще четырех выходов для малого сигнала 32, 32, 33, 34, которые отличаются по свойствам от выходов для большого сигнала 4, 5, 11, 12 - их выходные токи, пропорциональные разности uвх=uc3-uc10, только в том случае, если |uвх|<80÷100 мВ. Графики фиг.8 показывают, что верхняя граничная частота крутизны преобразования uвх=uc3-uc10 в выходные токи (S=iвых/uвх) близка к верхней граничной частоте S токовых выходов (4, 5, 11, 12) для большого сигнала (fв.5≈fв.14≈1,3÷1,5 ГГц).

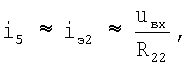

Введение p-n - переходов 25, 26, 28, 29 обеспечивает, с одной стороны, преобразование малых сигналов uвх=uc3-uc10 к выходам 31÷34, а с другой - нелинейное преобразование больших дифференциальных сигналов, передаваемых через эмиттерные повторители 17, 14, 13 и 18 на базы транзисторов 8, 1, 9, 2. Предположим, что uc3>>uc10. Это приводит к запиранию p-n - перехода 28 и фиксации потенциала базы транзистора 2 на уровне uб≈uс10. Таким образом, к участку цепи между входом 3 и базой транзистора 2 будут приложены практически все приращения uвх>>80÷100 мВ. Поэтому ток эмиттера транзистора 2 и, следовательно, ток выхода 5 будут пропорциональны uвх в широком диапазоне его изменения (до нескольких вольт):

где R22 - дифференциальное сопротивление двухполюсника 22.

Данный вывод подтверждают экспериментальные графики для выходных токов i4, i5 (фиг.5 и фиг.6), которые снимались при разных значениях сопротивлений двухполюсников 22 и 21 R22=R21=R.

Соединение синфазных выходов заявляемого ДУ для большого и малого сигналов по схеме фиг.4 позволяет (в зависимости от стоящей задачи) создавать входные каскады операционных усилителей и компараторов с высоким быстродействием как при малых, так и при больших сигналах. Графики фиг.9 показывают, что время фронта тока выхода для большого сигнала измеряется единицами наносекунд, причем этот ток пропорционален амплитуде uвх=Uвх, что характерно для линейных систем.

В общем случае проходная характеристика суммарного тока выхода B1-B4 iвых.В1=f(uвх) для схемы фиг.4 имеет вид, показанный на фиг.10. В зависимости от структуры двухполюсников 21-24 зона нечувствительности Uп может выбираться в пределах Uп=50-500 мВ.

Полученные выше выводы подтверждаются результатами моделирования предлагаемых схем в среде PSpice с использованием моделей интегральных транзисторов ФГУП НПП «Пульсар» (г.Москва) - заявляемый ДУ работоспособен в широком диапазоне изменения синфазных сигналов при высоком быстродействии, что невозможно обеспечить в рамках известных технических решений. При этом предлагаемый дифференциальный усилитель сохраняет все свои свойства усилителя с дифференциальными токовыми входами.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №5734294 (прототип).

2. Патент США №6621308.

3. Патент США №6639473.

4. Патентная заявка США US 2005/0140443.

5. Патент США №5900779.

6. Патент США №5742154.

7. Патент США №5834951.

8. Патент США №4378529.

9. Патент США №4510459.

10. Патент США №5973562.

11. Патент Франции №2337969.

12. Патент США №4887047.

13. Патент Японии JP 2001308658.

14. Патент США №3972003.

15. Патент США №4521739.

16. Патентная заявка US 2005/0140444.

17. Патент США №4277756.

18. Патентная заявка US 2004/0160275.

19. Патент США №6181207.

20. Патент США №4521737.

21. Патент США №4232271.

22. Патентная заявка US 2004/0227477.

23. Патент США №5734294.

24. Патент США №6191654.

25. Патент США №4065724.

26. Патент США RE 30587, Кл. 330-257, 1981 г.

27. Патент США №6825723.

28. Патент США №5126586.

29. Патент США №5258723.

30. Патент США №6882224.

31. Патент США №5671272.

32. Патентная заявка US 2005/0218994 A1.

33. Патент США №5671272.

34. Патент США №6882224.

35. Патентная заявка US 2005/0140443.

36. Патент США №3748588.

37. Патентная заявка ЕР 1548932 A1.

38. Патент США №5742154.

39. Патент США №4521739.

40. Патентная заявка US 2004/0160275.

41. Патент США №4232271.

42. Патент США №6191654.

43. Патент США №5126586.

44. Патент США №5671272.

45. Патент США №6822514.

46. Патент США №6624704.

47. Патент США №4446443.

48. Патент США №4393355.

49. Патент США №3748588.

50. Патентная заявка US 2006/0125565.

51. Патентная заявка US 2005/0218994.

52. Патент США №4510459.

53. Патентная заявка US 2005/0140443.

54. Патент США №4887047.

55. Патент Японии JP 2001308658.

56. Патент США №6822514.

57. Патентная заявка US 2005/0140444.

58. Патент США №4277756.

59. Патент США №5126586.

60. Патентная заявка US 2005/0218994.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НИЗКООМНЫМИ ВХОДАМИ | 2008 |

|

RU2383099C2 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2011 |

|

RU2458455C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ АКТИВНОЙ РАБОТЫ | 2007 |

|

RU2331971C1 |

| КОМПЛЕМЕНТАРНЫЙ ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2012 |

|

RU2510570C1 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2012 |

|

RU2509406C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ СИНФАЗНОГО СИГНАЛА | 2007 |

|

RU2331969C1 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2012 |

|

RU2504896C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319292C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2008 |

|

RU2384934C2 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ КЛАССА АВ | 2007 |

|

RU2331970C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления высокочастотных аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (операционные усилители (ОУ), быстродействующие компараторы двух напряжений и т.п.). Быстродействующий дифференциальный усилитель содержит входные транзисторы (Т) (1, 2) разного типа проводимости, эмиттеры которых связаны друг с другом и подключены к первому (3) входу дифференциального усилителя (ДУ), коллекторы соединены с первым (4) и вторым (5) выходами для большого сигнала, входные Т (8, 9) разного типа проводимости, эмиттеры которых связаны друг с другом и подключены ко второму (10) входу ДУ, коллекторы соединены с третьим (11) и четвертым (12) выходами для большого сигнала, вспомогательные Т (13, 14), база Т (1) связана с источником опорного тока (ИОТ) (15), а база Т (9) связана с ИОТ (16). Введены дополнительные Т (17, 18), а также дополнительные ИОТ (19, 20), ИОТ (19) соединен с эмиттером Т (17) и базой Т (8), ИОТ (20) соединен с базой Т (2) и эмиттером Т (18), база Т (17) соединена с входом (3) ДУ, а его коллектор подключен к шине отрицательного источника питания (ИП) (7), база Т (18) соединена с входом (10) ДУ, а его коллектор подключен к шине положительного ИП (6), эмиттер Т (13) соединен с базой Т (9), его база подключена к входу (3) ДУ, а коллектор связан с ИП (6), эмиттер Т (14) подключен к базе Т (1), его база связана с входом (10) ДУ, а коллектор подключен к ИП (7). 3 з.п. ф-лы, 10 ил.

| US 5734294 А, 31.05.1998 | |||

| Дифференциальный усилитель | 1983 |

|

SU1166271A1 |

| US 5742154 A, 21.04.1998 | |||

| US 5900779 A, 04.05.1999 | |||

| US 4887047, 12.12.1989. | |||

Авторы

Даты

2008-03-10—Публикация

2006-08-03—Подача