Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления широкополосных аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ) и компараторах, работающих с двумя сигналами, имеющими синфазную составляющую).

Известны схемы так называемых «перегнутых» каскодных дифференциальных усилителей (ДУ) на n-p-n- и p-n-р-транзисторах [1-37], которые стали основой более чем 20 серийных операционных усилителей, выпускаемых как зарубежными (НА2520, НА5190, AD797, AD8631, AD8632, ОР90 и др.), так и российскими (154УДЗ и др.) микроэлектронными фирмами. В связи с высокой популярностью такой архитектуры ДУ на их модификации выдано более 200 патентов. Предлагаемое изобретение относится к данному подклассу устройств.

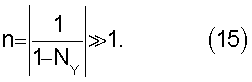

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте США №6.529.076, содержащий основной дифференциальный каскад 1 на первом 2 и втором 3 входных транзисторах с источником опорного тока 4 в их общей эмиттерной цепи и входами 5, 6, связанными с базами его первого 2 и второго 3 входных транзисторов, выходной каскодный усилитель на первом 7 и втором 8 выходных транзисторах, коллекторы которых связаны с первым токовым зеркалом 9, базы объединены и подключены к источнику напряжения смещения 10, а эмиттеры соединены с токовыми выходами 11 и 12 основного дифференциального каскада 1, а также с соответствующими синфазными токовыми выходами 13 и 14 управляемого по вспомогательному входу 15 второго токового зеркала 16.

Существенный недостаток известного ДУ (фиг.1) состоит в том, что он имеет сравнительно невысокое ослабление входных синфазных сигналов, что отрицательно сказывается на точностных параметрах неинвертирующих решающих усилителей и компараторов двух сигналов на его основе.

Основная цель предлагаемого изобретения состоит в повышении коэффициента ослабления входных синфазных сигналов.

Поставленная цель достигается тем, что в дифференциальный усилитель (фиг.1), содержащий основной дифференциальный каскад 1 на первом 2 и втором 3 входных транзисторах с источником опорного тока 4 в их общей эмиттерной цепи и входами 5, 6, связанными с базами его первого 2 и второго 3 входных транзисторов, выходной каскодный усилитель на первом 7 и втором 8 выходных транзисторах, коллекторы которых связаны с первым токовым зеркалом 9, базы объединены и подключены к источнику напряжения смещения 10, а эмиттеры соединены с токовыми выходами 11 и 12 основного дифференциального каскада 1, а также с соответствующими синфазными токовыми выходами 13 и 14 управляемого по вспомогательному входу 15 второго токового зеркала 16, вводятся новые элементы и связи - к основному дифференциальному каскаду 1 подключены входы дополнительного дифференциального каскада на транзисторах 17 и 18 с источником опорного тока 19 в общей эмиттерной цепи, токовые выходы которого 20, 21 соединены со вспомогательным входом 15 второго токового зеркала 16.

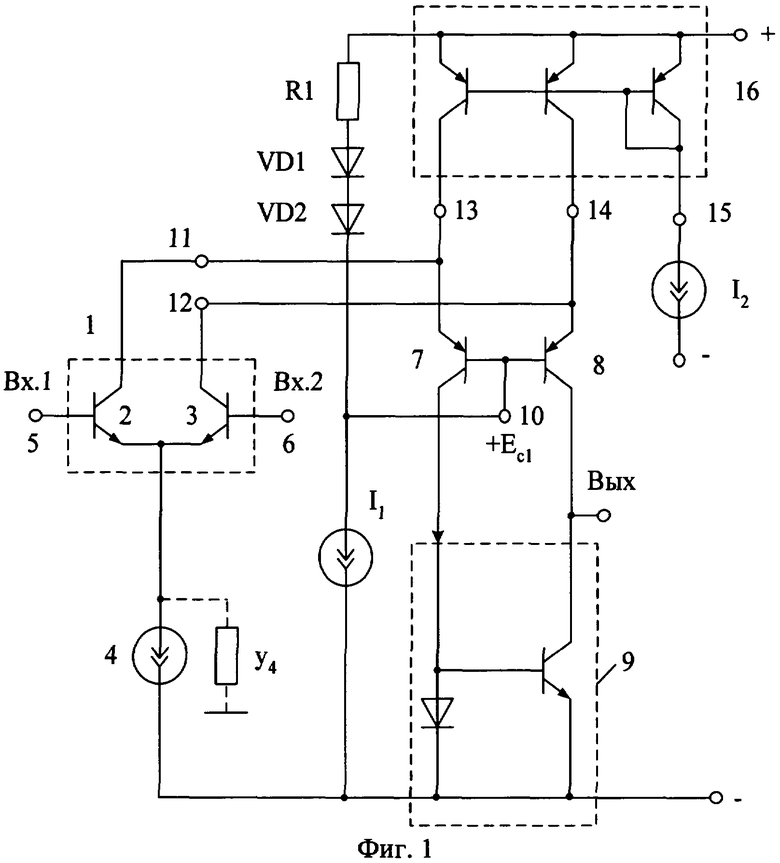

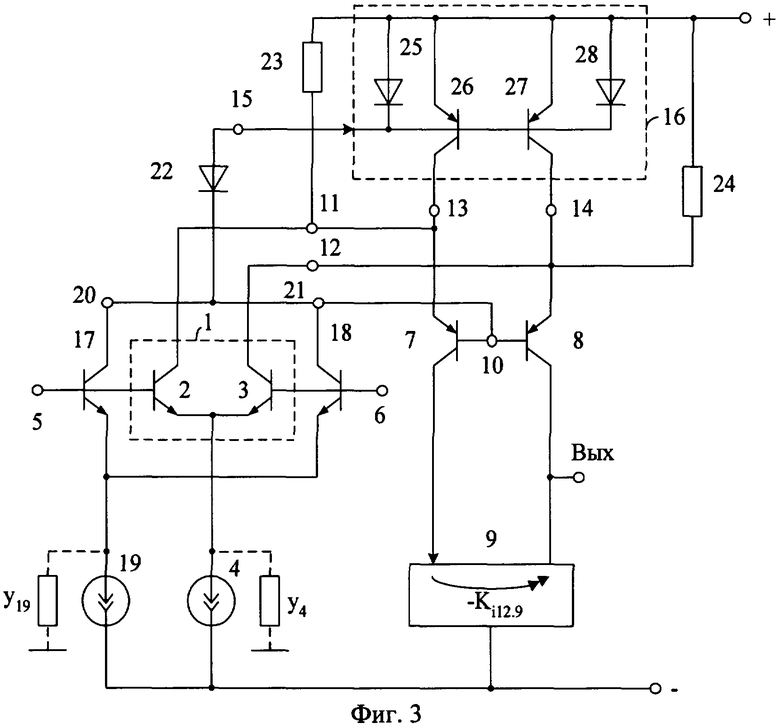

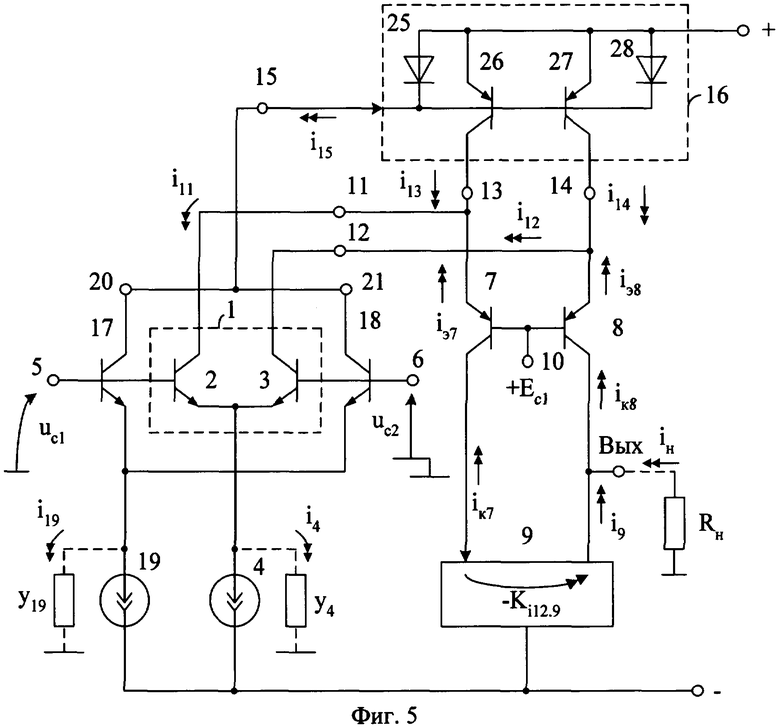

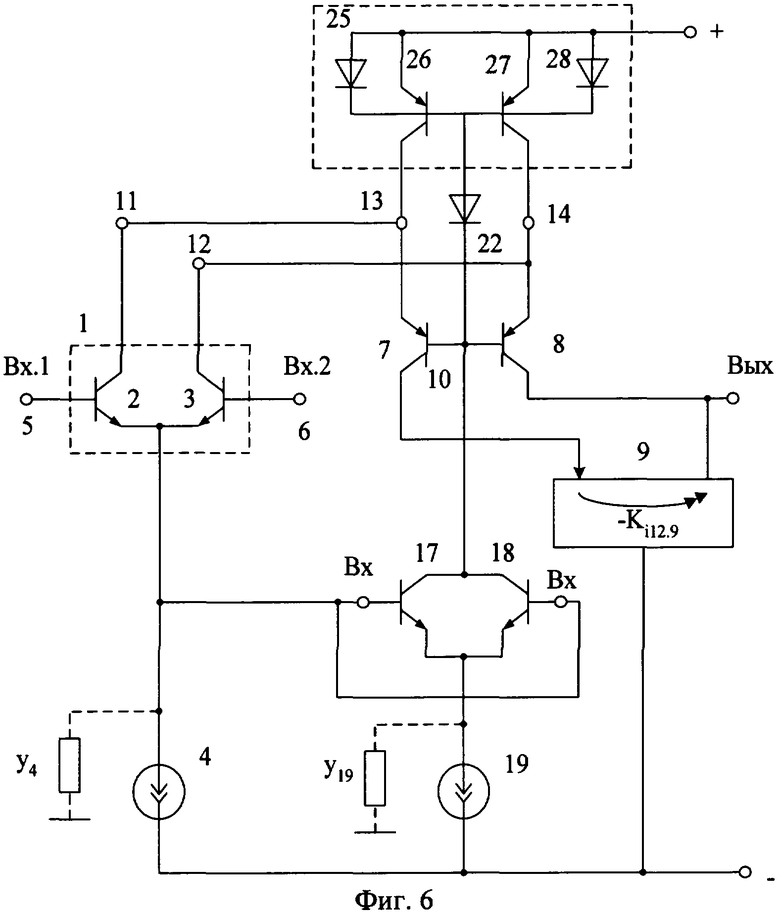

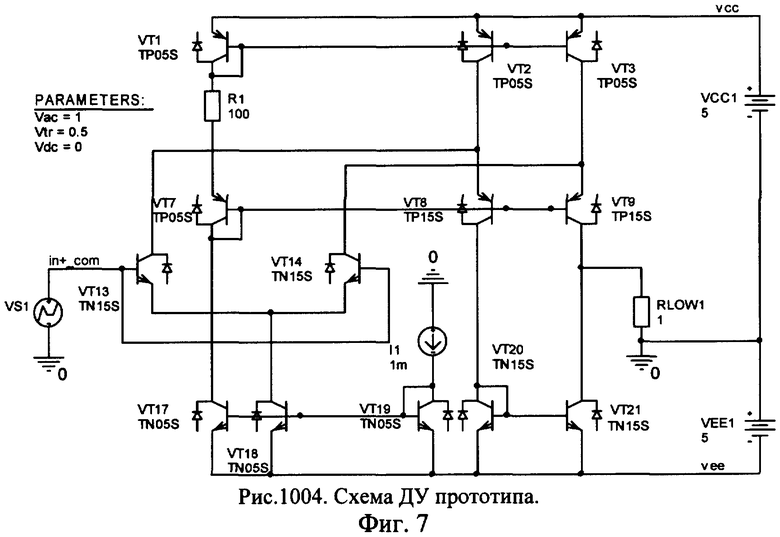

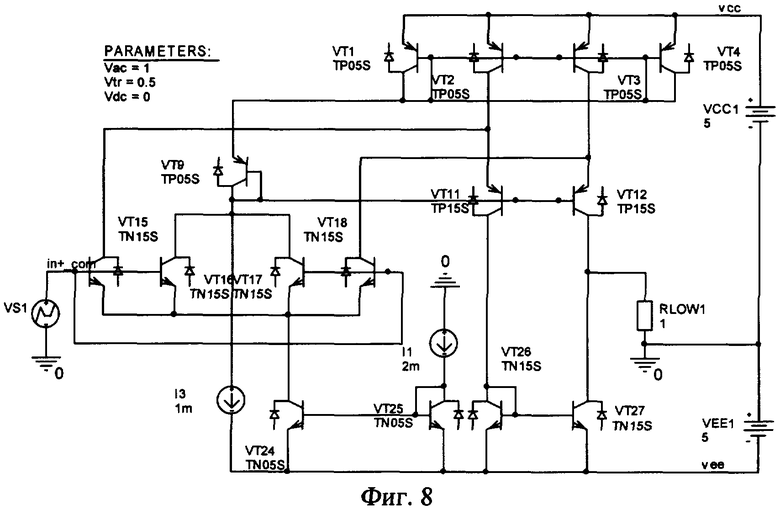

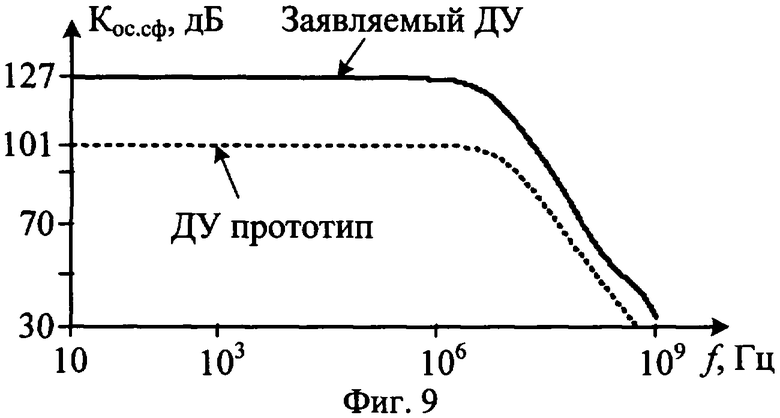

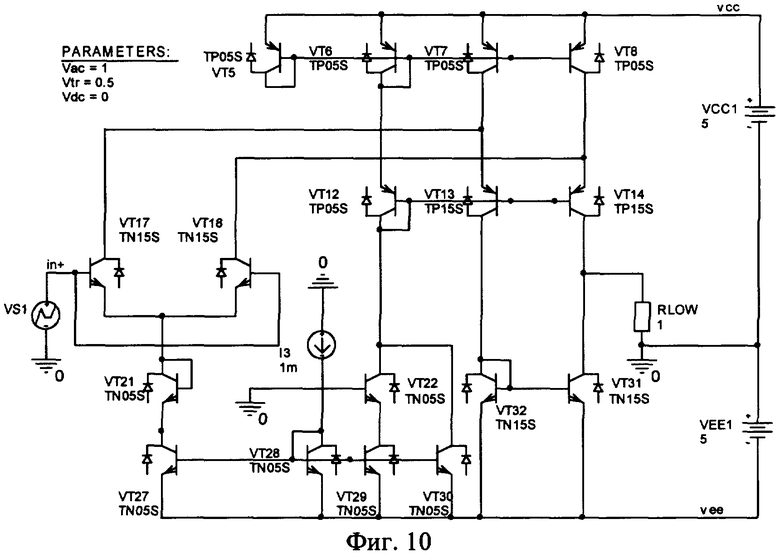

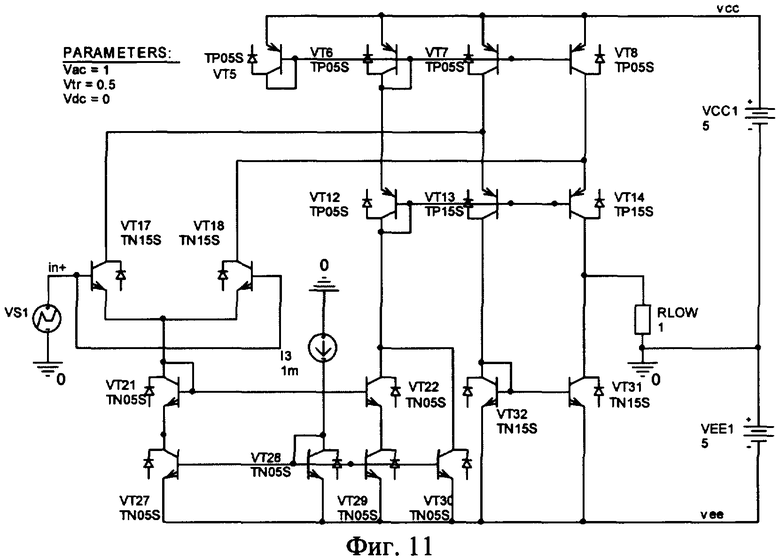

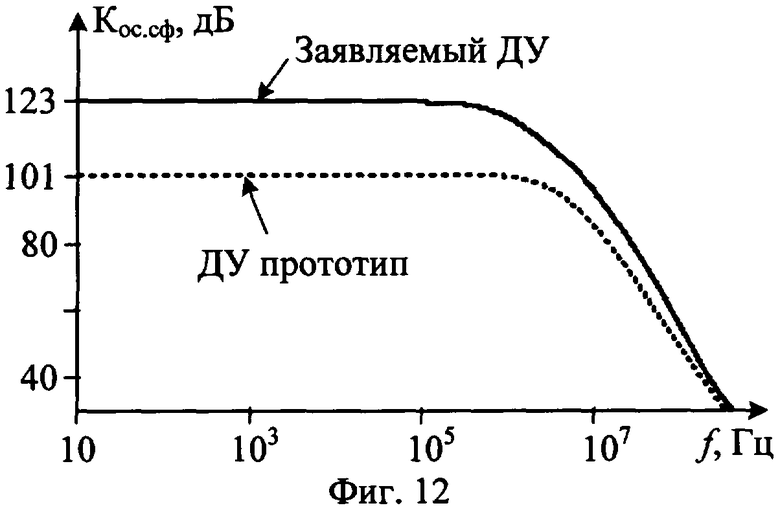

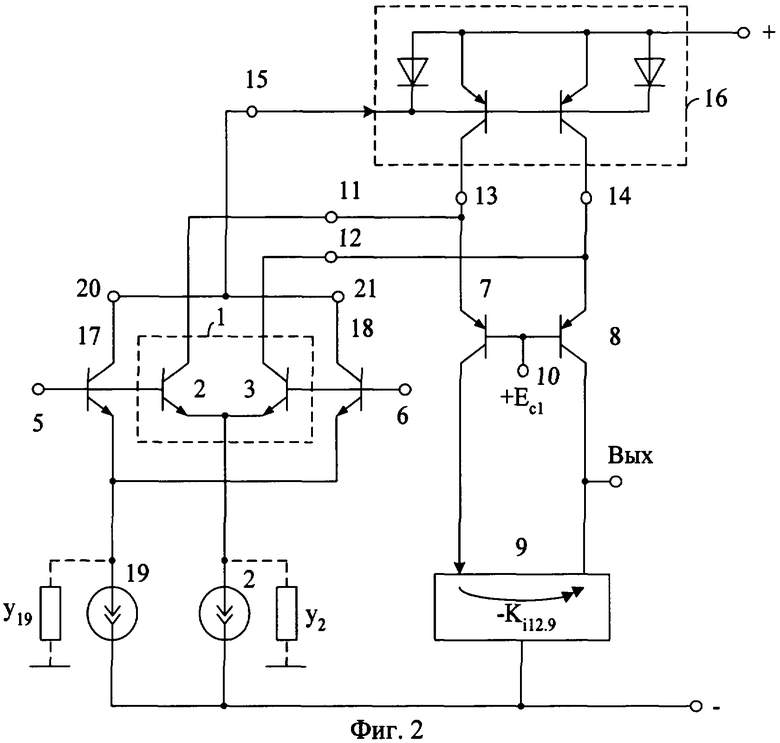

Схема усилителя-прототипа представлена на фиг.1. На фиг.2 показан заявляемый ДУ в соответствии с п.1 и 2 формулы изобретения. На фиг.3 представлена схема заявляемого устройства в соответствии с п.5 и 7 формулы изобретения. Частный вариант построения ДУ фиг.2, соответствующий п.6 формулы изобретения, показан на фиг.4. На фиг.5 показаны токи и напряжения ДУ фиг.2 при наличии на его входах синфазного сигнала. Эта схема используется авторами для вывода основных аналитических соотношений, поясняющих работу заявляемого устройства. На фиг.6 изображен ДУ, соответствующий п.3 формулы изобретения. Схемы исследованных авторами устройств в среде компьютерного моделирования PSpice представлены на фиг.7, 8, 10 и 11, а на фиг.9 и 12 изображены результаты их компьютерного моделирования.

Дифференциальный усилитель (фиг.2) содержит основной дифференциальный каскад 1 на первом 2 и втором 3 входных транзисторах с источником опорного тока 4 в их общей эмиттерной цепи и входами 5, 6, связанными с базами его первого 2 и второго 3 входных транзисторов, выходной каскодный усилитель на первом 7 и втором 8 выходных транзисторах, коллекторы которых связаны с первым токовым зеркалом 9, базы объединены и подключены к источнику напряжения смещения 10, а эмиттеры соединены с токовыми выходами 11 и 12 основного дифференциального каскада 1, а также с соответствующими синфазными токовыми выходами 13 и 14 управляемого по вспомогательному входу 15 второго токового зеркала 16. К основному дифференциальному каскаду 1 подключены входы дополнительного дифференциального каскада на транзисторах 17 и 18 с источником опорного тока 19 в общей эмиттерной цепи, токовые выходы которого 20, 21 соединены со вспомогательным входом 15 второго токового зеркала 16.

В дифференциальном усилителе фиг.3 объединенные токовые выходы 20, 21 дополнительного дифференциального каскада соединены со вспомогательным входом 15 второго токового зеркала 16 через дополнительный p-n-переход 22, который используется в качестве источника напряжения смещения 10 и подключен к объединенным базам первого 7 и второго 8 выходных транзисторов. Кроме этого, к эмиттерам первого 7 и второго 8 выходных транзисторов подключены дополнительные токостабилизирующие двухполюсники 23 и 24. Второе токовое зеркало 16 реализовано, в частном случае, на элементах 25-28.

В дифференциальном усилителе фиг.4 источник опорного тока 19 в общей эмиттерной цепи дополнительного дифференциального каскада на транзисторах 17 и 18 включен параллельно источнику опорного тока 4 в общей эмиттерной цепи основного дифференциального каскада 1 на первом 2 и втором 3 входных транзисторах. При таком соединении возможно использование транзисторов 2 и 17, 3 и 18 с несколькими коллекторными выводами, что упрощает топологическое описание схемы ДУ.

Схема фиг.5 полностью соответствует схеме фиг.2. Она используется авторами для расчетов.

В дифференциальном усилителе фиг.6 входы дополнительного дифференциального каскада на транзисторах 17-18 с источником опорного тока 19 в общей эмиттерной цепи соединены с источником опорного тока 4 в общей эмиттерной цепи основного дифференциального каскада 1.

На фиг.7 представлена схема ДУ-прототипа в среде компьютерного моделирования PSpice, а на фиг.8 - заявляемого ДУ, соответствующего фиг.4. На фиг.9 приведены сравнительные частотные характеристики коэффициента ослабления входных синфазных сигналов ДУ фиг.7 и 8.

На фиг.10 показана схема ДУ-прототипа в среде компьютерного моделирования PSpice, а на фиг.11 - заявляемого ДУ, соответствующего фиг.6. На фиг.12 приведены сравнительные частотные характеристики коэффициента ослабления входных синфазных сигналов ДУ фиг.10 и 11.

Рассмотрим работу заявляемого ДУ на примере анализа схемы фиг.5.

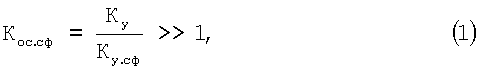

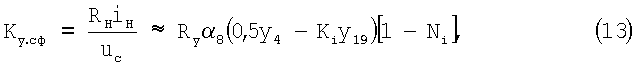

Коэффициент ослабления входного синфазного сигнала ДУ фиг.5 определяется отношением

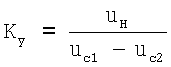

где  - коэффициент усиления дифференциального сигнала uвх;

- коэффициент усиления дифференциального сигнала uвх;

uH - выходное напряжение на нагрузке RH, обусловленное uвх;

uвх=uc1-uc2 - входной дифференциальный сигнал ДУ;

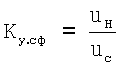

- коэффициент преобразования входного синфазного сигнала ДУ uc1=uc2=uс в выходное напряжение ДУ uH на нагрузке RH.

- коэффициент преобразования входного синфазного сигнала ДУ uc1=uc2=uс в выходное напряжение ДУ uH на нагрузке RH.

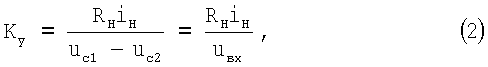

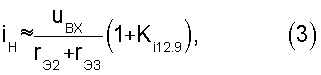

По определению

где iH - ток в нагрузке, обусловленный дифференциальным сигналом.

где rЭ2≈rЭ3 - сопротивление эмиттерного перехода транзисторов 2 и 3;

Ki12.9≈1 - коэффициент передачи по току токового зеркала 9.

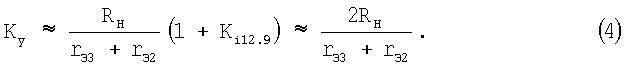

Из (2) и (3) находим

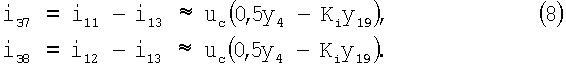

Рассмотрим далее факторы, влияющие на передачу синфазного сигнала uc со входа ДУ на его выход. Изменение uc1=uc2=uc приводит к изменению токов через выходные проводимости у19 и у4 источников опорного тока 19 и 4:

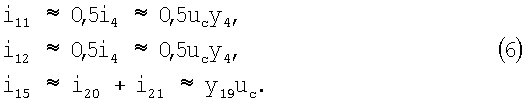

Это приводит к появлению приращений коллекторных токов транзисторов 17, 18 (i20, i21) и транзисторов 2 и 3 (i11, i12):

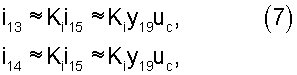

Приращение тока i15 поступает на вход 15 токового зеркала 16 и создает на его синфазных выходах 13 и 14 переменные токи

где Кi - коэффициенты передачи токового зеркала со входа 15 на выходы 13 и 14.

Поэтому у19 токи эмиттеров транзисторов 7 и 8

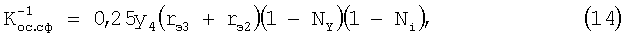

Из (8) следует, что для получения нулевых токов iэ7 и iэ8, а также нулевого тока в нагрузке iH=0, при котором Ку.сф=0 и Koc.сф=∞, необходимо, чтобы выходная проводимость источника опорного тока 19 удовлетворяла условию

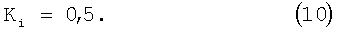

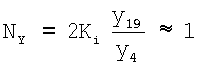

Если у4=У19, то условием получения Ку.сф≈0 и Кос.сф=∞ должно быть

следующее требование к величине коэффициента усиления по току токового зеркала 16:

В этом случае входной синфазный сигнал ДУ будет полностью подавляться и его Кос.сф=∞.

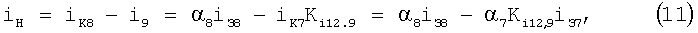

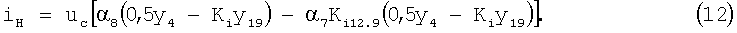

В общем случае выходной ток ДУ, обусловленный наличием на его входах 5 и 6 синфазного сигнала uc

где α7≈1, α8≈1, Ki12.9≈1 - коэффициенты передачи по току эмиттера транзисторов 7, 8 и токового зеркала 9.

Или

Следовательно, коэффициент передачи синфазного сигнала

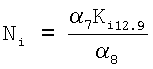

где  - коэффициент асимметрии элементов схемы ДУ.

- коэффициент асимметрии элементов схемы ДУ.

Как следствие, по сравнению с прототипом, у которого Ki=0, коэффициент ослабления входного синфазного сигнала заявляемого ДУ существенно улучшается:

где  - коэффициент асимметрии проводимостей источников опорного тока 19 и 4.

- коэффициент асимметрии проводимостей источников опорного тока 19 и 4.

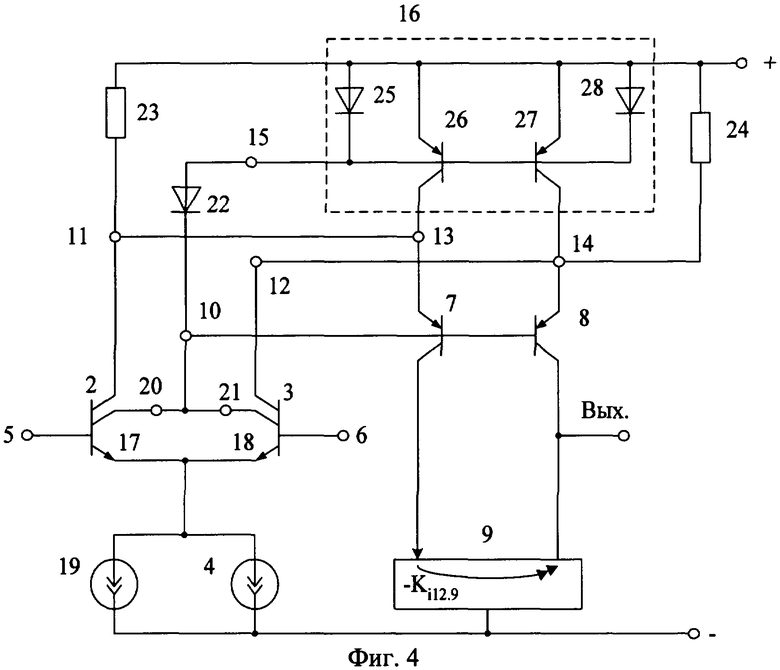

Причем, в сравнении с прототипом (фиг.1), это повышение Kос.сф достигает величины n раз:

При Ki=0,5 и одинаковых токах источников 19 и 4 NY≈1.

Практически, как показывает компьютерное моделирование, n=20÷100. Таким образом, заявляемый ДУ более эффективен при работе с синфазным сигналом.

Для обеспечения любого заданного разработчиком статического режима транзисторов ДУ могут в некоторых случаях потребоваться двухполюсники 23 и 24 (фиг.3 и 4).

Построение источника напряжения смещения 10 на основе дополнительного p-n-перехода 22 (фиг.3 и 4) уменьшает, в сравнении с прототипом (фиг.1), общее энергопотребление ДУ.

Реализация ДУ по схеме фиг.6 уменьшает входную емкость устройства, т.к. транзисторы 17 и 18 в этой схеме не связаны со входами 5 и 6.

Результаты компьютерного моделирования ДУ, представленные на графиках фиг.9 и 12, подтверждают, что заявляемое устройство имеет более высокие значения коэффициента ослабления входных синфазных сигналов.

Предлагаемый ДУ может использоваться в структуре широкополосных операционных усилителей с предельными значениями полосы пропускания в неинвертирующем включении.

Библиографический список

1. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989. - С.74, рис.4.15, с.98, рис.6. 7.

2. Патент США №6.218.900, фиг.1.

3. Патентная заявка US 2002/0196079.

4. Патент США №6.788.143.

5. Патент США №3.644.838, фиг.2.

6. Патент США №5.529.076.

7. Патент ЕР 1.227.580.

8. Патент США №6.714.076.

9. Патент США №5.786.729.

10. Патент США №5.327.100.

11. Патентная заявка US 2004/0090268 A1.

12. Патент США №4.274.061.

13. Патент США №5.422.600, фиг.2.

14. Патент США №6.788.143, фиг.2.

15. Патент США №4.959.622, фиг.1.

16. Патент США №4.406.990, фиг.4.

17. Патент США №5.418.491.

18. Патент США №6.018.268.

19. Патент США №5.952.882.

20. Патент США №4.723.111.

21. Патент США №4.293.824.

22. Патент США №6.580.325.

23. Патент США №6.965.266.

24. Патент США №6.867.643.

25. Патент США №6.236.270.

26. Патент США №5.323.121.

27. Патент США №6.229.394.

28. Патент США №5.734.296.

29. Патент США №5.477.190.

30. Патент США №5.091.701.

31. Патент США №6.717.474.

32. Патент США №6.084.475.

33. Патент США №3.733.559.

34. Патентная заявка US 2005/0001682 A1.

35. Патент США №6.300.831.

36. Патент Re 30.587.

37. Прокопенко Н.Н. Динамика микроэлектронных операционных усилителей на основе «перегнутых» каскодов /Н.Н.Прокопенко, А.С.Будяков // Известия высших учебных заведений. Северо-Кавказский регион. Технические науки. 2004. №6 - С.68-73.

| название | год | авторы | номер документа |

|---|---|---|---|

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ВХОДНЫМ СОПРОТИВЛЕНИЕМ | 2009 |

|

RU2394360C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2439784C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319291C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319294C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ СИНФАЗНОГО СИГНАЛА | 2007 |

|

RU2331968C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2455758C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2354041C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2005 |

|

RU2293433C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2374757C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННОЙ СТАБИЛЬНОСТЬЮ НУЛЕВОГО УРОВНЯ | 2010 |

|

RU2419187C1 |

Изобретение относится к радиотехнике и связи для усиления широкополосных аналоговых сигналов в аналоговых микросхемах различного функционального назначения. Технический результат заключается в повышении ослабления синфазной составляющей. Дифференциальный усилитель содержит основной дифференциальный каскад (ДК) (1) на первом (2) и втором (3) входных транзисторах (Т) с источником опорного тока (4) в их общей эмиттерной цепи и входами (5), (6), связанными с базами его первого (2) и второго (3) Т, выходной каскодный усилитель на первом (7) и втором (8) выходных Т, коллекторы которых связаны с первым токовым зеркалом (9), базы объединены и подключены к источнику напряжения смещения (10), а эмиттеры соединены с токовыми выходами (11) и (12) основного ДК (1), а также с соответствующими синфазными токовыми выходами (13) и (14) управляемого по вспомогательному входу (15) второго токового зеркала (16). К основному ДК (1) подключены входы дополнительного ДК с источником опорного тока (19) в общей эмиттерной цепи, токовые выходы которого (20), (21) соединены со вспомогательным входом (15) второго токового зеркала (16). 6 з.п. ф-лы, 12 ил.

| US 6529076 В2, 04.03.2003 | |||

| Операционный усилитель | 1984 |

|

SU1283946A1 |

| US 5786729 А, 28.07.1998 | |||

| US 5153529 А, 06.10.1992 | |||

| US 4004245, 18.01.1977. | |||

Авторы

Даты

2008-03-10—Публикация

2006-06-13—Подача