Ячейка однородной вычислительной структуры относится к вычислительной технике и может быть использована для построения однородных вычислительных структур, выполняющих параллельную логическую и арифметическую обработку данных.

Известна так же ячейка однородной структуры, авторское свидетельство SU №1501035 А2, содержащая два информационных входа 1, 2, три настроечных входа 3-5, три информационных выхода 7-8, два мультиплексора 9, 10, два элемента ИЛИ 11, 12, два элемента И, триггер 15, шесть элементов ЗАПРЕТ 16-21, элемент ИЛИ-НЕ.

Недостаток заключается в том, что обработка информации производится только в позиционной системе счисления и невозможно хранение информации в ячейке.

Из известных наиболее близким по технической сущности является ячейка однородной структуры, авторское свидетельство SU №1573456 А1, содержащая информационные входы 1-5, настроечные входы 6-8, информационные выходы 9-13, мультиплексоры 14, 15, элементы И 16-20, элементы ИЛИ 21-25, элемент ЗАПРЕТ 26-32, сумматор 33.

Предлагаемое изобретение направленно на повышение функциональных возможностей ячейки за счет реализации операции хранения и обработки информации в непозиционной системе счисления.

Это достигается тем, что в ячейку однородной вычислительной структуры, содержащей первый, второй, третий, четвертый элементы ЗАПРЕТ, первый, второй, третий, пятый, шестой элементы И, первый, второй элементы ИЛИ, дополнительно введены с целью расширения функциональных возможностей за счет реализации арифметических операций над непозиционными типами данных и возможности хранения информации первый, второй и третий триггеры, пятый, шестой элементы ЗАПРЕТ, четвертый элемент И и третий элемент ИЛИ, сумматор, первый, второй, третий, четвертый, пятый управляющие входы, первый, второй, третий информационные входы, первый, второй информационные выходы, первый управляющий выход и второй управляющий выход. Причем первый управляющий вход соединен с прямым входом первого элемента ЗАПРЕТ, с первым входом третьего элемента И, с первым инверсным входом третьего элемента ЗАПРЕТ, второй управляющий вход соединен с инверсным входом первого элемента ЗАПРЕТ, с прямым входом второго элемента ЗАПРЕТ, с инверсным входом третьего элемента ЗАПРЕТ, с входом разрешения сумматора, со вторым прямым входом четвертого элемента ЗАПРЕТ, с первым входом шестого элемента И, с третьим входом пятого элемента И, со вторым прямым входом пятого элемента ЗАПРЕТ, с первым входом четвертого элемента И, третий управляющий вход соединен с входом управления сумматора, со вторым управляющим выходом, с инверсным входом второго элемента ЗАПРЕТ, с первым входом первого элемента И, с первым входом второго элемента И, со вторым входом пятого элемента И, с третьим входом четвертого элемента И, с инверсным входом четвертого элемента ЗАПРЕТ, с инверсным входом пятого элемента ЗАПРЕТ, четвертый управляющий вход соединен с инверсным входом шестого элемента ЗАПРЕТ, с четвертым входом четвертого элемента И, пятый управляющий вход соединен с третьим входом шестого элемента И, первый информационный вход соединен со вторым входом первого элемента И, с информационным входом первого триггера, с информационным входом второго триггера, второй информационный вход соединен со вторым входом второго элемента И, с информационным входом третьего триггера, третий информационный вход соединен с входом переноса сумматора, выход первого элемента ЗАПРЕТ соединен с входом разрешения первого триггера, выход которого соединен со вторым входом третьего элемента И и с первым управляющим выходом, выход второго элемента ЗАПРЕТ соединен с входом разрешения второго триггера, выход которого соединен с первым прямым входом пятого элемента ЗАПРЕТ, со вторым входом четвертого элемента И, выход пятого элемента ЗАПРЕТ соединен с первым входом первого элемента ИЛИ, выход первого элемента И соединен со вторым входом первого элемента ИЛИ, выход которого соединен с входом первого слагаемого сумматора, выход третьего элемента ЗАПРЕТ соединен с входом разрешения третьего триггера, выход которого соединен с первым прямым входом четвертого элемента ЗАПРЕТ, выход которого соединен с первым входом второго элемента ИЛИ, выход второго элемента И соединен со вторым входом второго элемента ИЛИ, выход которого соединен с входом второго слагаемого сумматора, выход суммы которого соединен с прямым входом шестого элемента ЗАПРЕТ, с первым входом пятого элемента И, со вторым входом шестого элемента И, выход которого соединен с пятым входом третьего элемента ИЛИ, выход пятого элемента И соединен с четвертым входом третьего элемента ИЛИ, выход шестого элемента ЗАПРЕТ соединен с третьим входом третьего элемента ИЛИ, выход четвертого элемента И соединен со вторым входом третьего элемента ИЛИ, выход третьего элемента И соединен с первым входом третьего элемента ИЛИ, выход которого соединен с первым информационным выходом, выход переноса сумматора соединен со вторым информационным выходом.

Введение новых элементов и связей между ними обеспечивает решение поставленной задачи.

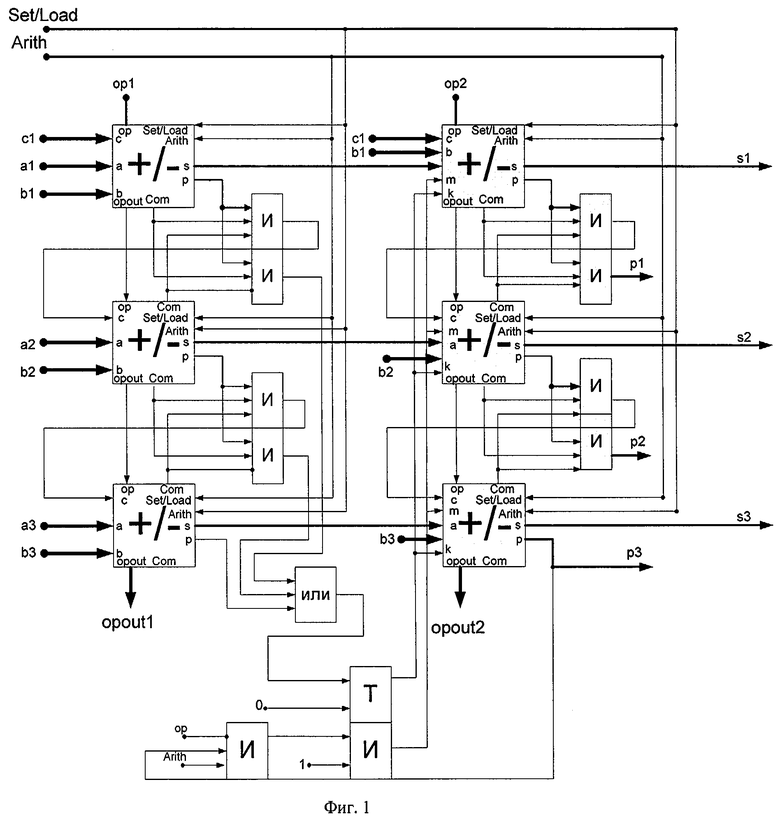

На фиг.1 представлена топология вычислительной структуры на базе ячейки однородной структуры. Устройство содержит два столбца ЯОС, информационные входы a1-a3, b1-b3 и с1 первого столбца, b1-b3 и с1 второго столбца, управляющие входы Set/Load, Arith, op1, op2, управляющие выходы opout1, opout2, информационные выходы s1-s3, схемы 2И-2И для настройки на работу с модулем требуемой разрядности и схему 2И-триггер для коррекции результата.

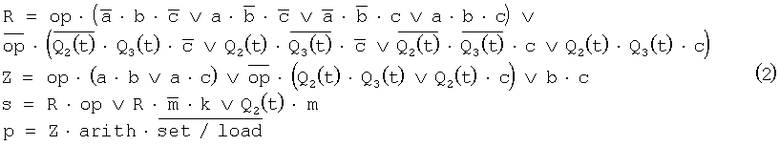

На фиг.2 представлена структурная схема ячейки однородной структуры, где 1, 2, 6, 7, 8 - управляющие входы, 3, 4, 5 - информационные входы, 9, 30 - управляющие выходы, 10, 11 - информационные выходы, 12, 13, 16, 22, 24, 27 элементы ЗАПРЕТ, 14, 15, 25, 26, 28, 29 элементы И, 20, 21, элементы ИЛИ, 17, 18, 19 - триггеры, 23 - сумматор-вычитатель.

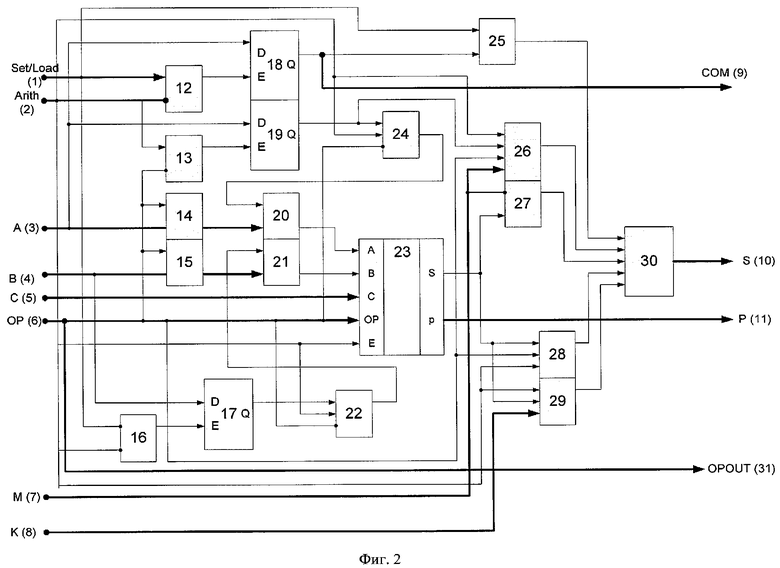

На фиг.3 представлен пример выполнения операции настройки однородной вычислительной среды на работу с данными по модулю 3.

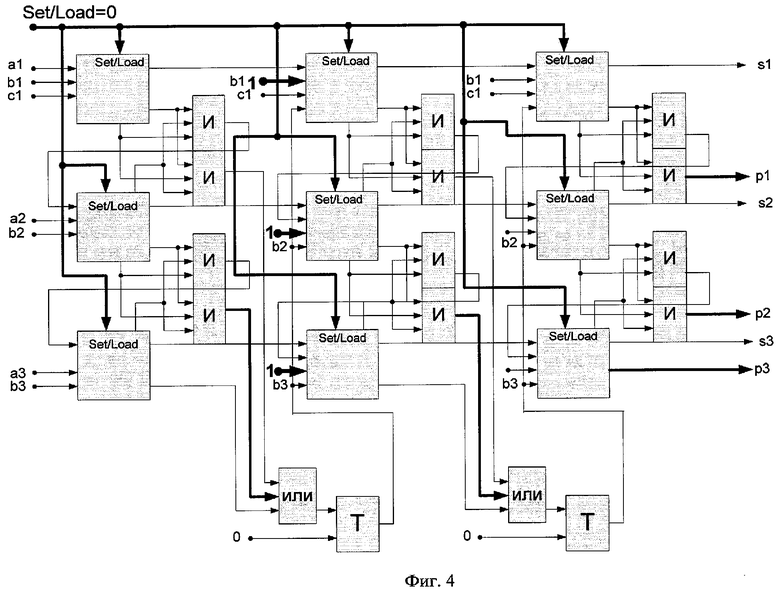

На фиг.4 представлен пример выполнения операции загрузки данных в однородную вычислительную среду, в данном примере данные загружаются в ячейки второго столбца (поток данных с входов b1-b3 второго столбца выделен жирными линиями).

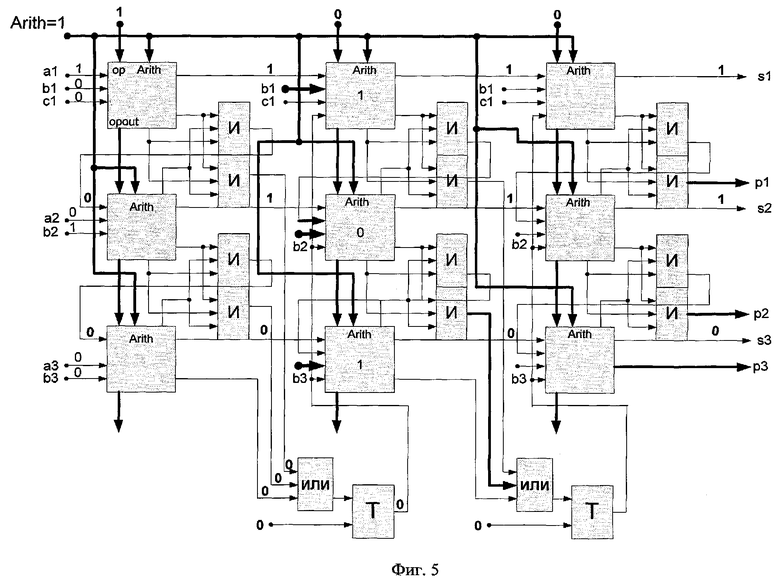

На фиг.5 представлен пример выполнения операции сложения над числами по заданному модулю и получение результата меньше модуля.

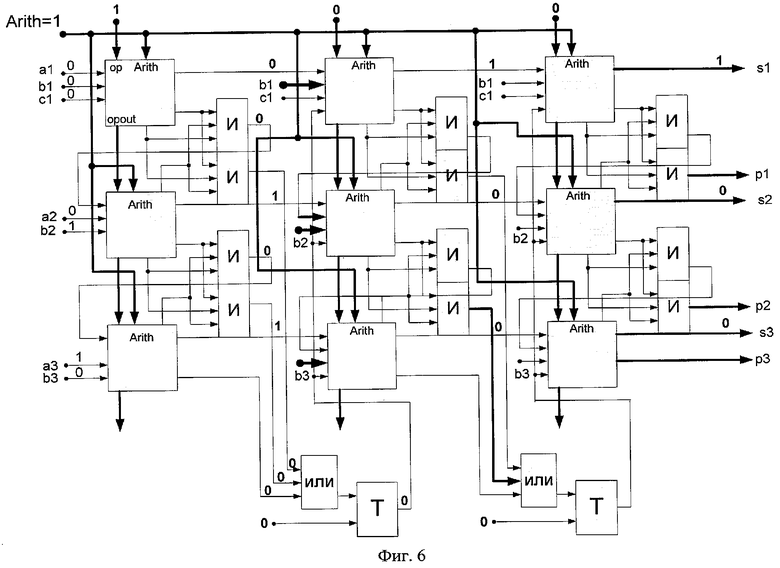

На фиг.6 представлен пример выполнения операции сложения над числами по заданному модулю и обработка результата больше модуля.

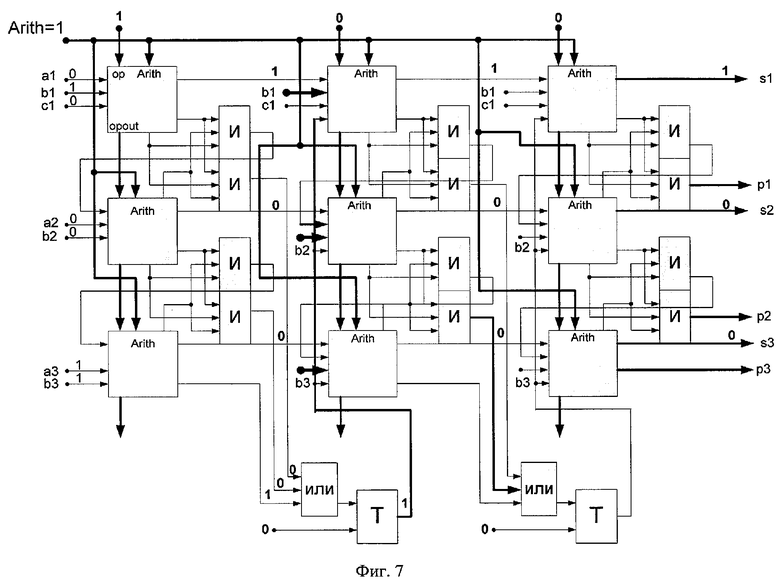

На фиг.7 представлен пример выполнения операции сложения над числами по заданному модулю, получение и обработка результата вышедшего за разрядную сетку модуля.

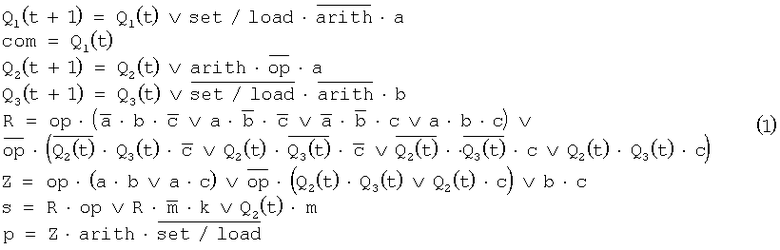

Ячейка однородной структуры реализует следующую систему логических функций:

где R и Z - соответственно значения сигналов, формируемые на выходах суммы и переноса сумматора, а, b, с - соответственно сигналы, подаваемые на одноименные 3, 4, 5 информационные входы ячейки однородной вычислительной структуры, com, op, arith, set/load - управляющие сигналы для конфигурации ЯОС на выполнение режима настройки, загрузки или выполнения арифметических операций, формируемые соответственно на 9 выходе и 6, 2, 1 управляющих входах, Q1(t+1), Q2(t+1), Q3(t+1) - соответственно состояние выходов триггеров 18, 19, 17 ячейки в момент времени t+1; Q1(t), Q2(t), Q3(1) - соответственно состояние выходов триггеров 18, 19, 17 ячейки в момент времени t, m и k - управляющие сигналы получения результата коррекции, формируются на 7 и 8 управляющих входах ячейки однородной вычислительной структуры.

Основными режимами работы ОИБ структура являются: режим настройки ЯОС, режим загрузки, режим выполнения арифметических операций.

Структура из однородных ячеек рассмотренного типа работает следующим образом.

Режим настройки ЯОС

В данном режиме решается задача настройки вычислительной среды на выполнение операции по требуемому модулю, так как количество ячеек в столбце вычислительной структуры может превышать разрядность рабочего модуля, то существует необходимость в настройке вычислительной среды на работу с конкретным модулем.

Для чего на информационные входы а первых n ячеек первого столбца, где n равно разрядности рабочего модуля, подается сигнал «1», на информационные входы а оставшихся ячеек первого столбца вычислительной матрицы подается сигнал, равный «0», на управляющий вход вычислительной структуры SET/LOAD подается активный сигнал «1», а на управляющий вход вычислительной структуры ARITH подается сигнал равный «0». В результате на выходах com ячеек столбцов сформируется управляющий сигнал, который либо перенаправит выход переноса ячейки данного столбца данной строки на вход переноса ячейки этого же столбца следующей строки через схемы управления 2И-2И ОВС, при условии, что управляющий сигнал com ячейки данного столбца данной строки и управляющий сигнал com ячейки этого же столбца следующей строки равны «1» или же выход переноса ячейки однородной структуры будет перенаправлен на вход схемы управления ИЛИ-триггер, при условии, что управляющий сигнал com ячейки следующего столбца равен «0», т.е. данная ячейка является последним разрядом обрабатываемого модуля. Заметим, что управляющий вектор хранится до следующей настройки вычислительной среды, это достигается за счет наличия в каждой ячейке триггера 18, хранящего требуемое значение Q1 управляющего сигнала com.

Система логических функций, реализуемая каждой ячейкой вычислительной структуры в данном режиме, приведена в табл.1.

Пример выполнения операции настройки приведен на фиг.3. Данный пример иллюстрирует настройку вычислительной среды на работу с данными по модулю 3. Для чего на управляющий вход SET/LOAD вычислительной среды подается активный сигнал, равный «1», который настраивает ячейки вычислительной среды на прием информации с группы информационных входов a1-an, в результате те ячейки, на информационный вход а которых подали активный сигнал, равный «1», программируются на работу с данным модулем. Так, в данном примере активными будут ячейки первых двух строк (направления управляющих и информационных сигналов выделены жирной линией).

Режим загрузки

В данном режиме решается задача загрузки в столбцы вычислительной структуры числа, биты которого размещаются в триггерах 17 ячеек столбцов ОВС.

Для настройки ОВС на данный режим работы, на управляющий вход SET/LOAD сигнал подается сигнал «0», на управляющий вход ARITH также подается сигнал «0», а на группу информационных входов b1-bn столбцов ОВС подается число, которое необходимо загрузить в ячейки столбцов ОВС.

Система логических функций, реализуемая каждой ячейкой вычислительной структуры в данном режиме, приведена в табл.2.

Пример выполнения режима загрузки показан на фиг.4. В данном примере осуществляется загрузка кода 1112 во второй столбец вычислительной структуры, для чего на группу входов b1-b3 второго столбца ОВС подаются биты вектора данных, а на управляющие входы SET/LOAD и ARITH сигнал, равный «0», в результате значение вектора считывается с группы входов b1-b3 в триггер 17 каждой ячейки второго столбца.

Режим выполнения арифметических операций.

В режиме арифметических операций возможно выполнение операции арифметического сложения чисел по заданному модулю, при этом следует учесть, что предварительно ОВС была настроена на работу по заданному модулю предыдущими режимами работы среды, т.е. произведена настройка каналов переноса pi-ci+1, через схемы 2И-2И и в ячейки второго столбца загружен код модуля, с которым будет сравниваться результат сложения.

Специфика выполнения сложения операции сложения в модулярной арифметике в том, что после выполнения операции сложения результат следует сравнить с модулем, по которому выполняется операция сложения, и если число вышло за пределы модуля, произвести коррекцию числа путем вычитания результата сложения из значения модуля, полученная разность и есть истинный результат. Если же результат сложения меньше рабочего модуля, то он принимается за окончательный результат.

Для настройки ОВС на работу в данном режиме на управляющий вход ARITH подается сигнал «1», а на управляющий вход SET/LOAD подается сигнал «0». На группу управляющих входов op1-opn подается управляющий вектор 1000...000. При этом «1» подается на управляющий вход ор первой ячейки первой строки первого столбца, на все управляющий вход ор остальных ячеек первой строки подается сигнал «0». В результате первый столбец ОВС программируется по каналам настройки opi-opouti на выполнение операции сложения, все последующие - на вычитание.

Система логических функций для выполнения арифметических операций следующая:

Данные для выполнения операции сложения поступают соответственно на группы входов a1-an и b1-bn первого столбца, при этом младшие биты данных поступают на входы а и b самой первой ячейки первой строки, первого столбца. В результате на группе выходов s1-sn первого столбца формируется сумма, а на группе выходов p1-pn первого столбца формируется значение переноса. Полученное значение суммы поступает на группу входов a1-an второго столбца и является уменьшаемым. Далее возможно три варианта работы ОВС:

1. Результат сложения меньше модуля и является истинным результатом.

2. Результат сложения больше модуля, но не больше разрядной сетки модуля, и в данном случае необходима коррекция результата, и результат коррекции является истинным результатом.

3. Результат сложения больше модуля и больше разрядной сетки модуля, и в данном случае необходима коррекция результата с учетом выхода результата за разрядную сетку, о данном факте сигнализирует «1» с выхода переноса р самой нижней «активной» ячейки работы по данному модулю ОВС. Результат коррекции является истинным результатом.

Рассмотрим примеры всех трех возможных вариантов работы вычислительной среды.

Вариант 1. Представлен на фиг.5. Результат меньше модуля и является истинным результатом.

Операнды А=110=0012, В=210=0102. Операции в данном примере выполняются по модулю 510. Первая стадия - сложение А с В и получение промежуточного результата А+В=0112. Данная стадия производится в первом столбце ОВС, для чего на входы a1-а3 и b1-b3 первого столбца подаются первое и второе слагаемое соответственно, при этом самые младшие биты слагаемых подаются на входы а и b первой ячейки первой строки первого столбца соответственно. Вторая стадия - сравнение полученного на группе выходов s1-s3 первого столбца результата сложения с модулем, сохраненным в триггере 17 ячеек второго столбца вычислительной структуры. Сравнение осуществляется путем вычитания результата операции сложения и модуля: (А+В)-М, (А+В)-М=1112. При этом вычитаемое поступило на группу входов a1-а3 второго столбца с группы выходов s1-s3 первого столбца. Заметим, что вычитаемое поступило не только на вход первого слагаемого сумматора ячеек второго столбца, но и было сохранено в триггере 19 ячеек второго столбца. Заем в старшем разряде вычитаемого говорит, что вычитаемое меньше вычитателя и полученный результат является отрицательным числом, в результате формируется управляющий сигнал М, подаваемый по группе входов m1-mn в каждую ячейку второго столбца. Из полученного результата делается вывод, что А+В является истинным результатом и с триггеров 19 ЯОС ОВС второго столбца код А+В=0112 подается на выходы s1-sn вычислительной структуры.

Вариант 2. Представлен на фиг.5. Результат больше модуля, но не больше разрядной сетки модуля, и в данном случае необходима коррекция результата, и результат коррекции является истинным результатом.

Операнды А=410=1002, B=210=0102. Первая стадия - сложение А с В и получение промежуточного результата А+В=1102. Данная стадия производится в первом столбце ОВС, для чего на входы a1-а3 и b1-b3 первого столбца подаются первое и второе слагаемое соответственно, при этом самые младшие биты слагаемых подаются на входы а и b первой ячейки первой строки первого столбца соответственно. Вторая стадия - сравнение полученного результата с модулем, сохраненным во втором столбце вычислительной структуры. Сравнение осуществляется путем вычитания результата операции сложения и модуля и производится во втором столбце (А+В)-М, (А+В)-М=0012. При этом вычитаемое поступило на группу входов a1-а3 второго столбца с группы выходов s1-s3 первого столбца. Заметим, что вычитаемое поступило не только на вход первого слагаемого сумматора ячеек второго столбца, но и было сохранено в триггере 19 ячеек второго столбца. Заем в старшем разряде вычитаемого отсутствует, отсюда управляющий сигнал m находится в пассивном состоянии и равен «0», что показывает: вычитаемое больше вычитателя и полученный результат с выходов суммы сумматоров ячеек второго столбца является положительным числом и результатом операции сложения и подается на выходы s1-sn вычислительной структуры.

Вариант 3. Представлен на фиг.6. Результат больше модуля и больше разрядной сетки модуля, и в данном случае необходима коррекция результата, с учетом выхода результата за разрядную сетку. Результат коррекции является истинным результатом.

Операнды А=410=1002, В=510=1012. Первая стадия - сложение А с В и получение промежуточного результата А+В=10012, для чего на входы a1-а3 и b1-b3 первого столбца подаются первое и второе слагаемое соответственно, при этом самые младшие биты слагаемых подаются на входы а и b первой ячейки первой строки первого столбца соответственно, заметим, что произошел выход результата за разрядную сетку модуля, о чем сигнализирует «1» на выходе переноса p самой нижней активной ячейки работы по данному модулю (в данном примере - третьей) первого столбца, которая поступает на схему коррекции ИЛИ - триггер. Вторая стадия - сравнение полученного результата с модулем, сохраненным во втором столбце вычислительной структуры. Сравнение осуществляется путем вычитания результата операции сложения и модуля: А+В-М, (А+В)-М=1002. При этом вычитаемое поступило на группу входов a1-а3 второго столбца с группы выходов s1-s3 первого столбца. Заметим, что вычитаемое поступило не только на вход первого слагаемого сумматора ячеек второго столбца, но и было сохранено в триггере 19 ячеек второго столбца. При выполнении вычитания произошел заем в старшем разряде вычитаемого, но при сложении было переполнение разрядной сетки, в результате был активизирован управляющий сигнал К, который показал, что, несмотря на заем при вычитании из старшего разряда и установлении в активное состояние сигнала М, истинным результатом является А+B=1002, и именно эти данные поступают на выходы s1-s3 OBC.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЯЧЕЙКА ОДНОРОДНОЙ СТРУКТУРЫ | 2005 |

|

RU2295147C1 |

| ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СТРУКТУРА ДЛЯ ВЫПОЛНЕНИЯ ОПЕРАЦИЙ ПО ЗАДАННОМУ МОДУЛЮ | 2005 |

|

RU2310223C2 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ, ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА И УСТРОЙСТВО ДЛЯ КОНВЕЙЕРНЫХ АРИФМЕТИЧЕСКИХ ВЫЧИСЛЕНИЙ ПО ЗАДАННОМУ МОДУЛЮ | 2011 |

|

RU2477513C1 |

| Ячейка однородной структуры | 1988 |

|

SU1573456A1 |

| Ячейка однородной структуры | 1990 |

|

SU1805461A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| ЯЧЕЙКА ОДНОРОДНОЙ СТРУКТУРЫ | 2004 |

|

RU2285285C2 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ, ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА И УСТРОЙСТВО ДЛЯ КОНВЕЙЕРНЫХ ВЫЧИСЛЕНИЙ СУММЫ м n-РАЗРЯДНЫХ ЧИСЕЛ | 2011 |

|

RU2475815C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 1993 |

|

RU2043650C1 |

| Арифметическое устройство | 1984 |

|

SU1229754A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения однородных вычислительных структур, выполняющих параллельную логическую и арифметическую обработку данных. Техническим результатом является расширение функциональных возможностей устройства за счет реализации операции хранения и обработки информации в непозиционной системе счисления. Устройство содержит шесть элементов ЗАПРЕТ, шесть элементов И, три элемента ИЛИ, три триггера, сумматор-вычитатель, управляющие и информационные входы и выходы. 7 ил., 2 табл.

Ячейка однородной вычислительной структуры для выполнения логических и арифметических операций, содержащая первый, второй, третий, четвертый элементы ЗАПРЕТ, первый, второй, третий, пятый, шестой элементы И, первый, второй элементы ИЛИ, отличающаяся тем, что она содержит первый, второй и третий триггеры, пятый, шестой элементы ЗАПРЕТ, четвертый элемент И и третий элемент ИЛИ, сумматор, первый, второй, третий, четвертый, пятый управляющие входы, первый, второй, третий информационные входы, первый, второй информационные выходы, первый управляющий выход и второй управляющий выход, причем первый управляющий вход соединен с прямым входом первого элемента ЗАПРЕТ, с первым входом третьего элемента И, с первым инверсным входом третьего элемента ЗАПРЕТ, второй управляющий вход соединен с инверсным входом первого элемента ЗАПРЕТ, с прямым входом второго элемента ЗАПРЕТ, с инверсным входом третьего элемента ЗАПРЕТ, с входом разрешения сумматора, со вторым прямым входом четвертого элемента ЗАПРЕТ, с первым входом шестого элемента И, с третьим входом пятого элемента И, со вторым прямым входом пятого элемента ЗАПРЕТ, с первым входом четвертого элемента И, третий управляющий вход соединен с входом управления сумматора, со вторым управляющим выходом, с инверсным входом второго элемента ЗАПРЕТ, с первым входом первого элемента И, с первым входом второго элемента И, со вторым входом пятого элемента И, с третьим входом четвертого элемента И, с инверсным входом четвертого элемента ЗАПРЕТ, с инверсным входом пятого элемента ЗАПРЕТ, четвертый управляющий вход соединен с инверсным входом шестого элемента ЗАПРЕТ, с четвертым входом четвертого элемента И, пятый управляющий вход соединен с третьим входом шестого элемента И, первый информационный вход соединен со вторым входом первого элемента И, с информационным входом первого триггера, с информационным входом второго триггера, второй информационный вход соединен со вторым входом второго элемента И, с информационным входом третьего триггера, третий информационный вход соединен с входом переноса сумматора, выход первого элемента ЗАПРЕТ соединен с входом разрешения первого триггера, выход которого соединен со вторым входом третьего элемента И и с первым управляющим выходом, выход второго элемента ЗАПРЕТ соединен с входом разрешения второго триггера, выход которого соединен с первым прямым входом пятого элемента ЗАПРЕТ, со вторым входом четвертого элемента И, выход пятого элемента ЗАПРЕТ соединен с первым входом первого элемента ИЛИ, выход первого элемента И соединен со вторым входом первого элемента ИЛИ, выход которого соединен с входом первого слагаемого сумматора, выход третьего элемента ЗАПРЕТ соединен с входом разрешения третьего триггера, выход которого соединен с первым прямым входом четвертого элемента ЗАПРЕТ, выход которого соединен с первым входом второго элемента ИЛИ, выход второго элемента И соединен со вторым входом второго элемента ИЛИ, выход которого соединен с входом второго слагаемого сумматора, выход суммы которого соединен с прямым входом шестого элемента ЗАПРЕТ, с первым входом пятого элемента И, со вторым входом шестого элемента И, выход которого соединен с пятым входом третьего элемента ИЛИ, выход пятого элемента И соединен с четвертым входом третьего элемента ИЛИ, выход шестого элемента ЗАПРЕТ соединен с третьим входом третьего элемента ИЛИ, выход четвертого элемента И соединен со вторым входом третьего элемента ИЛИ, выход третьего элемента И соединен с первым входом третьего элемента ИЛИ, выход которого соединен с первым информационным выходом, выход переноса сумматора соединен со вторым информационным выходом.

| Ячейка однородной структуры | 1988 |

|

SU1573456A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ СТРУКТУРЫ | 1993 |

|

RU2036511C1 |

| ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА С ДВУСЛОЙНОЙ ПРОГРАММИРУЕМОЙ СТРУКТУРОЙ | 1998 |

|

RU2134448C1 |

| Ячейка однородной структуры | 1988 |

|

SU1501035A2 |

| US 6154053 A, 28.11.2000. | |||

Авторы

Даты

2007-06-10—Публикация

2005-10-17—Подача