Изобретение относится к вычислительной технике и может быть использовано для построения конвейерных средств обработки.

Цель изобретения увеличение производительности в конвейерном рв «йме работы.

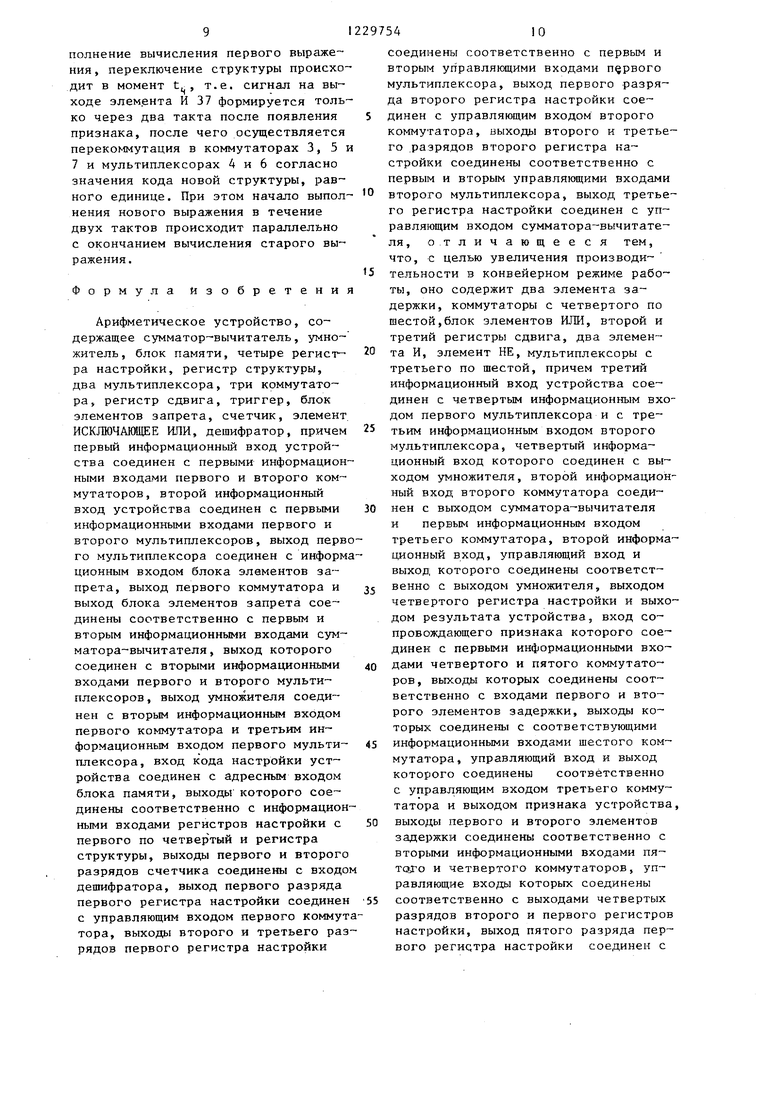

На фиг. 1 представлена схема арифметического устройства; на фиг. 2 - временная диаграмма работы.

Арифметическое устройство содержит сумматор-вычитатель 1, умножител 2, коммутатор 3, мультиплексор 4, коммутатор 5, мультиплексор 6, коммутаторы 7-10, выход 11 результата, элементы 1-2 и 13 задержки, .выход 14 признака, блок 15 элементов запрета, блок 16 элементов ИЛИ, вход 17 кода настройки, блок 18 памяти, регистры 19-22 настройки, регистр 23 структуры, регистры 24-26 сдвига, счетчик 27,дешифратор 28, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 29, мультиплексоры 30-33, триггер 34, элемент ИЛИ 35, элементы И 36 и 37, элемент НЕ 38, информационные входы 39-41, вход 42 сопровождающего признака, вход 43 разрешения настройки, вход 44 окончания настройки, входы 45 и 46 модифицирующих признаков, выход 47 типлексора 31, выходы 48-51 разрядов мультиплексора 30, входы 52 и 53 сумматора-вычитателя 1, выходы 54 и 55 умножителя 2, выход 56 мультиплексора 32.

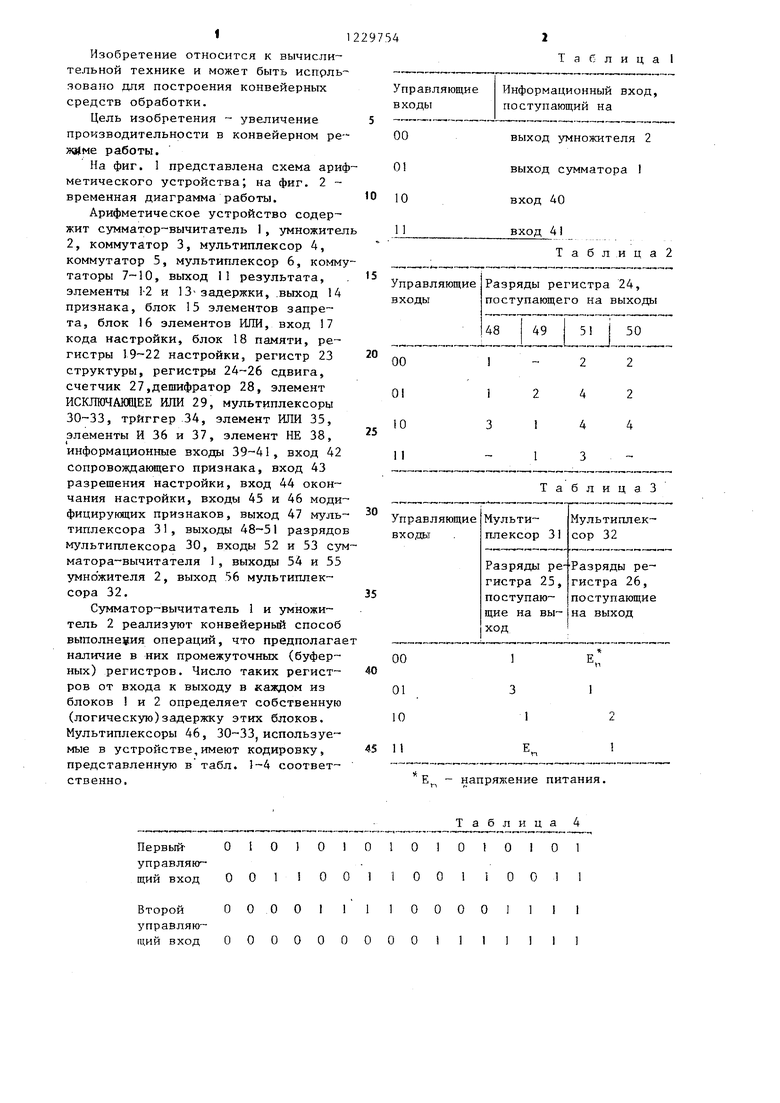

Сумматор-вычитатель 1 и умножитель 2 реализуют конвейерный способ выполнения операций, что предполагае наличие в них промежуточных (буферных) регистров. Число таких регистров от входа к выходу в каждом из блоков и 2 определяет собственную (логическую)задержку этих блоков. Мультиплексоры 46, 30-33, используемые в устройстве,имеют кодировку, представленную в табл. 1-4 соответственно.

0101010101010101

001 1001

001 1001 1 00001111

0000 I

001 1001 0000111

0000000001 1 1 1 1 I

Таблица I

Таблица2

Т а б л и ц а 3

Управляющие входы

Мультиплексор 31

Мультиплексор 32

Разряды регистра 25, поступающие на выход

Разряды регистра 26, поступающие на выход

00 40

01 10

45 П

Е напряжение питания.

Таблица

001 1001 1 00001111

Информационный вход поступающий на выход

Е.

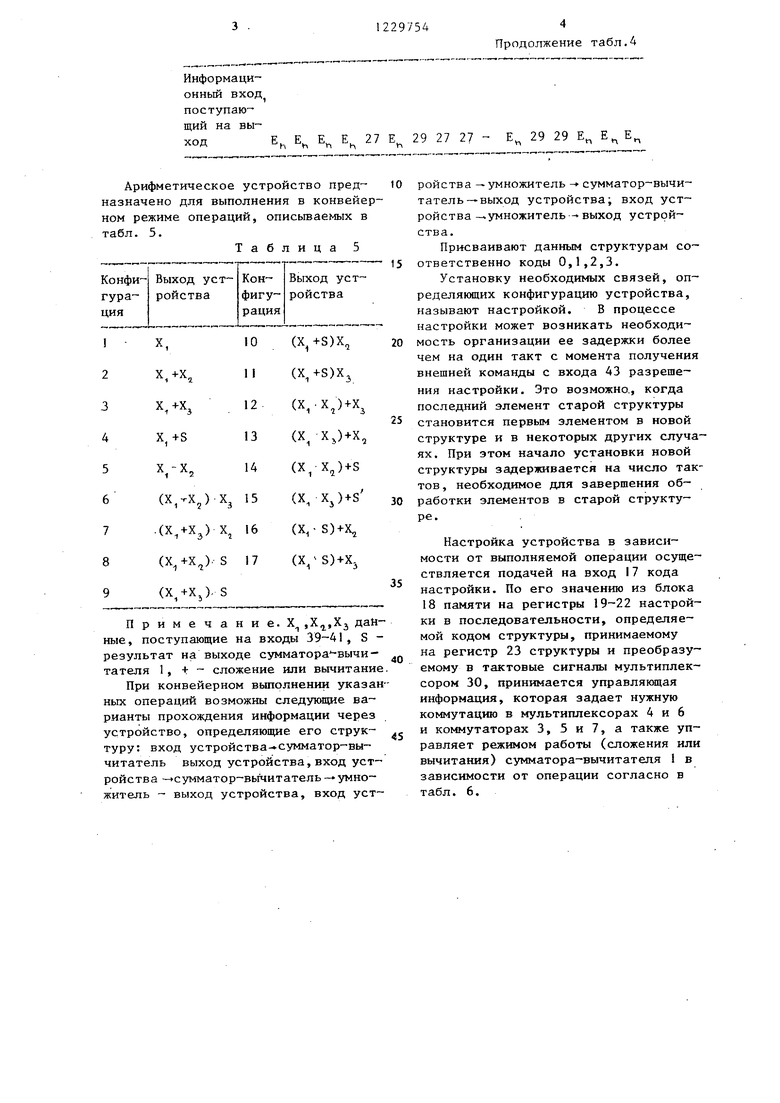

Арифметическое устройство предназначено для выполнения в конвейерном режиме операций, описьгоаемых в табл. 5.

Таблица 5

Примечание. Х,X,X данные, поступающие на входы 39-41, S - результат на выходе сумматора -вычи- тателя 1, + - сложение или вычитание.

При конвейерном выполнении указанных операций возможны следующие варианты прохождения информации через устройство, определяющие его структуру: вход устройства- сумматор-вы- читатель выход устройства, вход устройства - сумматор-вьгчитатель-«умножитель - выход устройства, вход уст-

Продолжение табл.А

Е 29 27 27 Е 29 29 Е

10

15

20

25

30

5

0

S

роиства - умножитель - сумматор-вычи- татель-выход устройства; вход устройства - умножитель-выход устройства.

Присваивают данным структурам соответственно коды 0,1,2,3.

Установку необходимых связей, определяющих конфигурацию устройства, называют настройкой, В процессе настройки может возникать необходимость организации ее задержки более чем на один такт с момента получения внешней команды с входа 43 разрешения настройки. Это возможно., когда последний элемент старой структуры становится первым элементом в новой структуре и в некоторых других случаях. При этом начало установки новой структуры задерживается на число тактов, необходимое для завершения обработки элементов в старой структуре.

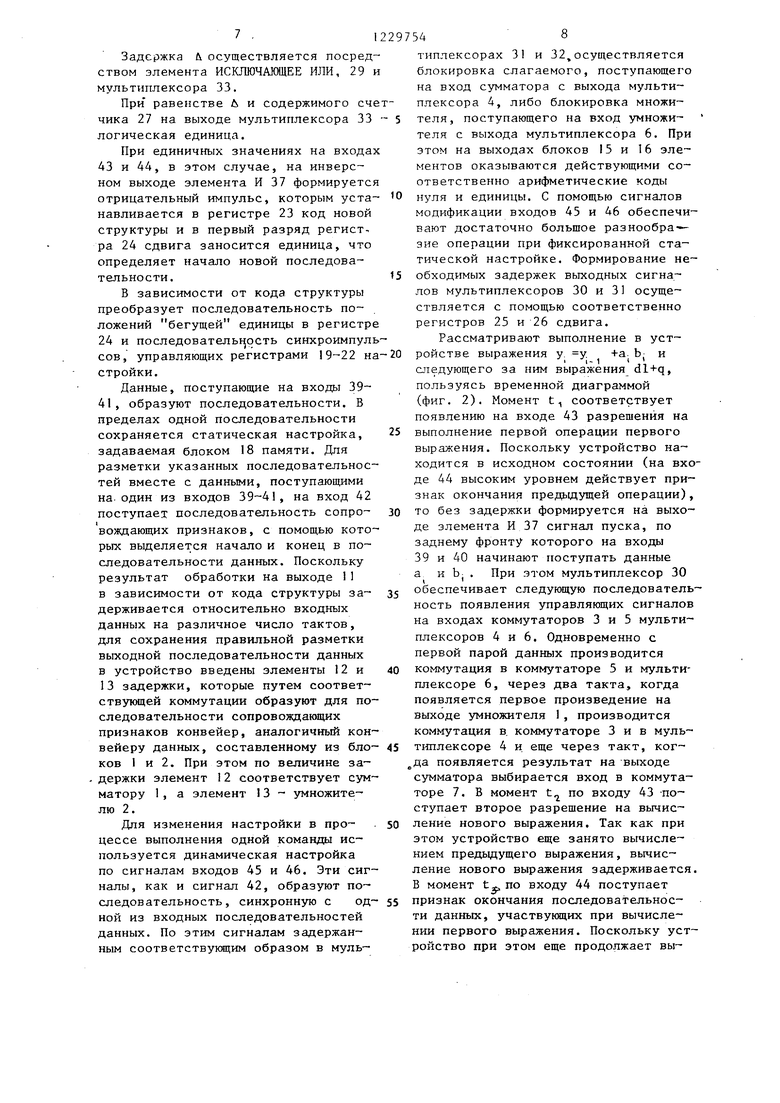

Настройка устройства в зависимости от выполняемой операции осуществляется подачей на вход I7 кода настройки. По его значению из блока 18 памяти на регистры 19-22 настройки в последовательности, определяемой кодом структуры, принимаемому на регистр 23 структуры и преобразуемому в тактовые сигналы мультиплексором 30, принимается управляющая информация, которая задает нужную коммутацию в мультиплексорах 4 и 6 и коммутаторах 3, 5 и 7, а также управляет режимом работы (сложения или вычитания) сумматора-вычитателя 1 в зависимости от операции согласно в табл. 6.

Сумматор 1

12297546

Таблицаб Умножитель 2

Выход 1

Вход 52 I Вход 53

2 3 4 5 6 7 8 9

10 1 I 12 13 14 15 16 17

М - результат на выходе умножителя 2.

Предлагаемую настройку называют димость в задержке перестройки, статической.45 Значение задержек ь приведены в

При переходу от старой струк- табл.7.

туры к новой возникает необхо Таблица 7

Код старой

структуры 0000

Код новой структуры

1 1 122223333 0123012301230123

О О О О L, О

Примечание, )- собственная задержка соответственно сумматора-вычитателя и умножителя.

ицаб

Выход 1

Вход 54 I Вход 55

S S Ч г, О S О О О О

Задержка & осуществляется посредством элемента ИСКЛЮЧАЩЕЕ ИЛИ, 29 и мультиплексора 33,

При равенстве U и содержимого счечика 27 на выходе мультиплексора 33 логическая единица.

При единичных значениях на входах 43 и 44, в этом случае, на инверсном выходе элемента И 37 формируется отрицательный импульс, которым уста- навливается в регистре 23 код новой структуры и в первый разряд регистра 24 сдвига заносится единица, что определяет начало новой последовательности.

В зависимости от кода структуры преобразует последовательность положений бегущей единицы в регистре 24 и последователь ость синхроимпульсов, управляющих регистрами 19-22 на стройки.

Данные, поступающие на входы 39- 41, образуют последовательности. В пределах одной последовательности сохраняется статическая настройка, задаваемая блоком 18 памяти. Для разметки указанных последовательностей вместе с данными, поступающими на. один из входов 39-41, на вход 42 поступает последовательность сопро- вождающих признаков, с помощью которых выделяется начало и конец в последовательности данных. Поскольку результат обработки на выходе 11 в зависимости от кода структуры за- держивается относительно входных данных на различное число тактов, для сохранения правильной разметки выходной последовательности данных в устройство введены элементы 12 и 13 задержки, которые путем соответствующей коммутации образуют для последовательности сопровождающих признаков конвейер, аналогичный кон вейеру данных, составленному из бло- ков 1 и 2. При этом по величине задержки элемент 12 соответствует сумматору 1, а элемент I3 - умножителю 2.

Для изменения настройки в про- . цессе выполнения одной команды используется динамическая настройка по сигналам входов 45 и 46. Эти сигналы, как и сигнал 42, образуют последовательность, синхронную с од- ной из входных последовательностей данных. По этим сигналам задержанным соответствукяцим образом в муль5

5

О 5

0

типлексорах 31 и 32,осуществляется блокировка слагаемого, поступающего на вход сумматора с выхода мультиплексора 4, либо блокировка множителя, поступающего на вход умножителя с выхода мультиплексора 6. При этом на выходах блоков 15 и 16 элементов оказываются действующими соответственно арифметические коды нуля и единицы. С помощью сигналов модификации входов 45 и 46 обеспечивают достаточно большое разнообразие операции при фиксированной статической настройке. Формирование необходимых задержек выходных сигналов мультиплексоров 30 и 3 осуществляется с помощью соответственно регистров 25 и 26 сдвига.

Рассматривают выполнение в устройстве выражения у. у. +а. bj и следующего за ним выражения dl+q, пользуясь временной диаграммой (фиг. 2). Момент t, соответствует появлению на входе 43 разрешения на выполнение первой операции первого выражения. Поскольку устройство находится в исходном состоянии (на входе 44 высоким уровнем действует признак окончания предьщущей операции), то без задержки формируется на выходе элемента И 37 сигнал пуска, по заднему фронту которого на входы 39 и 40 начинают поступать данные а и bj . При этом мультиплексор 30 обеспечивает следующую последовательность появления управляющих сигналов на входах коммутаторов 3 и 5 мультиплексоров 4 и 6. Одновременно с первой парой данных производится коммутация в коммутаторе 5 и мультиплексоре 6, через два такта, когда появляется первое произведение на выходе умножителя 1, производится коммутация в, коммутаторе 3 и в мультиплексоре 4 и. еще через такт, ког- да появляется результат на выходе сумматора выбирается вход в коммутаторе 7. В момент t по входу 43 -поступает второе разрешение на вычисление нового выражения. Так как при этом устройство еще занято вычислением предыдущего выражения, вычисление нового выражения задерживается. В момент t по входу 44 поступает признак окончания последовательности данных, участвующих при вычислении первого выражения. Поскольку устройство при этом еще продолжает выполнение вычисления первого вырсцке- ния, переключение структуры происходит в момент t, т.е. сигнал на выходе элемента И 37 формируется только через два такта после появления признака, после чего осуществляется перекоммутация в коммутаторах 3, 5 7 и мультиплексорах 4 и 6 согласно значения кода новой структуры, равного единице. При этом начало выпол нения нового выражения в течение двух тактов происходит параллельно с окончанием вычисления старого выражения.

Формула Изобретени

Арифметическое устройство, содержащее сумматор-вычитатель, умножитель , блок памяти, четыре регист- ра настройки, регистр структуры, два мультиплексора, три коммутатора, регистр сдвига, триггер, блок элементов запрета, счетчик, элемент ИСКЛЮЧАЩЕЕ ИЛИ, дешифратор, причем первый информационный вход устройства соединен с первыми информационными входами первого и второго коммутаторов, второй информационный вход устройства соединен с первыми информационными входами первого и второго мультиплексоров, выход первго мультиплексора соединен с информционным входом блока элементов запрета, выход первого коммутатора и выход блока элементов запрета соединены соответственно с первым и вторым информационными входами сум- матора-вычитателя, выход которого соединен с вторыми ин4юрмационными входами первого и второго мультиплексоров , выход умножителя соединен с вторым информационным входом первого коммутатора и третьим информационным входом первого мульти- плексора, вход кода настройки устройства соединен с адресным входом блока памяти, выходы которого соединены соответственно с информационными входами регистров настройки с первого по четвертый и регистра структуры, выходы первого и второго разрядов счетчика соединены с входо дешифратора, выход первого разряда первого регистра настройки соединен с управляющим входом первого коммуттора, выходы второго и третьего разрядов первого регистра настройки

соединены соответственно с первым и вторым управляющими входами первого мультиплексора, выход первого разряда второго регистра настройки соединен с управляющим входом второго коммутатора, выходы второго и третьего разрядов второго регистра настройки соединены соответственно с первым и вторым управляющими входами второго мультиплексора, выход третьего регистра настройки соединен с управляющим входом сумматора-вычитате- ля, отличающееся тем, что, с целью увеличения производительности в конвейерном режиме работы, оно содержит два элемента задержки, коммутаторы с четвертого по шестой,блок элементов ИЛИ, второй и третий регистры сдвига, два элемента И, элемент НЕ, мультиплексоры с третьего по шестой, причем третий информационный вход устройства соединен с четвертым информационным входом первого мультиплексора и с третьим информационным входом второго мультиплексора, четвертый информационный вход которого соединен с выходом умножителя, второй информационный вход второго коммутатора соединен с выходом сумматора-вычитателя и первым информационньпу входом третьего коммутатора, второй информационный вход, управляющий вход и выход которого соединены соответственно с выходом умножителя, выходом четвертого регистра настройки и выходом результата устройства, вход сопровождающего признака которого соединен с первыми информационными входами четвертого и пятого коммутаторов , выходы которых соединены соответственно с входами первого и второго элементов задержки, выходы которых соединены с соответствующими информационными входами шестого коммутатора, управляющий вход и выход которого соединены соответственно с управляющим входом третьего коммутатора и выходом признака устройства выходы первого и второго элементов задержки соединены соответственно с вторыми информационными входами пя- тсгго и четвертого коммутаторов, управляющие входы которых соединены соответственно с выходами четвертых разрядов второго и первого регистров настройки, выход пятого разряда первого регистра настройки соединен с

ч

первым входом элемента ИЛИ, выход которого соединен с управляющим входом блока элементов запрета, выход второго мультиплексора соединен с ин формационным входом блока элементов ИЛИ, выход которого и выход второго коммутатора соединены соответственно с входами множителя и множимого умножителя, выходы разрядов регистра структуры соединены с соответствующими управляющими входами третьего мультиплексора, информационные входы которого соединены с выходами соответствующих разрядов первого регистра сдвига, выхода разрядов третьего мультиплексора соединены с так -товыми входами соответствующих регистров настройки, выходы первого и второго разрядов регистра структура соединень с соответствующими управляющими входами четвертого и пятого мультиплексоров, информационные входы которых соединены соответственно с выходами разрядов второго и третьего регистров сдвига, входы которых являются соответственно первым и вторым входами модифицирующих при знаков устройства, выходы четвертого и пятого мультиплексоров соединены соответственно с вторым входом элемента ИЛИ и с управляющим входом

2Ч7т412

блока элементов ИЛИ, вход окончания пастроИки устройства соединен с первым входом первого элемента И и входом разрешения счета счетчика, вход

5 запрета счета которого соединен с (га-)-м выходом дешифратора (т - модуль счета), выходы первого и второго разрядов счетчика соединены с соответствующими входами элемента ИС- to КЛЮЧАЩЕЕ ИЛИ, выход которого и выход первого разряда счетчика соединены соответственно с первым и вторым информационными входами шестого мультиплексора, первый и второй

15 управляющие входы которого соединены соответственно с выходом и информационным входом регистра структуры, выход шестого мультиплексора соединен с вторым входом первого элемен20 та И, выход которого соединен с входом триггера и первым входом второго элемента И, второй вход и инверсный выход которого соединены соответственно с выходом триггера и тактовым

25 входом регистра структуры, вход первого регистра сдвига через элемент НЕ соединен с инверсным выходом второго элемента И, третий вход первого элемента И является

30 входом разрешения настройки устройства .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации быстрого преобразования Фурье | 1988 |

|

SU1672468A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1989 |

|

SU1667065A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1988 |

|

SU1640709A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Устройство для умножения чисел | 1986 |

|

SU1325475A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Устройство для вычисления свертки | 1989 |

|

SU1654835A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения конвейерных средств обработки информации. Цель изобретения - увеличение производительности в конвейерном режиме работы. Сущность изобретения состоит в том, что устройство, содержащее сумматор, умножитель, три буферных регистра, два мультиплексора, дополнительно содержит шесть мультиплексоров, два блока задержки, четыре регистра настройки, регистр кода структуры, три сдвигающих регистра, счетчик задержки настройки, дешифратор модуля счета, триггер, формирователь кода задержки начала настройки, блок настроечной последовательности, два блока модифициргующих последовательностей, схему сравнения, схему блокировки слагаемого , схему блокировки множителя, вентиль И, вентиль ИЛИ, вентиль И-НЕ, инвертор и накопитель настроек с отличительными связями. 2 ил. S Ю ю со 01 4ib

Л

ij

фиг. 2

Редактор М.Бианар Заказ 2450/48

Составитель А.Клюев Техред О.Гортвай

Корректор С.Шекмар

Тираж 671 . Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, , Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. .Ужгород, ул. Проекч ная,

Корректор С.Шекмар

| Вычислительное устройство | 1981 |

|

SU1016779A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Регулятор для вертикальных ветряных двигателей | 1925 |

|

SU2060A1 |

| Транспортер для перевозки товарных вагонов по трамвайным путям | 1919 |

|

SU102A1 |

| М, 1977, с | |||

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

Авторы

Даты

1986-05-07—Публикация

1984-01-20—Подача