Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов с широким динамическим диапазоном, в структуре аналоговых микросхем различного функционального назначения (например, быстродействующих операционных усилителях (ОУ)).

Известны схемы дифференциальных усилителей (ДУ) на n-р-n и р-n-р транзисторах с так называемой «архитектурой входного каскада операционного усилителя μА741» [1-30]. На их модификации выдано более 50 патентов для ведущих микроэлектронных фирм мира. Дифференциальные усилители данного класса, наряду с типовым параллельно-балансным каскадом [29-30], стали основным усилительным элементом многих аналоговых интерфейсов. Предлагаемое изобретение относится к данному подклассу устройств.

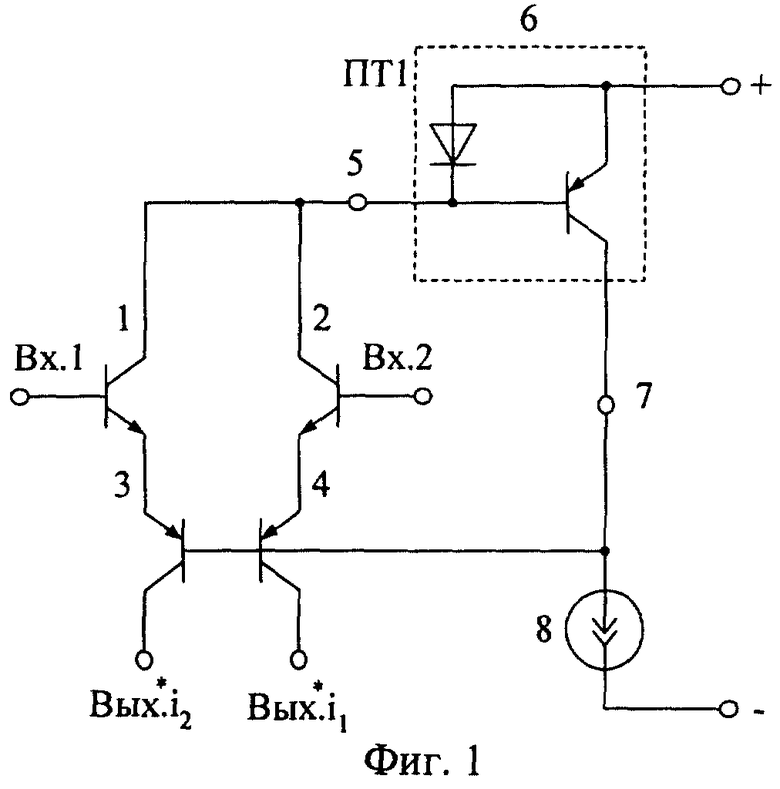

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте США № 3660773, а также в [1-14], содержащий первый 1 и второй 2 входные транзисторы, эмиттеры которых соединены с соответствующими эмиттерами первого 3 и второго 4 выходных транзисторов противоположного типа проводимости, базы которых соединены, причем коллектор первого 1 входного транзистора соединен со входом 5 токового зеркала 6, коллекторный выход которого 7 связан с первым источником опорного тока 8.

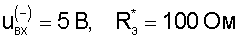

Существенный недостаток известного ДУ состоит в том, что он имеет сравнительно узкий динамический диапазон линейного усиления сигналов (uвх<Uгр≈100÷150 мВ), а также повышенное энергопотребление. Последнее обстоятельство связано с тем, что ДУ фиг.1 включает токовую ветвь (ПТ1 - I8), которая не участвует в усилении дифференциальных сигналов, т.к. служит только для установления статического режима ДУ. Кроме этого известный ДУ характеризуется небольшим коэффициентом ослабления синфазного сигнала (Кос.сф).

Основная цель предлагаемого изобретения состоит в расширении диапазона активной работы ДУ. Дополнительная цель - повышение коэффициента усиления дифференциального сигнала без ухудшения энергопотребления и повышение Кос.сф.

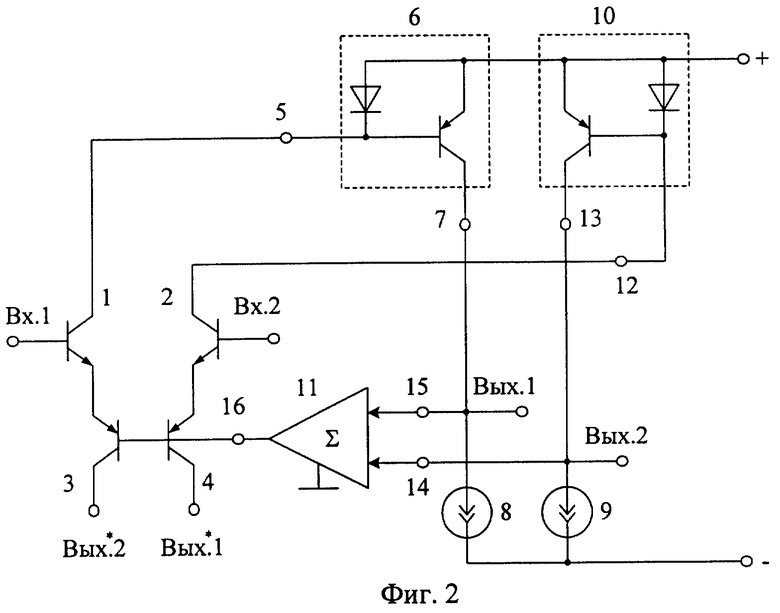

Поставленная цель достигается тем, что в дифференциальный усилитель фиг.1, содержащий первый 1 и второй 2 входные транзисторы, эмиттеры которых соединены с соответствующими эмиттерами первого 3 и второго 4 выходных транзисторов противоположного типа проводимости, базы которых соединены, причем коллектор первого 1 входного транзистора соединен со входом 5 токового зеркала 6, коллекторный выход которого 7 связан с первым источником опорного тока 8, вводятся новые элементы и связи - второй источник опорного тока 9, второе токовое зеркало 10 и сумматор двух сигналов с синфазным выходом 11, причем вход 12 второго токового зеркала 10 связан с коллектором второго входного транзистора 2, его коллекторный выход 13 - соединен с первым входом 14 сумматора двух сигналов с синфазным выходом 11 и вторым источником опорного тока 9, а коллекторный выход 7 первого токового зеркала 6 подключен ко второму входу 15 сумматора двух сигналов с синфазным выходом 11, выход 16 которого связан с объединенными базами выходных транзисторов 3 и 4.

Схема усилителя-прототипа представлена на фиг.1. На фиг.2 показано заявляемое устройство в соответствии с п.1 формулы изобретения.

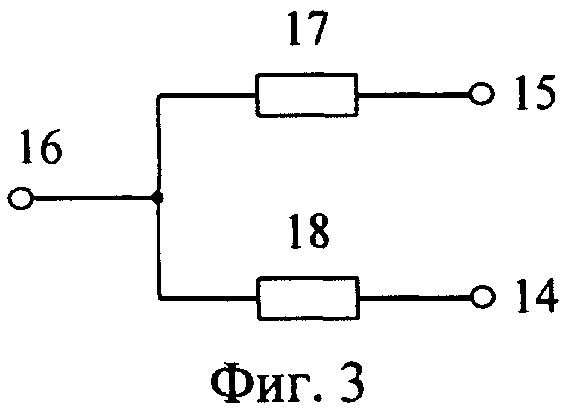

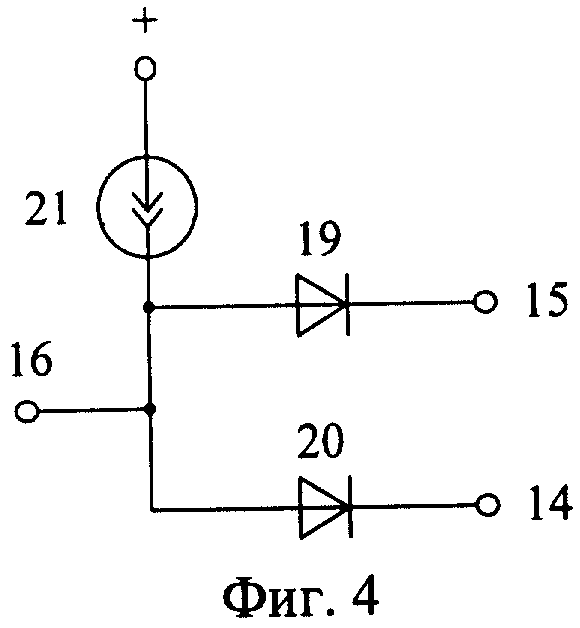

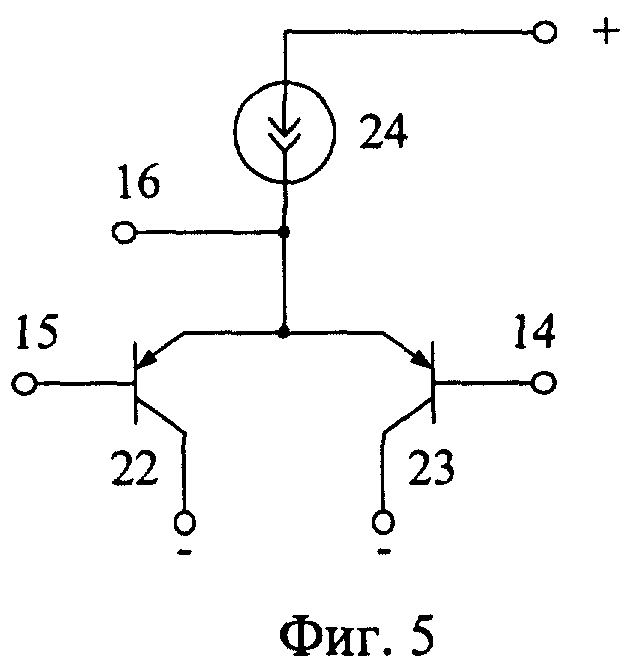

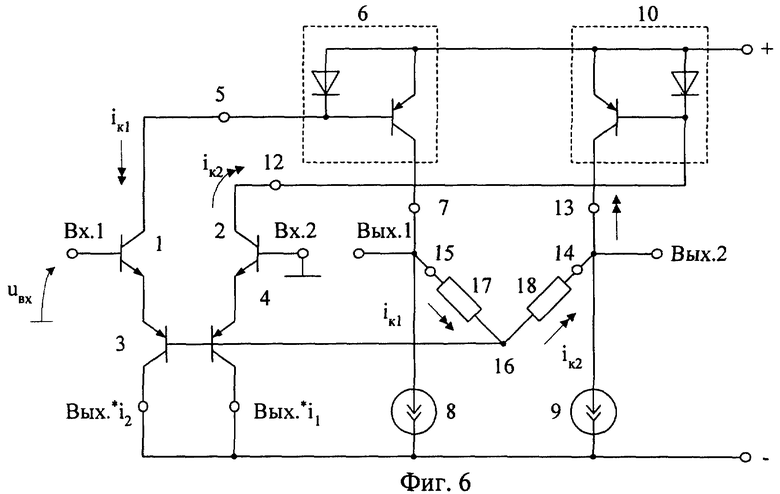

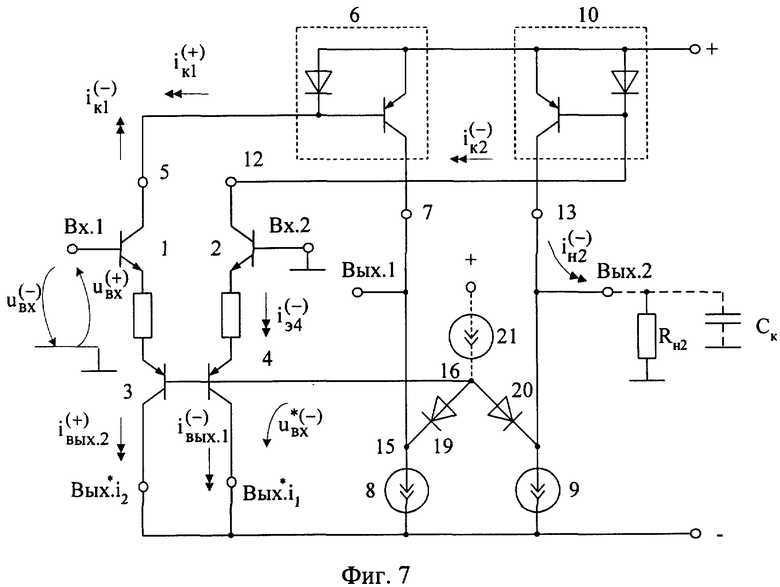

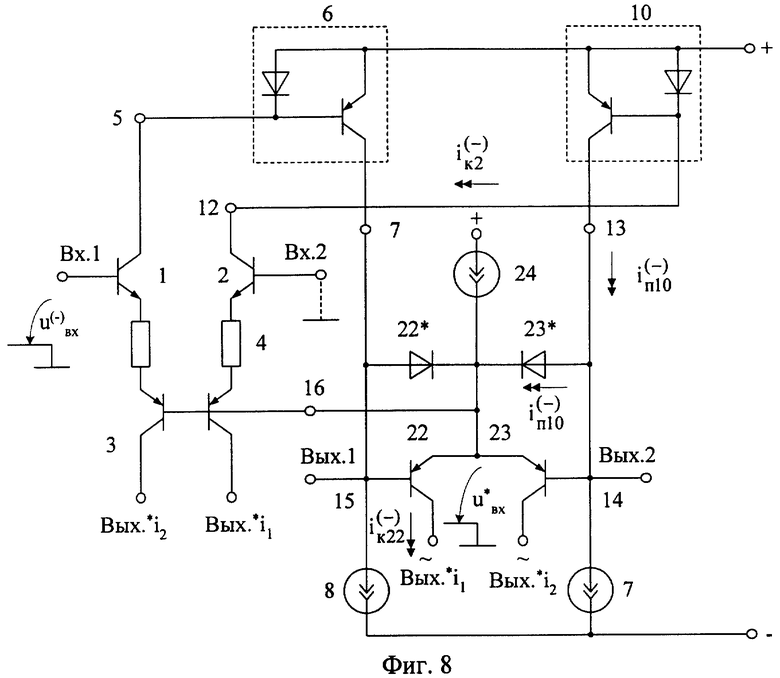

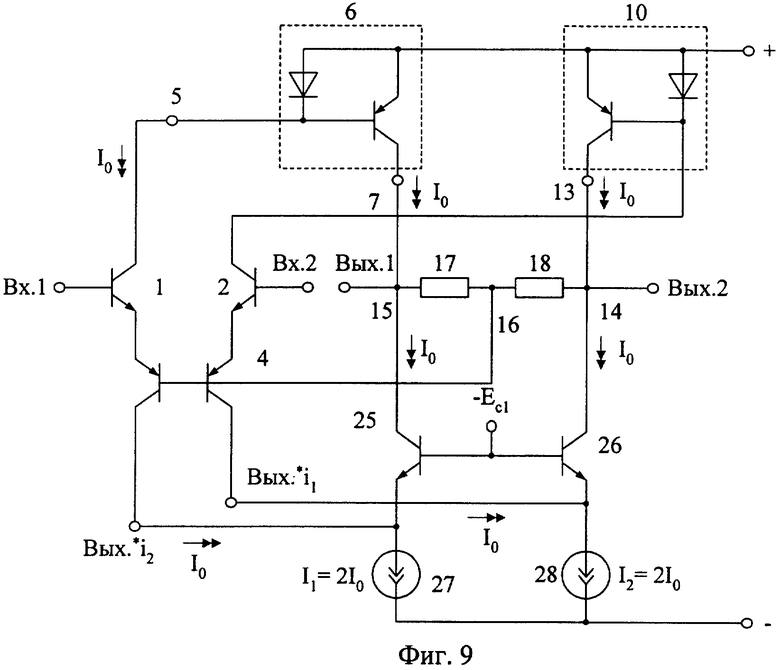

На фиг.3, 4 и 5 показаны варианты выполнения сумматора двух сигналов с синфазным выходом 11 на основе вспомогательных резисторов 17, 18 (фиг.3, п.2 формулы изобретения), вспомогательных р-n переходов 19, 20 (фиг.4, п.3 формулы изобретения), вспомогательных транзисторов 22, 23 (фиг.5, п.4 формулы изобретения). Кроме этого, ДУ, соответствующие п.2, п.3, п.4 и п.5 формулы изобретения, показаны также на фиг.6-9.

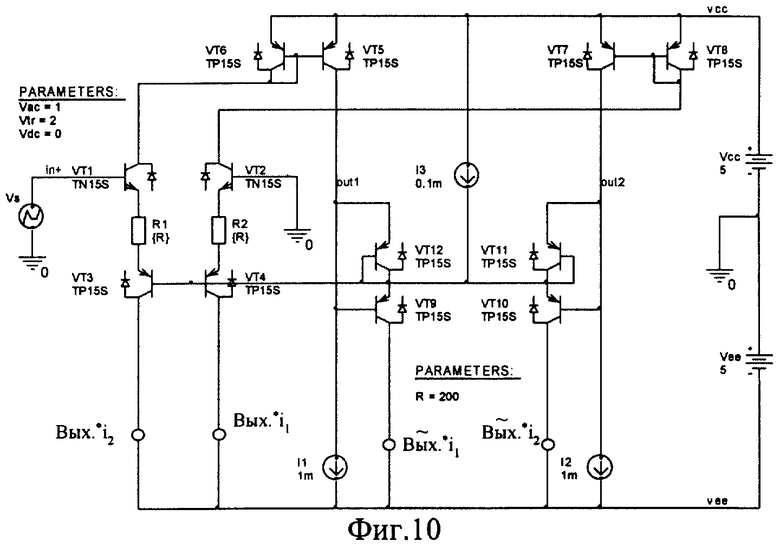

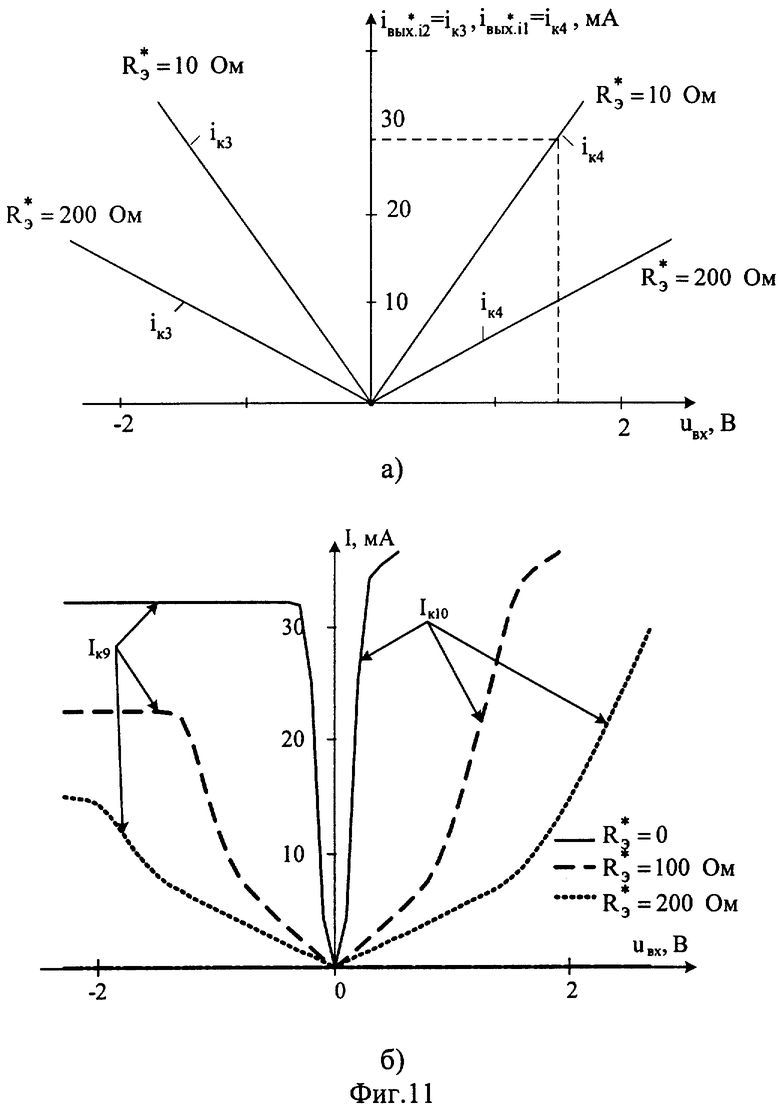

На фиг.10 показана схема заявляемого устройства фиг.8 в среде компьютерного моделирования PSpice, а на фиг.11 - проходные характеристики ДУ фиг.10 - зависимость коллекторных токов Iк3, Iк4, Iк9, Iк10 транзисторов VT3, VT4, VT9, VT10 от входного дифференциального сигнала.

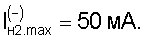

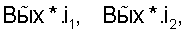

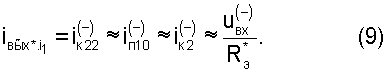

Причем следует заметить, что на большом сигнале в схеме фиг.10 закон изменения токов выходов  ,

,  совпадает с законом изменения токов выходов Вых*.i2, Вых*.i1:

совпадает с законом изменения токов выходов Вых*.i2, Вых*.i1:

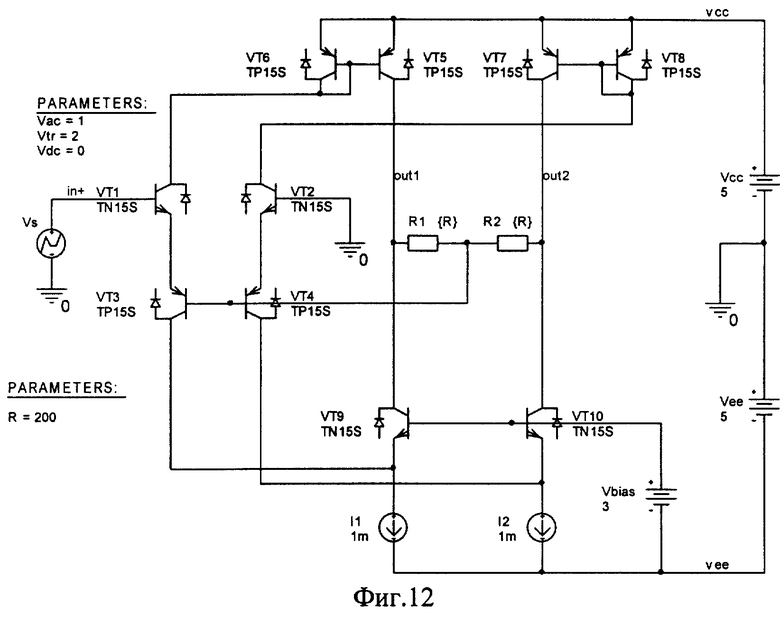

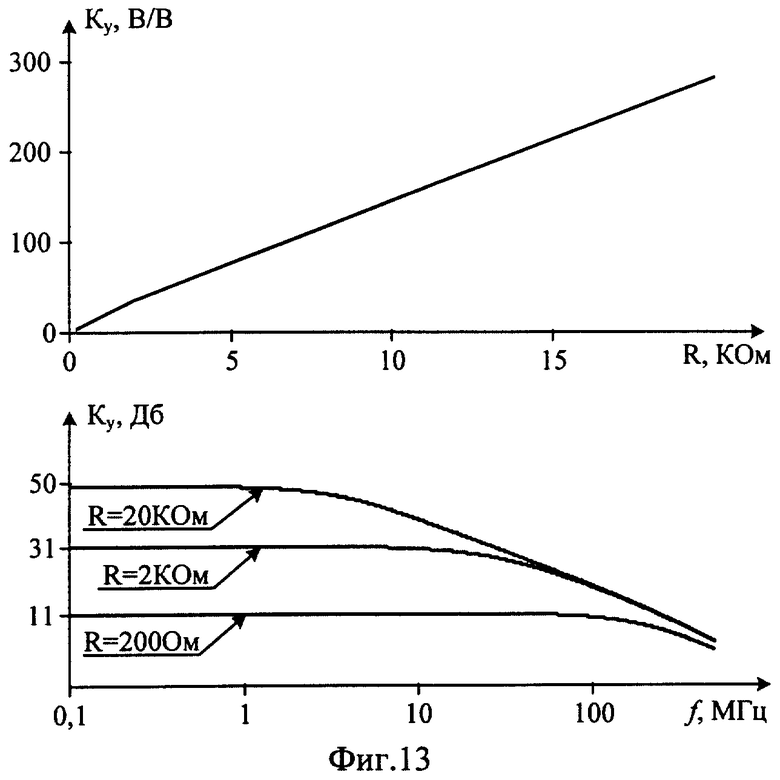

На фиг.12 представлена схема заявляемого ДУ по п.5 формулы изобретения в среде PSpice, а на фиг.13 - графики, характеризующие зависимость его коэффициента усиления по напряжению Ку от сопротивлений R1=R и R2=R, входящих в сумматор сигналов 11.

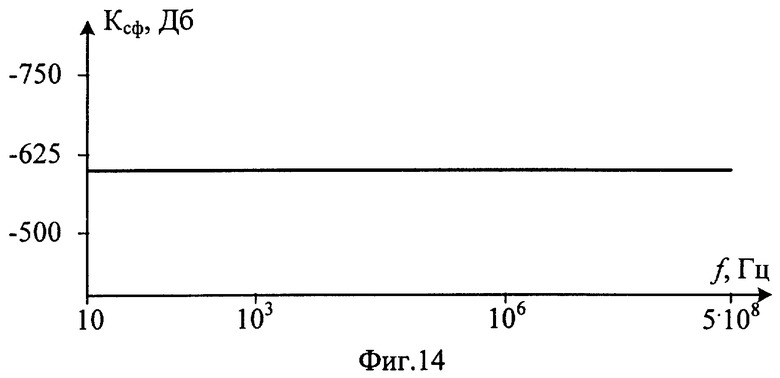

График фиг.14 показывает зависимость коэффициента преобразования входных синфазных сигналов ДУ фиг.12 в выходное дифференциальное напряжение Ксф от частоты.

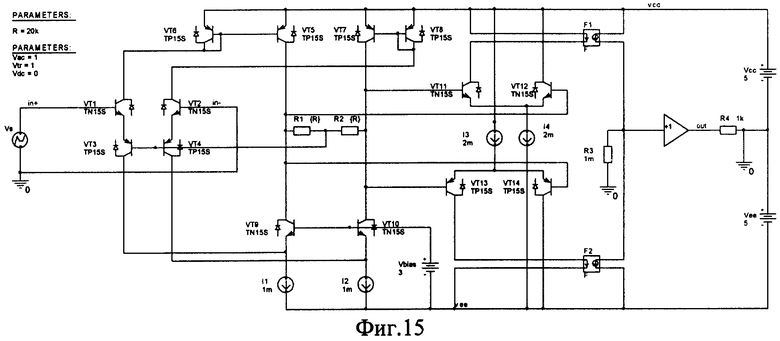

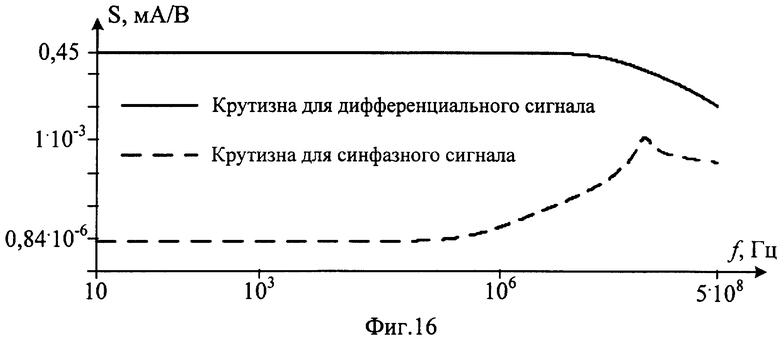

На фиг.15 приведен пример построения операционного усилителя с предлагаемой в настоящей заявке архитектурой ДУ, а на фиг.16 - зависимость крутизны входной подсхемы этого ОУ от дифференциального uд и синфазного uc сигналов.

Дифференциальный усилитель фиг.2 содержит первый 1 и второй 2 входные транзисторы, эмиттеры которых соединены с соответствующими эмиттерами первого 3 и второго 4 выходных транзисторов противоположного типа проводимости, базы которых соединены, причем коллектор первого 1 входного транзистора соединен со входом 5 токового зеркала 6, коллекторный выход которого 7 связан с первым источником опорного тока 8. В схему введен второй источник опорного тока 9, второе токовое зеркало 10 и сумматор двух сигналов с синфазным выходом 11, причем вход 12 второго токового зеркала 10 связан с коллектором второго входного транзистора 2, его коллекторный выход 13 - соединен с первым входом 14 сумматора двух сигналов с синфазным выходом 11 и вторым источником опорного тока 9, а коллекторный выход 7 первого токового зеркала 6 подключен ко второму входу 15 сумматора двух сигналов с синфазным выходом 11, выход 16 которого связан с объединенными базами выходных транзисторов 3 и 4.

Следует заметить, что для расширения диапазона изменения входного синфазного сигнала ДУ в качестве токовых зеркал 6 и 10 авторы рекомендуют применять повторители тока, описанные, например, в патентах США № 5357188, 5907262.

Частные случаи построения сумматора 11 (п.2-п.4 формулы изобретения) показаны на фиг.3-5, а соответствующих им ДУ - фиг.6-8.

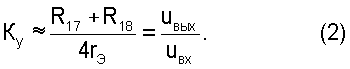

Сумматор двух сигналов с синфазным выходом 11 (фиг.3 и 6) выполнен на основе вспомогательных резисторов 17, 18, общая точка первых выводов которых является выходом 16 сумматора двух сигналов с синфазным выходом 11, а вторые выводы - его первым 14 и вторым 15 входами.

Сумматор двух сигналов с синфазным выходом 11 (фиг.4 и 7) выполнен на основе двух вспомогательных р-n переходов 19 и 20, n-области которых являются входами 15 и 14 сумматора двух сигналов с синфазным выходом 11, а р-области - его выходом 16, причем к выходу 16 подключен первый вспомогательный источник опорного тока 21.

Сумматор двух сигналов с синфазным выходом 11 (фиг.5 и 8) выполнен на основе двух вспомогательных транзисторов 22 и 23, базы которых являются входами 15 и 14 сумматора двух сигналов с синфазным выходом 11, а объединенные эмиттеры - его выходом 16, причем к выходу 16 подключен второй вспомогательный источник опорного тока 24. В частном случае параллельно эмиттерно-базовым р-n переходам транзисторов 22 и 23 авторы рекомендуют включать р-n переходы 22* и 23* (фиг.8).

ДУ фиг.9 (п.5 формулы изобретения) содержит первый 8 и второй 9 источники опорного тока, выполненные на основе первого 25 и второго 26 вспомогательных транзисторов, включенных по схеме с общей базой, причем эмиттеры этих транзисторов связаны с коллекторами выходных транзисторов 3 и 4 и токостабилизирующими двухполюсниками 27 и 28.

Рассмотрим работу заявляемого ДУ для двух вариантов построения сумматора двух сигналов с синфазным выходом 11:

1. Сумматор двух сигналов 11 - линейное устройство.

2. Сумматор двух сигналов 11 - нелинейное устройство (содержит р-n переходы и транзисторы), включенные в соответствии с формулой изобретения.

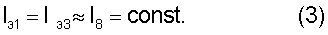

В статическом режиме коллекторные токи транзисторов ДУ фиг.6 для первого варианта построения сумматора двух сигналов 11 равны

Iк3=Iк1≈Iк8, Iк2=Iк4≈Iк9, Iк8≈Iк9.

Такой режим обеспечивается за счет отрицательной обратной связи по синфазному сигналу, которую образует сумматор двух сигналов 11 (резисторы 17, 18 и транзисторы 3 (4), 1 (2)).

Если на вход Вх.1 подать напряжение uвх, то коллекторные токи транзисторов 2 и 4 начнут уменьшаться, а транзисторов 1 и 3 - увеличиваться. Как следствие между узлами «Вых.1» и «Вых.2» образуется дифференциальное выходное напряжение ДУ

где iк1=у21uвх,

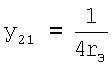

- крутизна входной подсхемы ДУ на транзисторах 1-4,

- крутизна входной подсхемы ДУ на транзисторах 1-4,

rЭ - сопротивление эмиттерного перехода транзисторов 1-4.

Таким образом, коэффициент усиления по напряжению ДУ фиг.6

Диапазон входных сигналов, при котором соблюдается пропорциональность между выходным током ДУ фиг.6 и входным напряжением ДУ, не превышает Uгр=80÷100 мВ.

Существенная особенность схемы фиг.6 - высокая симметрия, что обеспечивает ей хорошее ослабление синфазных сигналов (Кос.сф>120 дБ).

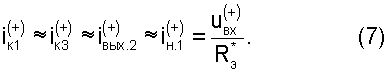

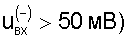

Рассмотрим далее работу заявляемой схемы на примере ДУ фиг.7, который содержит нелинейный сумматор двух сигналов 11, выполненный на р-n переходах 19 и 20. При таком построении ДУ его свойства, в отличие от ДУ фиг.6, существенно изменяются - диапазон его линейной работы (Uгр1) расширяется до единиц вольт. Действительно, при уменьшении напряжения на входе «Вх.1» относительно входа «Вх.2» увеличивается коллекторный ток транзистора 2  и, следовательно, выходной ток токового зеркала 10 становится больше тока I9: p-n переход 20 закрывается. В то же время, благодаря нелинейному сумматору сигналов 11 и отрицательной обратной связи, в схеме фиг.7 обеспечивается дальнейшая стабилизация коллекторного тока транзисторов 1 и 3 левого плеча ДУ:

и, следовательно, выходной ток токового зеркала 10 становится больше тока I9: p-n переход 20 закрывается. В то же время, благодаря нелинейному сумматору сигналов 11 и отрицательной обратной связи, в схеме фиг.7 обеспечивается дальнейшая стабилизация коллекторного тока транзисторов 1 и 3 левого плеча ДУ:

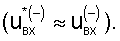

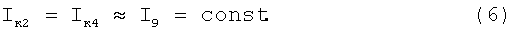

Это означает, что дальнейшее изменение входного напряжения  будет с единичным коэффициентом передаваться на базу транзистора 4

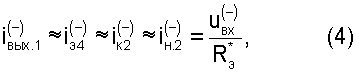

будет с единичным коэффициентом передаваться на базу транзистора 4  Поэтому коллекторные токи транзисторов 2, 4, выходной ток токового зеркала 10 и, следовательно, ток в нагрузке Rн2 пропорциональны входному напряжению

Поэтому коллекторные токи транзисторов 2, 4, выходной ток токового зеркала 10 и, следовательно, ток в нагрузке Rн2 пропорциональны входному напряжению

где  - эквивалентное сопротивление в эмиттерной цепи транзисторов 2 и 4.

- эквивалентное сопротивление в эмиттерной цепи транзисторов 2 и 4.

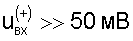

При  получаем, что максимальный ток в нагрузке

получаем, что максимальный ток в нагрузке

Если в качестве нагрузки ДУ рассматривать емкость коррекции АЧХ операционного усилителя Ск или паразитную емкость на подложку, то из последней формулы следует, что ток заряда этой емкости, пропорциональный входному сигналу, может достигать величины, значительно превышающей статические токи в схеме (1÷2 мА). Такой режим характерен для двухтактных каскадов класса «В». Следовательно, в предлагаемом ДУ существенно повышается быстродействие, так скорость изменения напряжения на емкости Ск пропорциональна  :

:

При положительном входном напряжении  в ДУ фиг.7 обеспечивается стабилизация коллекторных токов транзисторов 2 и 4 на уровне

в ДУ фиг.7 обеспечивается стабилизация коллекторных токов транзисторов 2 и 4 на уровне

Поэтому при увеличении  потенциал базы транзистора 3 перестает изменяться

потенциал базы транзистора 3 перестает изменяться  , а все приращение

, а все приращение  прикладывается между базами транзисторов 1 и 3. Поэтому приращения токов

прикладывается между базами транзисторов 1 и 3. Поэтому приращения токов  в схеме фиг.7 пропорциональны

в схеме фиг.7 пропорциональны  :

:

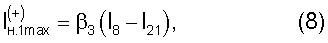

Максимальное значение тока в нагрузке при

где β3=50÷100 - коэффициент усиления по току базы транзистора 3.

Дальнейшим развитием схемы фиг.7 является схема ДУ фиг.8, в которой нелинейный сумматор сигналов 11 выполнен на транзисторах 22-23, источнике опорного тока 24 и р-n переходах 22*-23*, которые шунтируют эмиттерные р-n переходы транзисторов 22-23.

Такое построение сумматора двух сигналов 11 позволяет преобразовать дифференциальное выходное напряжение между выходами «Вых.1-Вых.2» с достаточно высокой крутизной в приращения токов выходов  а также обеспечить пропорциональность токов этих выходов в широком диапазоне входных сигналов ДУ

а также обеспечить пропорциональность токов этих выходов в широком диапазоне входных сигналов ДУ  Отличие в работе ДУ фиг.8 от ДУ фиг.7 состоит в том, что при запирании эмиттерного р-n перехода транзистора 23 (при

Отличие в работе ДУ фиг.8 от ДУ фиг.7 состоит в том, что при запирании эмиттерного р-n перехода транзистора 23 (при  открывается р-n переход 23*, который передает в эмиттерную цепь транзистора 22 приращение тока

открывается р-n переход 23*, который передает в эмиттерную цепь транзистора 22 приращение тока  токового зеркала 10. Поэтому при большом сигнале ток выхода

токового зеркала 10. Поэтому при большом сигнале ток выхода  не ограничивается

не ограничивается

Заметим, что если исключить р-n переходы 22*, 23*, то токи указанных выше выходов не будут превышать ток I24, хотя токи выходов Вых*.i2 и * Вых*.i1 по-прежнему изменяются пропорционально Uвх.

Дальнейшим развитием предлагаемого технического решения является ДУ фиг.9, который (в частном случае) содержит «линейный» вариант построения сумматора сигналов 11 на основе резисторов 17 и 18 (при построении сумматора сигналов 11 на основе схем фиг.4 и 5 он приобретает те же свойства, которые имеют ранее рассмотренные ДУ фиг.7 и 8).

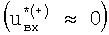

Существенная особенность ДУ фиг.9 состоит в том, что здесь источники токов 8 и 9 (фиг.2, 6, 7, 8) выполнены в виде зависимых источников тока - они управляются от выходов Вых*.i1, Вых*.i2 ДУ. Во-первых, это повышает коэффициент усиления по напряжению в 4 раза (фиг.13). Во-вторых, при этом расширяется полоса пропускания (см. фиг.13), так как передача сигналов на выходы ДУ «Вых.1», «Вых.2» обеспечивается не только через инерционные токовые зеркала 6 и 10, но и через более широкополосный «перегнутый» каскод на транзисторах 25-26. В-третьих, схема фиг.9 становится «двухтактной» как для выхода «Вых.1», так и для выхода «Вых.2». В-четвертых, в схеме фиг.9 исключаются составляющие ошибки усиления синфазных сигналов, пропорциональные абсолютным значениям выходных проводимостей применяемых транзисторов. Так, моделирование ДУ фиг.9 на моделях интегральных транзисторов ФГУП «Пульсар» (в среде Pspice - фиг.12) показывает, что заявляемый усилитель имеет исключительно высокое ослабление синфазных сигналов (Ксф=uвых/uс, Kсф>600 дБ, фиг.14).

Таким образом, различные варианты выполнения сумматора сигналов 11 (пп.2 и 3), а также построение двухполюсников 8 и 9 в виде управляемых источников тока (п.5) позволяет получить ряд существенных преимуществ заявляемого ДУ.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США № 3.786.362.

2. Патент США № 4.030.044.

3. Патент США № 4.059.808, фиг.5.

4. Патент США № 4.286.227.

5. Авт. вид. СССР № 375754, H03f 3/38.

6. Авт. вид. СССР № 843164, H03f 3/30.

7. Патент США № 3.660.773.

8. Патент США № 4.560.948.

9. Патент РФ № 2930041, H03f 1/32.

10. Патент Японии № 57-5364, H03f 3/343.

11. Патент ЧССР № 134845, кл. 21а2 18/08.

12. Патент ЧССР № 134849, кл. 21а2 18/08.

13. Патент ЧССР № 135326, кл. 21а2 18/08.

14. Патент США № 4.389.579.

15. Патент Англии № 1543361, Н3Т.

16. Патент США № 5.521.552 (фиг.3а).

17. Патент США № 4.059.808.

18. Патент США № 5.789.949.

19. Патент США № 4.453.134.

20. Патент США № 4.760.286.

21. Авт. свид. СССР № 1283946.

22. Патент РФ № 2019019.

23. Патент США № 4.389.579.

24. Патент США № 4.453.092.

25. Патент США № 3.566.289.

26. Патент США № 4.059.808 (фиг.2).

27. Патент США № 3.649.926.

28. Патент США № 4.714.894 (фиг.1).

29. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989.

30. М. Херпи. Аналоговые интегральные схемы. - М.: Радио и связь, 1983, стр.174, рис.5.52.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2005 |

|

RU2292632C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2446554C1 |

| КОМПЛЕМЕНТАРНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2439779C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ СИНФАЗНОГО СИГНАЛА | 2006 |

|

RU2319287C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2005 |

|

RU2292633C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С СИММЕТРИЧНОЙ НАГРУЗКОЙ | 2009 |

|

RU2394361C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2005 |

|

RU2293433C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ СИНФАЗНОГО СИГНАЛА | 2005 |

|

RU2292638C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2439784C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2011 |

|

RU2449464C1 |

Изобретение относится к радиотехнике и связи для использования в структуре аналоговым микросхем различного функционального назначения. Технический результат заключается в расширении динамического диапазона и повышении коэффициента усиления и коэффициента ослабления синфазного сигнала. Дифференциальный усилитель содержит первый (1) и второй (2) входные транзисторы (Т), эмиттеры которых соединены с соответствующими эмиттерами первого (3) и второго (4) выходных Т противоположного типа проводимости, базы которых соединены, причем коллектор первого (1) входного Т соединен со входом (5) токового зеркала (ТЗ) (6), коллекторный выход которого (7) связан с первым источником опорного тока (8). В схему введен второй источник опорного тока (ИОТ) (9), второе ТЗ (10) и сумматор (11) двух сигналов с синфазным выходом, причем вход (12) второго ТЗ (10) связан с коллектором второго входного Т (2), его коллекторный выход (13) - соединен с первым входом (14) сумматора (11) и вторым ИОТ (9), а коллекторный выход (7) первого ТЗ (6) подключен ко второму входу (15) сумматора (11), выход (16) которого связан с объединенными базами выходных Т (3) и (4). 4 з.п. ф-лы, 16 ил.

| US 3660773, 02.05.1972 | |||

| Дифференциальный усилитель | 1974 |

|

SU678640A1 |

| Дифференциальный усилитель | 1982 |

|

SU1107279A1 |

| US 4030044, 14.06.1977 | |||

| US 4272728, 09.06.1981. | |||

Авторы

Даты

2007-11-10—Публикация

2006-04-12—Подача