Текст описания приведен в факсимильном виде.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| ПАРАЛЛЕЛЬНАЯ СИСТЕМА ПОИСКА И ЗАМЕНЫ | 2003 |

|

RU2245579C2 |

| УСТРОЙСТВО ПАРАЛЛЕЛЬНОГО ПОИСКА И ЗАМЕНЫ ВХОЖДЕНИЙ В ОБРАБАТЫВАЕМЫХ СЛОВАХ | 2005 |

|

RU2296366C1 |

| Устройство параллельно-последовательного поиска и замены вхождений в обрабатываемых словах | 2022 |

|

RU2793554C1 |

| УСТРОЙСТВО ПОИСКА И ЗАМЕНЫ ПРОИЗВОЛЬНЫХ ВХОЖДЕНИЙ В СЛОВАХ ТЕКСТА | 2002 |

|

RU2250493C2 |

| СИСТЕМА ВЗАИМОРАСПРЕДЕЛЕНИЯ РЕСУРСОВ | 2000 |

|

RU2188451C2 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА ДЛЯ ИНТЕРВАЛЬНЫХ ВЫЧИСЛЕНИЙ | 1991 |

|

RU2006929C1 |

| ПАРАЛЛЕЛЬНАЯ ПРОЦЕССОРНАЯ СИСТЕМА | 1991 |

|

RU2084953C1 |

| ФОРМУЛЬНЫЙ ПРОЦЕССОР С КОМАНДОПОДОБНЫМИ ЛОГИЧЕСКИМИ УПРАВЛЯЮЩИМИ ЭЛЕМЕНТАМИ | 1997 |

|

RU2143726C1 |

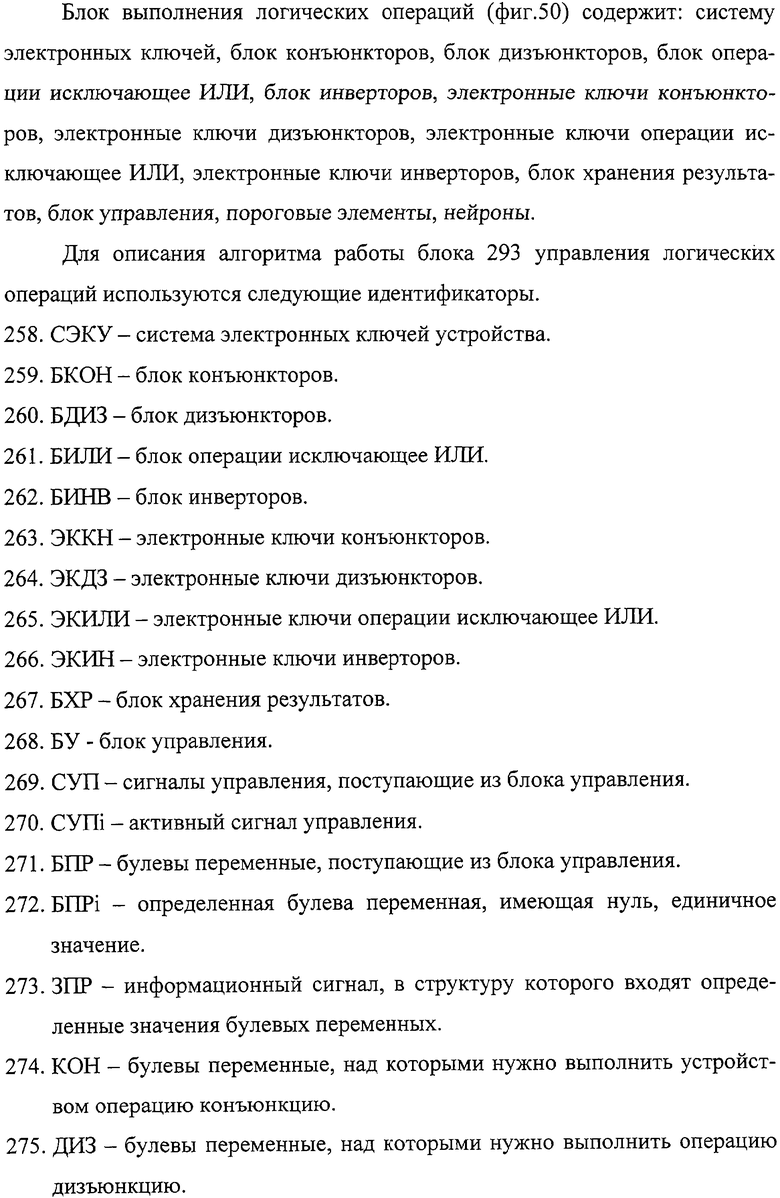

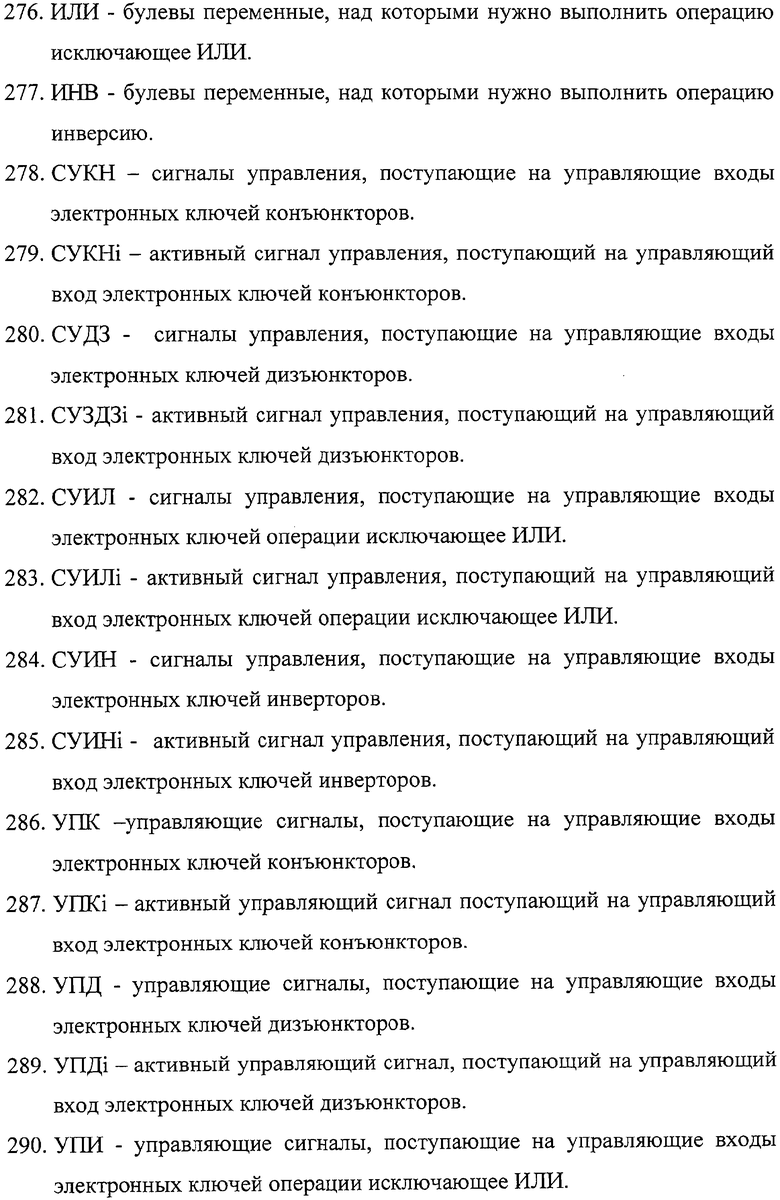

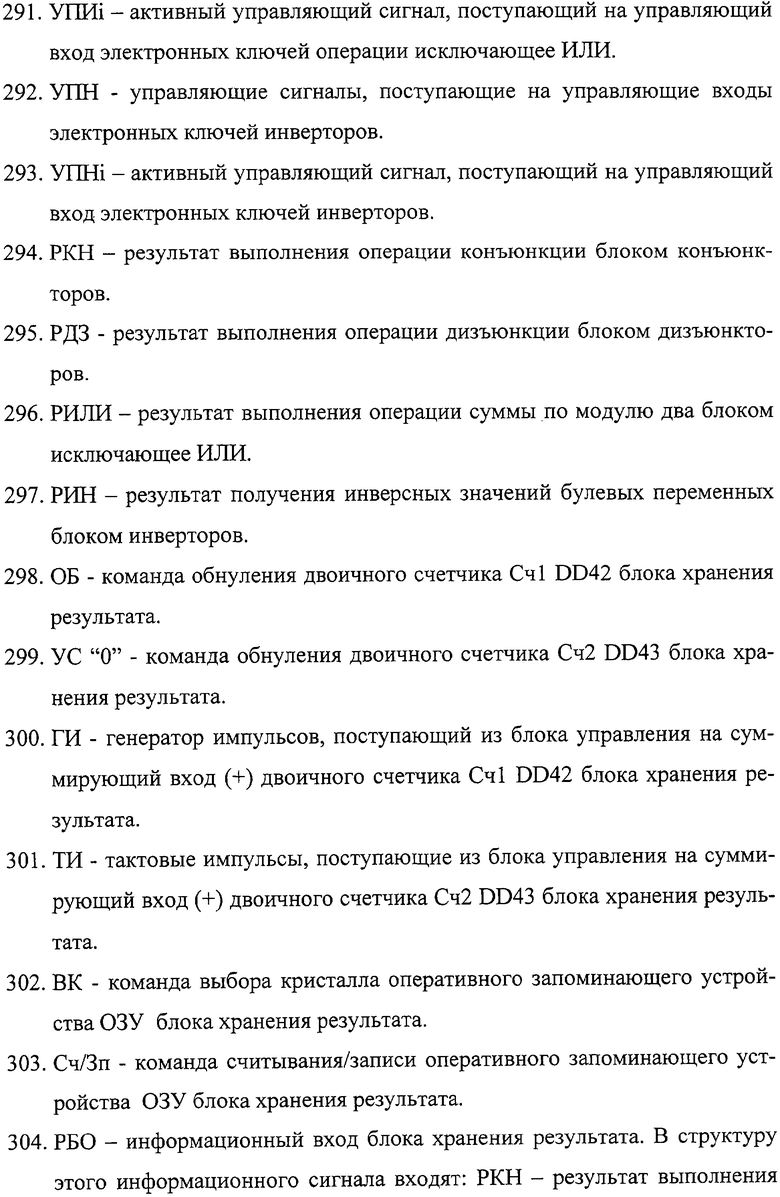

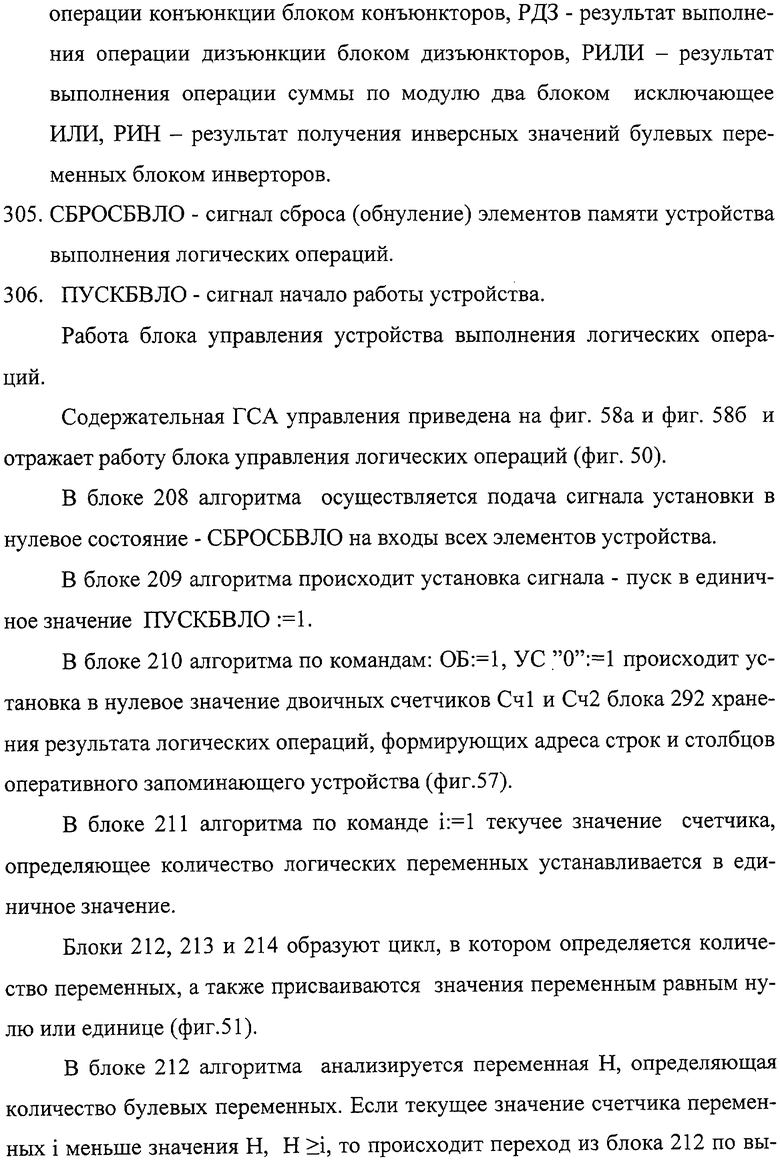

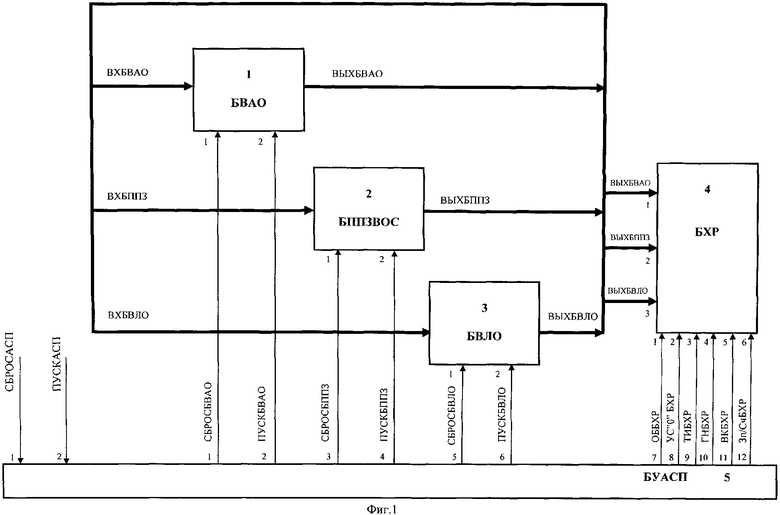

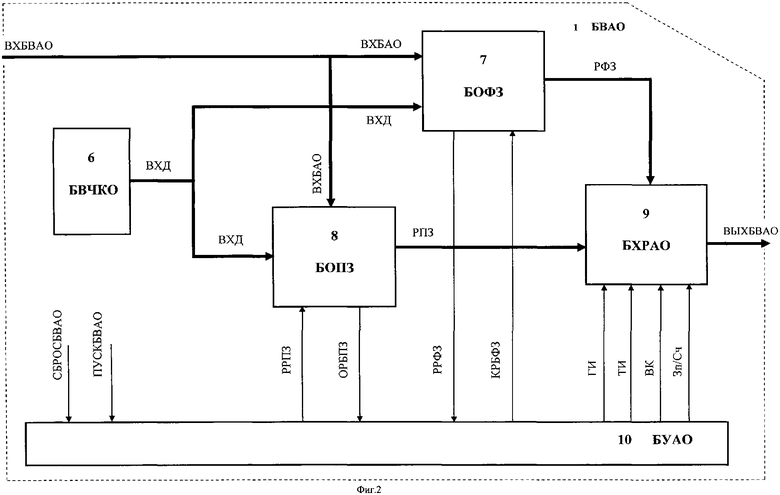

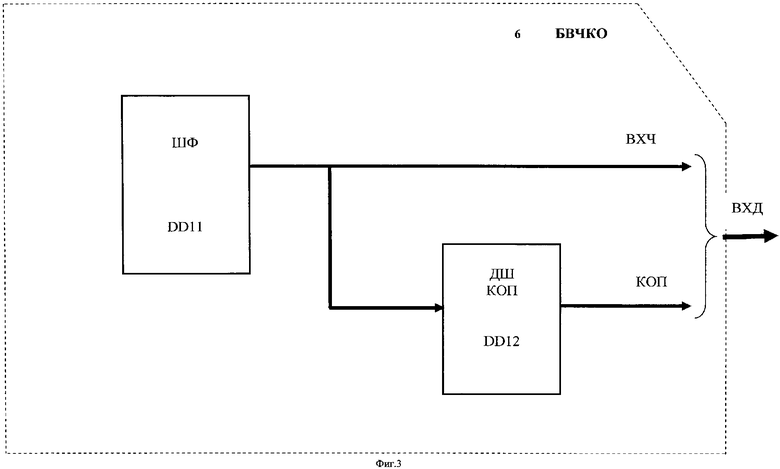

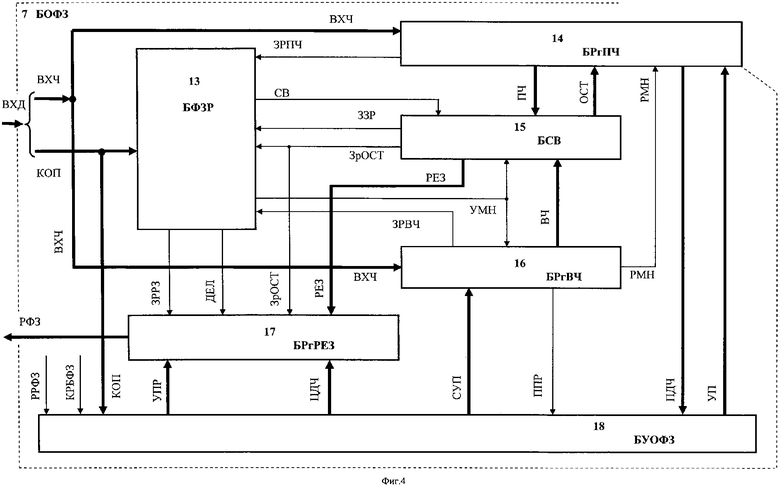

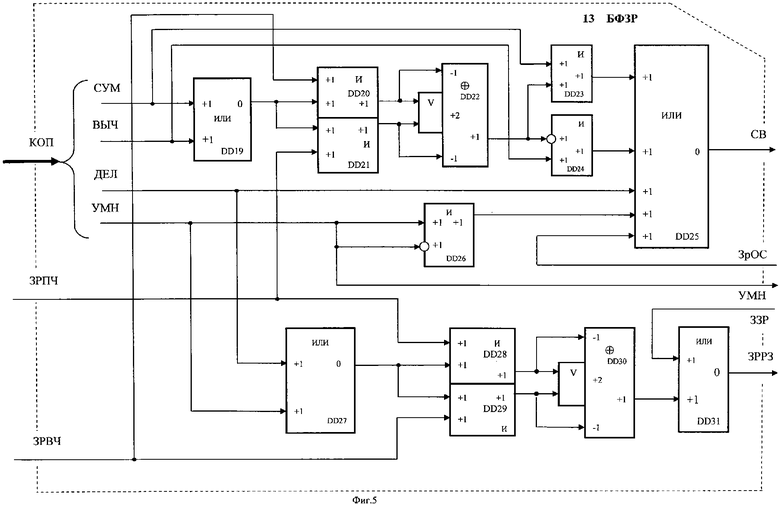

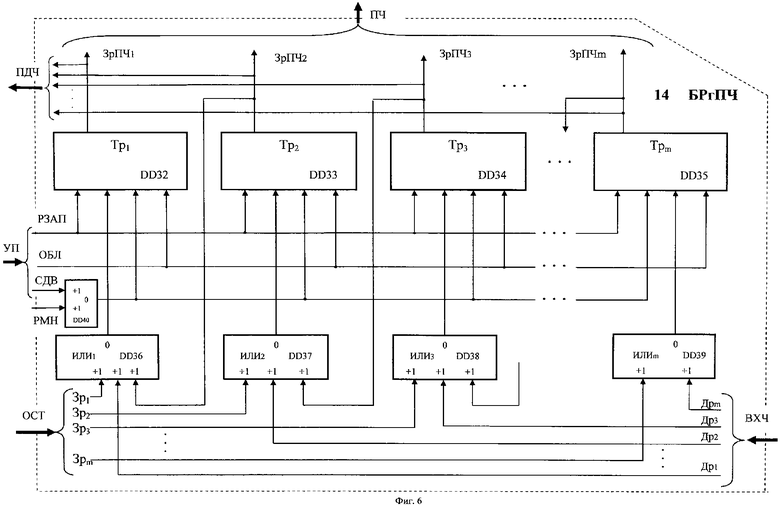

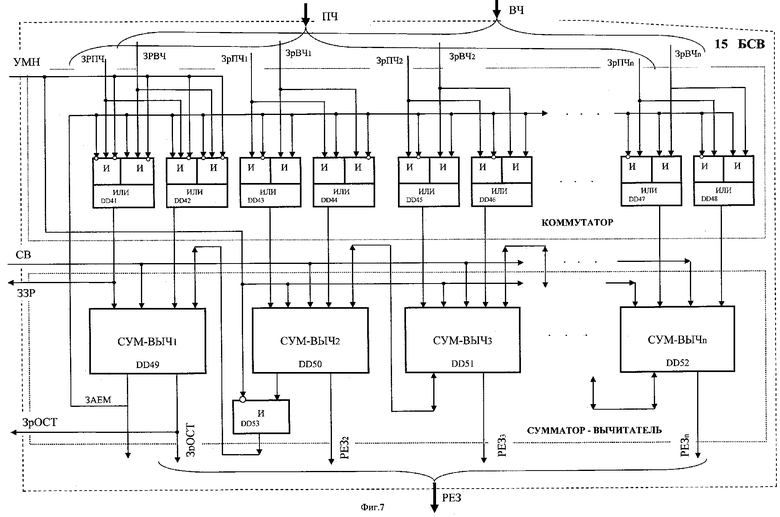

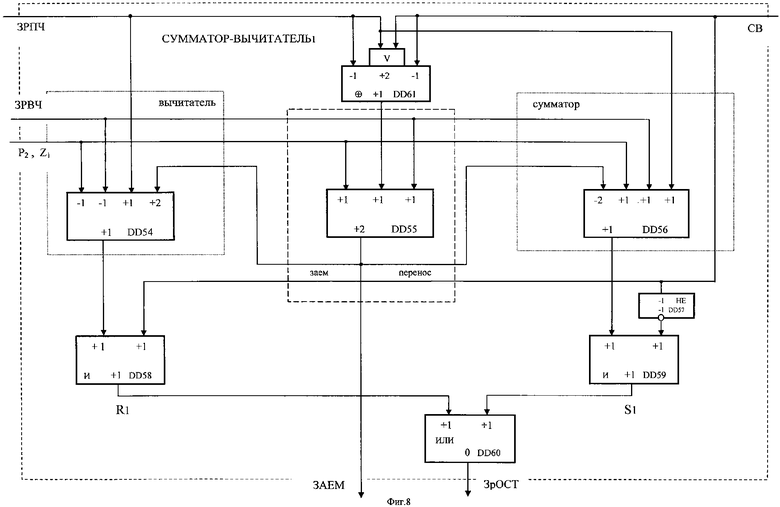

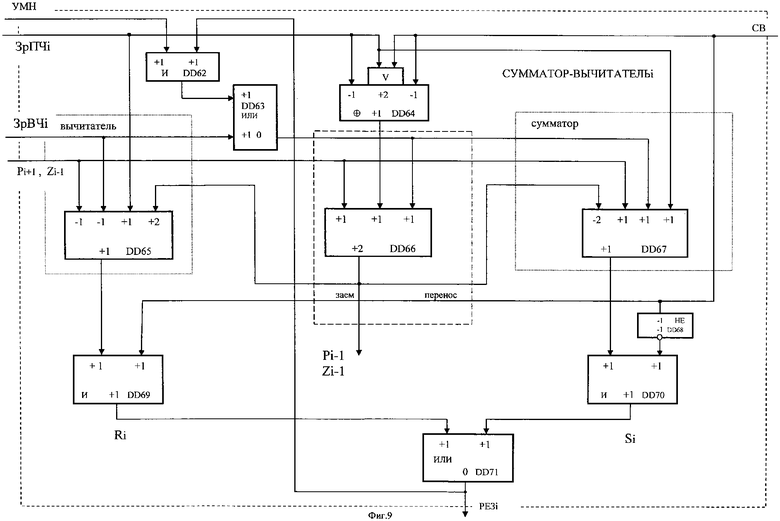

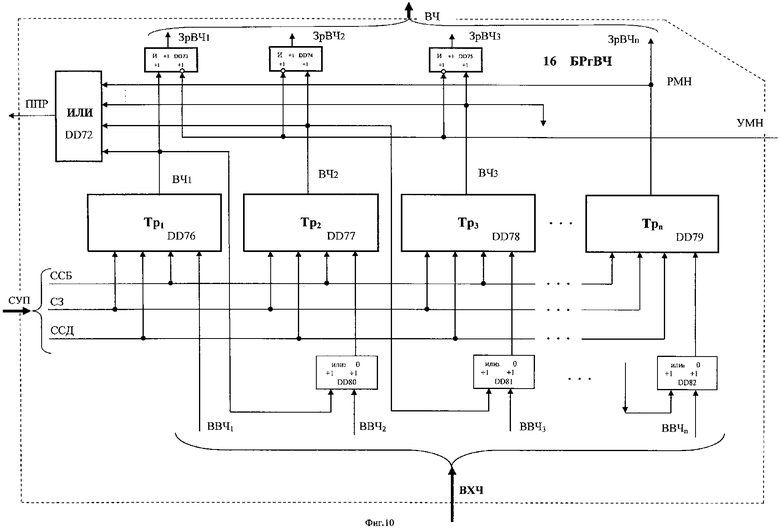

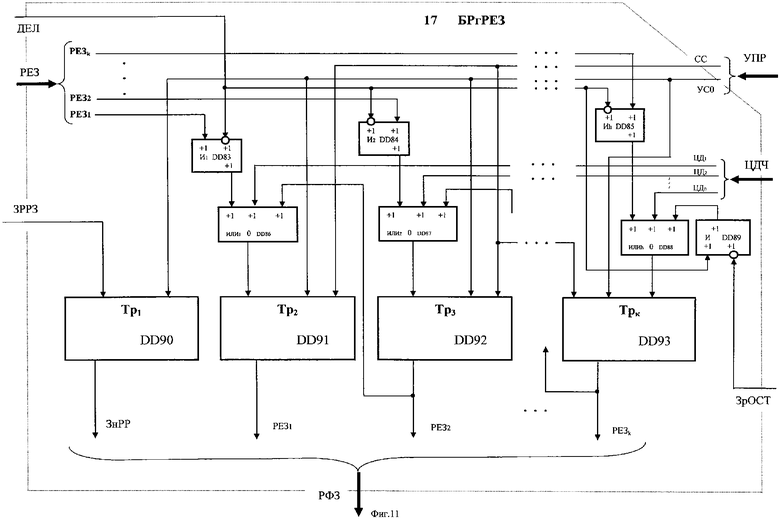

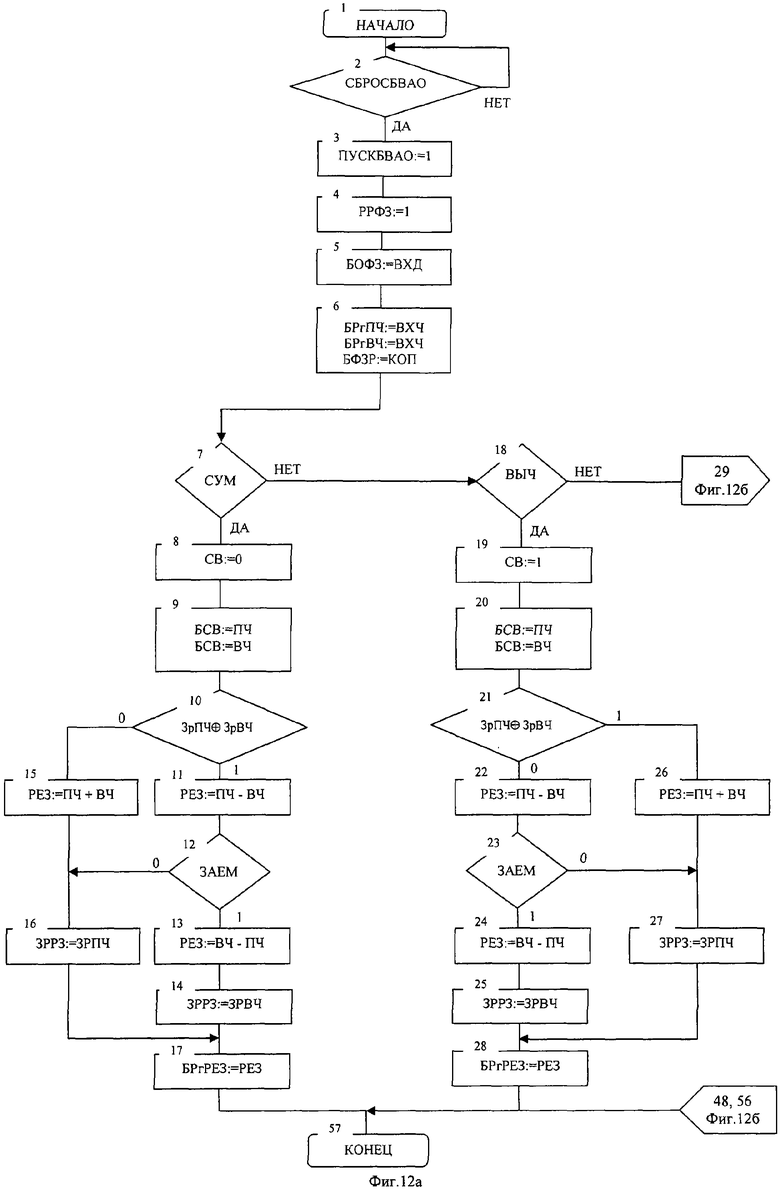

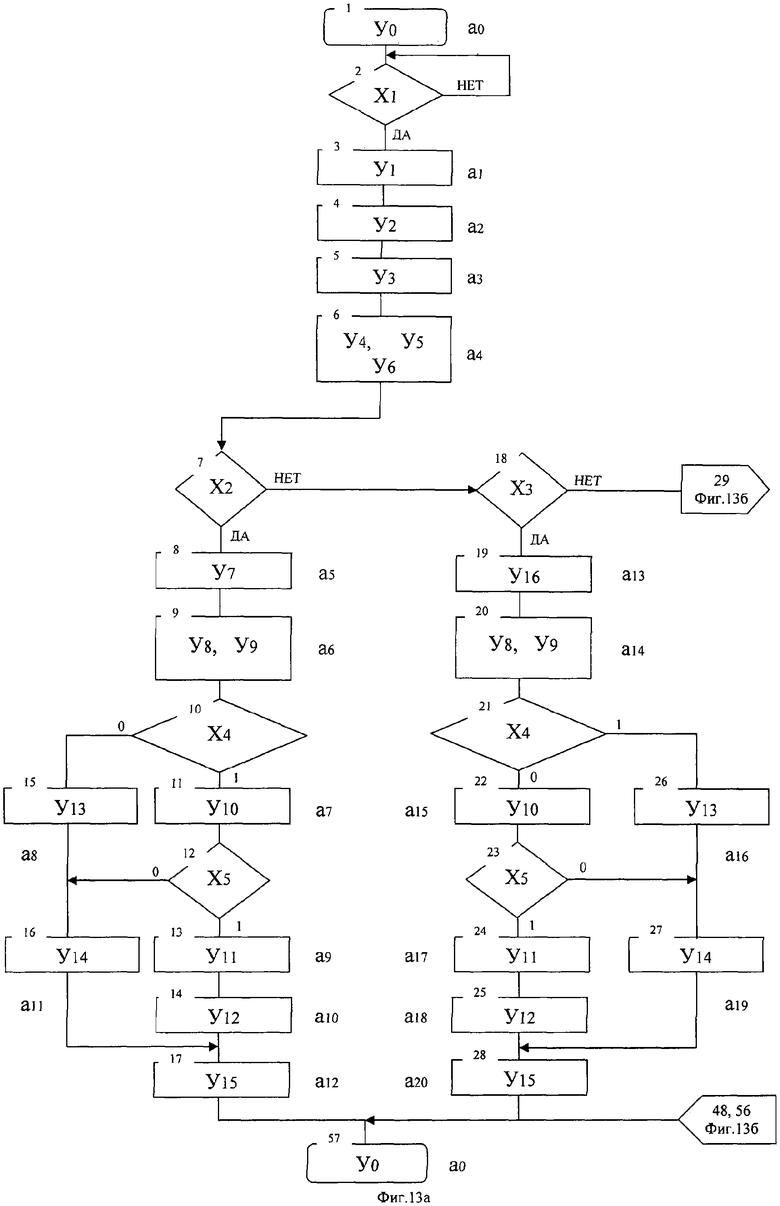

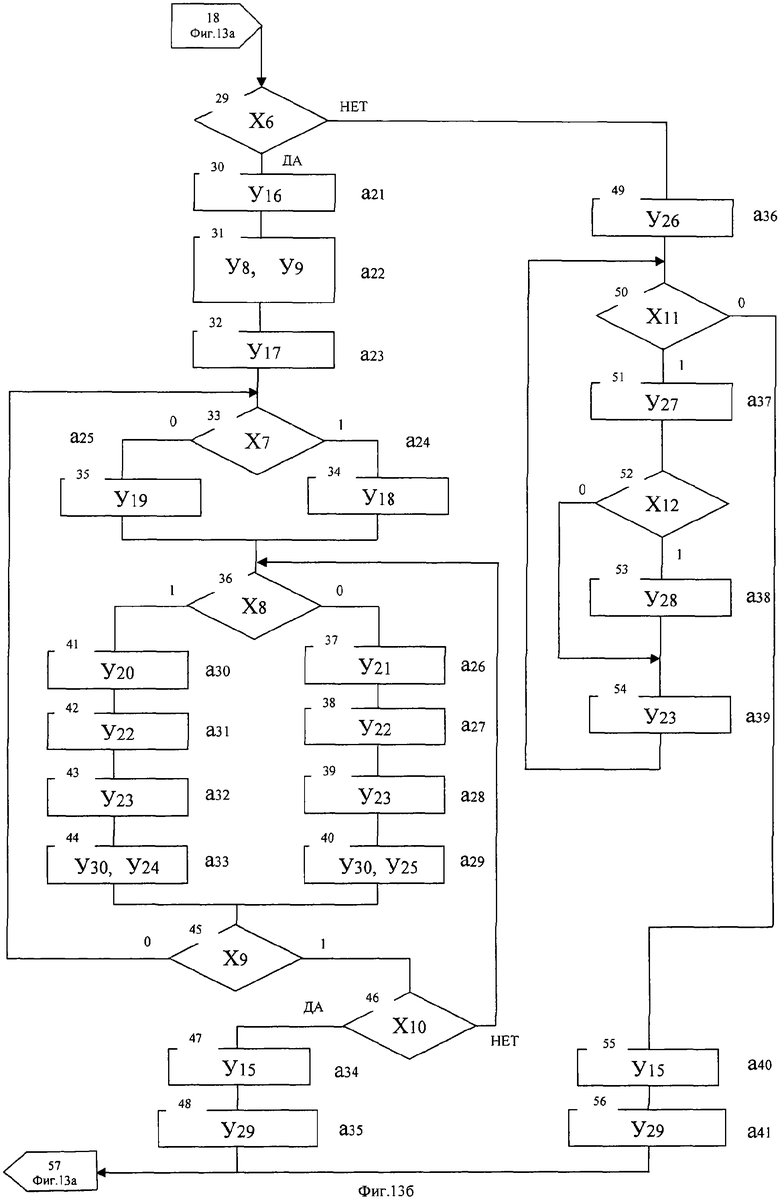

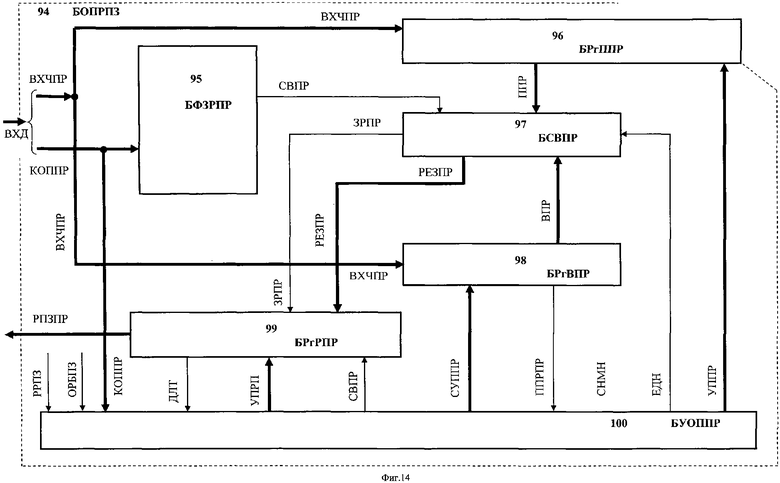

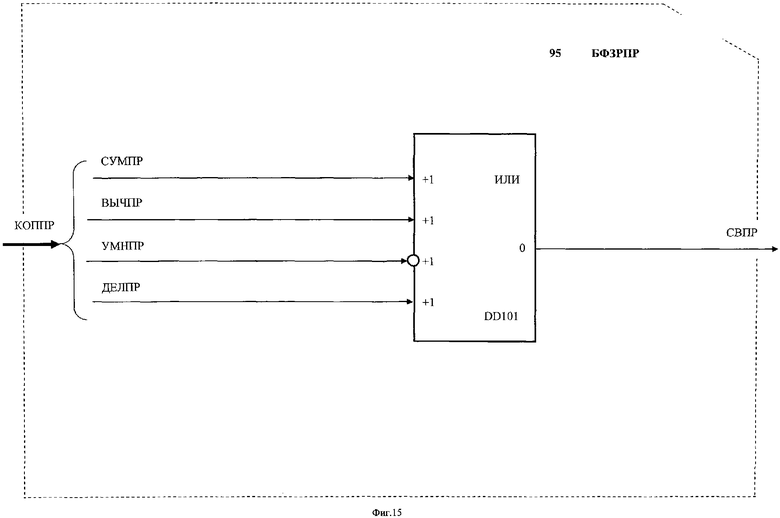

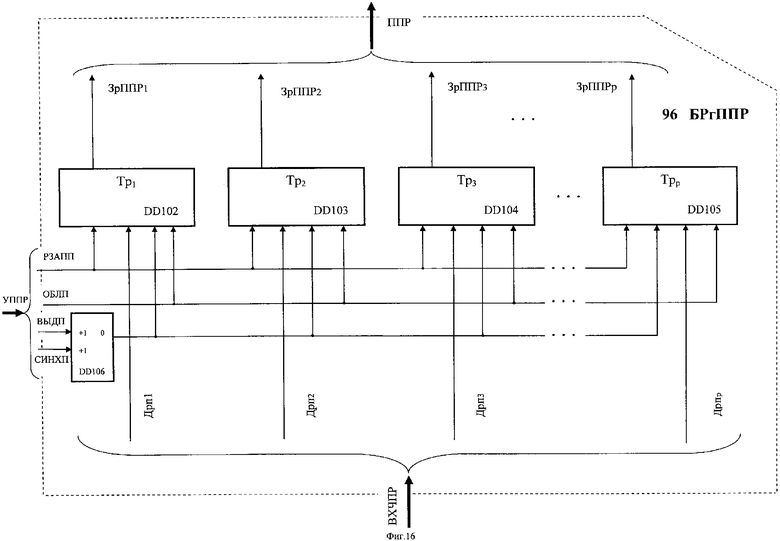

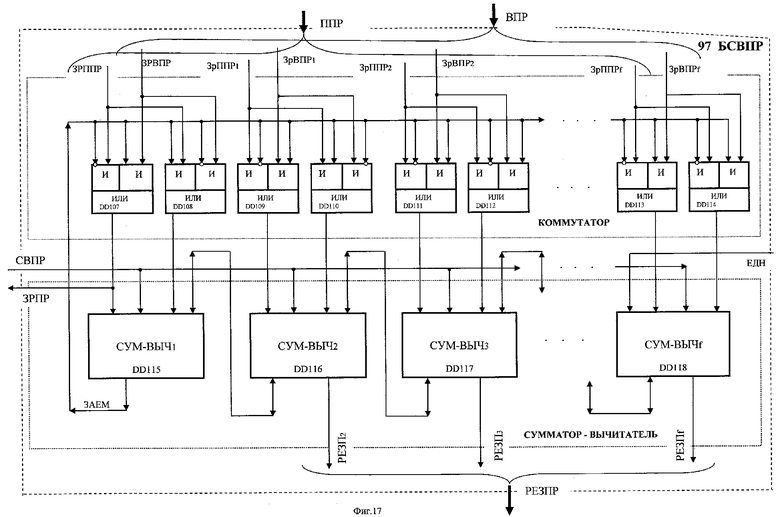

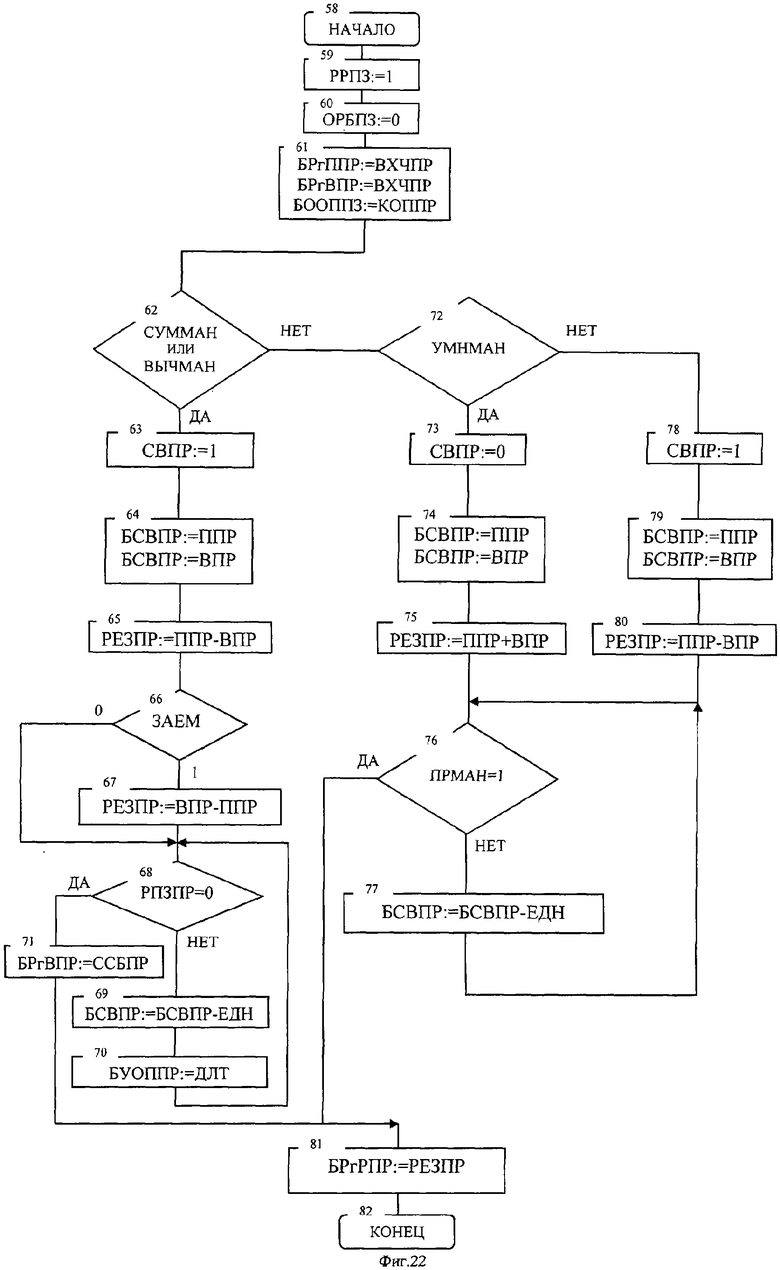

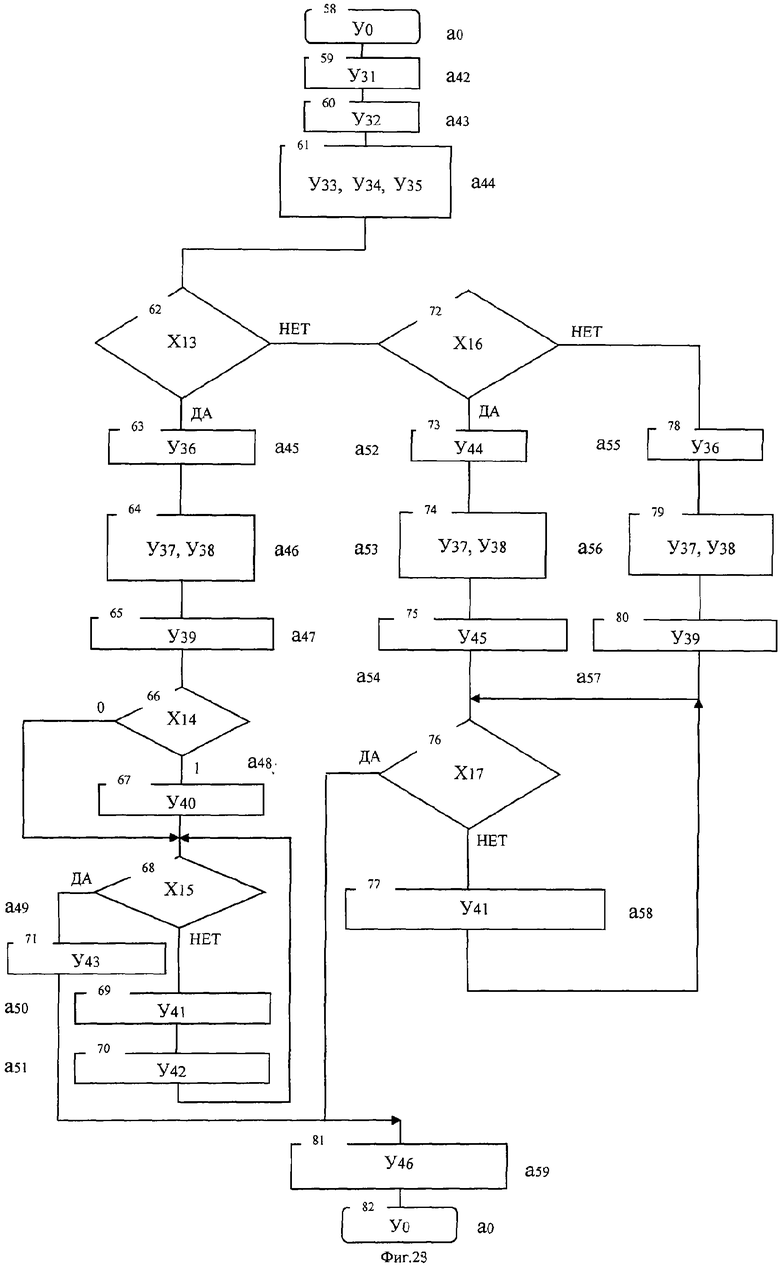

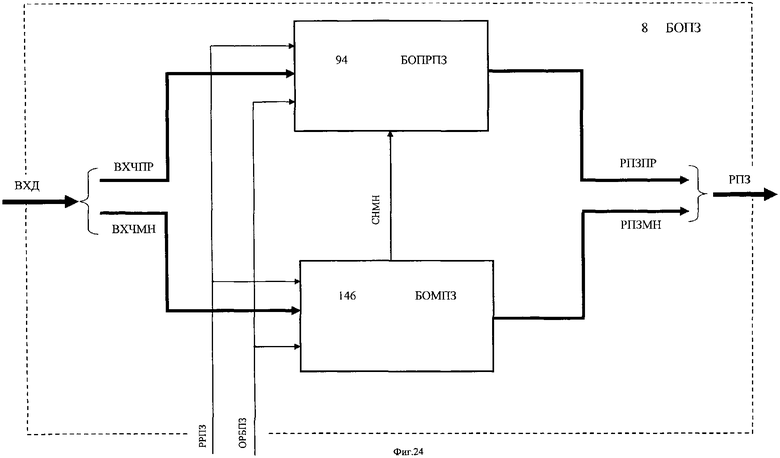

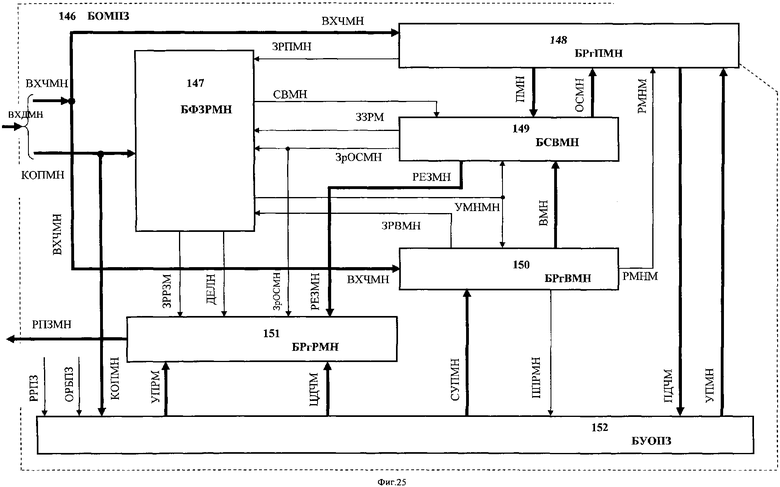

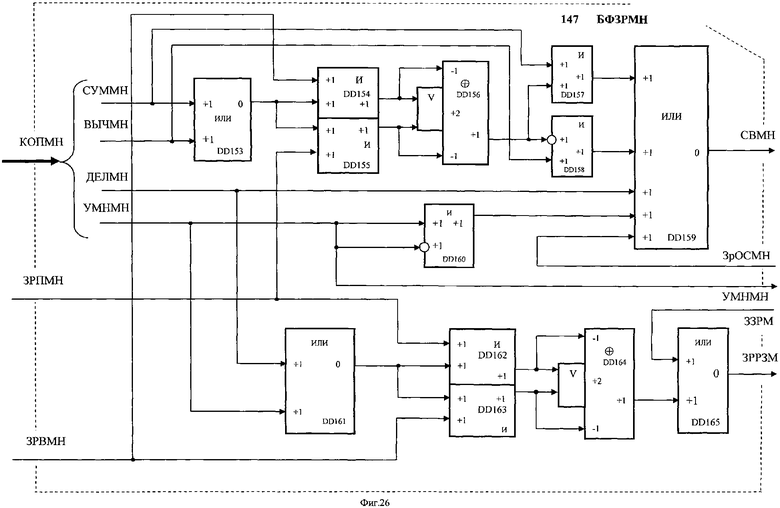

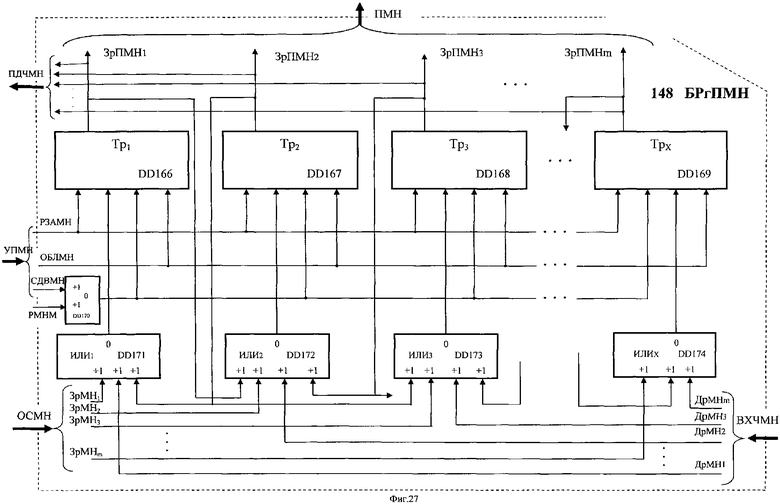

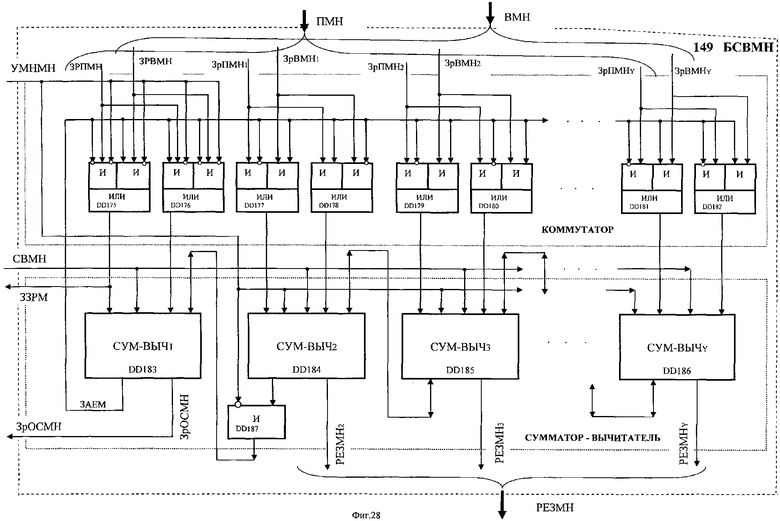

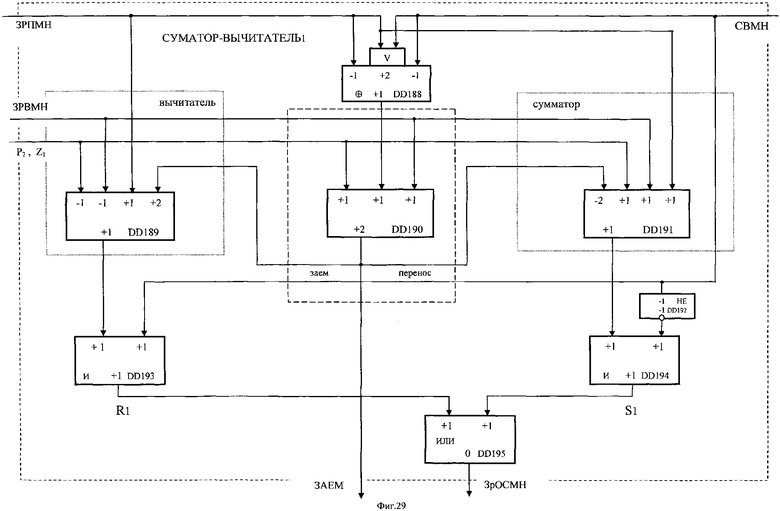

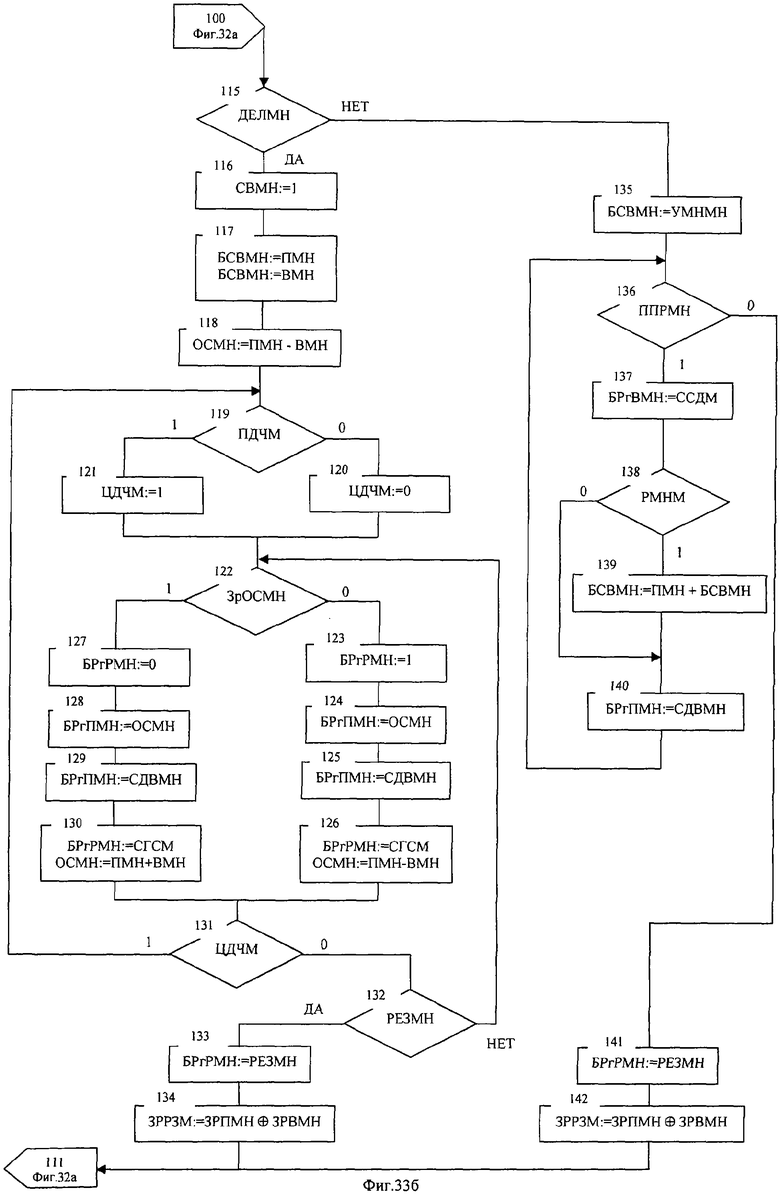

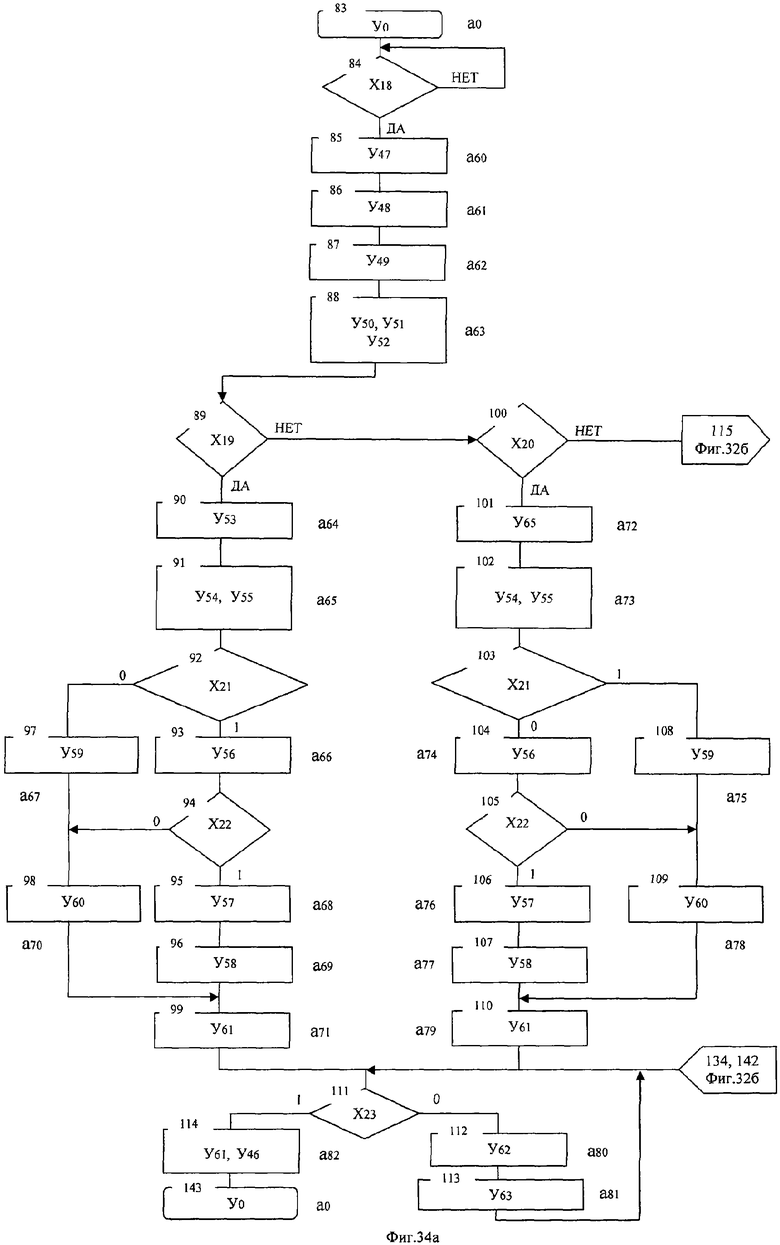

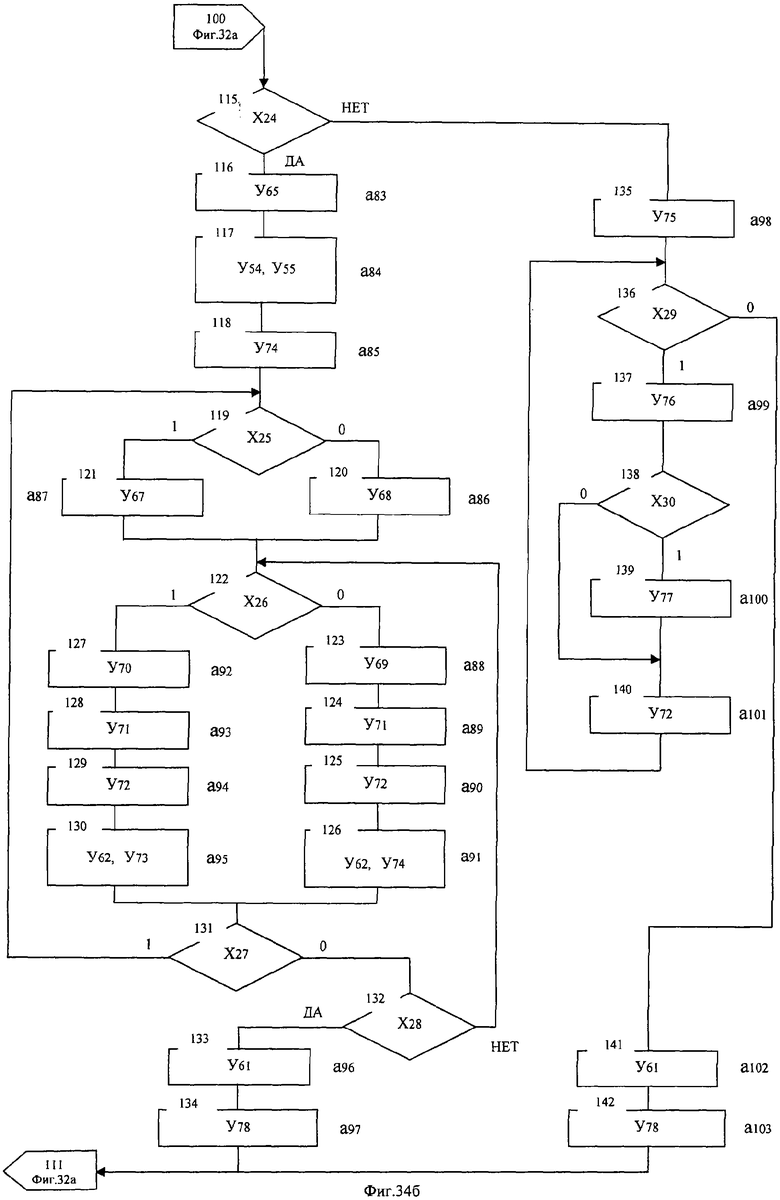

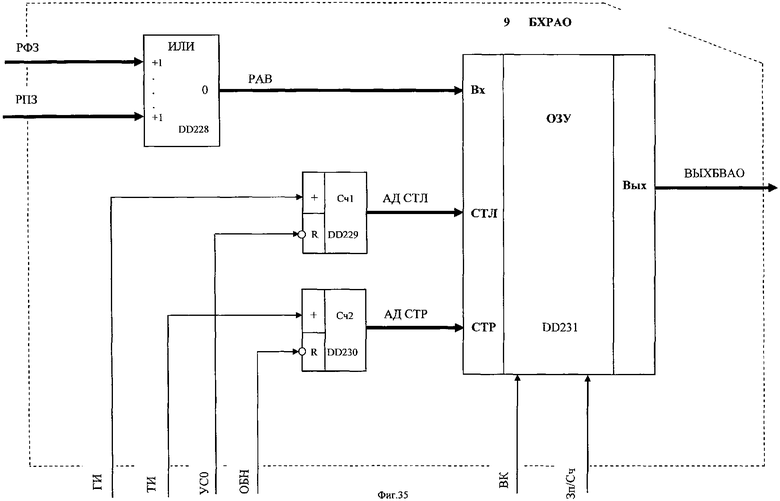

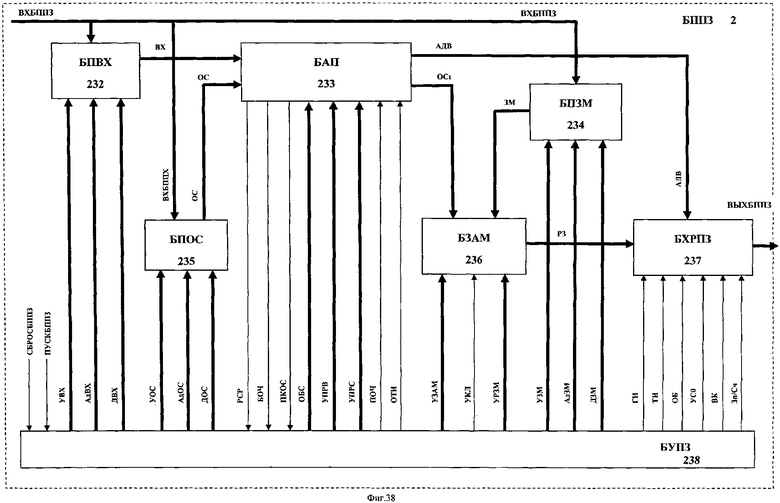

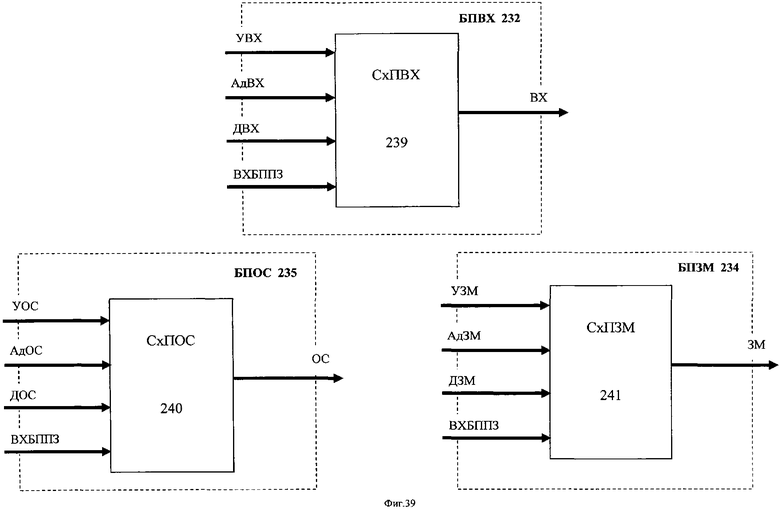

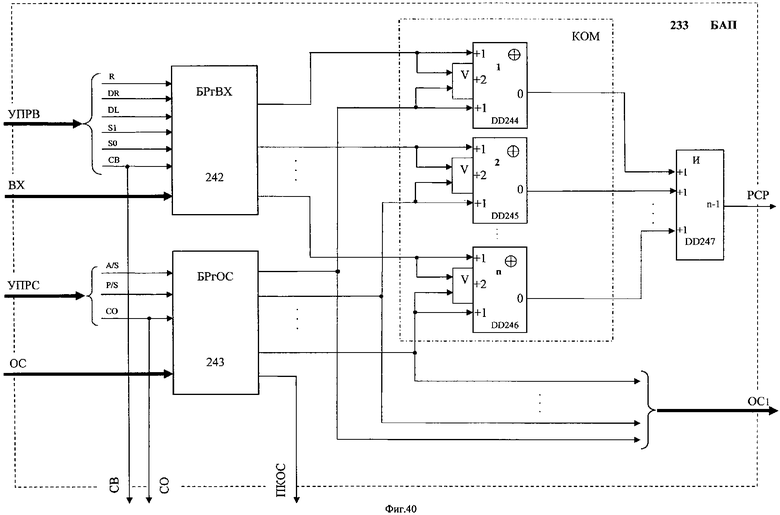

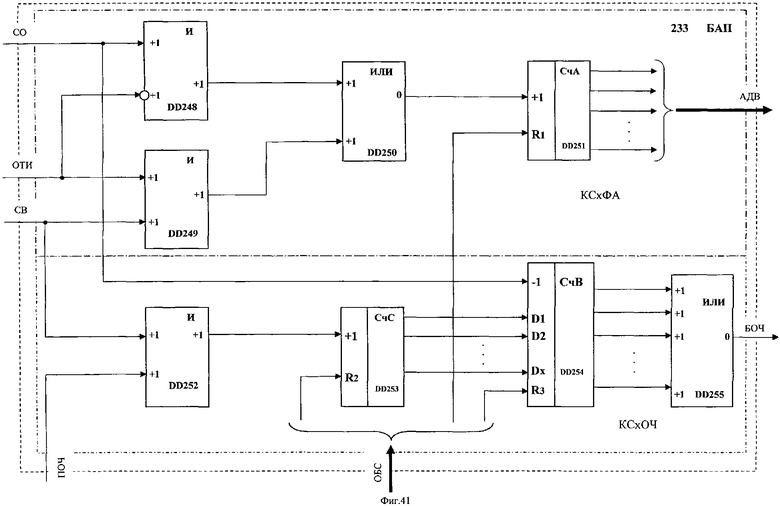

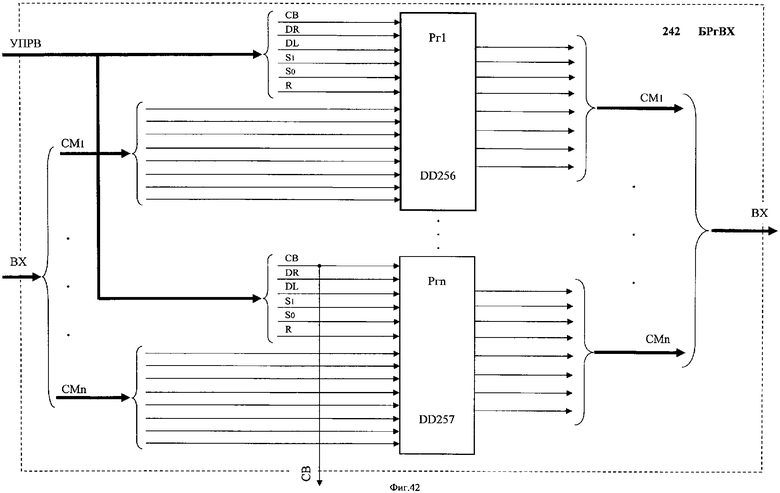

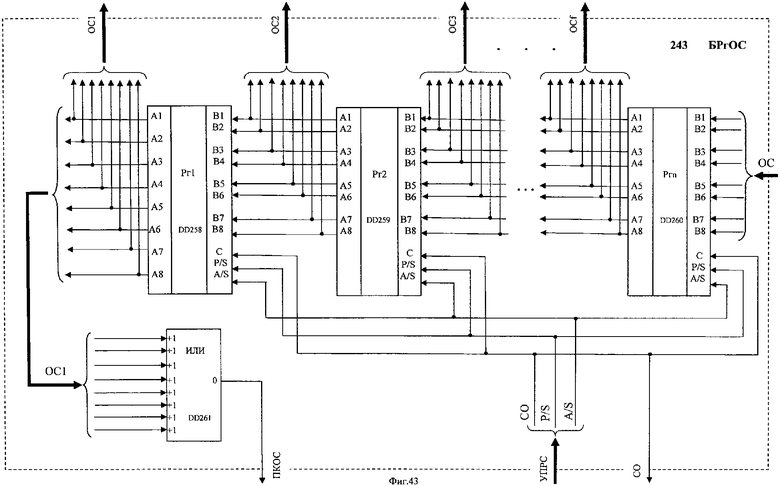

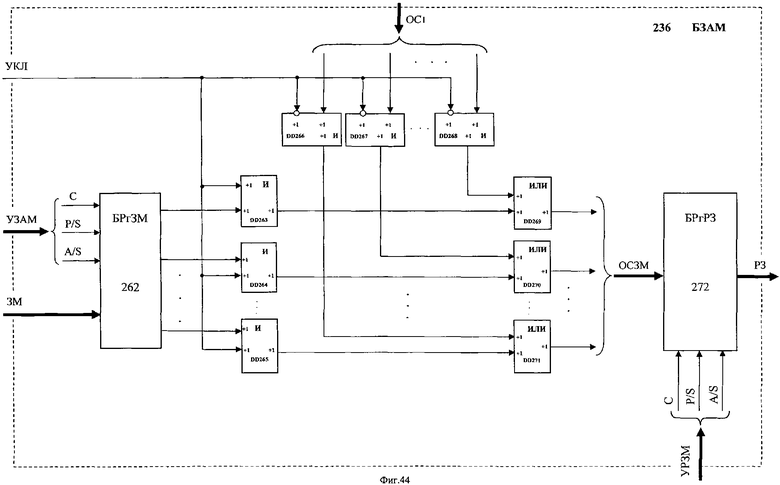

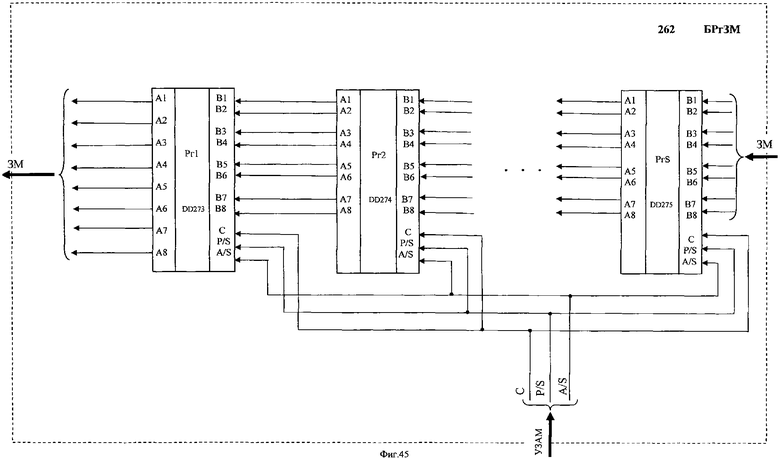

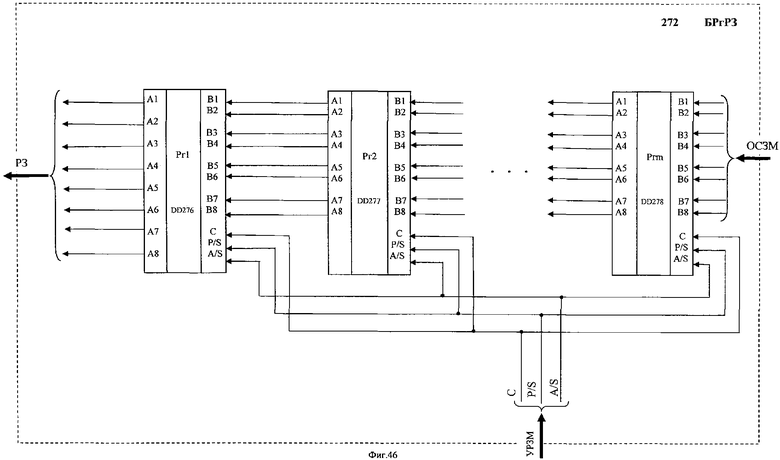

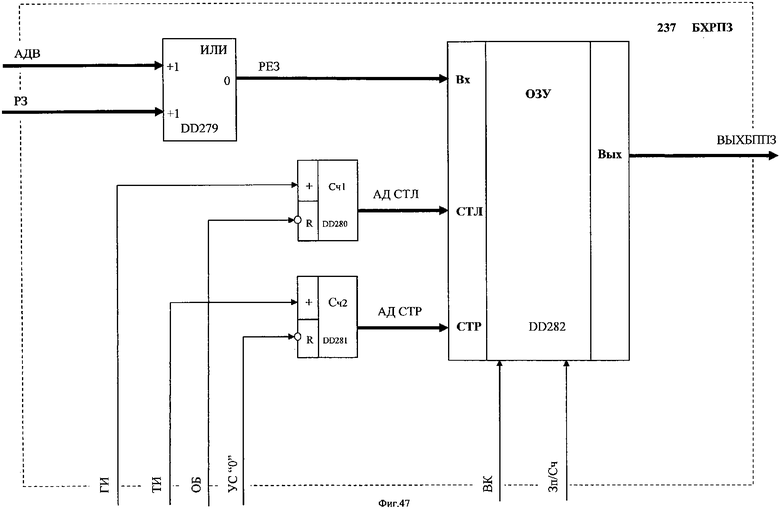

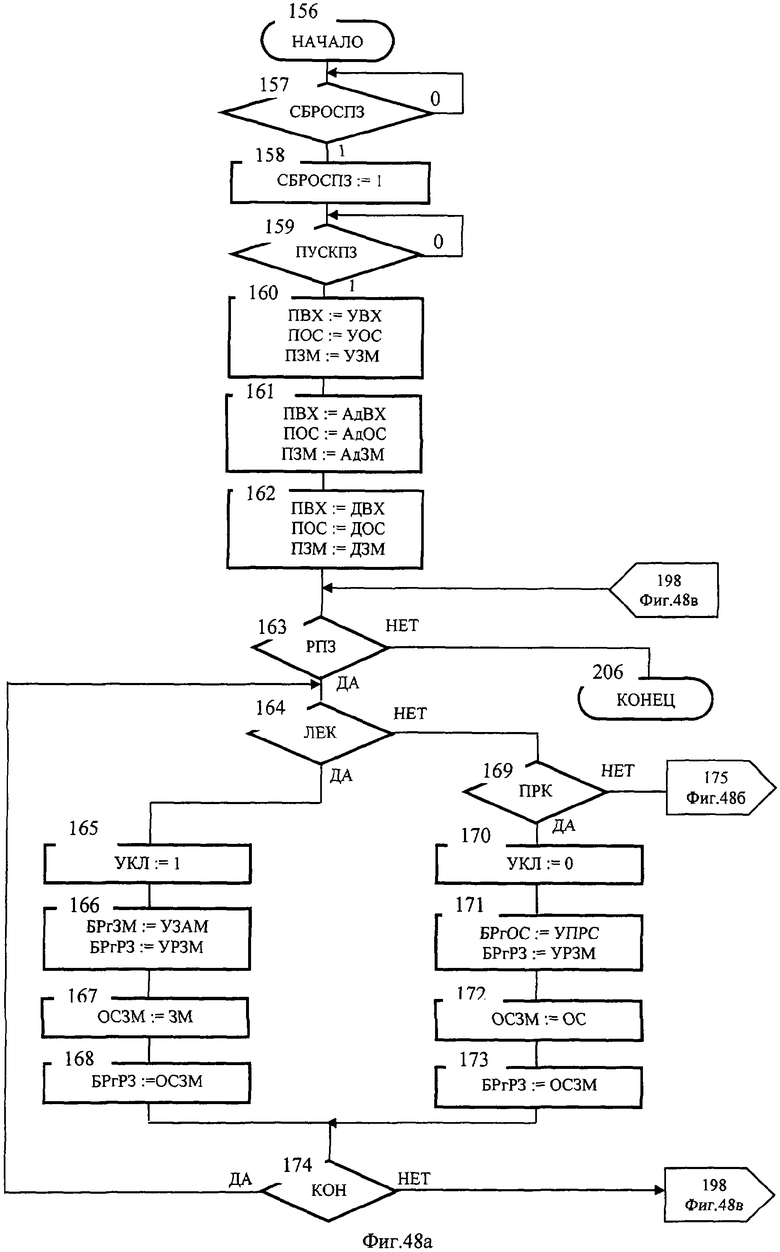

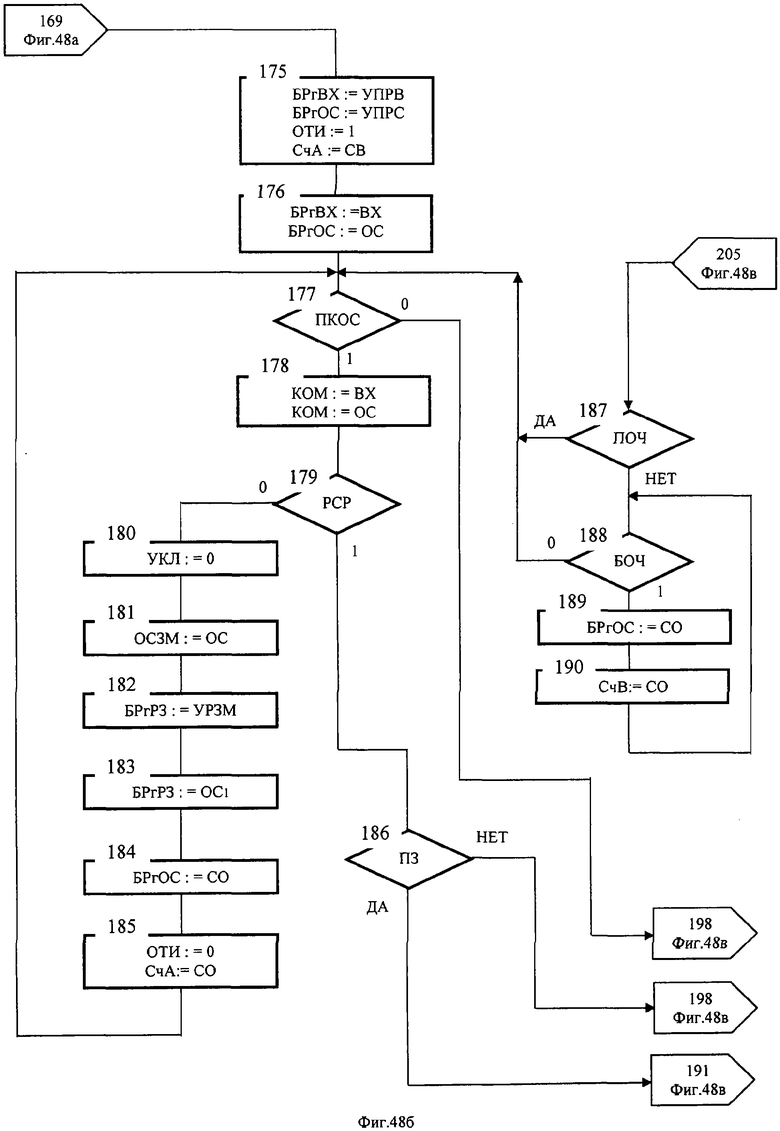

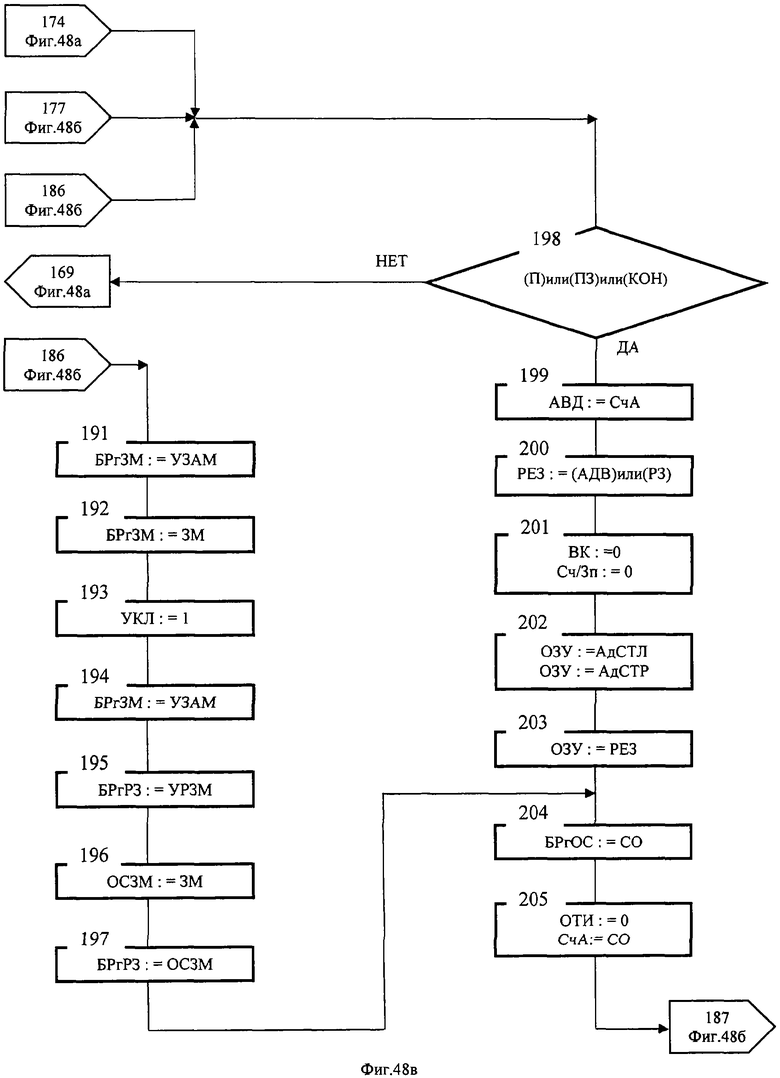

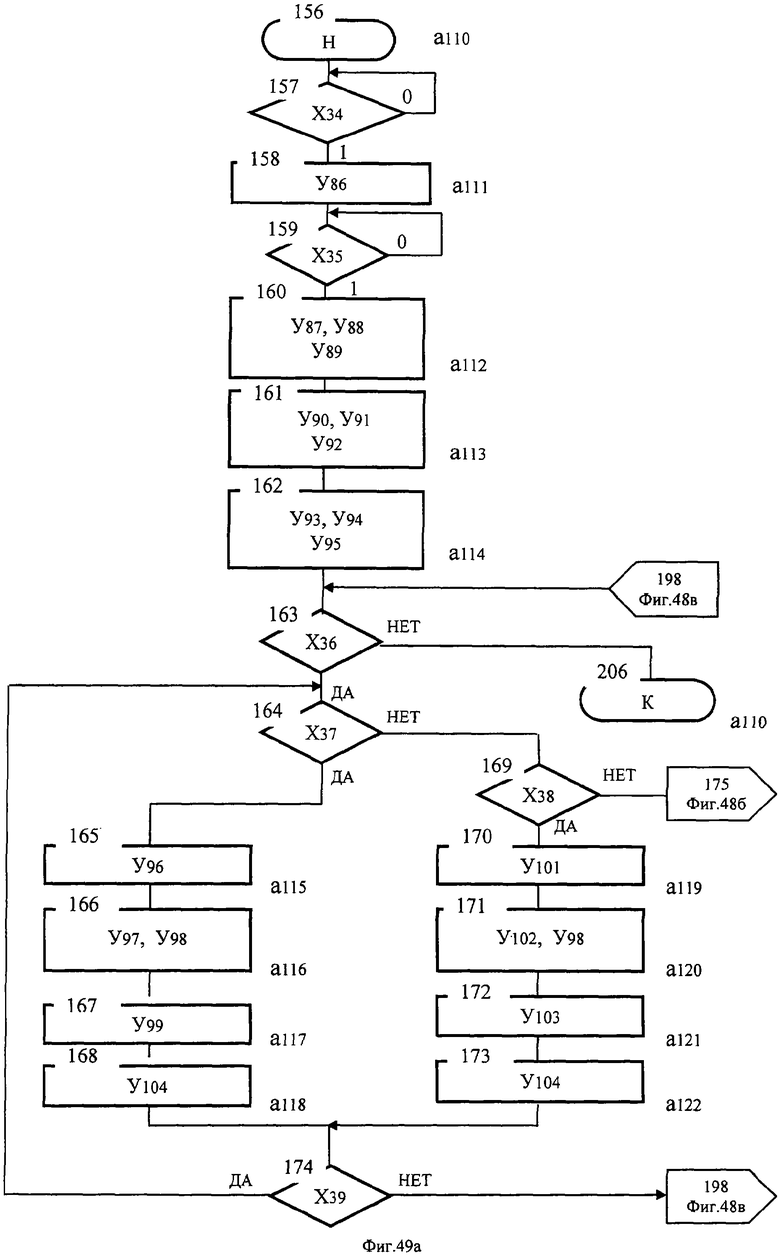

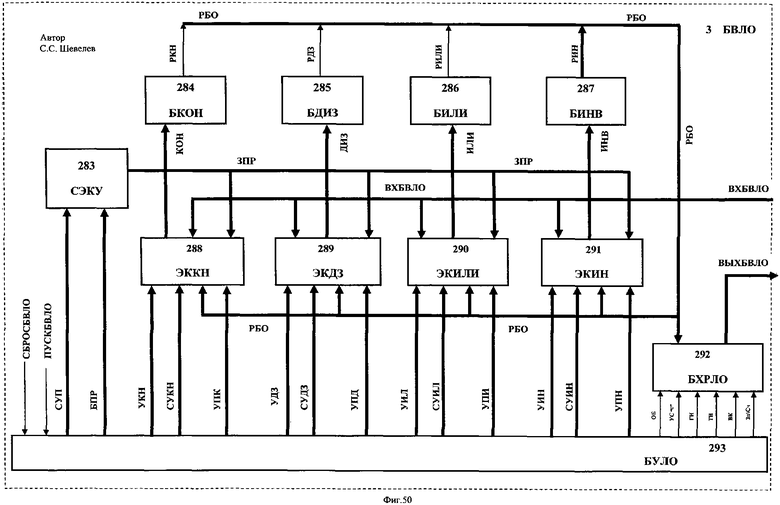

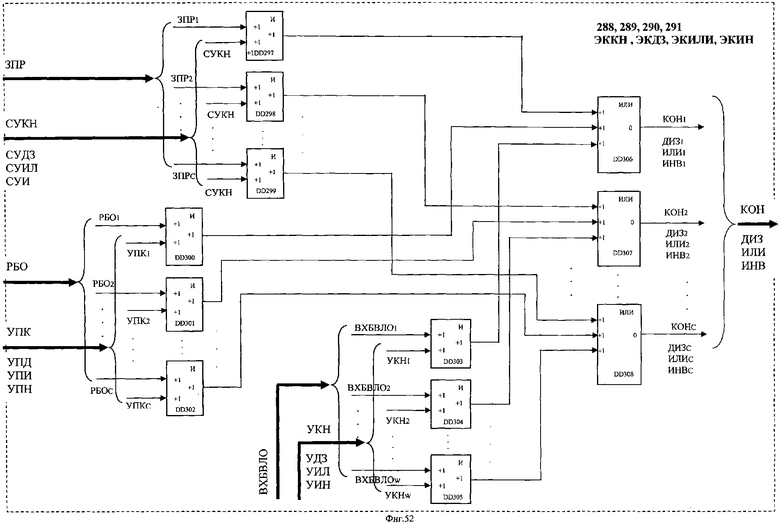

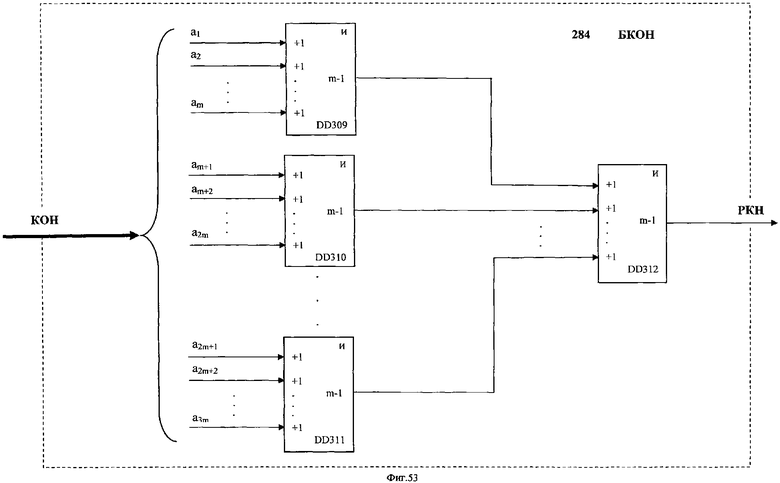

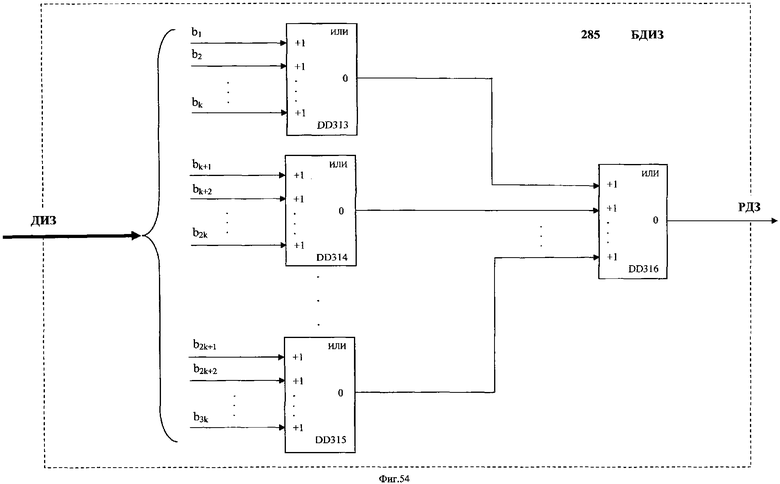

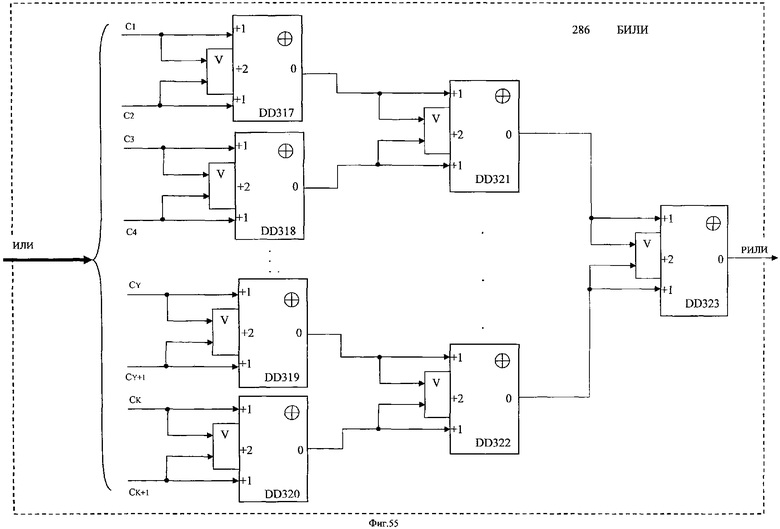

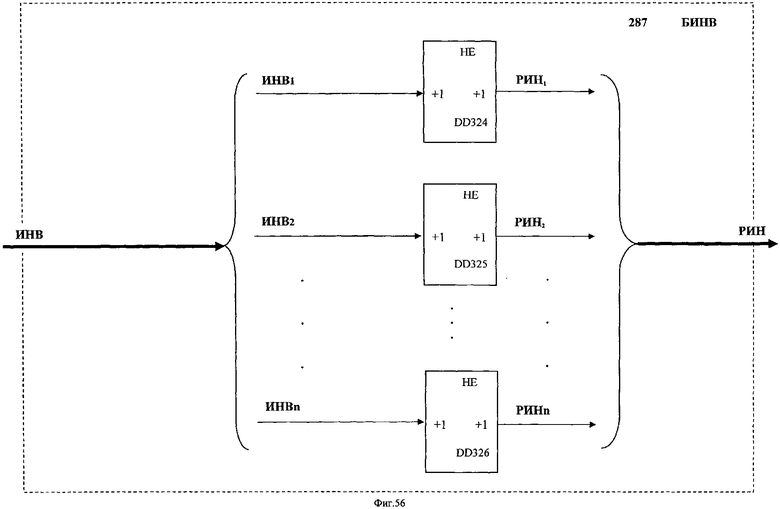

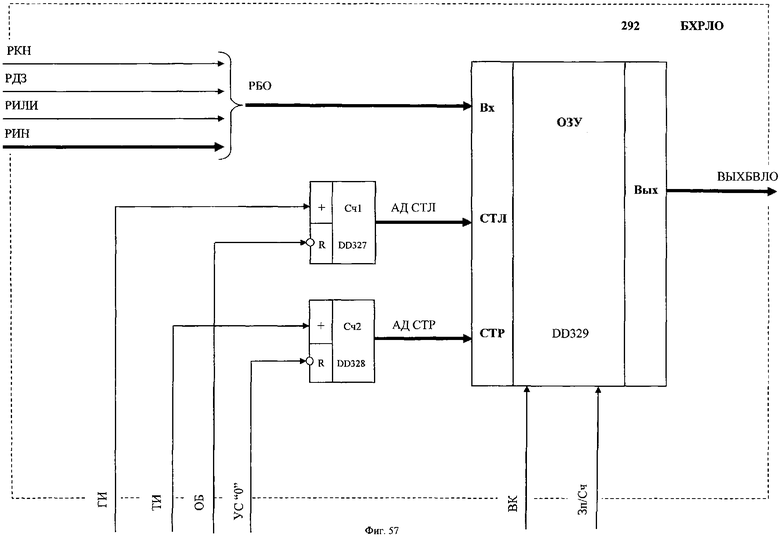

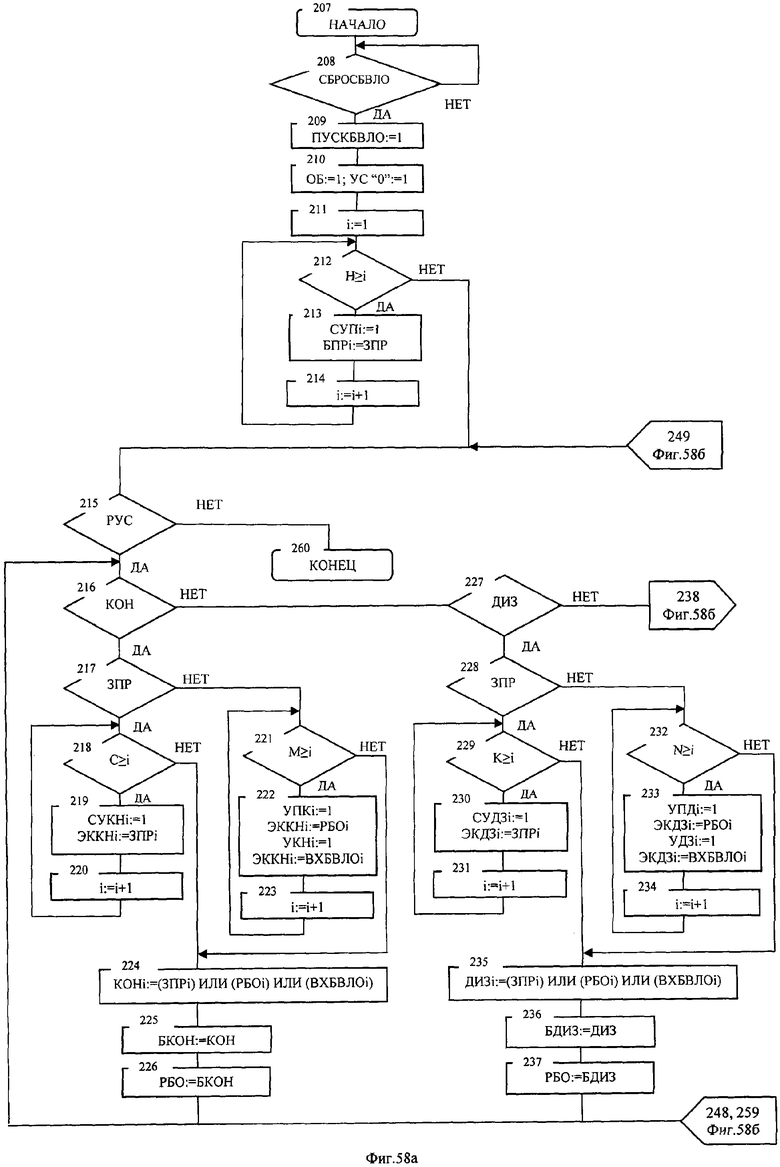

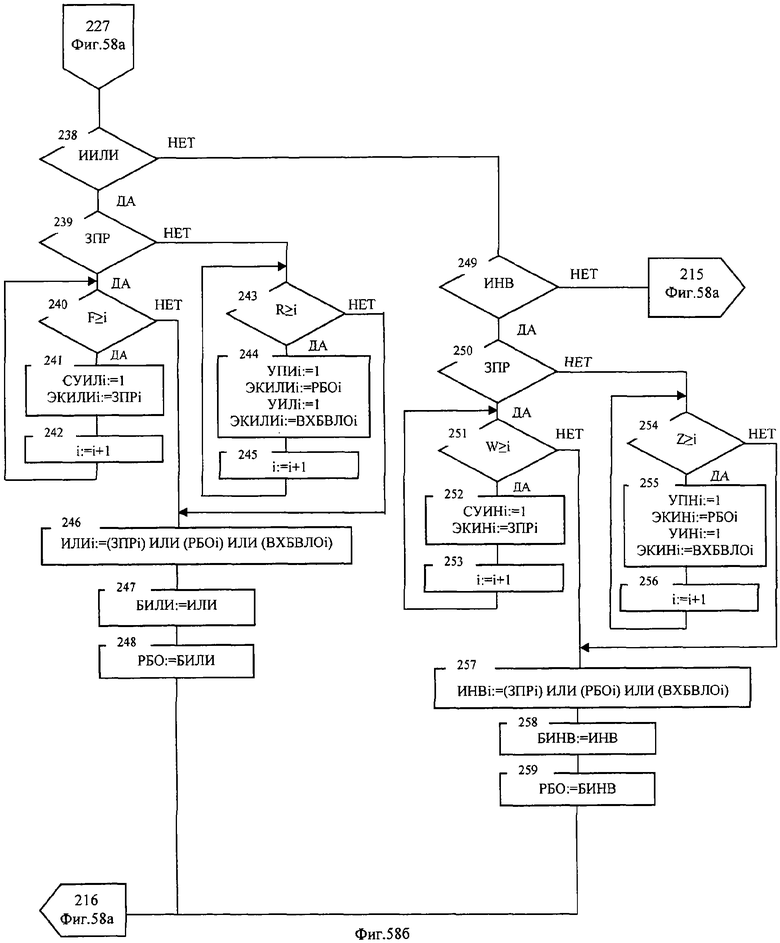

Изобретение относится к техническим средствам автоматики и вычислительной техники и может быть использовано для синтеза вычислительных систем, для создания быстродействующих и производительных цифровых процессоров, выполняющих основные арифметические операции, осуществляющих поисковые функции и операции замены вхождений в обрабатываемых словах, а также выполняющих логические операции. Техническим результатом является расширение функциональных возможностей и повышение надежности работы процессора. Устройство содержит блок выполнения арифметических операций над числами, представленными в прямых кодах, блок параллельного поиска и замены вхождений в обрабатываемых словах, блок выполнения логических операций, блок хранения результатов, блок управления. 71 ил., 4 табл.

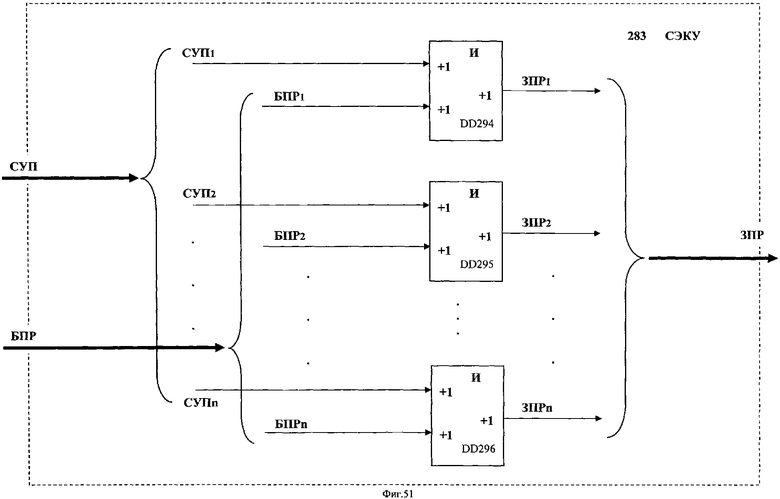

Арифметико-символьный процессор, содержащий блок хранения результатов, блок управления, отличающийся тем, что дополнительно введены: блок выполнения арифметических операций над числами, представленными в прямых кодах, блок параллельного поиска и замены вхождений в обрабатываемых словах, блок выполнения логических операций, причем первый и второй управляющие выходы блока управления арифметико-символьного процессора соединены соответственно с первым и вторым управляющими входами блока выполнения арифметических операций над числами, представленными в прямых кодах, информационный выход которого соединен с информационным входом блока выполнения арифметических операций над числами, представленными в прямых кодах, с информационным входом блока параллельного поиска и замены вхождений в обрабатываемых словах, с информационным входом блока выполнения логических операций, с первым информационным входом блока хранения результатов, с первого по шестой управляющие входы которого соединены соответственно с седьмым по двенадцатый управляющими выходами блока управления арифметико-символьного процессора, третий и четвертый управляющие выходы которого соединены соответственно с первым и вторым управляющими входами блока параллельного поиска и замены вхождений в обрабатываемых словах, информационный выход которого соединен с информационным входом блока выполнения арифметических операций над числами, представленными в прямых кодах, с информационным входом блока параллельного поиска и замены вхождений в обрабатываемых словах, с информационным входом блока выполнения логических операций, со вторым информационным входом блока хранения результатов, пятый и шестой управляющие выходы блока управления арифметико-символьного процессора соединены соответственно с первым и вторым управляющими входами блока выполнения логических операций, информационный выход которого соединен с информационным входом блока выполнения арифметических операций над числами, представленными в прямых кодах, с информационным входом блока параллельного поиска и замены вхождений в обрабатываемых словах, с информационным входом блока выполнения логических операций, с третьим информационным входом блока хранения результатов, первый и второй управляющие входы "СБРОСАСП" и "ПУСКАСП" блока управления арифметико-символьного процессора являются внешними входами арифметико-символьного процессора.

| УСТРОЙСТВО ПОИСКА И ЗАМЕНЫ ПРОИЗВОЛЬНЫХ ВХОЖДЕНИЙ В СЛОВАХ ТЕКСТА | 2002 |

|

RU2250493C2 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2246752C1 |

| ПРОЦЕССОР | 1990 |

|

SU1826787A1 |

| US 4896133 A, 23.01.1990 | |||

| НЕШУМОВА К.А | |||

| Электронные вычислительные машины и системы | |||

| М.: Высшая школа, 1989, с.252-254. | |||

Авторы

Даты

2008-01-27—Публикация

2005-12-23—Подача