Устройство может быть использовано в универсальных вычислительных машинах, работающих в двоичной и десятичной системах счисления, в режимах с фиксированной и плавающей запятой, при представлении информации в виде мащин.ных слоев и алфавитноцифровых символов, имеющих возможность щирокого наращивания внещних устройств.

Известны процессоры, которые содерлсат арифметическое и логическое устройство, разбитое на секции, накопитель данных с адресацией словами и посимвольной адресацией, устройство управления, исполняющее операции в соответствии с последовательностью команд программы, встроенный мультиплексный и селекторный каналы для связи с набором внещних устройств, работающих одновременно с арифметическим и логическим устройством, блок выделения символа, блок числа, регистр адреса накопителя.

Предлагаемый процессор отличается тем, что он содержит схему задания конфигурации соединения секций арифметического и логического устройства и подачи сигналов управления операциями, которая связана с устройством управления, схему управления умножением и схему управления делением, также подключенные к устройству управления и через схему задания конфигурации взаимосвязанные с соответствующими секциями арифметического и логического устройства. Группа секций арифметического и логического устройства связана через схему задания конфигурации и общий для селекторного и мультиплексного каналов блок регистра адреса устройств ввода-вывода с блоком централизованного формирования адресов, накопителя, поступающих от различных источников. Блок

выработки текущего адреса по управляющему слову, поступающему из блока числа накопителя или из дежурного регистра селекторного канала, взаимосвязанный с дежурным регистром селекторного канала и подсоедивенный к блоку выделения символа, подключенному к распределителю символов, связанному с общим буферным регистром символа селекторного и мультиплексного каналов и блоком записи символа и контроля на пропадание символов и через схему задания конфигурации- со входами соответствующих секций арифметического и логического устройства. Блок числа накопителя связан с блоком записи символа, с блоком выделения символа, через распределитель слов-со входом блока выработки текущего адреса и дежурным регистром селекторного канала через схему задания конфигурации - со входами всех секций арифметического и логического устройза счет использования отдельных блоков для выполнения различных функций.

С целью задания переменного максимального адреса и последовательности адресов, по которым разрешен обмен между накопителем и устройствами ввода-вывода, и признаков окончания обмена, в нем блок выработки текущего адреса по управляющему слову содержит блок операций, блок служебных признаков, блок текущего адреса, схему сравнения и блок управления обменом, .причем блоКн операций, слул ебпых признаков и текущего адреса взаимосвязаны с распределителем слое и дежурным регистром селекторного канала. Выход блока операций подключен ко входу блока управления обменом, который взаимосвязан с блоком служебных признаков, схемой сравнения и блоком текущего адреса. Выходы блоков служебных признаков и текущего адреса подключены соответственно к первому и второму входам схемы сравнения, третий вход которой соединен с буферным регистром символа. Вход блока текущего адреса соединен со схемой задания конфигураций, а второй выход подключен к блоку централизованного формирования адреса.

С целью обнаружения лишних сИлМволов или пропадания символов, вводимых из устройства ввода, блок задиси символа содержит блок замены символа при записи, схему коррекции контрольного разряда слова, дешифратор кода номера символа, вход которого подключен к блоку выработки текущего адреса. Выход дешифратора соединен со вторыми входами схемы коррекции контрольного разряда и блока замены символа, первые входы которых соединены с распределителем символа, а третьи- с блоком числа. Выход схемы коррекции контрольного разряда связан с обмоткой записи контрольного разряда накопителя, выход блока замены символов - с обмотками записи слова накопителя шинами, позволяющими управлять записью слова, состоящего из п символов, один из которых является неполноразрядным. Это позволяет обнаружить сдвиги информации при вводе в накопитель за счет нарушения соответствия между информацией слова и его контрольным разрядом в накопителе при записи полноразрядного си.мвола на место яеполноразрядного символа з слове.

С целью сокращения оборудования, схема задания конфигураций соединений секций арифметического и логического устройства содержит блок разбивки секций, взаимосвязанный со схемой устройства управления, со схемами управления делением и умножением с одной стороны и с соответствующей группой секций арифметического и логического устройства с другой, входы которого соединены с выходами блоков формирования слов и символов, взаимосвязанных с одной стороны с распределителями слов и символов и с другой - с соответствующи.ми группами секций арифметического и логического устройства, а выходы

блока разбивки секций присоединены к вентилям, объединяющим вход и выход любых двух секций арифметического и логического устройства. Выходы соответствующих групп

секций последнего связаны с общим регистром адреса устройств ввода-вывода селекторного и мультиплексного каналов, с блоком выработки текущего адреса по управляющему слову и с блоком централизоваппого

формирования адресов.

Это позволяет организовывать из отдельпых секций арифметического и логического устройства различпые по назначению сумматоры для обработки слов, символов и адресов в

различных режимах работы (с плавающей и фиксированной запятой, с целыми числами) и с операндами в различных системах счисления (двоичной, десятичной).

С целью увеличения производительности процессора при выполнении операций деления, в нем схема управления делением содержит первый и второй вентили корректировки частного, соответственно подключенные по входам к единичному и нулевому входам младшего разряда второго регистра младшей секции арифметического и логического устройства. Вход управления вентилей корректировки связан с соответствующим выходом устройства управления арифметическими и логическими операциями и с прямым и инверсным выходами разряда знака третьего регистра старщей секции арнфметического и логического устройства, которые подключены ко входам

управления 3-го и 4-го вентилей, дополнительные входы которых связаны с шиной сдвига влево устройства управления арифметическими и логическими операциями и прямым и инверсным выходами старшего разряда третьего

регистра старшей секции арифметического п логического устройства. Выходы 3-го и 4-го вентилей подключены к схеме формирования сдвигов влево во втором и третьем регистрах объединенных секций арифметического и логпческого устройства, причем выход старшего значащего разряда третьего регистра старшей секции связан со входом разряда знака того же регистра и со входом младшего разряда второго регистра младшей секции. 1.11ина

сдвига влево через вентиль, управляющий вход которого через схему анализа делимого и делителя при нормализации подключеп к старшим значащим разрядам первого и третьего регистров старшей секции, п сборку, связапную по дополнительному входу с шиной сдвига вправо устройства управления арифметическими и логическими операциями и первым входом вентиля управления сдвигами вправо на заданное число сдвигов, соединена со счетчиком формирования числа сдвигов при нормализации, выход которого через ипвертор связан со вторым входом последнего вентиля, выход которого подключен к шине передачи содержимого разряда знака в старший зпаных секций арифметического и логического устройства.

Это позволяет увеличить быстродействие арифметического и логического устройства при выполнении операций деления при минимальных затратах оборудования и организовать экономичную схему получения конечного остатка.

С целью сокращения оборудования процессора при выполнении операций умножения двоичных чисел и умножения двоично-десятичных чисел, в нем схема управления умножением содержит дешифратор, связанный непосредственно с прямым и инверсным входами разряда знака первого регистра старшей секции и с прямыми и инверсными выходами двух младших разрядов второго регистра младшей секции, выходы которого связаны с шинами сигналов очередной микрооперации устройства управления арифметическим и логическим устройством. Шина сдвига вправо через вентиль, управляюший вход которого соединен с шиной сигнала десятичного умножения, подключенной к управляющим входам вентилей переноса, соединена со входом сдвиговых цепей разряда знака первого регистра старшей секции, выход которых связан со входом сдвиговых цепей разряда знака второго регистра старшей секции, а выход последних соединен со входом сдвиговых ценей разряда зиака третьего регистра старшей секции. Выход переноса этого разряда через вентиль иереноса соединен со счетным входом разряда знака второго регистра, а выход переноса последнего связан со счегным входом разряда знака первого регистра старшей секции арифметического и логического устройства.

Это позволяет при выполнении операции двоичного умножения организовать схему тетрады переполнения без введения специального оборудования дополнительной тетрады, а при выполнении операций двоичного умножения организовать схему анализа множителя без введения в нее специальной аппаратуры запоминания.

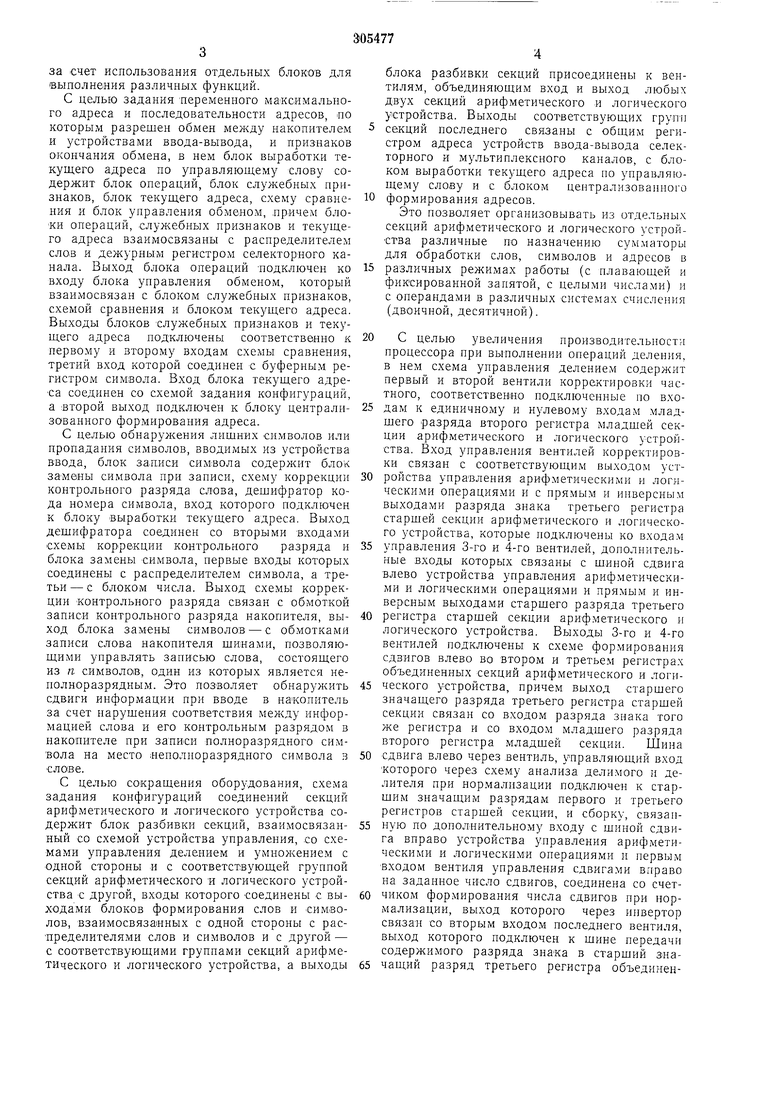

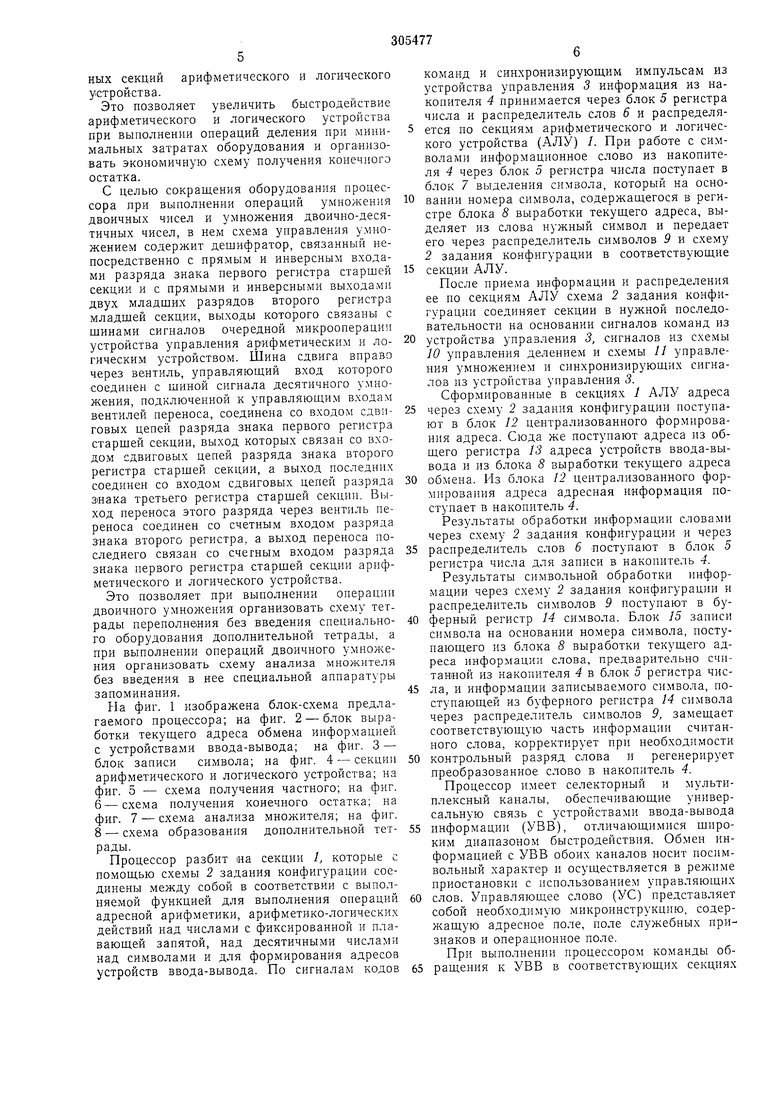

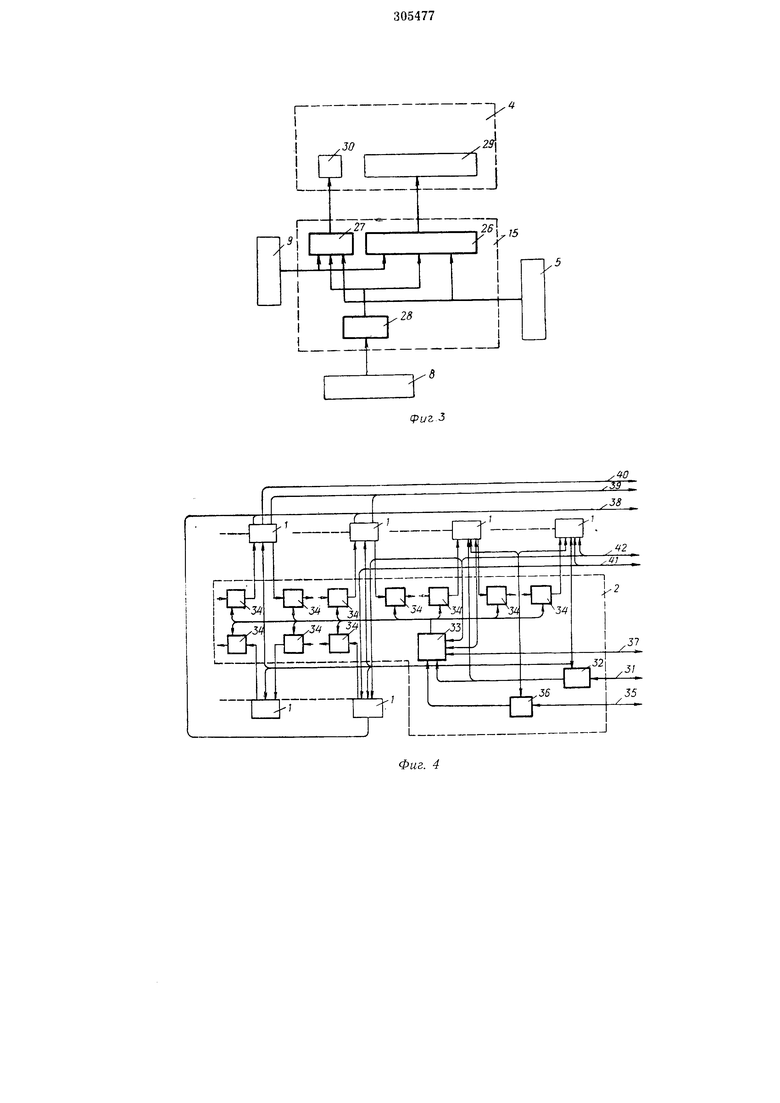

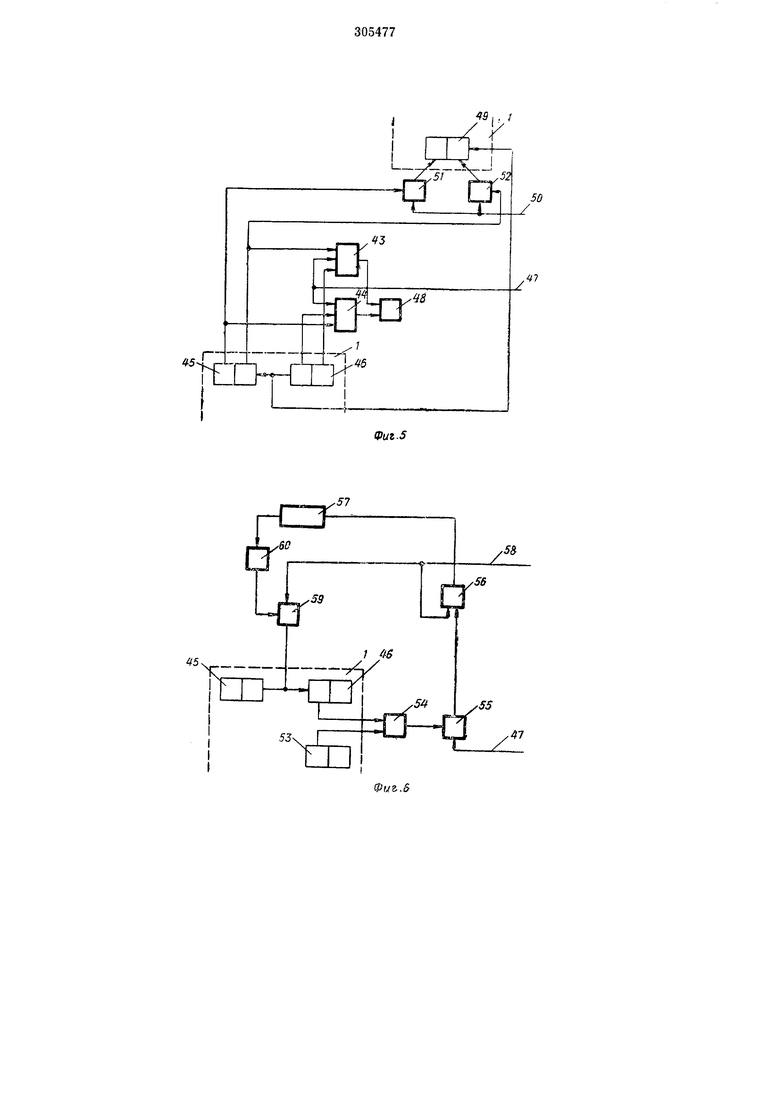

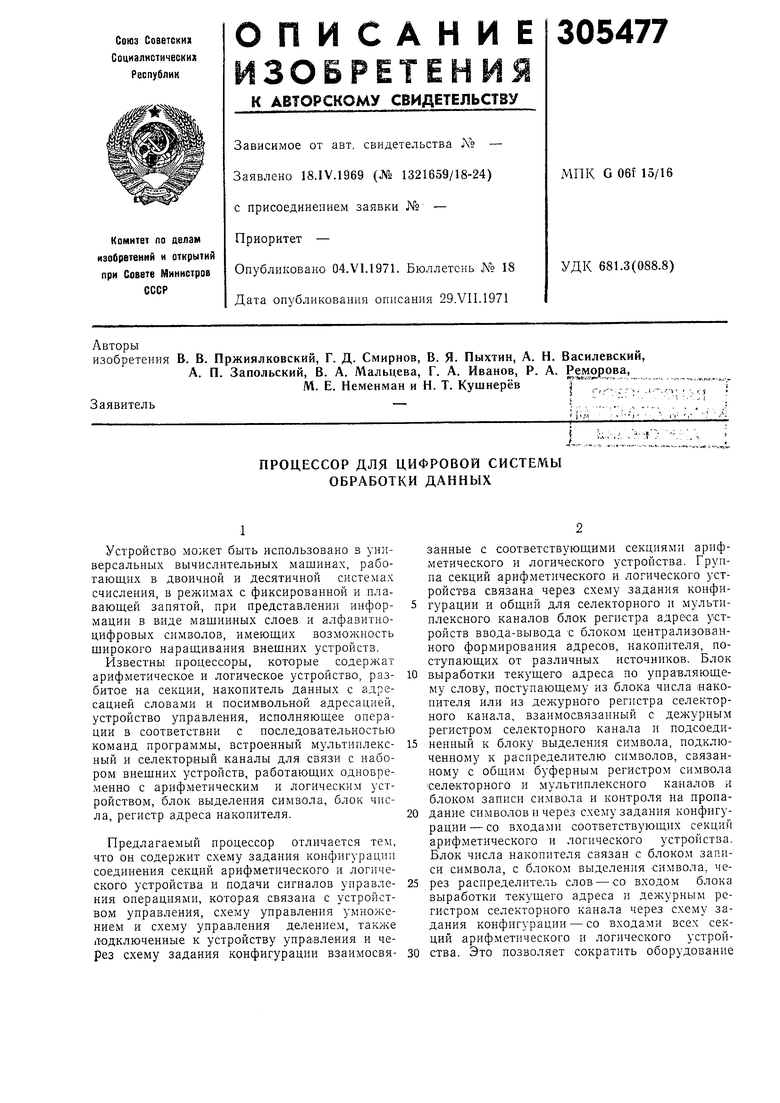

На фиг. 1 изображена блок-схема предлагаемого процессора; на фиг. 2 - блок выработки текущего адреса обмена информацией с устройствами ввода-вывода; на фиг. 3 - блок записи символа; на фиг. 4 - секции арифметического и логического устройства; на фиг. 5 - схема получения частного; на фиг. 6-схема получения конечного остатка; на фиг. 7 - схема анализа множителя; на фиг. 8 - схема образования дополнительной тетрады.

Процессор разбит иа секции 1, которые с помощью схемы 2 задания конфигурации соединены между собой в соответствии с выполняемой функцией для выполнения операций адресной арифметики, арифметико-логических действий над числами с фиксированной и плавающей запятой, над десятичными числами над символами и для формирования адресов устройств ввода-вывода. По сигналам кодов

команд и синхронизирующим импульсам из устройства управления 3 информация из накопителя 4 принимается через блок 5 регистра числа и распределитель слов 6 и распределяется по секциям арифметического и логического устройства (АЛУ) 1. При работе с символами информационное слово из накопителя 4 через блок 5 регистра числа поступает в блок 7 выделения символа, который на основании номера символа, содержащегося в регистре блока 5 выработки текущего адреса, выделяет из слова нужный символ и передает его через распределитель символов 9 и схему 2 задания конфигурации в соответствующие

секции АЛУ.

После приема информации и распределения ее по секциям АЛУ схема 2 задания конфигурации соединяет секции в нужной последовательности на основании сигналов команд из

устройства управления 3, сигналов из схемы 10 управления делением и схемы // управления умножением и синхронизирующих сигналов из устройства управления 3.

Сформированные в секциях / АЛУ адреса

через схему 2 задания конфигурации поступают в блок 12 централизованного формирования адреса. Сюда же поступают адреса из общего регистра 13 адреса устройств ввода-вывода и из блока 8 выработки текущего адреса

обмена. Пз блока 12 централизованного фюрмирования адреса адресная информация поступает в накопитель 4.

Результаты обработки информации словами через схему 2 задания конфигурации и через

распределитель слов 6 поступают в блок 5 регистра числа для записи в накопитель 4.

Результаты символьной обработки информации через схему 2 задания конфигурации и распределитель символов 9 поступают в буферный регистр 14 символа. Блок 15 записи символа на основании номера символа, поступающего из блока 8 выработки текущего адреса информации слова, предварительно считанной из накопителя 4 в блок 5 регистра числа, и информации записываемого символа, поступающей из буферного регистра 14 символа через распределитель символов 9, замещает соответствующую часть информации считанного слова, корректирует при необходимости

контрольный разряд слова и регенерирует преобразованное слово в накопитель 4.

Процессор имеет селекторный и мультиплексный каналы, обеспечивающие универсальную связь с устройствами ввода-вывода

информации (УВВ), отличающимися широким диапазоном быстродействия. Обмен информацией с УВВ обоих каналов носит посимвольный характер и осуществляется в режиме приостановки с использованием управляющих

слов. Управляющее слово (УС) представляет собой необходимую микроинструкцию, содержащую адресное поле, поле служебных признаков и операционное иоле. При выполнении процессором команды обАЛУ предварительно формируется адрес этого устройства. Использование для этой цели оборудования АЛУ позволяет сократить общее оборудование процессора. Сформированный адрес поступает через схему 2 задания конфигурации (СЗК) в общий регистр ГЗ адреса внешних устройств селекторного и мультиплексного каналов, который выбирает соответствующее УВВ при помощи щин выборки 16.

Конкретный код операции через схему 2 задания конфигурации, распределитель символов 9 и буферный регистр 14 символа отсылается в УВВ. По окончании команды вводавывода процессор приступает к обработке следующей комаиды. При обращении к УВВ с командой ввода-вывода механизм УВВ начинает отрабатывать сообщенный код операции, а в ячейку накопителя 4 с адресом, соответствующим адресу УВВ (дежурный регистр УС), записывается управляющее слово.

Ячейка дежурного регистра адресуется передачей адреса из общего регистра 13 адреса УВВ в блок 12 централизованного формирования адреса процессора.

При выполнении команды ввода-вывода с УВВ селекторного канала управляющее слово поступает и в дежурный регистр П селекторного канала.

Это делает возможным обмен информацией с УВВ со скоростью имеющегося накопителя.

УВВ, отрабатывая код олерации но вводувыводу информации, Б нужные моменты посылает в процессор запросы на необходимость в обмене информации (символом). При наличии такого запроса на щинах 18, 19 запроса УВВ селекторного канала или мультиплексного канала 19 выполнение процессором текущей команды приостанавливается, запрос соответствующего УБВ преобразуется в его адрес, который заносится в общий регистр адреса 13 УВВ. Согласно содержимому регистра адреса производится выборка УВВ (аналогично выборке при выполнении команд обращения к УВВ). При этом по запросу УВВ мультиплексного капала происходит адресация соответствующего дежурного регистра управляющего слова, расположенного в накопителе 4, для чего содержимое общего регистра адреса УВВ, как и при командах ввода-вывода, передается в блок 12 централизованного формирования адреса. По запросу УВВ селекторного канала производится обращение к дежурному регистру 17 этого канала. В обоих случаях УС считывается в общий для каналов блок 8 выработки текущего адреса обмена. При обмене информацией с УВВ мультинлексного канала УС поступает из накопителя через распределитель 6, при обмене инфор.мацией с УВВ селекторного канала из дежуряого регистра 17 селекторного канала. Соответствующие компоненты УС заносятся:

адресное поле - в блок 21 текущего адреса, ноле служебных признаков - в блок 22 служебных признаков, операционное поле - в блок операций 23.

Блок операций 23 согласно информации операционного поля УС устанавливает необходимый режим выполнения инструкции УС, для чего его выход подключен ко входу блока 24 управления обменом. Кроме того, блок

24 получает необходимую исходную информацию из блока 22 служебных призпаков и может измепять ее, если необходимо, в определенные моменты в процессе обмена.

Выходы блоков 21, 22 служебных признаков

и текущего адреса подключены к первому и второму входам схемы сравнения 25, третий вход которой соединен с источником символа обмена - буферным регистром символа 14. Такая схема блока 8 выработки текущего адреса позволяет задавать переменный максимальный адрес возможного обмена и переменный признак окончания обмена.

Максимальный адрес возможного обмен; для конкретного УВВ прн организации конкретного обмена задается в иоле служебных признаков УС. В нем задается и признак окончания обмена для данного массива информации. Схема сравнения 25 сравнивает необходимые компоненты блоков 21, 22 служебных

признаков и текущего адреса и регистра символа 14 обмена согласно разновидности операции, заданной в определенном ноле УС. Так, например, при вводе информации в накопитель из УВВ в поле служебных признаков

можно задать граничный адрес ячейки или листа накопителя. Таким образом, УВВ может вводить информацию в накопитель последовательно символ за символом, начиная с начального адреса, указанного в адресном поло

первоначального УС.

После ввода каждого очередного символа в накопитель адресное поле в блоке 21 текущего адреса модифицируется на «I. подготавливая адрес для ввода следующего символа. При выводе модификация адреса аналогична. При равенстве информации адресного поля и граничного адреса поля служебных признаков обмен оканчивается. Признаком окончания обмена может служить также совпадение информации обменного символа с конкретным эталоном, заданным в поле служебных признаков.

Если адрес, заданный адресным полем, оказывается больше установленного граничного

адреса, происходят блокировка обмена информацией, остаиов УВВ и выработка сигнала сбоя с установкой соответствующего признака. Аналогичная ситуация создается и при переполнении адресного поля. По окончании

обмена каждым символом модифицированное УС (с измененной информацией адресного поля и возможной иЗдМененной информацией поля служебных признаков) из блока 8 выработки текущего адреса передается в источплексного канала в накопителе 4 или дежурный регистр 17 управляющего слова селекторного канала).

При окончании обмена заданным количеством информации с УВВ селекторного канала УС из дежурного регистра 17 селекторного канала передается в дежурный регистр накопителя 4 согласно адресу УВВ, с которым происходил обмен. Символы, вводимые по запросам УВВ как мультиплексного, так и селекторного каналов, с кодовых шин 20 символа каналов через общий для каналов буферный регистр символов 14 и через распределитель символов 9 поступают в блок 15 записи символа. При выводе символ из накопителя 4 через блок 7 выделения символа, распределитель символов 9 и буферный регистр символа 14 поступает в канал по щинам 20. Для посимвольной адресации накопителя часть информации адресного поля (код номера символа в ячейке накопителя) из блока 8 выработки текущего адреса подается на блок 7 выделения символа и блок 15 записи символа, а другая часть, представляющая адрес ячейки накопителя - в блок 12 централизованного формирования адреса.

Механизм посимвольной адресации накопителя при обмене информацией с УВВ используется также в командах посимвольных операций процессора, для чего из соответствующих секций 1 АЛУ через схему 2 задания конфигурации часть адреса, представляющая код номера символа в ячейке накопителя 4, поступает в блок 8 выработки текущего адреса, а другая часть, представляющая адрес ячейки накопителя, - в блок 12 централизованного формирования адреса. При этом символ при записи из соответствующей группы секций / АЛУ через схему 2 задания конфигурации, распределитель символов 9 и буферный регистр символа 14 поступает в блок 15 записи символа. При чтении символ из блока 5 регистра числа через блок 7 выделения символа, распределитель символов 9 и схему 2 задания конфигурации поступает в соответствующую группу секций 1 АЛУ.

Реализация некоторых функций взаимодействия процессора с УВВ на оборудовании АЛУ и устройства управления с одной стопоны и реализация некоторых функций выполнения команд посимвольных операций на оборудовании взаимодействия с УВВ с другой, а также использования централизованных каналов передачи информации при выполнении процессором различных функций позволяют значительно сократить общее оборудование процессора.

Реализация блока выработки текущего адреса обмена информацией с УВВ по приведенной схеме (фиг. 2) позволяет мин-имизировать оборудование при достижении гибкости управления процессами обмена.

Использование общего оборудования в двухканальной связи процессора с УВВ (блока 13 адреса УВВ, буферного регистра символа //.

блока 8 выработки текущего адреса) позволяет сократить оборудование связи процессооа с УВВ. Для посимвольного ввода информации служит блок /5 записи символа (фиг. 3). Символ записывается путем регенерации считанного слова с частичным замещением информации в нем и коррекцией контрольного разряда слова. Считанное из накопителя 4 слово через

блок 5 регистра числа поступает в блок 15 записи символа, в блок 26 его замены и на схему 27 коррекции контрольного разряда. На эти же блоки поступает символ из распределителя символов 9. Из блока 8 выработки

текуп его адреса на дещифратор 28 поступает код номера символа - адрес .поля информации, подлежащей замещению вводимым символом. Этот дещифратор управляет процессом замещения информации при ее регенерации в

блоке замены 26, выходы которого соединены с обмотками записи 29 накопителя, и регенерации контрольного разряда слова с коррекцией в случае необходимости в схеме коорекции 27, выход которой соединен с обмоткой

записи контрольного разрядл 30 накопителя. Контрольный разряд корректируется в том случае, если количество замещаемых информационных единиц слова четное, а вводимого символа - нечетное и наоборот. Такой принцип требует строгого соответствия количества вводимых иксЬормационных разрядов количеству разрядов, замещаемых в слове. В противном случае слово записывается с несоответствующим значением контрольного пазряда и при очередном его чтении возникает сбой. Эта ситуация используется для обнаружения лищних символов или их пропадания при вводе информации из устройства ввода в накопитель. Для этого в последовательность вводимых символов введены неполноразрятные периодически повторяющиеся символы. При правильном вводе инсЬопмации неполноразрядные символы поступают в соответствующие им неполноразрядные поля замещения слов

накопителя. При пропаже во вводимом массиве хотя бы одного символа или появлении лищнего оказывается, что в неполнооазрядные поля замещения записываются полноразрядные символы, что приводит к несоответс ВИЮ КОНТРОЛЬНОГО разряда при чтении (сбою). Такая схема посимвольной записи приобретает особый эффект в случае некратности количеств разрядов слова накопителя и вводимого символа за счет отсутствия необходимости

введения избыточного оборудования (неполноразрядного по,яя замещения накопителя).

В связи с многообразием режимов работы арифметического и логического устройства оно выполнено в виде ряда секций / ((1;иг. 4).

В зависимости от режима работы процессора нужный набор секций коммутируется в определенной последовательности с помощью схемы 2 задания конфигураций. Информация в виде мащинных слов с выхода распределите11

пает на блок 32 формирования слов. Блок 32 управляет блоком 33 разбивки секций, а последеий с помощью вентилей 34 объединяет все секции / арифметического и логического устройства. После этого информация в виде машинных слов с блока 32 поступает на все секции арифметического и логического устройства.

Обработанная информация через блок 32 формирования слов и кодовые шины чисел 31 отсылается на вход распределителя слов 6 для пересылки ее в нужное устройство процессора. При посимвольной обработке в работе участвуют несколько секций арифметического и логического устройства. Информация из распределителя символов 9 по кодовым шинам 35 символа поступает на блок 36 формирования символов 36, который через блок 33 разбивки секций организует объединение соответствующих секций арифметического и логического устройства для работы с символами, поступающими на эти секции с блока 36 формирования символов. С этих секций обработанная информация поступает через блок 36 формирования символов и кодовые шины символов 35 на распределитель символов 9 для пересылки ее в нужное устройство процессора. При обработке адресной информации все секции объединяются в различные груипы в зависимости от типа обрабатываемого адреса блоком 33 разбивки секций по сигналам из устройства 3 управления через управляющие шины 37. С выходов соответствующих секций арифметического и логического устройства обработанная адресная информация поступает либо на блок 12 централизованного формирования адресов по кодовым щинам 38 адреса, либо на общий регистр адреса 13 устройств ввода-вывода селекторного и мультиплексного каналов по щинам 39 адресов каналов, либо на блок 8 выработки текущего адреса по щинам 40 номера символа. При выполнении операций деления сигналы со схемы 10 управления делением поступают через щины 41 управления делением на блок разбивки секций 33 и на отдельные группы секций арифметического и логического устройства. Блок 33 в зависимости от типа операций (с фиксированной и нлавающей запятой) коммутирует секции арифметического и логического устройства. Потенциалы, необходимые для выработки управляющих сигналов, поступают с соответствующих секций / по шинам 41 управления делением на схему 10 управления делением. При выполнении оепраций умножения сигналы со схемы управления умножением поступают через шины 42 управления умножением на отдельные секции / и блок 33 разбивки секций, коммутирующий секции арифметического и логического устройства в зависимости от типа операций умножения (с фиксированной запятой, плавающей запятой десятичного или умножения целых чисел). По шинам 42 управления умножением необходимые потенциалы лостуцают с секций арифметического и

12

логического устройства в схему управления умнол ением. В схему управления 10 делением входят схема получения частного (фиг. 5) и схема иолучения конечного остатка (фиг. 6). В схеме получения частного (фиг. 5) происходит деление без восстановления остатка с нропуском последовательного ряда «О или «1 с обязательной коррекцией последней цифры частного. При наличии в третьем регистре

частичного остатка тина 0,0000... 01... или 1, 11...10... соответствующее число нулей или единиц, находящихся между знаковым разрядом и противоположной но смыслу цифрой, с третьего регистра старщих секций / ариф

метического и логического устройства помещается путем сдвига во второй регистр младших секций 1. Затем корректируется последняя цифра частного. С этой целью на двух схемах «И 43 и 44 организован анализ состояния триггеров 45 и 46 знакового и первого разрядов третьего регистра старших секций арифметического и логического устройства. При совпадении вышеуказанных комбинаций чисел и при наличии сигнала на шине 47 сдвига схема 48 «ИЛИ формирует сигналы сдвига влево второго и третьего регистров секций 1 арифметического и логического устройства, иричем содержимое триггера 46 старшего разряда третьего регистра старшей секции попадает в триггер 49 младшего разряда второго регистра младшей секции. После очередной итерации или вычитания содержимого третьего и первого регистров соответствующих секций / содержимое младшего разряда 49 второго регистра младшей секции / корректируется в зависимости от знакового разряда частичного остатка. Для этого по шине 50 корректировки частного на схемы 5/ и 52 «И подается сигнал коррекции, и в зависимости от состояния триггера 45 знакового разряда третьего регистра секции / устанавливается в «О или «1 младший разряд 49 второго регистра младшей секции / арифметического и логического устройства.

В схеме получения конечного остатка (фиг. 6) иравильный конечный остаток получается при делении без восстановления остатка с пропуском последнего ряда «О или «1. По этот метод применим лишь для нормализованных

чисел. Поэтому перед началом деления происходит нормализация путем сдвига влево как делимого, так и делителя, причем число сдвигов фиксируется в специальном счетчике сдвигов. Старщий разряд 46 третьего регистра

старшей секции 1, где расположено делимое, и старший разряд 53 первого регистра той же секции /, где расиоложен делитель, анализируется схемой «И 54, а сдвиги - на схеме «И 55, куда подаются сигналы по шине сдвигов 47. С выхода схемы «И 55 сигналы сдвига подаются на первый и третий регистры секции 1 арифметического и логического устройства, а также через схему «ИЛИ 56 на счетчик сдвигов 57, где формируется дополннтель13

окончании деления остаток сдвигается вправо на число разрядов, зафиксированное в счетчике сдвигов при нормализации. С этой целью сигнал с шины 58 сдвигов вправо поступает на вход счетчика и схему «И 59, на второй вход схемы «И 59 подан сигнал с выхода инвертора 60, и сдвиги вправо на схеме «И 59 формируются до тех пор, пока не переполнится счетчик и на выходе инвертора 60 не выработается запрещающий сигнал.

В схему умножения // входят схема анализа множителя (фиг. 7) и схема образования дополнительной тетрады (фиг. 8).

В схеме анализа множителя (фиг. 7) анализируемые разряды множителя не передаются в специальные элементы запоминания, а непосредственно снимаются с двух младщих разрядов 49 и 61 второго регистра младщей секции / арифметического и логического устройства, куда они поочередно поступают путем сдвига множителя на два разряда вправо при наличии сигнала на щине 62 сдвига вправо и знакового разряда первого регистра секции арифметического и логического устройства. Триггер 63 знакового разряда используется для запоминания единицы от предыдущего цикла и одновременно является указателем того, в каком коде находится множимое после выполнения очередного цикла, так как в арифметическом и логическом устройстве мащины отсутствуют специальные цепи для вычитания, и вычитание заменяется сложением обратных кодов отрицательных чисел.

Значения этих разрядов поступают на дешифратор 64, раскрывающий характер действия, которое надо произвести в очередном цикле умножения, и выдающий в арифметическое и логическое устройство сигналы «Инвертирование множимого в знак множимого (шина 65), «сложение (шина 66) или «Сложение со сдвигом (щина 67), согласно таблице.

Таблица

14

В операции умножения над десятичными числами, осуществляемой путем последовательного сложения в коде 8421, для получения правильного результата в качестве разрядов дополнительной тетрады, хранящей возможные переносы из старшей тетрады третьего регистра секции /, используются знаковые разряды 63, 68, 69 и 45 секции / арифметического и логического устройства (фиг. 8).

Триггеры знаковых разрядов связаны между собой и другими десятичными разрядами (тетрадами) шиной сигнала переноса и шиной сигнала сдвига вправо 70. Сигнал переноса из старшего знакового разряда 69 третьего регистра секции / поступает в цепь переноса знакового разряда 68 второго регистра секции / через схему «И 71 при наличии разрешающего сигнала на шине 72 десятичного умножения, а затем по цепи переноса через вторую схему «И 73 в цепь переноса знакового разряда 63 первого регистра секции / арифметического и логического устройства.

При сдвиге частичного произведения вправо сигнал сдвига поступает по шине 70 через

схему «И 74 при наличии разрешающего сигнала на шине 72 десятичного умнол енпя на сдвиговые цепи триггеров разрядов знака 63, 68, 69 и 45 и далее на сдвиговые цепи старшей секции / третьего регистра арифметического

и логического устройства.

Предмет изобретения

1. Процессор для цифровой системы обработки данных, содержащий арифметическое и

логическое устройство, разбитое на п секций, каждая из которых содержит первый, второй и третий регистры, объединенные в сумматор т-разрядных чисел, накопитель данных с адресацией словами и посимвольной адресацией,

блок числа накопителя, устройство управления, исполняющие операции в соответствии с последовательностью команд программы, встроенный .мультиплексный и селекторный каналы для связи с набором внешних устройств, работающих одновременно с устройством управления и арифметическим и логическим устройством, регистр адреса, блок выделения символа, распределители символов и слов и буферный регистр символа, отличающийся тем, что, с целью сокращения оборудования за счет иснользования отдельных устройств для выполнения различных функций, он содержит схему задания конфигурации соединения секций арифметического и логического устройства и подачи сигналов управления операциями, связанную с устройством управления, схему управления умножением и схему управления делением, подключенные к устройству управления и через схему задания конфигурации взаимосвязанные с соответствующими секциями арифметического п логического устройства, группа секций арифметического п логического устройства связана через схему задания конфигурации и обналов блок регистра адреса устройств вводавывода с блоком централизованного формирования адресов накопителя, поступающих от различных источников; блок выработки текущего адреса по управляющему слову, поступающему из блока числа накопителя или из дежурного регистра селекторного канала, взаимосвязанный с дежурным регистром селекторного канала и подсоединенный к блоку выделения символа, подключениому к распределителю символов, связанному с общим буферным регистром символа селекторного и мультиплексного каналов и блоком записи и контроля на пропадание символов и через схему задания конфигурации - со входами соответствующих секций логического и арифметического устройства; блок числа накопителя связан с блоком записи символа, с блоком выделения символа, через распределитель слов - со входом блока выработки текущего адреса и дежурным регистром селекторного канала и через схему задания конфигурации- со входами всех секций арифметического и логического устройства. 2.Процессор по п. I, отличающийся тем, что, с целью задания переменного максимального адреса в последовательности адресов, по которым разрешен обмен между накопителями и устройствами ввода-вывода, и признаков окончания обмена, в нем блок выработки текущего адреса по управляющему слову содержит блок операций, -блок слул ебпых признаков, блок текущего адреса, схему сравнения и блок управления обменом, причем блоки операций, служебных признаков, текущего адреса взаимосвязаны с распределителем слов и дежурным регистром селекторного канала, выход блока операций подключен ко входу блока управления обменом, который взаимосвязан с блоком служебных признаков, схемой сравнения и блоком текущего адреса, выходы блоков служебных признаков и текущего адреса подключены соответственно к первому и второму входам схемы сравнения, третий вход которой соединен с буферным регистром символа, вход блока текущего адреса соединен со схемой задания конфигураций, а второй выход подключен к блоку централизованного формирования адресов. 3.Процессор по п. I, отличающийся тем. что, с целью обнаружения лишних символов или пропадания символов, вводимых из устройства ввода, в нем блок записи символа содержит блок замены символа при записи, схему коррекции контрольного разряда слова, дешифратор кода номера символа, вход которого подключен к блоку выработки текущего адреса, выход дешифратора соединен со вторыми входами схемы коррекции контрольного разряда и блока замены символа, первые входы которых соединены с распределителем символа, а третьи входы - с блоком числа, выход схемы коррекции контрольного разряда связан с обмоткой записи контрольного разряда накопителя, выход блока замены символов связан с обмотками записи слова накопителя щинами, позволяющими управлять записью слова, состоящего из п символов, один из которых является неполноразрядным. 4. Процессор по п. 1, отличающийся тем, что, с целью сокращения оборудования, в нем схема задания конфигураций соединений секций арифметического и логического устройства содержит блок разбивки секций, взаимосвязанный со схемой устройства управления, со схемами управления делением и умножением с одной стороны и с соответствующей группой секций арифметического и логического устройства с другой, входы которого соединены с выходами блоков формирования слов и символов, взаимосвязанных с одной стороны с распределителями слов и символов и с другой- с соответствующими группами секций арифметического и логического устройства, а выходы блока разбивки секций подсоединены к вентилям, объединяющим вход и выход любых двух секций арифметического и логического устройства; выходы соответствующих групп секций арифметического и логического устройства связаны с общим регистром адреса устройств ввода-вывода селекторного и мультиплексного каналов, с блоком выработки текущего адреса по управляющему слову и с блоком централизованного формирования адресов. 5. Процессор по п. I, отличающийся тем, что, с целью увеличения его производительности при выполнении операций деления, в нем схема управления делением содержит первый и второй вентили корректировки частного, подключенные по выходам к единичному и нулевому входам младщего разряда второго регистра младщей секции арифметического и логического устройства соответственно, вход вентилей корректировки связан с соответствующим выходом устройства управления арифметическими и логическими операпиями и с прямым и инверсным выходами разряда знака третьего регистра старшей секции арифметического и логического устройства, которые подключены ко входам управления 3-го и 4-го вентилей, дополнительные входы которых связаны с щиной сдвига влево устройства управления арифметическими и логическими операциями и прямым и инверсным выходами старщего разряда третьего регистра старщей секции арифметического и логического устройства; выходы 3-го и 4-го вентилей подключены к схеме формирования сдвигов влево зо втором и третьем регистрах объединенных секций арифметического и логического устройства, причем выход старшего значащего разряда третьего регистра старщей секции связан со входом разряда знака того же регистра и со входом младщего разряда второго регистра младщей секции; шипа сдвига влево через вентиль, управляющий вход которого через схему анализа делимого и делителя при нормализации подключен к старшим значапдим шей секции, и сборку, связанную по дополнительному входу с шиной сдвига вправо устройства управления арифметическими и логическими операциями и первым входом вентиля управления сдвигами вправо на заданное число сдвигов, соединена со счетчиком формирования числа сдвигов при нормализации, выход которого через инвертор связан со вторым входом последнего вентиля, выход которого подключен к шине передачи содержимого разряда знака в старший значащий разряд третьего регистра объединенных секций арифметического и логического устройства. 6. Процессор по п. 1, отличающийся тем, что, с целью сокращения его оборудования при выполнении операций умножения двоичных чисел и умножения двоично-десятичных чисел, в нем схема управлен-ия умножением содержит дешифратор, связанный непосредственно с прямым и инверсным входами разряда знака первого регистра старшей секции и с прямыми и инверсными выходами двух младших разрядов второго регистра младшей секции, выходы которого связаны с шинами сигналов очередной микрооперации устройства управления арифметическим и логическим устройством; шина сдвига вправо через вентиль, управляющий вход которого соединен с шиной сигнала десятичного умножения, подключенной к управляющим входам вентилей перекоса, соединена со входом сдвиговых цепей разряда знака первого регистра старшей секции, выход которых связан со входом сдвиговых цепей разряда знака второго регистра старшей секции, а выход последних соединен со входом сдвиговых цепей разряда знака третьего регистра старшей секции, выход переноса этого разряда через вентиль переноса соединен со счетным входом разряда знака второго регистра, а выход переноса последнего связан со счетным входом разряда знака первого регистра старшей секции арифметического и логического устройства.

1

г

,Щ

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Устройство для обработки данных переменной длины | 1976 |

|

SU648984A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU386444A1 |

| УСТРОЙСТВО для ВЫЧИСЛЕНИЯ АЭРОДИНАМИЧЕСКИХПАРАМЕТРОВ | 1970 |

|

SU276528A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ КАНАЛАМИ | 1973 |

|

SU386395A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Процессор микропрограммируемой ЭВМ | 1979 |

|

SU860077A1 |

| ЦЕНТРАЛЬНЫЙ ПРОЦЕССОР МУЛЬТИПРОГРАММНОЙ МУЛЬТИПРОЦЕССОРНОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1971 |

|

SU309363A1 |

| Устройство для отображения информации | 1986 |

|

SU1506478A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

Фиг. 4

гО

«

5/-х:::

50

41

5&

6f 66 61

Авторы

Даты

1971-01-01—Публикация