Изобретение относится к техническим средствам информатики и вычислительной техники и может быть использовано для синтеза арифметико-логических устройств, для создания быстродействующих и производительных цифровых устройств суммирования и вычитания чисел в прямых кодах.

Известна "Схема цифрового сумматора" (патент № 99109089/09, от 04.07.1997 г. Бюл. 7 (1 ч.) 2001 г.), позволяющая выполнять операцию сложения чисел в двоичной системе счисления.

Известно также "Устройство для сложения" (патент № 4892584/24, от 19.12.1990 г. Бюл. N 25 1995 г.), позволяющее складывать двоичные числа.

В качестве прототипа выбрано "Устройство для вычисления модуля М-мерного вектора" (95104370/09, от 01.03.1995. Бюл. № 15, 1997 г.), которое выполняет операции суммирования и вычитания над М-мерными векторами.

Задача заключалась в следующем:

1) уменьшить аппаратные затраты устройства,

2) упростить алгоритм блока управления,

3) повысить скорость операции суммирования-вычитания чисел в прямых кодах,

4) повысить надежность работы сумматора-вычитателя. В представленном сумматоре-вычитателе происходит сложение или вычитание двоичных чисел. Предлагаемый сумматор-вычитатель позволит значительно снизить аппаратные средства, что ведет к упрощению комбинационной схемы, а также значительно упростит алгоритм работы устройства.

Решение задачи осуществляется тем, что параллельный сумматор-вычитатель на нейронах, содержащий блок сумматоров-вычитателей, блок управления, отличающиеся тем, что дополнительно введены: блок ввода чисел, блок компарации, блок регистра большего числа, блок регистра меньшего числа, блок регистра результата, причем первый и второй информационные выходы блока ввода чисел соединены соответственно с первым и вторым информационными входами блока компарации, первый информационный выход которого соединен с первым информационным входом блока регистра большего числа, управляющий вход которого соединен с первым управляющим выходом блока компарации, управляющий вход которого соединен с управляющим выходом блока ввода чисел, и с управляющим входом блока суммирования-вычитания, и с пятым управляющим входом блока управления, третий управляющий вход которого соединен с четвертым управляющим выходом блока компарации, второй информационный выход которого соединен с первым информационным входом блока регистра меньшего числа, управляющий вход которого соединен со вторым управляющим выходом блока компарации, третий управляющий выход которого соединен с управляющим входом блока регистра результата, второй информационный вход которого соединен с первым информационным выходом блока управления, третий информационный выход которого соединен со вторым информационным входом блока регистра большего числа, информационный выход которого соединен с первым информационным входом блока суммирования-вычитания, второй информационный вход которого соединен с информационным выходом блока регистра меньшего числа, второй информационный вход которого соединен со вторым информационным выходом блока управления, четвертый управляющий вход которого соединен с управляющим выходом блока суммирования-вычитания, информационный выход которого соединен с первым информационным входом блока регистра результата, первый и второй управляющие входы "СБРОС" и "ПУСК" блока управления являются внешними входами параллельного сумматора-вычитателя.

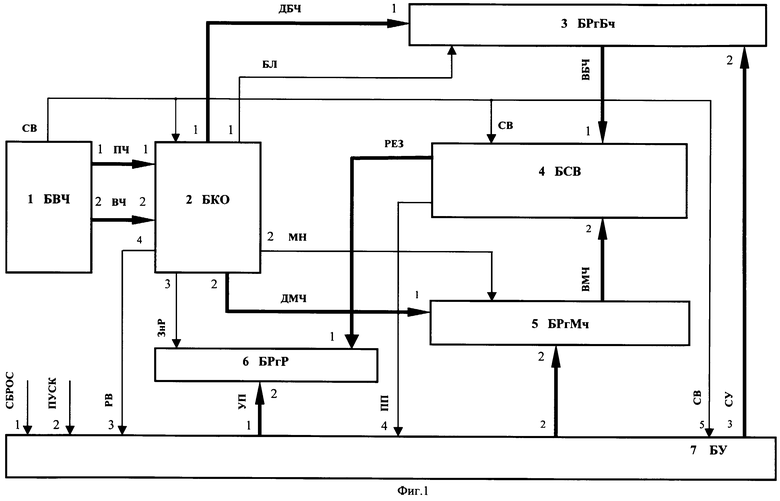

БВЧ - блок ввода чисел служит для ввода операндов и знака операции (+ или -).

БКО - блок компарации служит для сравнения чисел А и В, если необходимо выполнить операцию вычитания.

БСВ - блок суммирования-вычитания служит для выполнения операций сложения или вычитания.

БРгБЧ - блок регистра большего числа служит для хранения первого числа в случае выполнения операции сложения или для хранения большего по модулю числа в случае выполнения операции вычитания.

БРгМЧ - блок регистра меньшего числа служит для хранения второго числа в случае выполнения операции сложения или для хранения меньшего по модулю числа в случае выполнения операции вычитания.

БРгР - блок регистра результата служит для хранения суммы при сложении или разности при вычитании чисел, а также знака результата.

БУ - блок служит для управления устройством.

В современных ЭВМ операция вычитания выполняется с применением дополнительного или обратного кода. Если было введено отрицательное число, то происходит перевод этого числа в дополнительный или обратный код. Признаком отрицательного числа является единица в знаковом разряде двоичного представления операнда, например 11.10011. В этом случае осуществляется перевод отрицательного числа в дополнительный или обратный код. Полученный результат также анализируется. Если получен отрицательный результат, то осуществляется перевод в дополнительный или обратный код. Если получен положительный результат, то перевода в коды не происходит. По этому алгоритму результат можно получить только после анализа знакового разряда результата. В случае ввода двух отрицательных чисел необходимо перевести оба числа в коды. Результат в этом случае также переводится в дополнительный или обратный код.

Известен алгоритм сложения чисел в прямых кодах. Этот алгоритм позволяет сразу получить правельный результат в прямом коде. В этом случае необходимо применить операцию вычитания чисел. Для этого используется комбинационная схема вычитателя чисел в прямых кодах.

Для получения суммы двух чисел возможны два случая:

1) слагаемые имеют одинаковые знаки;

2) слагаемые имеют разные знаки.

Алгоритм получения суммы двух чисел с одинаковыми знаками определяется следующем образом:

Алгоритм первый.

1) сложить два числа;

2) сумме присвоить знак одного из слагаемых.

Алгоритм получения суммы двух чисел с разными знаками определяется следующем образом:

1) сравниваются знаки слагаемых и, если они одинаковы, то выполняется сложение по первому алгоритму;

2) если знаки слагаемых разные, то сравниваются числа по абсолютной величине;

3) если есть необходимость, переставить числа местами, чтобы вычитать из большего меньшее;

4) произвести вычитание двух чисел;

5) результату присвоить знак большего слагаемого.

Этот алгоритм позволяет получить сумму или разность чисел в прямых кодах в параллельном режиме. После получения чисел из блока ввода операндов и перевода их в двоичную систему счисления необходимо определить одинаковые ли знаки чисел. Определяется это с помощью операции сумматора по модулю два. Если знаки одинаковые, то результат будет нуль. В противном случае результат будет единица. После этого выбирается операция сложения или вычитания.

На фиг.1 изображена структурная схема сумматора-вычитателя.

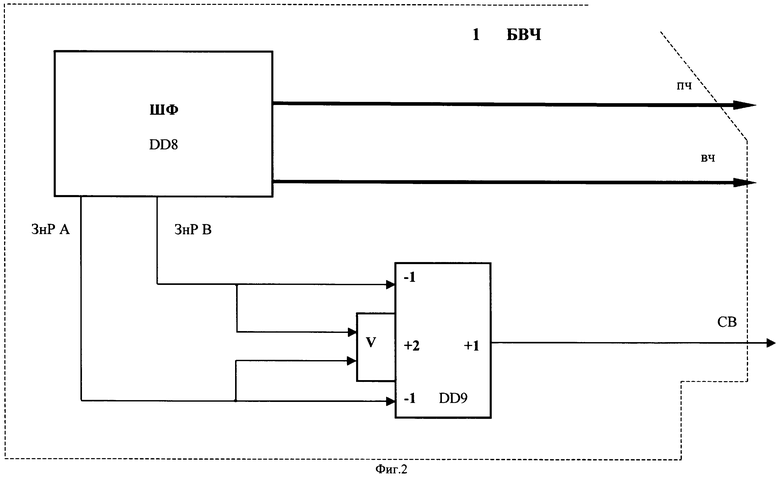

На фиг.2 представлен вариант технической реализации блока ввода чисел.

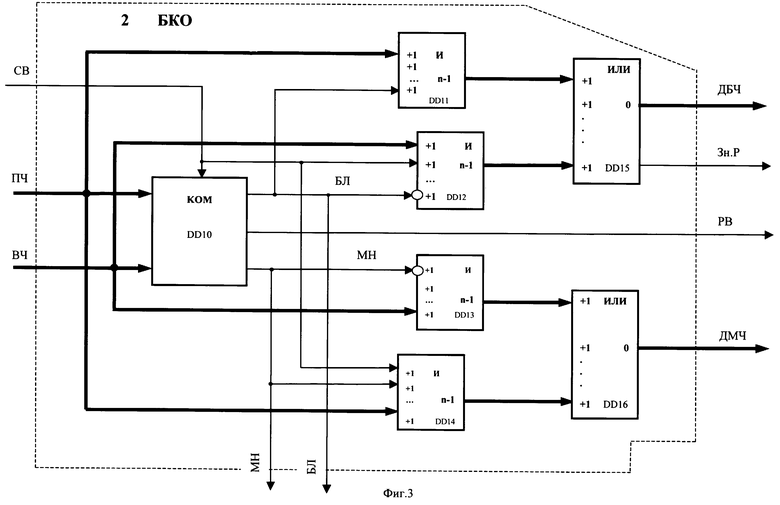

На фиг.3 представлен вариант технической реализации блока компарации.

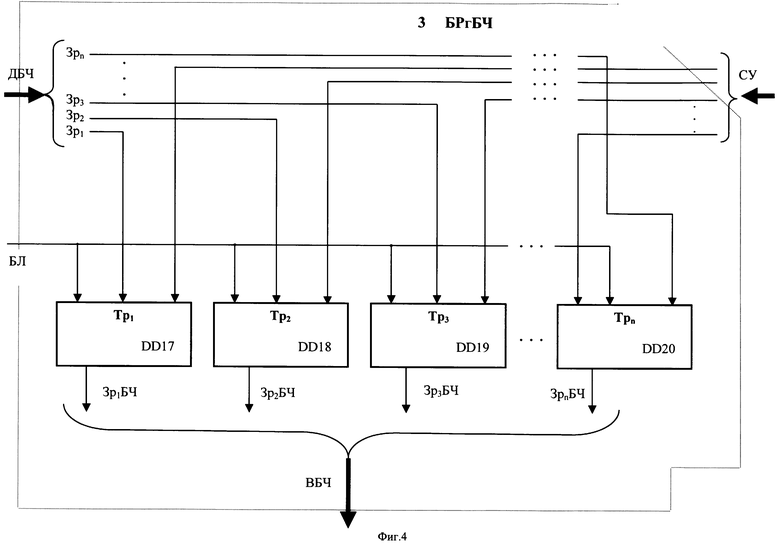

На фиг.4 изображена функциональная схема блока регистра большего числа.

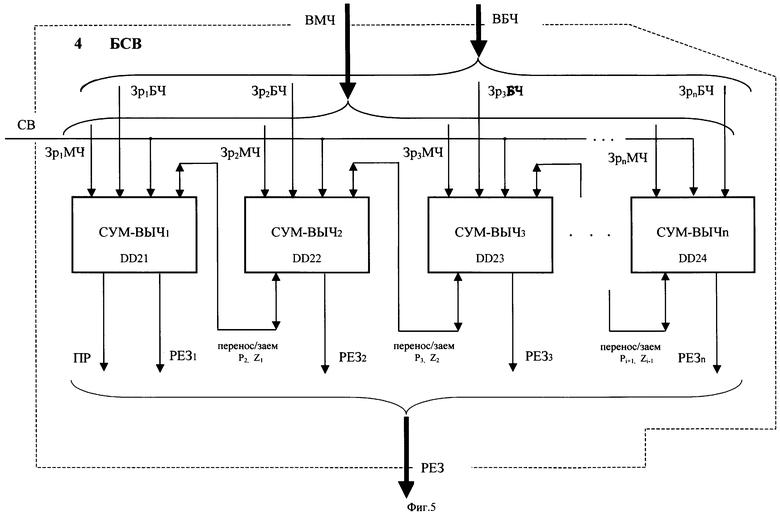

На фиг.5 показана функциональна схема блока суммирования-вычитания.

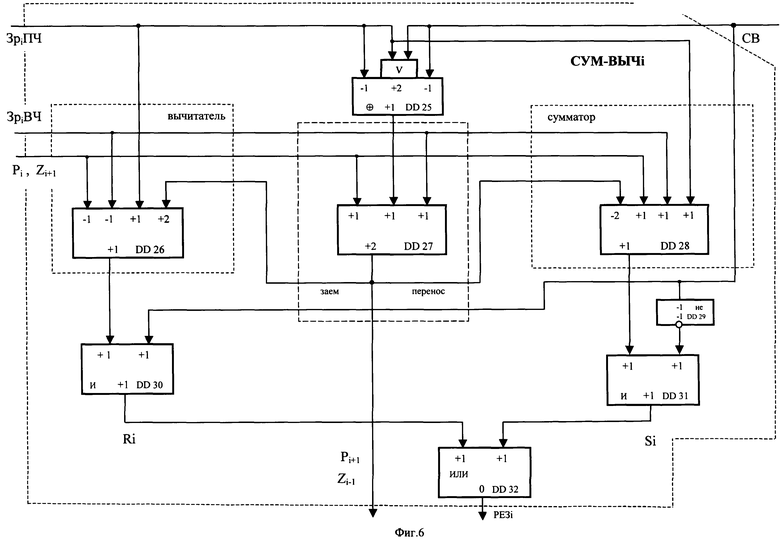

На фиг.6 показана принципиальная схема одноразрядного сумматора-вычитателя на нейронах.

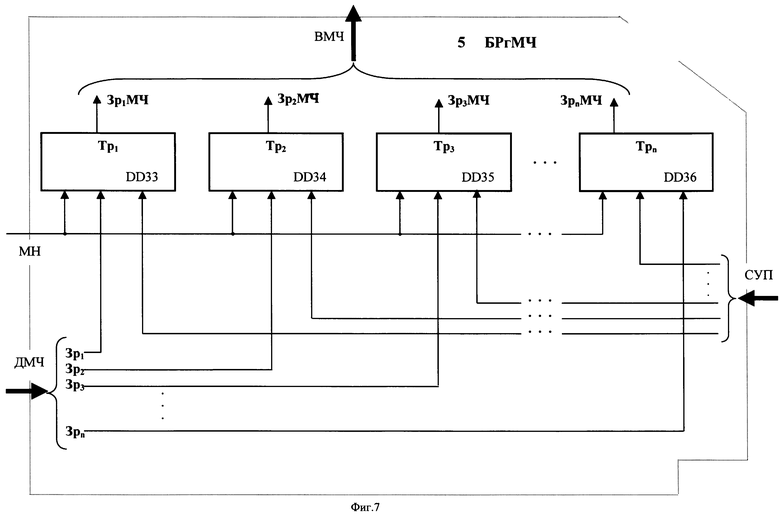

На фиг.7 изображена функциональная схема блока регистра меньшего числа.

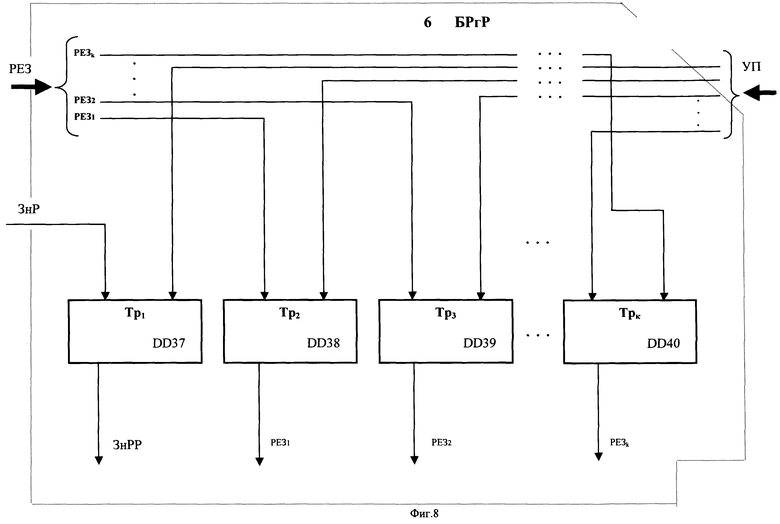

На фиг.8 представлен вариант технической реализации блока регистра результата.

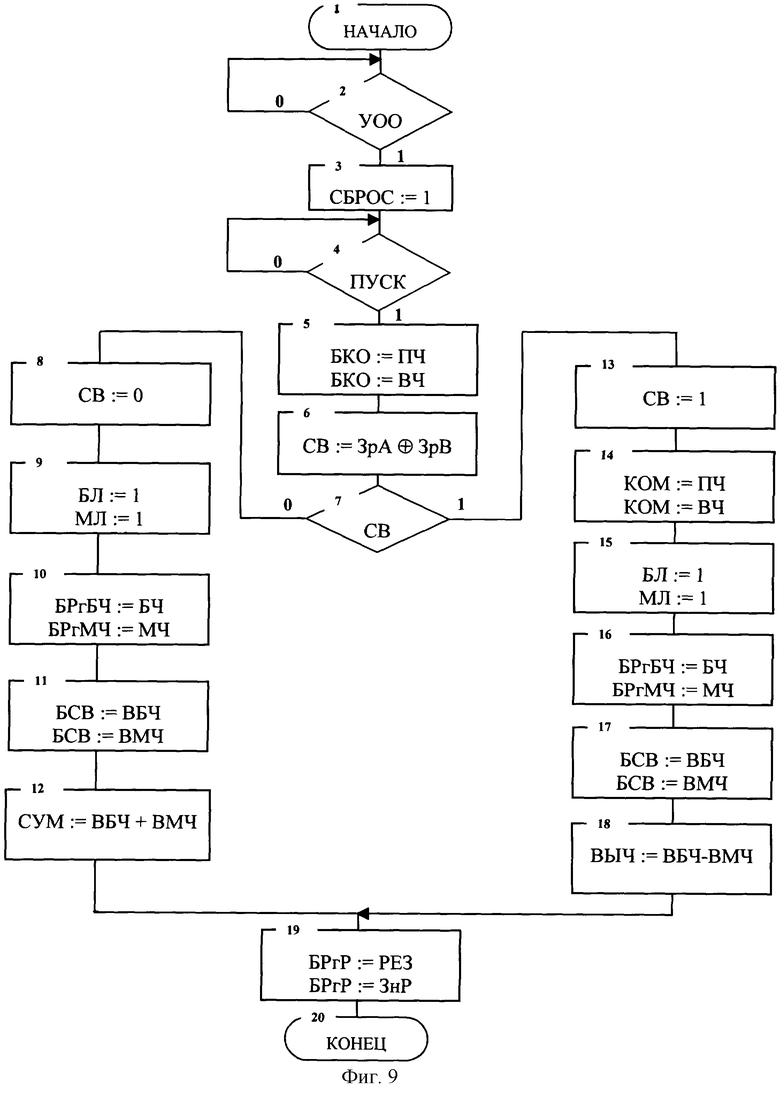

На фиг.9 - содержательная ГСА (граф-схема алгоритма) работы устройства.

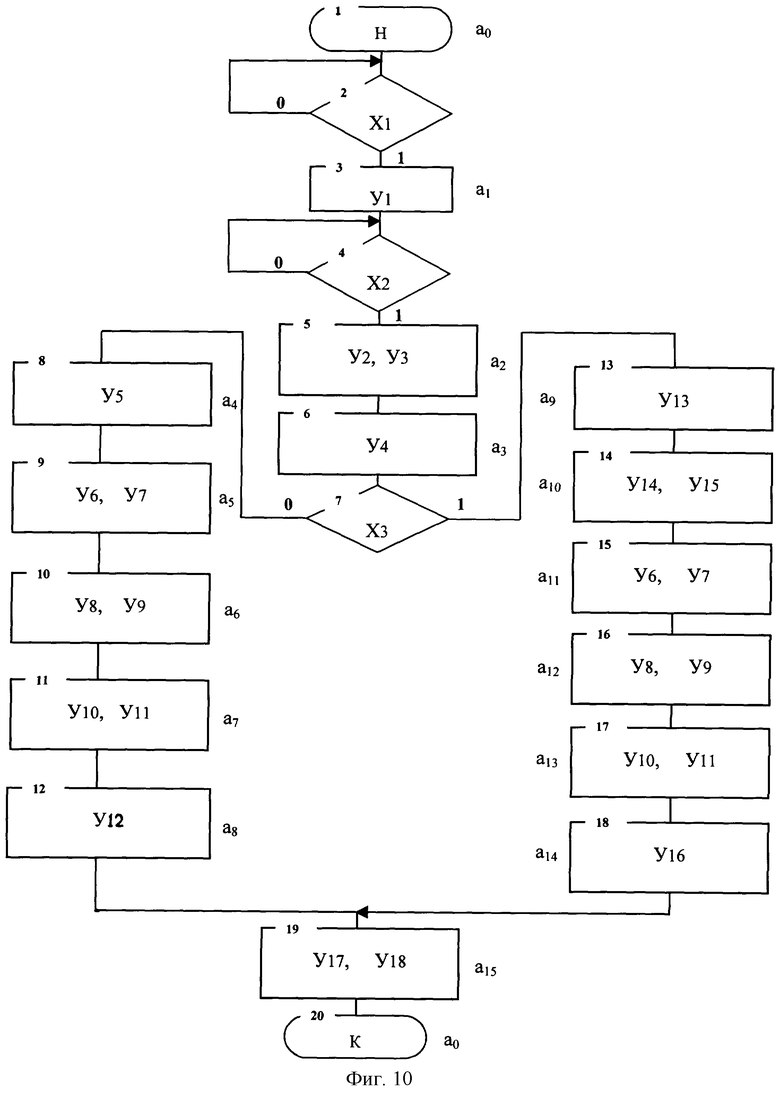

На фиг.10 - размеченная ГСА работы устройства.

Параллельный сумматор-вычитатель на нейронах (фиг.1) содержит: блок ввода чисел, блок компарации, блок суммирования-вычитания, блок регистра большего числа, блок регистра меньшего числа, блок регистра результата, блок управления, пороговые элементы, нейроны.

Для описания алгоритма работы блока 7 управления используются следующие идентификаторы.

1. ПЧ - первое число.

2. ВЧ - второе число.

3. ДБЧ - двоичные разряды большего числа.

4. ДМЧ - двоичные разряды меньшего числа.

5. РВ - сигнал равенства чисел, поступивший с выхода компаратора.

6. БЛ - сигнал "больше", поступивший с выхода блока компаратора.

7. МН - сигнал "меньше", поступивший с выхода блока компаратора.

8. ЗнР - знаковый разряд.

9. СВ - сигнал суммы-вычитания.

10. PE3i - двоичные разряды результата.

11. УП - информационный сигнал управления работой блока регистра результата, включающий в себя сигналы: обнуления, синхронизации, разрешения записи, хранения, выдачи.

12. ВБЧ - выходная двоичная информация большего числа.

13. ВМЧ - выходная двоичная информация меньшего числа.

14. СУП - информационный сигнал управления работой блока регистра меньшего числа.

15. СУ - информационный сигнал управления работой блока регистра большего числа.

16. ЗнрА - знаковый разряд первого числа.

17. ЗнрВ - знаковый разряд второго числа.

18. Зр1ПЧ - двоичные разряды первого числа.

19. 3piBЧ - двоичные разряды второго числа.

20. 3piБЧ - двоичные разряды большего числа.

21. 3piMЧ - двоичные разряды меньшего числа.

22. ЗнРР - знаковый разряд результата.

23. ПП - признак получения результата.

24. СБРОС - сигнал сброса (обнуления) всех комбинационных блоков и элементов памяти сумматора-вычитателя.

25. ПУСК - сигнал начало работы сумматора-вычитателя.

Работа алгоритма управления параллельного сумматора-вычитателя на нейронах.

Содержательная ГСА управления приведена на фиг.9 и отражает работу блока управления (фиг.1).

В блоке 2 алгоритма осуществляется подача сигнала установки в нулевое состояние - УОО на входы всех элементов устройства.

В блоке 3 алгоритма происходит установка сигнала сброса в единичное значение СБРОС:=1.

В блоке 4 алгоритма осуществляется подача внешнего сигнала ПУСК в блок управления сумматора-вычитателя для разрешение работы сумматора-вычитателя.

В блоке 5 алгоритма осуществляется подача на вход компаратора первого и второго чисел, поступивших с выходам блока ввода данных по командам БКО:=ПЧ, БКО:=ВЧ.

В блоке 6 алгоритма определяется сигнал сумма-вычитание - СВ, который определяет какую операцию необходимо выполнять сложение или вычитание. Этот сигнал определяется по операции сложения по модулю два СВ:=ЗрА⊕ЗрВ.

В блоке 7 алгоритма осуществляется анализ сигнала СВ. Если сигнал СВ равен нулевому значению, то выполняется операция сложение - выход 0 блока, если единичному значению - выход 1 блока, то выполняется операция вычитание.

В блоке 8 алгоритма сигнал СВ принимает значение нуля СВ:=0, в этом случае выполняется операция сложение, а также осуществляется блокировка работы компаратора по приходу сигнала СВ, поступившего из блока ввода чисел. В этом случае на вход сумматора-вычитателя из блока ввода чисел поступают числа с одинаковыми знаками, и поэтому сравнение чисел производить не нужно.

В блоке 9 алгоритма по командам БЛ:=1, МЛ:=1 происходит подача отпирающих сигналов, поступающих на входы блоков регистров большего и меньшего числа. После этого происходит запись входной информации в регистры блоков.

В блоке 10 алгоритма по командам БРгБЧ:=БЧ, БРгМЧ:=МЧ осуществляется загрузка чисел в регистры блоков большего и меньшего числа.

В блоке 11 алгоритма по командам БСВ:=ВБЧ, БСВ:=ВМЧ происходит подача чисел на блок сумматора-вычитателя. На входы блока поступают числа, представленные в двоичном эквиваленте.

В блоке 12 алгоритма осуществляется операция суммирование чисел по команде СУМ:=ВБЧ+ВМЧ.

В блоке 13 алгоритма по команде СВ:=1 сигнал суммы-вычитания принимает единичное значение. В этом случае поступившие числа с блока ввода данных имеют разные знаки и при этом необходимо выполнить операцию сравнения модулей чисел, для того чтобы определить большее и меньшее из чисел для выполнения операции вычитания. Компаратор отпирается единичным сигналом.

В блоке 14 алгоритма по командам: КОМ:=ПЧ, КОМ:=ВЧ на вход компаратора поступают первое и второе число с выхода блока ввода данных для выполнения операции сравнения между ними.

В блоке 15 алгоритма происходит подача отпирающих сигналов из блока компаратора на входы блоков регистров большего и меньшего числа по командам: БЛ:=1, МЛ:=1 для записи информации в регистры.

В блоке 16 алгоритма осуществляется загрузка операндов в регистры блоков большего и меньшего числа по командам: БРгБЧ:=БЧ, БРгМЧ:=МЧ.

В блоке 17 алгоритма на входы блока сумматора-вычитателя по командам: БСВ:=ВБЧ, БСВ:=ВМЧ поступает первое и второе число для выполнения операции вычитания.

В блоке 18 алгоритма по команде ВЫЧ:=ВБЧ - ВМЧ осуществляется операция вычитание между числами. Из большего по модулю числа вычитается меньшее.

В блоке 19 алгоритма по командам: БРгР:=РЕЗ, БРгР:=ЗнР происходит запись результата и его знака в регистр блока результата.

Блок 20 алгоритма является конечным.

Работа параллельного сумматора-вычитателя на нейронах заключается в следующем.

Внешние управляющие сигналы СБРОС и ПУСК поступают в блок 7 управления.

С выхода шифратора поступают в регистры большего числа и меньшего числа двоичные числа А2 и В2. На сумматоре по модулю два определяется знак результата. Если числа имеют одинаковые знаки, то вычисляется сумма чисел. Знак результату присваивается знак любого из слагаемых. Если знаки чисел разные, то проводится операция вычитания. Из большего по модулю числа вычитается меньшее. Знак результату в этом случае присваивается знак большего по модулю числа. Предлагаемое арифметическое устройство выполняет операции суммирования и вычитания в параллельном варианте. Определяется перенос в старшие разряды при суммировании, который необходимо учитывать при сложении чисел. Вычисляется заем из старших разрядов в младшие при вычитании.

Блок 1 ввода чисел содержит шифратор (обычная стандартная клавиатура) ШФ DD8, сумматор по модулю два DD9 (фиг.2). Этот блок позволяет вводить двоичные числа. С выхода шифратора формируется двоичный код чисел со своими знаками: А2, В2, ЗнР А, ЗнРВ. Знаковые разряды с выхода шифратора поступают на вход сумматора по модулю два. Сигнал СВ суммирования-вычитания формируется на выходе элемента DD9. Сумматор по модулю два реализуется на формальном нейроне ФН [1]. Выходной сигнал вычисляется по формуле:

Если СВ равен единице, то необходимо выполнять операцию вычитания, Если СВ равен нулю, то осуществляется операция сложения. Выходными сигналами блока 1 ввода чисел являются двоичные коды А2 и В2, представленные в прямых кодах и признак операции СВ.

Блок 2 компарации содержит компаратор КОМ DD10, схему электронных ключей (конъюнкция) DD11, схему электронных ключей (конъюнкция) с инверсным входом DD12, схему электронных ключей (конъюнкция) с инверсным входом DD13, схему электронных ключей (конъюнкция) DD14, логический элемент (схема ИЛИ) DD15, логический элемент DD16 (фиг.3). Этот блок предназначен для определения большего числа по модулю. На вход компаратора поступает управляющий сигнал СВ - признак суммирования или вычитания. Этот сигнал СВ поступает на входы логических элементов И (конъюнкторов) DD12, DD14 (фиг.3). Если на вход сумматора-вычитателя поступят числа с разными знаками, то в этом случае необходимо в блок регистра большего числа записать больший по модулю операнд. В блок регистра меньшего числа загружается число меньшее по модулю. Компаратор КОМ DD10 представляет собой схему сравнения чисел. Эта схема может быть выполнена на формальном нейроне ФН [1]. Если управляющий сигнал СВ суммирования-вычитания равен нулю, то это означает, что выполняется операция суммирования. В этом случае сравнивать числа не нужно. Поэтому компаратор КОМ DD10, логические элементы И DD12 и DD14 будут заперты нулевым сигналом СВ. Через открытый логический элемент И DD11 и логический элемент ИЛИ DD15 первое число поступит на вход блока 3 регистра большего числа (фиг.1, 3). Через открытый логический элемент И DD13 и логический элемент ИЛИ DD16 второе число поступит на вход блока 5 регистра меньшего числа (фиг.1, 3). Если сигнал СВ равен единице, то в этом случае выполняется операция вычитания. Компаратор КОМ DD10, логические элементы DD12 и DD14 будут открыты. Сравнение чисел в этом случае проводить необходимо для определения большего и меньшего по модулю числа. На вход компаратора КОМ поступают n-разрядные числа А и В без знаковых разрядов. На выходе компаратора имеется три выхода: БЛ - число А больше В, РВ - числа А и В равны по модулю, МН - число А меньше В. Логические схемы И DD11, DD12, DD13, DD14 выполнены на формальных нейронах ФН [1]. Схема конъюнкция описывается с помощью формулы [w1=1, w2=1,...,wn=1; T=n-1], где w1, w2,...,wn - коэффициенты усиления, а Т - пороговое напряжение, n - количество входов. Схема дизъюнкция описывается с помощью формулы [w1=1, w2=1,...,wn=1; T=0], где w1, w2,...,wn - коэффициенты усиления, а Т равное нулю - пороговое напряжение, n - количество входов. Инвертор описывается формулой [w=-1; T=-1]. На входы логических схем И DD11, DD14 поступает число А со своим знаком. На входы логических схем И DD12, DD13 поступает число В со своим знаком. Выходы логических схем И DD11, DD12 поступают на вход логической схемы ИЛИ DD15. Выходы логических схем И DD13, DD14 поступают на вход логической схемы ИЛИ DD16 (фиг.3). Выходная информация ДБЧ логической схемы ИЛИ DD15 поступает на вход блока регистра большего числа (фиг.1). Выходная информация ДМЧ логической схемы ИЛИ DD16 поступает на вход блока регистра меньшего числа (фиг.1). При поступлении чисел А и В на вход компаратора, на выходе компаратора КОМ формируется отношение операндов. Если на выходе БЛ будет единица, то это означает, что число А больше В по модулю. Остальные выходы компаратора будут равны нулевому значению. Единичный выход БЛ откроет схему И DD11, через которую число А поступит вход схемы ИЛИ DD15. Логическая схема И DD12 будет заперта, т.к. управляется инверсным сигналом. С выхода схемы ИЛИ DD15 информационный сигнал поступит в блок регистра большего числа. Логическая схема И DD13 будет открыта, через нее меньшее по модулю число В поступит на вход схемы ИЛИ DD16. С выхода схемы ИЛИ DD16 информационный сигнал поступит на вход блока регистра меньшего числа. Если выходной сигнал МН будет равен единичному значению, что означает число В больше по модулю, чем число А. В этом случае логические схемы DD12 и DD14 будут открыты и через их информационные сигналы поступят на входы схем ИЛИ DD15 и DD16 соответственно. Через схему DD12 число В большее по модулю поступит на вход схемы ИЛИ DD15, затем в блок регистра большего числа. Через схему DD14 число А меньшее по модулю поступит на вход схемы ИЛИ DD16, затем в блок регистра меньшего числа. Если числа А и В равны по модулю и имеют равные знаки, то сигнал РВ будет равен единице, а сигналы БЛ и МН будут равны нулю. Логические схемы И DD11 и DD14 будут заперты, а схемы DD12 и DD13 будут открыты. На логические схемы ИЛИ DD15 и DD16 поступит число В. В этом случае произойдет сложение чисел В и В. Знак результата ЗнР всегда будет формироваться с выхода логической схемы ИЛИ DD15, т.к. на выходе будет большее по модулю число (фиг.3).

Блок 3 регистра большего числа содержит n-триггеров Трп, где n - количество разрядов входного числа: DD17, DD18, DD19, DD20 (фиг.4). Блок 3 регистра большего числа предназначен для хранения двоичного кода большего по модулю операнда. Перед началом работы сумматора-вычитателя по приходу из блока 7 управления информационного сигнала СУ происходит обнуление всех триггеров блока. По приходу из блока 2 компарации информационного сигнала ДБЧ - данные большего числа - осуществляется загрузка двоичного кода одного из чисел. При поступлении управляющего сигнала БЛ - больше на входы триггеров Тр1, Тр2, Тр3,...,Трn из блока 2 компарации, разрешающего записать информацию в триггера, происходит загрузка поступившего двоичного кода числа в триггера блока. Сигнал БЛ является входным управляющим сигналом для всех элементов памяти блока (фиг.4). В этом блоке хранится большее по модулю число, если необходимо выполнить операцию вычитания, и первое число, поступившее из блока ввода чисел, в случае выполнения операции сложения.

Блок 4 суммирования-вычитания (фиг.5) содержит n - одноразрядных сумматоров-вычитателей СУМ-ВЫЧn, выполненных на комбинационых схемах DD21, DD22, DD23, DDn. На вход каждого одноразрядного сумматора-вычитателя поступает четыре входных двоичных числа: ЗрiБЧ - двоичный i - разряд большего по модулю числа при выполнении операции вычитания или первого числа при выполнении операции суммирования, 3piMЧ - двоичный i - разряд меньшего по модулю числа при выполнении операции вычитания или второго числа при выполнении операции суммирования, перенос Pi из младших разрядов в старшие, Zi - заем из старших разрядов в младшие при выполнении операции вычитания, управляющий сигнал СВ - суммирования-вычитания из блока 1 ввода чисел. Выходом каждого сумматора-вычитателя является результат суммы или разности - PE3i и перенос/заем Pi+1/Zi-1. Управляющий сигнал СВ поступает параллельно на входы всех одноразрядный сумматоров-вычитателей (фиг.5). Если сигнал суммирования-вычитания СВ равен нулю, то это означает, что с выхода блока ввода чисел поступили числа с одинаковыми знаками, в этом случае выполняется операция суммирования, во всех блоках СУМ-ВЫЧn вычисляется сумма чисел. В случае равенства СВ единице выполняется операция вычитания. Все блоки СУМ-ВЫЧn вычисляют разность между входными числами. Выходная информация в виде результата РЕЗ с выхода блока суммирования-вычитания поступает на вход блока регистра результата (фиг.1, 5, 8).

Одноразрядный сумматор-вычитатель СУМ-ВЫЧi (фиг.6) суммирования-вычитания содержит сумматор по модулю два, выполненный на формальном нейроне - элемент DD25, пороговые элементы DD26, DD27, DD28, инвертор DD29, логические схемы И DD30, DD31, логическую схему ИЛИ DD32. На пороговом элементе (ПЭ) DD27 формируется перенос при сложении или заем при вычитании. Пороговые элементы DD27 и DD28 составляют сумматор [1, 2]. На входы этих пороговых элементов поступают двоичные разряды чисел ЗрiПЧ и ЗрiВЧ, а также перенос Pi из младших разрядов в старшие (фиг.6). Двоичные разряды поступают поразрядно: ЗрiПЧ - разряд большего числа, ЗpiBЧ - разряд меньшего числа. Pi - перенос, Zi+1 - заем, а также признак суммирования-вычитания СВ (фиг.6). Пороговые элементы DD26 и DD27 образуют схему вычитателя чисел от большего меньшего. Логические элементы DD30 и DD31 выполняют роль электронных ключей. Управляющим сигналом для них является признак суммирования-вычитания СВ. На пороговый элемент DD31 этот сигнал поступает через инверторы DD29. Если признак операции СВ суммирования-вычитания будет равен нулю - выполнение операции суммирования, то электронный ключ DD31 будет открыт, а ПЭ DD30 будет заперт, управляющий сигнал СВ поступает через инверторы DD29. На выходе порогового элемента DD27 сформируется перенос из старших разрядов в следующий больший по весу разряд, если на входе порогового элемента DD27 будет не менее двух единиц. Пороговый элемент DD28 вычисляет сумму одноразрядных двоичных чисел - ЗрiПЧ и 3piBЧ, а также переноса Pi из младших разрядов в старшие. При суммировании через открытый элемент DD31 и схему ИЛИ DD32 разряд суммы Si поступит на вход блока регистра результата. Если сигнал СВ равен единице, что означает выполнение операции вычитания. Пороговые элементы DD27 и DD26 образуют схему вычитателя. С выхода элемента DD27 формируется заем из старших разрядов в младшие. С выхода элемента DD26 вычисляется разность поступивших на вход одноразрядного сумматора-вычитателя двоичных чисел - ЗрiПЧ и 3piBЧ, а также заема Zi+1 из старших разрядов. Через открытый электронный ключ DD30 и пороговый элемент DD32 (схема ИЛИ) разряды разности Ri будут поступать на вход блока регистра результата.

Блок 5 регистра меньшего числа содержит n-триггеров Трп, где n - количество разрядов меньшего по модулю входного числа: DD33, DD34, DD35, DD36. Блок 5 регистра меньшего числа предназначен для хранения двоичного кода меньшего по модулю числа при выполнении операции вычитания и второго, введенного из блока 1 ввода, числа, если необходимо выполнить операцию сложения. Перед началом работы сумматора-вычитателя по приходу из блока 7 управления информационного сигнала СУП происходит обнуление всех триггеров блока. По приходу из блока 2 компарации информационного сигнала ДМЧ - данные меньшего числа осуществляется загрузка двоичного кода числа. При поступлении управляющего сигнала МН - меньше на входы триггеров Тр1, Тр2, Тр3,...,Трn из блока 2 компарации, разрешающего записать информацию в триггера, происходит загрузка поступившего кода с выходов блока компарации в триггера блока. Сигнал МН является входным управляющим сигналом для всех элементов памяти блока (фиг.7).

Блок 6 регистра результата содержит k-триггеров Трк, где k - количество разрядов, необходимое для получения результата заданной точности: DD38, DD39, DD40 для хранения двоичных разрядов результата. А также в состав блока входит триггер Tpl DD37, предназначенный для хранения знакового разряда результата (фиг.8). В блоке регистра результата формируется результат в параллельном режиме при выполнении операций сложения или вычитания. Перед началом работы сумматора-вычитателя по приходу из блока 7 управления информационного сигнала УП происходит обнуление всех триггеров блока. Информационный сигнал результата РЕЗ, поступающий из блока суммирования-вычитания, поступает на входы триггеров Tk DD38, DD39, DD40 блока регистра результата. Полученный результата будет хранится в триггерах, составляющих регистр блока для хранения суммы или разности. На вход триггера Tpl DD37 из блока 2 компарации поступит управляющий сигнал ЗнР - знаковый разряд. После этого в триггер Tpl DD37 запишется знаковый разряд результата - ЗнР (фиг.8).

ИСТОЧНИКИ ИНФОРМАЦИИ

1. Мкртчян С.О. Проектирование логических устройств ЭВМ на нейронных элементах. - М.: Энергия, 1977 г.

2. Дертоузос М. Пороговая логика. - М.: Мир, 1967 г.

3. Вавилов Е.И. и др. Синтез схем на пороговых элементах. - М.: Сов. радио. 1970 г.

4. Галушкин А.И. Синтез многослойных схем распознавания образов. М.: Энергия, 1974 г.

5. Позин И.В. Моделирование нейронных структур. - М.: Наука, 1970 г.

6. Патент № 95104370/09, Бюл. № 15, 1997 01.03.95 (прототип).

7. Патент № 4892584/24, Бюл. № 25, 1995 19.12.90 (аналог).

8. Патент № 99109089/09, Бюл. № 7, (1 ч.) 01.07.1997 (аналог).

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| Параллельно-последовательный сумматор-вычитатель старшими разрядами вперед на нейронах | 2019 |

|

RU2708501C1 |

| Параллельный сумматор-вычитатель на нейроподобных элементах | 2023 |

|

RU2805774C1 |

| СУММАТОР-ВЫЧИТАТЕЛЬ СТАРШИМИ РАЗРЯДАМИ ВПЕРЕД НА НЕЙРОНАХ | 2002 |

|

RU2205444C1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Параллельный сумматор-вычитатель на элементах нейронной логики | 2020 |

|

RU2780299C2 |

| УСКОРЕННЫЙ УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2006 |

|

RU2322688C2 |

| УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249845C1 |

Изобретение относится к вычислительной технике и может быть использовано для синтеза арифметико-логических устройств, для создания быстродействующих и производительных цифровых устройств суммирования и вычитания чисел в прямых кодах. Техническим результатом является снижение аппаратных средств, повышение надежности работы цифрового сумматора-вычитателя, упрощение алгоритмов работы блока управления устройства. Для этого сумматор-вычитатель содержит блок ввода чисел, блок компарации, блок регистра большего числа, блок суммирования-вычитания, блок регистра меньшего числа, блок регистра результата, блок управления. 10 ил.

Параллельный сумматор-вычитатель на нейронах, содержащий блок сумматоров-вычитателей, блок управления, отличающийся тем, что дополнительно введены блок ввода чисел, блок компарации, блок регистра большего числа, блок регистра меньшего числа, блок регистра результата, причем первый и второй информационные выходы блока ввода чисел соединены соответственно с первым и вторым информационными входами блока компарации, первый информационный выход которого соединен с первым информационным входом блока регистра большего числа, управляющий вход которого соединен с первым управляющим выходом блока компарации, управляющий вход которого соединен с управляющим выходом блока ввода чисел, и с управляющим входом блока суммирования-вычитания, и с пятым управляющим входом блока управления, третий управляющий вход которого соединен с четвертым управляющим выходом блока компарации, второй информационный выход которого соединен с первым информационным входом блока регистра меньшего числа, управляющий вход которого соединен со вторым управляющим выходом блока компарации, третий управляющий выход которого соединен с управляющим входом блока регистра результата, второй информационный вход которого соединен с первым информационным выходом блока управления, третий информационный выход которого соединен со вторым информационным входом блока регистра большего числа, информационный выход которого соединен с первым информационным входом блока суммирования-вычитания, второй информационный вход которого соединен с информационным выходом блока регистра меньшего числа, второй информационный вход которого соединен со вторым информационным выходом блока управления, четвертый управляющий вход которого соединен с управляющим выходом блока суммирования-вычитания, информационный выход которого соединен с первым информационным входом блока регистра результата, первый и второй управляющие входы "Сброс" и "Пуск" блока управления являются внешними входами параллельного сумматора-вычитателя.

| СУММАТОР-ВЫЧИТАТЕЛЬ СТАРШИМИ РАЗРЯДАМИ ВПЕРЕД НА НЕЙРОНАХ | 2002 |

|

RU2205444C1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ | 1990 |

|

RU2043651C1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| RU 94041972 A1, 27.09.1996 | |||

| RU 99109089 A1, 10.03.2001 | |||

| US 5581661 A, 03.12.1996. | |||

Авторы

Даты

2005-02-20—Публикация

2003-07-30—Подача