Изобретение относится к радиотехнике и может быть использовано для измерения несущей частоты импульсных и непрерывных сигналов.

Известно устройство измерения частоты [1, патент США №3956706, G01R 23/04, опубл. 11.05.1976], содержащее в своем составе первый делитель мощности, предназначенный для деления мощности входного сигнала на две равные части. К первому выходу первого делителя мощности подключен второй делитель мощности, а ко второму его выходу подключен третий делитель мощности. Со вторым и третьим делителями мощности соединен выходной двойной тройник и выходной тройник. К указанному выходному двойному тройнику и упомянутому выходному тройнику подключено устройство, обеспечивающее выведение сигналов, которые характеризуют мгновенную частоту упомянутого входного сигнала.

Недостатком известного устройства измерения частоты (1) по патенту США №3956706, G01R 23/04, опубл. 11.05.1976 является то, что устройство не обладает достаточными избирательными свойствами.

Известно устройство измерения частоты [2, патент Франции №1.605.213, опубл. 31.08.73], содержащее пять направленных ответвителей (гибридных колец) и четыре амплитудных детектора с квадратичной вольтамперной характеристикой, три согласованные нагрузки, причем пятый направленный ответвитель выполняет функцию делителя мощности, разветвляя входной сигнал на два направления "синус" и "косинус", выход b первого и третьего направленных ответвителей соединен со входом b второго и четвертого направленных ответвителей, а выход с первого и третьего направленных ответвителей соединен со входом с второго и четвертого направленных ответвителей, выход d первого, второго и пятого направленных ответвителей нагружены на согласованные нагрузки, выходы a и d второго и четвертого направленных ответвителей нагружены на амплитудные детекторы, на выходах которых детектируются четыре напряжения, пропорциональные соответственно (1+cos(ϕ)), (1-cos(ϕ)), (1+sin(ϕ)), (1-sin(ϕ)). При этом угол ϕ пропорционален частоте входного СВЧ-сигнала.

Признаками аналога, совпадающими с признаком заявляемого технического решения, являются направленные ответвители, согласованные нагрузки, а также амплитудные детекторы.

Недостатком известного устройства измерения частоты (2) по патенту Франции №1.605.213, опубл. 31.08.73, как и устройства измерения частоты (1) по патенту США №3956706, G01R 23/04, опубл. 11.05.1976, является то, что устройства не обладают достаточными избирательными свойствами.

Наиболее близким по технической сущности к заявляемому устройству измерения частоты является приемник мгновенного измерения частоты (ПМИЧ) [3, Баландин B.C., Головинский К.В., Дорофеев В.В., Куц В.А. Перспективы развития приемных устройств систем радиоэлектронной борьбы, ЗРЭ №12, 1987] - принятое за прототип, которое обеспечивает измерение несущей частоты импульсных и непрерывных СВЧ-сигналов в широкой полосе частот и большом динамическом диапазоне уровней входных сигналов, обладает высоким быстродействием, а также очевидной реализуемостью схемных и конструкторско-технологических решений.

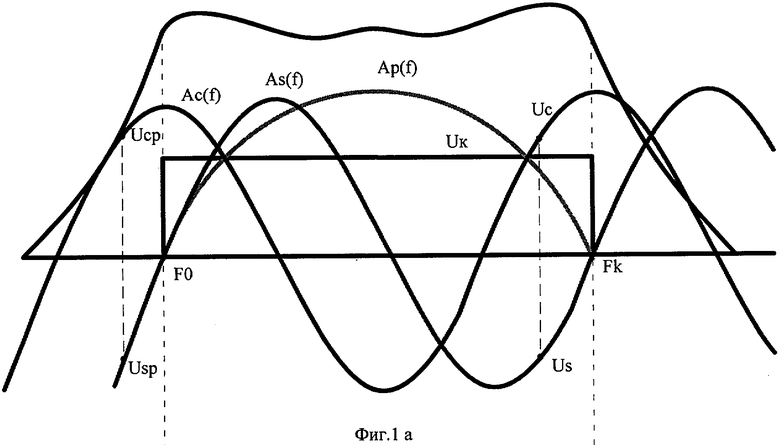

Структурно ПМИЧ состоит из аналоговой и цифровой части. В аналоговой части осуществляется преобразование входного сигнала Uin(t)=U0sin(2πfτ) в косинусный - Uc(f)=U0sin(2πfτ) и синусный - Us(f)=U0sin(2πfτ) сигналы на ее выходе (фиг.1а). Здесь τ - временной интервал (задержка), используемый при формировании сигналов Uc(f) и Us(f) и определяющий ширину полосы ΔF рабочих частот ПМИЧ, ΔF=(Fk-Fn). Сигналы Uc(f) и Us(f) на выходах аналоговой части (на выходах косинусного и синусного каналов) подвергаются аналого-цифровому преобразованию и представляются в виде кодов Uc и Us. В цифровой части ПМИЧ паре кодов Uc и Us ставится в соответствие частота Ftrue входного сигнала. Таким образом, для любого гармонического входного сигнала частоты Fc, находящегося в полосе рабочих частот ΔF=(Fk-F0), всегда находится однозначно соответствующее частоте Fс значение выходной (измеренной) частоты. Однако, вследствие периодичности сигналов Uc(f)=U0sin(2πfτ) и Us(f)=U0sin(2πfτ) пара кодов Uc и Us может существовать и за полосой рабочих частот ПМИЧ, (фиг.1а), что приводит к ошибке измерения несущей частоты. Пусть, например, сигнал находится за полосой рабочих частот и дает соответствующие отклики (Ucp и Usp), эти отклики приведут к формированию кода, соответствующего значению частоты Ffalse, хотя должен был сформироваться код частоты Ftrue. Таким образом, выбор τ не обеспечивает однозначность измерения частоты входного сигнала. Применение полосовых фильтров не позволяет обеспечить однозначность измерения несущей частоты, т.к. реальные фильтры имеют коэффициент прямоугольности более единицы. На фиг.1а для примера показана АЧХ полосового фильтра Апф(f) с коэффициентом прямоугольности 1,5. Как видно из фиг.1а, даже такая прямоугольность не обеспечивает однозначности отсчета частоты из-за недостаточного ослабления сигнала вне полосы рабочих частот. Создание полосовых фильтров на СВЧ с высокой прямоугольностью является сложной технической задачей.

Признаками прототипа, совпадающими с признаком заявляемого технического решения, являются первый, второй делители мощности, первый, второй и третий направленные ответвители, первая линия задержки, согласованная нагрузка, подключенная к первому входу третьего направленного ответвителя, второй вход которого через первую линию задержки подключен ко второму выходу первого делителя мощности, первый выход которого соединен с входом второго делителя мощности, соединенным первым выходом с первым входом первого направленного ответвителя, а вторым выходом - с первым входом второго направленного ответвителя, третий выход которого подключен к первому входу третьего направленного ответвителя, соединенным вторым своим выходом со вторым входом второго направленного ответвителя, первый и второй выход первого направленного ответвителя, а также первый и второй выход второго направленного ответвителя нагружены на входы первого, второго, третьего и четвертого амплитудных детекторов соответственно.

Недостатком прототипа, является то, что за полосой рабочих частот приемника появляются сочетания уровней сигналов Ucp и Usp, которые будут совпадать с уже существующим сочетанием уровней сигналов в полосе рабочих частот, что вызовет появление ложной измеренной частоты входного сигнала Ffalse. Возможность появления таких сигналов за полосой ΔF следует из указанных в прототипе форм АЧХ. Они содержат гармонические функции sin(ϕ) и cos(ϕ), определенные во всей полосе частот, что приведет к неопределенности отсчета частоты.

Задачей, на решение которой направленно предполагаемое изобретение, является обеспечение режекции ложных сигналов за полосой рабочих частот.

Технический результат, достигаемый при осуществлении предполагаемого изобретения, заключается в режекции ложных сигналов за полосой рабочих частот устройства измерения частоты и исключении неоднозначности отсчета.

Технический результат достигается тем, что в известное устройство измерения частоты, выполненное по схеме приемника мгновенного определения частоты, включающее в себя первый, второй делители мощности, первый, второй и третий направленные ответвители, первую линию задержки, согласованную нагрузку, подключенную к первому выходу третьего направленного ответвителя, второй вход которого через первую линию задержки подключен ко второму выходу первого делителя мощности, первый выход которого соединен с входом второго делителя мощности, соединенного первым выходом с первым входом первого направленного ответвителя, а вторым выходом - с первым входом второго направленного ответвителя, третий выход которого подключен к первому входу третьего направленного ответвителя, соединенным вторым своим выходом со вторым входом первого направленного ответвителя, первый и второй выходы которого, а также первый и второй выход второго направленного ответвителя нагружены на входы первого, второго, третьего и четвертого амплитудных детекторов соответственно, введены усилитель ограничитель, третий и четвертый делители мощности, вторая линия задержки, первый и второй двухканальные разностные видеоусилители, первый и второй аналого-цифровые преобразователи, программируемая логическая матрица, сумматор, пятый амплитудный детектор, одноканальный видеоусилитель, компаратор, при этом выход усилителя ограничителя подключен ко входу третьего делителя мощности, соединенного первым своим выходом с входом первого делителя мощности, а вторым выходом - с входом четвертого делителя мощности, выходы первого и второго амплитудных детекторов подключены к первому и второму входам первого двухканального разностного видеоусилителя соответственно, а выходы третьего и четвертого амплитудных детекторов соединены с первым и вторым входами второго двухканального разностного видеоусилителя соответственно, выход первого двухканального разностного видеоусилителя через первый аналого-цифровой преобразователь соединен с первым входом программируемой логической матрицы, выход второго двухканального разностного видеоусилителя через второй аналого-цифровой преобразователь соединен со вторым входом программируемой логической матрицы, первый выход четвертого делителя мощности подключен через вторую линию задержки к первому входу сумматора, соединенного вторым своим входом со вторым выходом четвертого делителя мощности, выход сумматора через пятый амплитудный детектор, одноканальный видеоусилитель, а также компаратор соединен с третьим входом программируемой логической матрицы, выход которой является выходом устройства определения частоты, а входом устройства - вход усилителя ограничителя.

Структурная схема заявляемого измерителя частоты представлена на фиг.2.

Измеритель мгновенной частоты содержит: усилитель ограничитель 1, третий делитель мощности 2, первый делитель мощности 3, второй делитель мощности 4, первый направленный ответвитель 5, второй направленный ответвитель 6, третий направленный ответвитель 7, первую линию задержки 8, согласованную нагрузку 9, первый амплитудный детектор 10, второй амплитудный детектор 11, третий амплитудный детектор 12, четвертый амплитудный детектор 13, первый двухканальный разностный видеоусилитель 14, второй двухканальный разностный видеоусилитель 15, первый аналого-цифровой преобразователь 16, второй аналого-цифровой преобразователь 17, программируемая логическая матрица 18, четвертый делитель мощности 19, вторую линия задержки 20, сумматор 21, пятый амплитудный детектор 22, третий одноканальный видеоусилитель 23, компаратор 24.

Усилитель ограничитель 1, вход которого является входом устройства, соединен с входом третьего делителя мощности 2, соединенным первым своим выходом с входом первого делителя мощности 3, а вторым - с входом четвертого делителя мощности 19, первый выход первого делителя мощности 3 соединен с входом второго делителя мощности 4, первым своим выходом соединенным с первым входом первого направленного ответвителя 5, а вторым выходом - с первым входом второго направленного ответвителя 6, второй выход второго делителя мощности 3 через первую линию задержки 8 подключен ко второму входу третьего направленного ответвителя 7, соединенным первым своим выходом с согласованной нагрузкой 9, а вторым выходом - со вторым входом первого направленного ответвителя 5, третий выход второго направленного ответвителя 6 подключен к первому входу третьего направленного ответвителя 7, первый, второй выходы первого направленного ответвителя 5 и первый, второй выходы второго направленного ответвителя 6 соединены с входами первого 10, второго 11, третьего 12 и четвертого 13 амплитудных детекторов соответственно, выходы первого 10 и второго 11 амплитудных детекторов подключены к первому и второму входам первого двухканального разностного видеоусилителя 14 соответственно, соединенного через первый аналого-цифровой преобразователь 16 с первым входом программируемой логической матрицы 18, выходы третьего 12 и четвертого 13 амплитудных детекторов подключены к первому и второму входам второго двухканального разностного видеоусилителя 15 соответственно, соединенного выходом через второй аналого-цифровой преобразователь 17 со вторым входом программируемой логической матрицы 18, первый выход четвертого делителя мощности 19 соединен через вторую линию задержки 20 с первым входом сумматора 21, соединенным вторым своим входом с вторым выходом четвертого делителя мощности 19, выход сумматора 21 через пятый амплитудный детектор 22, одноканальный видеоусилитель 23 и компаратор 24, соединен с третьим входом программируемой логической матрицы 18, выход которой является выходом устройства определения частоты.

Заявляемое устройство измерения частоты работает следующим образом. Формирование полосы режекции поясняется фиг.1 и фиг.2. При этом фиг.1а, б показывает принцип формирования полосы режекции устройства, а по структурной схеме фиг.2 поясняется принцип работы устройства.

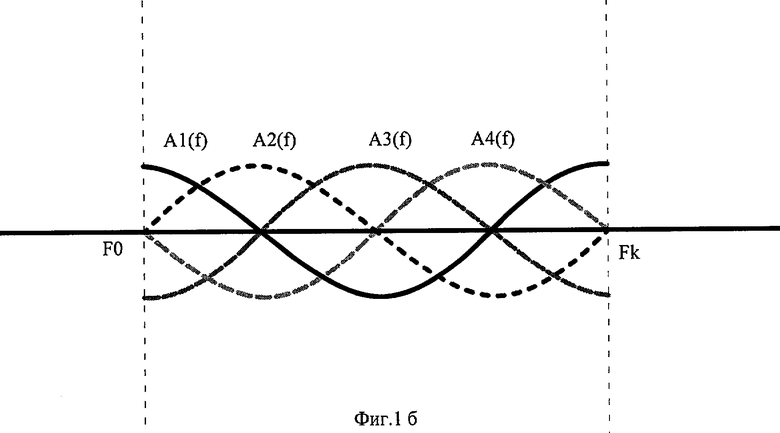

Усилитель ограничитель 1 обеспечивает сужение динамического диапазона входного СВЧ-сигнала и обеспечивает необходимый уровень мощности сигнала на входе ПМИЧ. После третьего делителя мощности 2 входной сигнал разветвляется на два канала: измерительный и избирательный. В измерительном канале на делителе мощности 3 сигнал разделяется на два направления: задержанный и незадержанный. Линия задержки 8 выбирается, таким образом, чтобы в диапазоне рабочих частот изменение фазы сигнала было в пределах от 0° до 360°. Первый 5 и второй 6 направленный ответвители, нагруженные на амплитудные детекторы 10, 11, 12, 13, образуют фазовые детекторы. Третий направленный ответвитель 7 обеспечивает формирование разности фаз между синусным и косинусным каналами на 90°. На выходе ПМИЧ детектируются сигналы с амплитудно-частотными характеристиками, изображенными на фиг.16 (A1(f), A2(f), A3(f), A4(f)). Далее эти сигналы попарно A1(f) и A3(f), а также A2(f) и A4(f) поступают на дифференциальные входы первого и второго двухканальных разностных видеоусилителей 14 и 15, на выходе которых образуются сигналы As(f) - амплитудно-частотная характеристика синусного канала и Ac(f) - амплитудно-частотная характеристика косинусного канала, изображенные на фиг.1а. С выходов видеоусилителей 14 и 15 сигналы As(f) и Ac(f) поступают на входы первого и второго аналого-цифровых преобразователей 16, 17. На выходах аналого-цифровых преобразователей 16, 17 формируются соответственно коды анализируемого сигнала Us(f) и Uc(f), которые однозначно определяют частоту входного сигнала в полосе рабочих частот ПМИЧ ΔF=(Fk-F0). Коды амплитудно-частотных характеристик Us(f) и Uc(f) поступают на первый и второй входы программируемой логической матрицы 18, где они записываются в постоянное запоминающее устройство.

В избирательном канале, обеспечивающем режекторные свойства устройства, входной сигнал делителем мощности 19 делится на два направления: задержанный и незадержанный. При этом величина второй линии задержки 20 выбирается таким образом, чтобы фаза входного сигнала в полосе рабочих частот изменялась в пределах от 0° до 180°. Выделяемое пятым амплитудным детектором 22 напряжение Ap(f), изображенное на фиг.1а, через видеоусилитель 23 поступает на компаратор 24, на выходе которого формируется сигнал Uк ТТЛ уровня. Причем в полосе рабочих частот устройства сигнал Uк принимает уровень логической 1, а вне полосы - значение логического 0. При наличие сигнала Uк уровнем логической единицы на третьем входе программируемой логической матрицы 18 на ее выходе формируется код измеряемой частоты. Этот код может формироваться в пределах полосы ΔF=(Fk-F0), при этом получим значение измеренной частоты Ftrue, и за пределами полосы ΔF=(Fk-F0) при этом получим ложное значение измеренной частоты Ffalse. Избирательный канал устраняет эту неоднозначность (т.е. исключает появление ложного значения измеренной частоты на выходе устройства).

Таким образом, предлагаемое устройство измерения частоты формирует код измеренной частоты только для входных сигналов, частота которых попадает в полосу рабочих частот устройства ΔF=(Fk-F0), а сигналы вне полосы рабочих частот режектируются.

Предлагаемое устройство измерения частоты может быть выполнено на основе серийно выпускаемых элементов. Усилитель ограничитель может быть реализован из последовательно соединенных усилительных модулей СВЧ, например, типа М421102 бШ2.030.220ТУ (для диапазона частот от 8 до 18 ГГц). В качестве направленного ответвителя используется широкополосный мост Ланге в микрополосковом исполнении. Линии задержки в зависимости от диапазонов рабочих частот могут выполнены как в микрополосковом исполнении, так и в виде кабеля определенной длины. Аналого-цифровые преобразователи могут быть реализованы на микросхемах AD9057BRS-80. Компаратор на микросхеме 521СА3. Программируемая логическая матрица может быть реализована на микросхемах EPF10K30RC240-3 фирмы Atmel с постоянным запоминающим устройством AT29C512-15TI.

Представленные чертежи и описание устройства измерения частоты позволяют, используя существующую элементную базу, изготовить его промышленным способом и использовать по своему прямому назначению, что позволяет сделать вывод о промышленной применимости предлагаемого изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА ОБНАРУЖЕНИЯ РАДИОЛОКАЦИОННЫХ СИГНАЛОВ | 2003 |

|

RU2256937C1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ ПАРАМЕТРОВ ИМПУЛЬСНЫХ СВЧ СИГНАЛОВ С ШИРОКИМ ДИАПАЗОНОМ РАБОЧИХ ЧАСТОТ | 2021 |

|

RU2775355C1 |

| СПОСОБ И УСТРОЙСТВО СЕЛЕКЦИИ СИГНАЛОВ НАДВОДНОЙ ЦЕЛИ В МОНОИМПУЛЬСНОЙ РЛС | 2004 |

|

RU2278397C2 |

| АКТИВНАЯ ФАЗИРОВАННАЯ АНТЕННАЯ РЕШЕТКА | 2012 |

|

RU2531562C2 |

| СПОСОБ СНИЖЕНИЯ НИЖНЕЙ ГРАНИЦЫ ИЗМЕРЕНИЯ МАЛЫХ ВЫСОТ ДО НУЛЯ И УСТРОЙСТВО КОГЕРЕНТНОГО ИМПУЛЬСНО-ДОПЛЕРОВСКОГО РАДИОВЫСОТОМЕРА, РЕАЛИЗУЮЩЕГО СПОСОБ | 2008 |

|

RU2412450C2 |

| ИМПУЛЬСНО-ДОПЛЕРОВСКИЙ РАДИОВЫСОТОМЕР | 2012 |

|

RU2522907C2 |

| СИСТЕМА ОБНАРУЖЕНИЯ РАДИОЛОКАЦИОННЫХ СИГНАЛОВ | 2006 |

|

RU2309426C1 |

| ИМПУЛЬСНО-ДОПЛЕРОВСКАЯ РАДИОВЫСОТОМЕРНАЯ СИСТЕМА | 2012 |

|

RU2500001C1 |

| МОНОИМПУЛЬСНАЯ РЛС | 2004 |

|

RU2267137C1 |

| ЧАСТОТНО-МОДУЛИРОВАННЫЙ РАДИОВЫСОТОМЕР | 2003 |

|

RU2263330C2 |

Устройство включает в себя измерительный и избирательный каналы. В измерительном канале принимаемый сигнал разделяется на задержанный и незадержанный. Формируются сигналы АЧХ синусного канала и АЧХ косинусного канала. Далее эти сигналы поступают на входы аналого-цифровых преобразователей, где формируются коды частоты, эти коды поступают на первый и второй входы программируемой логической матрицы. Избирательный канал предназначен для выделения сигналов, частота которых попадает в полосу рабочих частот устройства, а сигналы вне рабочих частот режектируются. Поступающий сигнал разделяется на задержанный и незадержанный. Далее сигналы поступают на амплитудный детектор и через видеоусилитель и компаратор на выходе которого формируется сигнал, принимаемый в полосе рабочих частот уровень логической 1, а вне полосы - значение логического 0. Этот сигнал поступает на третий вход программируемой логической матрицы, на выходе которой формируется код измеряемой частоты. Технический результат заключается в режекции ложных сигналов за полосой рабочих частот и исключении неоднозначности отсчета частоты. 2 ил.

Устройство измерения частоты, включающее в себя первый, второй делители мощности, первый, второй и третий направленные ответвители, первую линию задержки, согласованную нагрузку, подключенную к первому выходу третьего направленного ответвителя, второй вход которого через первую линию задержки подключен ко второму выходу первого делителя мощности, первый выход которого соединен с входом второго делителя мощности, соединенного первым выходом с первым входом первого направленного ответвителя, а вторым выходом - с первым входом второго направленного ответвителя, третий выход которого подключен к первому входу третьего направленного ответвителя, соединенным вторым своим выходом со вторым входом первого направленного ответвителя, первый и второй выходы которого, а также первый и второй выход второго направленного ответвителя нагружены на входы первого, второго, третьего и четвертого амплитудных детекторов соответственно, отличающееся тем, что в него введены усилитель ограничитель, третий и четвертый делители мощности, вторая линия задержки, первый и второй двухканальные разностные видеоусилители, первый и второй аналого-цифровые преобразователи, программируемая логическая матрица, сумматор, пятый амплитудный детектор, одноканальный видеоусилитель, компаратор, при этом выход усилителя ограничителя подключен ко входу третьего делителя мощности, соединенного первым своим выходом с входом первого делителя мощности, а вторым выходом - с входом четвертого делителя мощности, выходы первого и второго амплитудных детекторов подключены к первому и второму входам первого двухканального разностного видеоусилителя соответственно, а выходы третьего и четвертого амплитудных детекторов соединены с первым и вторым входами второго двухканального разностного видеоусилителя соответственно, выход первого двухканального разностного видеоусилителя через первый аналого-цифровой преобразователь соединен с первым входом программируемой логической матрицы, выход второго двухканального разностного видеоусилителя через второй аналого-цифровой преобразователь соединен со вторым входом программируемой логической матрицы, первый выход четвертого делителя мощности подключен через вторую линию задержки к первому входу сумматора, соединенного вторым своим входом со вторым выходом четвертого делителя мощности, выход сумматора через пятый амплитудный детектор, одноканальный видеоусилитель, а также компаратор соединен с третьим входом программируемой логической матрицы, выход которой является выходом устройства определения частоты, а входом устройства - вход усилителя ограничителя.

| US 3956706, 11.05.1976 | |||

| RU 2003115 C1, 15.11.1993 | |||

| СУПЕРГЕТЕРОДИННЫЙ ПРИЕМНИК-ЧАСТОТОМЕР | 2004 |

|

RU2287833C2 |

Авторы

Даты

2008-02-20—Публикация

2005-12-02—Подача