Изобретение относится к вычислительной технике и может быть использовано в модулярных нейрокомпьютерах для реализации основной операции - определение вычета (остатка) числа, которое используется как при выполнении арифметических операций, так и при выполнении операции ввода данных.

Известна нейронная сеть для классификации сигналов или символьной информации (заявка 19917957, МПК7 G06F/15/18, опубликована 26.10.2000, немецкая), содержащая входной, выходной, скрытый слои и связи между ними. Однако такие нейронные сети предназначены для классификации целей радиолокатора.

Наиболее близким по технической сущности к заявленному устройству является нейронная сеть конечного кольца (заявка 2003124689, МПК7 G06N 3/02, RU), содержащая арифметические элементы, имеющие характеристики взвешенного суммирования, и элементы, имеющие характеристику оператора по модулю.

Однако известная нейронная сеть конечного кольца требует больших аппаратурных затрат.

Цель изобретения - сокращение оборудования.

Указанная цель достигается тем, что в нейронную сеть введены мультиплексор, просмотровые таблицы (память) и демультиплексор.

Предлагается эффективный метод преобразования двоичного числа в систему остаточных классов на основе разбиения исходного двоичного числа на отдельные форматы, для которых отводится заранее известное количество В-двоичных разрядов. Тогда n-битное двоичное число может быть выражено как комбинация  взвешенных (позиционных) форматов размерностью B бит (разрядов). При этом позициям каждого формата

взвешенных (позиционных) форматов размерностью B бит (разрядов). При этом позициям каждого формата  присваивается определенный вес 2j, где j=0, В, 2В,...MB.

присваивается определенный вес 2j, где j=0, В, 2В,...MB.

Прямое преобразование двоичного числа в модулярное осуществляется с помощью модульного суммирования остатков по модулю рi(i=1, 2,..., n) В разрядов  форматов с учетом их весов.

форматов с учетом их весов.

На основании сказанного любое двоичное число может быть записано в виде

где: В - количество разрядов выбранного формата;

М - степень формата;

хi - коэффициент 0 или 1;

j=0, B, 2В,...MB - позиция формата;

i - позиция разряда в формате.

Если развернуть выражение (1), тогда

Из выражения (2) видно, что число Х может быть представлено двоичным числом ширины М×В разрядов.

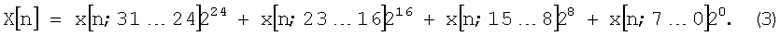

Если в качестве примера входное слово взять как 32-разрядное число и число разрядов в формате взять равным 8 бит, тогда входное число может быть выражено как комбинация четырех байтов:

Таким образом, остаток Х(n) по модулю рi может быть представлен в виде

Каждый член выражения (4) с учетом веса 2j может быть предварительно вычислен и сохранен в просмотровых таблицах. Организация просмотровых таблиц определяется двоичным представлением модуля рi и выражается формулой m=[log pi]. ПЛИС устройства имеют встроенные логические блоки. В зависимости от семейства каждый логический блок включает одну или более просмотровых таблиц размером 24×1 бит, выходной регистр, специализированную логическую схему ускоренного переноса.

Схема конвейерной нейронной сети конечного кольца приведена на фигуре 1.

Схема состоит из мультиплексора 2 на четыре группы входов 1 (разрядность каждой группы равна 1 байту) с адресным входом 3, [log pi]-LUT таблиц 4, трех умножителей 7 по модулю pi, демультиплексора 5 с адресным входом 6, осуществляющего подключение выхода LUT таблицы на один из четырех выходов и нейронной сети конечного кольца 8 для суммирования по mod pi остаточных значений байтов с учетом их весов. Принцип работы изобретения излагается ниже. Процесс преобразования подразделяется на 4 этапа, каждый из которых выполняется определенной частью аппаратного обеспечения, причем все эти части могут работать параллельно. Конвейер из четырех стадий (а), состояние каждой стадии в зависимости от количества пройденных циклов (б) для 11 циклов, приведен на фигуре 2. На фигуре 2,а изображен конвейер из 4 блоков, которые называются стадиями. Исходное входное число разделено на 4 байта: нулевой, первый, второй и третий. В LUT таблицу помещены заранее вычисленные все возможные значения нулевого байта по mod pi, которое будет использовано при преобразованиях всех байтов. Учет веса каждого байта определяется синаптическими весами wj умножителей.

Стадия C1 вызывает старший байт числа x[31, 24] и помещает его на выход мультиплексора, выход которого является входом LUT-таблицы. Вызов байта определяется кодом числа, поданным на адресные входы 3 мультиплексра. Стадия C2 считывает их LUT-таблицы значение вычета (остатка) байта по mod pi. Стадия С3 выполняет умножение считанного остатка  их памяти LUT-таблицы на значение соответствующего синаптического веса

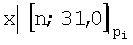

их памяти LUT-таблицы на значение соответствующего синаптического веса  где j - степень байта. Коммутация байтов осуществляется демультиплексором под действием адресного входа 6. Стадия С4 выполняет суммирование остатков всех байтов по mod pi. Суммирование выполняется нейронной сетью конечного кольца по mod pi.

где j - степень байта. Коммутация байтов осуществляется демультиплексором под действием адресного входа 6. Стадия С4 выполняет суммирование остатков всех байтов по mod pi. Суммирование выполняется нейронной сетью конечного кольца по mod pi.

Пример 1. Пусть дано число Х=10000001 10000011 00011011 10100010. Найти остаток числа X по mod 7 (фигура 1). Весовые коэффициенты w3=|224|7=1; w2=|216|7=4; w1=|28|7=2; w0=|20|7=1.

В примере в качестве формата принято В=8 разрядов из соображений использования для преобразования чисел просмотровых таблиц LUT (look-up tables) программируемых логических интегральных схем Xilinx серии ХС4000, которые имеют 8 входов.

На фиг.2,б приведено действие конвейера во времени. Во время цикла 1 стадия C1 работает над третьим байтом, помещая его на выход мультиплексора. Во время цикла 2 стадия С2 считывает из памяти (LUT-таблицы) значение третьего байта, в то время как стадия С1 помещает на выход мультиплексора значение второго байта. Во время цикла 3 стадия С3 выполняет умножение считанного остатка третьего байта по mod pi на его синаптический вес w3, стадия С2 считывает значение первого байта, а стадия С1 помещает значение нулевого байта на выход мультиплексора. Во время цикла 4 стадия С4 выполняет суммирование значения остатка третьего байта, С3 выполняет умножение значения второго байта на синаптический вес w2, С2 считает первый байт, и С1 помещает на выход мультиплексора значение нулевого байта и так далее. На седьмом цикле на выходе сумматора формируется значение остатка числа  . И далее через каждые 4 следующих цикла формируются остатки следующих чисел. Итак, остаток первого числа формируется через 7 циклов, а остатки следующих чисел будут формироваться через каждые 4 цикла.

. И далее через каждые 4 следующих цикла формируются остатки следующих чисел. Итак, остаток первого числа формируется через 7 циклов, а остатки следующих чисел будут формироваться через каждые 4 цикла.

Предположим, что время цикла у этого преобразователя 5 нс. Тогда для того, чтобы один байт прошел через весь конвейер, требуется 20 нс. На первый взгляд может показаться, что такой преобразователь может выполнять 50 млн байтов в секунду, в действительности же скорость его гораздо выше. Во время каждого цикла (5 нс) завершается преобразование одного байта, поэтому преобразователь выполняет не 50 млн, а 200 млн байт в секунду, тогда преобразование четырех байтов выполняется со скоростью 50 млн входных слов в секунду.

Для реализации данного изобретения требуется [log рi]-LUT-таблиц, мультиплексор на 4 входа, демультиплексор на 4 выхода, три умножителя по mod pi и одна нейронная сеть конечного кольца для четырех групп входов. Известные схемы используют 15 нейронных сетей конечного кольца на 2 группы входов.

Аппаратные затраты схемы: мультиплексора, демультиплексора, умножителей на константу и одной нейронной сети конечного кольца намного меньше аппаратных затрат 15 нейронных сетей конечного кольца.

| название | год | авторы | номер документа |

|---|---|---|---|

| НЕЙРОННАЯ СЕТЬ УСКОРЕННОГО МАСШТАБИРОВАНИЯ МОДУЛЯРНЫХ ЧИСЕЛ | 2007 |

|

RU2359325C2 |

| НЕЙРОННАЯ СЕТЬ С ПОРОГОВОЙ (k, t) СТРУКТУРОЙ ДЛЯ ПРЕОБРАЗОВАНИЯ ОСТАТОЧНОГО КОДА В ДВОИЧНЫЙ ПОЗИЦИОННЫЙ КОД | 2008 |

|

RU2380751C1 |

| АДАПТИВНАЯ ПАРАЛЛЕЛЬНО-КОНВЕЙЕРНАЯ НЕЙРОННАЯ СЕТЬ ДЛЯ КОРРЕКЦИИ ОШИБОК | 2003 |

|

RU2279131C2 |

| УСТРОЙСТВО ДЛЯ ОСНОВНОГО ДЕЛЕНИЯ МОДУЛЯРНЫХ ЧИСЕЛ В ФОРМАТЕ СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ | 2013 |

|

RU2559772C2 |

| НЕЙРОННАЯ СЕТЬ ДЛЯ КОРРЕКЦИИ ОШИБОК В МОДУЛЯРНЫХ НЕЙРОКОМПЬЮТЕРАХ | 2003 |

|

RU2256213C2 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЗНАКА МОДУЛЯРНОГО ЧИСЛА | 2011 |

|

RU2503995C2 |

| НЕЙРОННАЯ СЕТЬ ДЛЯ ОПРЕДЕЛЕНИЯ КООРДИНАТ ТОЧЕК НА ЭЛЛИПТИЧЕСКОЙ КРИВОЙ | 2008 |

|

RU2397541C2 |

| НЕЙРОННАЯ СЕТЬ ДЛЯ ПРЕОБРАЗОВАНИЯ ОСТАТОЧНОГО КОДА В ДВОИЧНЫЙ ПОЗИЦИОННЫЙ КОД | 2006 |

|

RU2318238C1 |

| НЕЙРОННАЯ СЕТЬ ДЛЯ ВЫЧИСЛЕНИЯ ПОЗИЦИОННЫХ ХАРАКТЕРИСТИК НЕПОЗИЦИОННОГО КОДА | 2003 |

|

RU2257615C2 |

| НЕЙРОННАЯ СЕТЬ ДЛЯ РАСШИРЕНИЯ КОРТЕЖА ЧИСЛОВОЙ СИСТЕМЫ ВЫЧЕТОВ | 2003 |

|

RU2256226C2 |

Изобретение относится к конвейерным нейронным сетям конечного кольца. Техническим результатом является сокращение аппаратных затрат преобразователя двоичного кода в код системы остаточных классов. Для этого конвейерная нейронная сеть конечного кольца содержит мультиплексор, просмотровую таблицу (память), где хранятся предварительно вычисленные значения формата с весовым коэффициентом w=20, демультиплексор, умножители на константы 2j и суммирующую нейронную сеть конечного кольца. 3 ил.

Конвейерная нейронная сеть конечного кольца для определения остатка числа по модулю, содержащая нейронную сеть конечного кольца с весовыми коэффициентами wj, отличающаяся тем, что в нее введены мультиплексор, демультиплексор и просмотровая таблица, представленная в виде памяти, реализующая вычислительную модель (х020+х121+...XВ-12В-1)20, где В - количество разрядов выбранного формата; хi - коэффициент 0 или 1; i - позиция разряда в формате, входы просмотровой таблицы подключены к выходам мультиплексора, входы которого являются входами конвейерной нейронной сети конечного кольца, а выходы просмотровой таблицы с разрядностью m=[log pi] подключены ко входу демультиплексора, который коммутируется последовательно под действием адресного входа демультиплексора на входы соответствующих схем умножителей на константы  выходы которых суммируются нейронной сетью конечного кольца, выход которой является

выходы которых суммируются нейронной сетью конечного кольца, выход которой является  выходом конвейерной нейронной сети конечного кольца, при этом в мультиплексоре вызов байта определяется кодом числа, поданным на адресные входы мультиплексора.

выходом конвейерной нейронной сети конечного кольца, при этом в мультиплексоре вызов байта определяется кодом числа, поданным на адресные входы мультиплексора.

| RU 2003124689 A1, 27.05.2005 | |||

| RU 2003124041 A1, 27.01.2005 | |||

| НЕЙРОННАЯ СЕТЬ ДЛЯ КОРРЕКЦИИ ОШИБОК В МОДУЛЯРНЫХ НЕЙРОКОМПЬЮТЕРАХ | 2003 |

|

RU2256213C2 |

| КЛЕЙ-РАСПЛАВ | 0 |

|

SU357212A1 |

| Устройство для контроля положения петли рулонного материала | 1972 |

|

SU482376A1 |

Авторы

Даты

2008-02-20—Публикация

2006-06-20—Подача