Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления широкополосных аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ) и компараторах, работающих с двумя сигналами, имеющими синфазную составляющую).

Известны схемы двухтактных дифференциальных усилителей (ДУ) на основе трех токовых зеркал [1-13], которые стали основой многих серийных операционных усилителей, выпускаемых как зарубежными (СА3080, НА2700 и др.), так и российскими (К154УД1 и др.) микроэлектронными фирмами. В связи с высокой популярностью такой архитектуры ДУ на их модификации выдано более 50 патентов в различных странах. Предлагаемое изобретение относится к данному подклассу устройств.

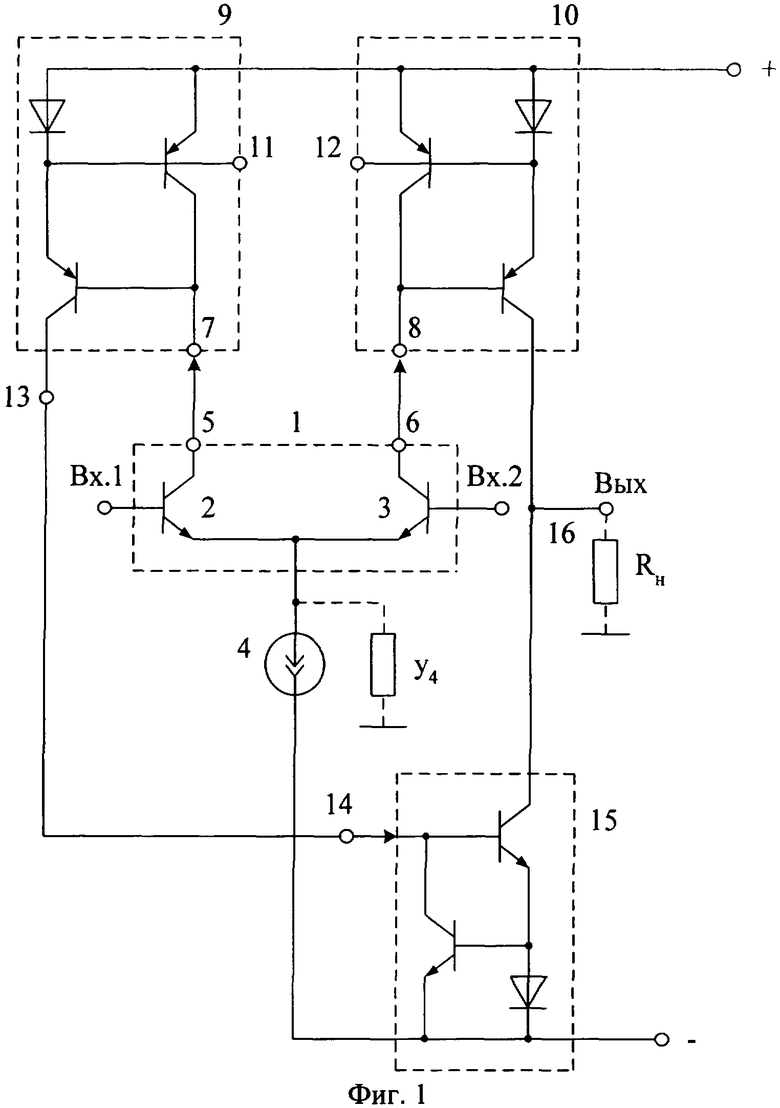

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте США №3921090, содержащий входной дифференциальный каскад 1 на транзисторах 2 и 3 с источником опорного тока 4 в их общей эмиттерной цепи, первый 5 и второй 6 противофазные токовые выходы которого соединены с инвертирующими токовыми входами 7 и 8 первого 9 и второго 10 токовых зеркал, имеющих также неинвертирующие токовые входы 11 и 12, причем токовый выход 13 первого токового зеркала 9 соединен со входом 14 третьего токового зеркала 15, а токовые выходы второго 10 и третьего 15 токовых зеркал связаны с выходом 16 дифференциального усилителя.

Существенный недостаток известного ДУ фиг.1 состоит в том, что он имеет сравнительно невысокое ослабление входных синфазных сигналов, что отрицательно сказывается на точностных параметрах неинвертирующих решающих усилителей и компараторов двух сигналов на его основе.

Основная цель предлагаемого изобретения состоит в повышении коэффициента ослабления входных синфазных сигналов.

Поставленная цель достигается тем, что в дифференциальный усилитель фиг.1, содержащий входной дифференциальный каскад 1 на транзисторах 2 и 3 с источником опорного тока 4 в их общей эмиттерной цепи, первый 5 и второй 6 противофазные токовые выходы которого соединены с инвертирующими токовыми входами 7 и 8 первого 9 и второго 10 токовых зеркал, имеющих также неинвертирующие токовые входы 11 и 12, причем токовый выход 13 первого токового зеркала 9 соединен со входом 14 третьего токового зеркала 15, а токовые выходы второго 10 и третьего 15 токовых зеркал связаны с выходом 16 дифференциального усилителя, вводятся новые элементы и связи - в схему введен каскад выделения входного синфазного сигнала 17, имеющий потенциальный 18, а также первый 19 и второй 20 токовые выходы и дополнительный источник опорного тока 21, соединенный с его потенциальным выходом 18, причем первый токовый выход 19 каскада выделения входного синфазного сигнала 17 соединен с неинвертирующим токовым входом 11 первого токового зеркала 9, а второй токовый выход 20 каскада выделения входного синфазного сигнала 17 соединен с неинвертируюшим токовым входом 12 второго токового зеркала 10.

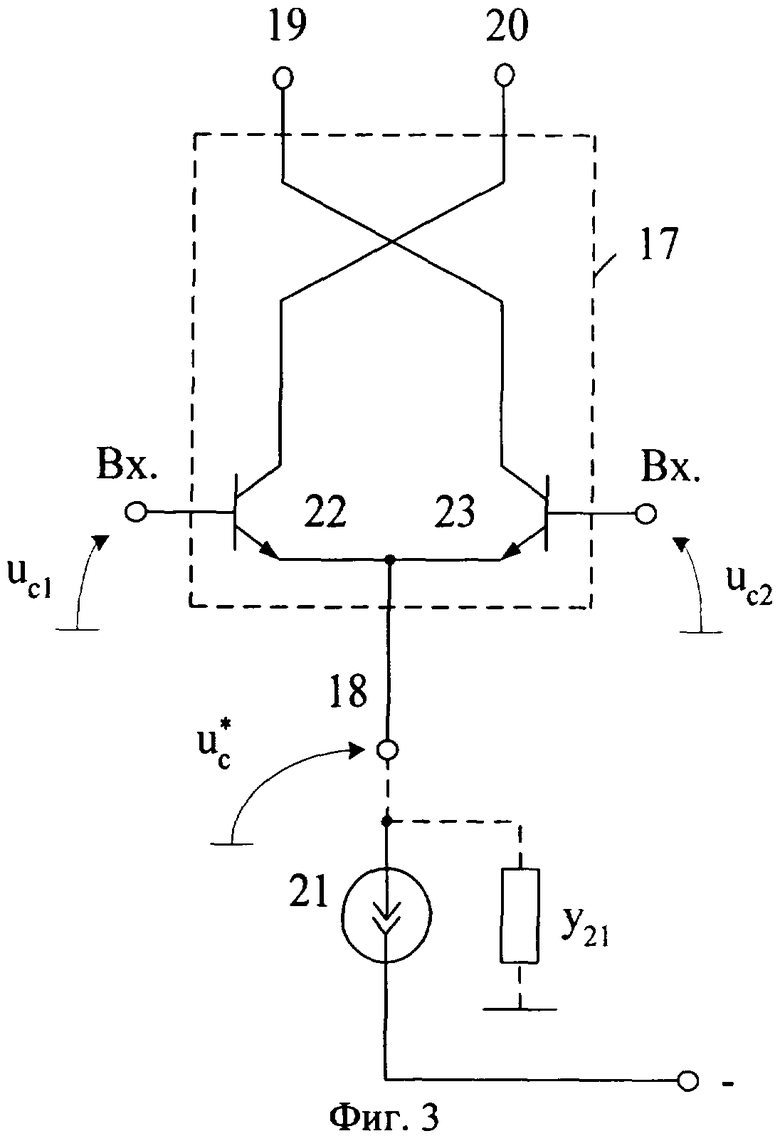

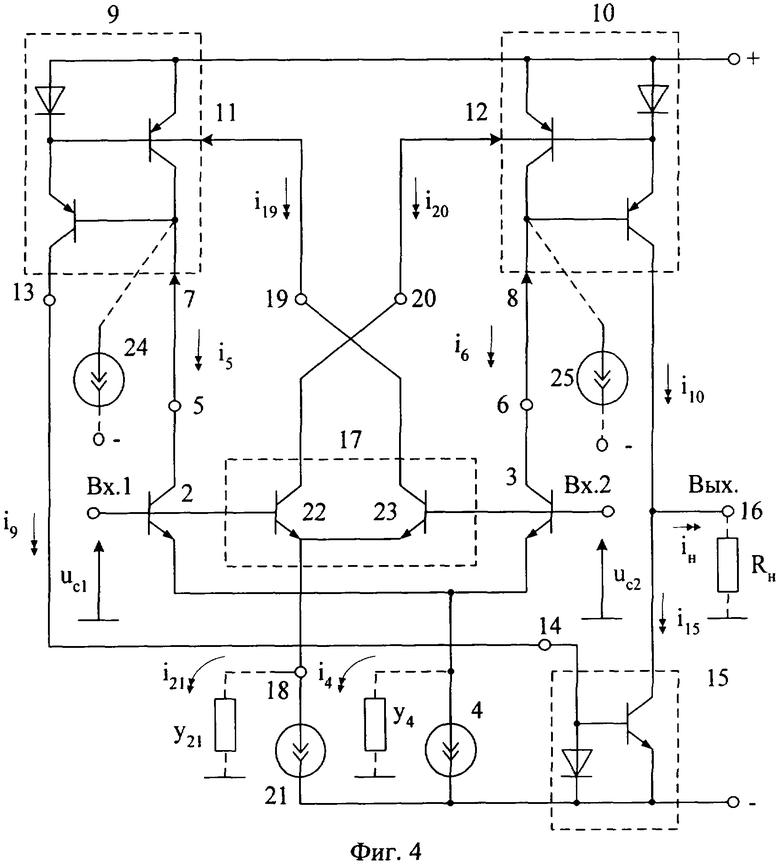

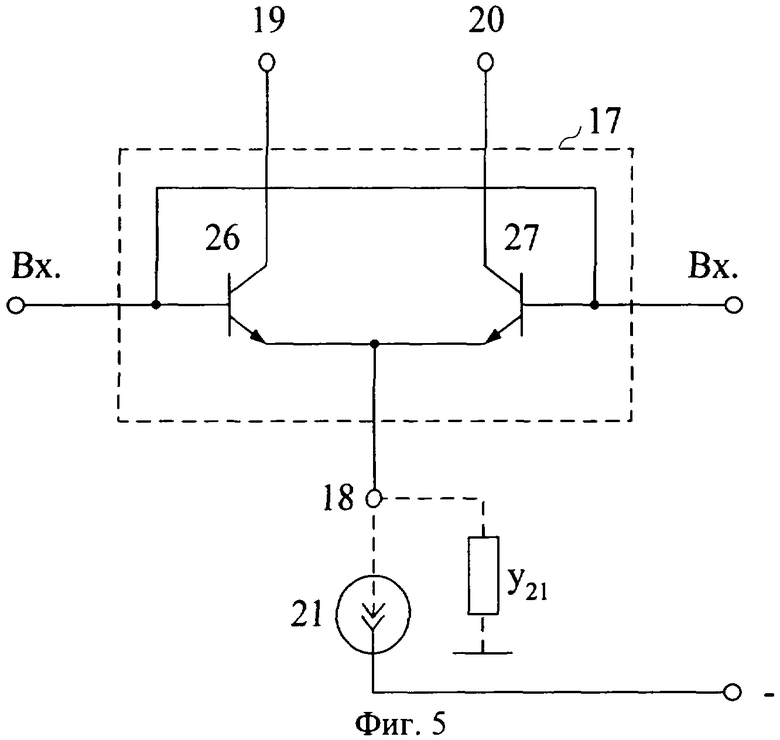

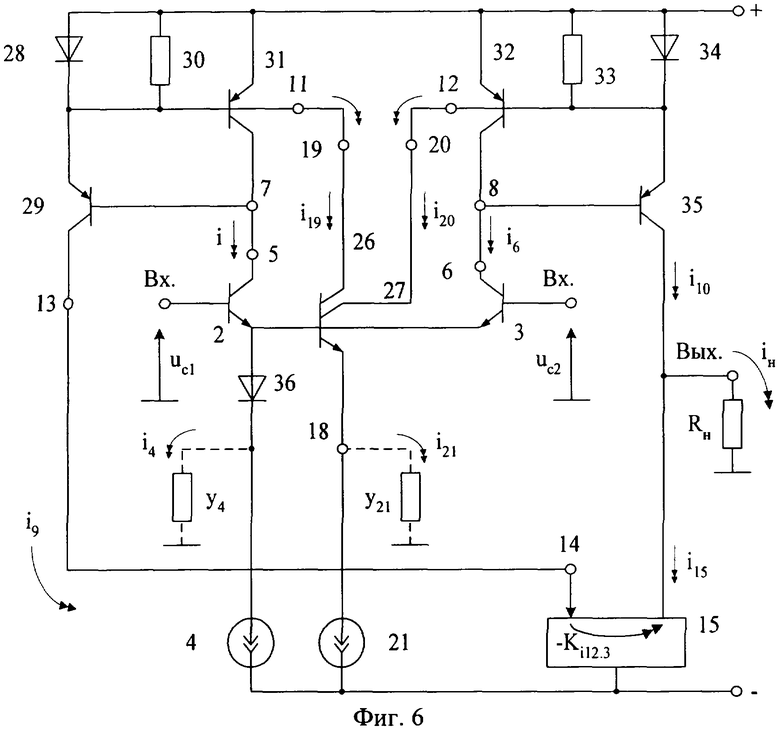

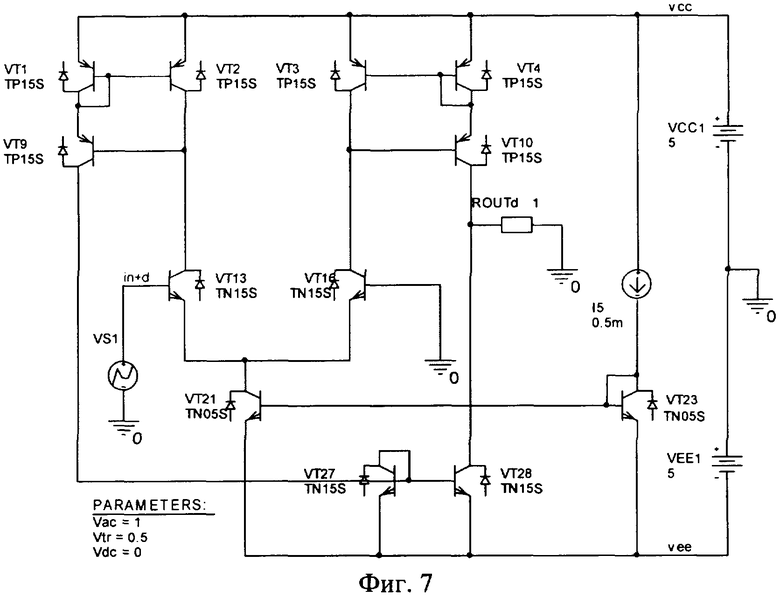

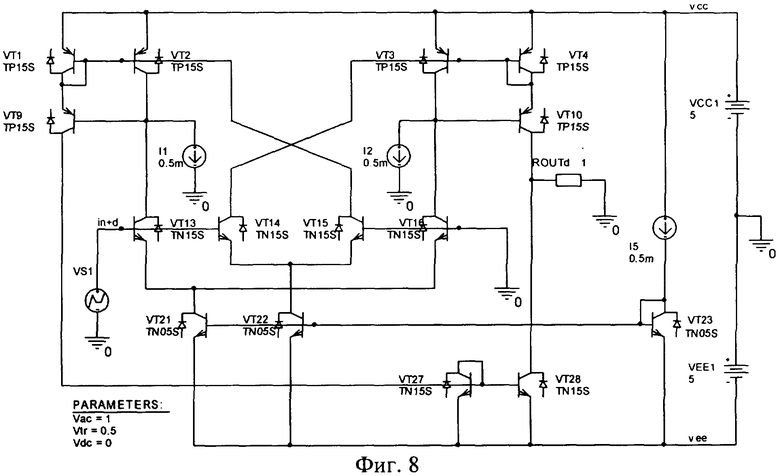

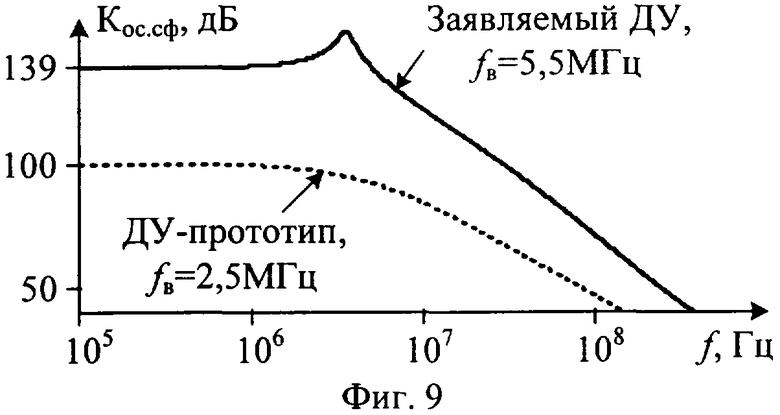

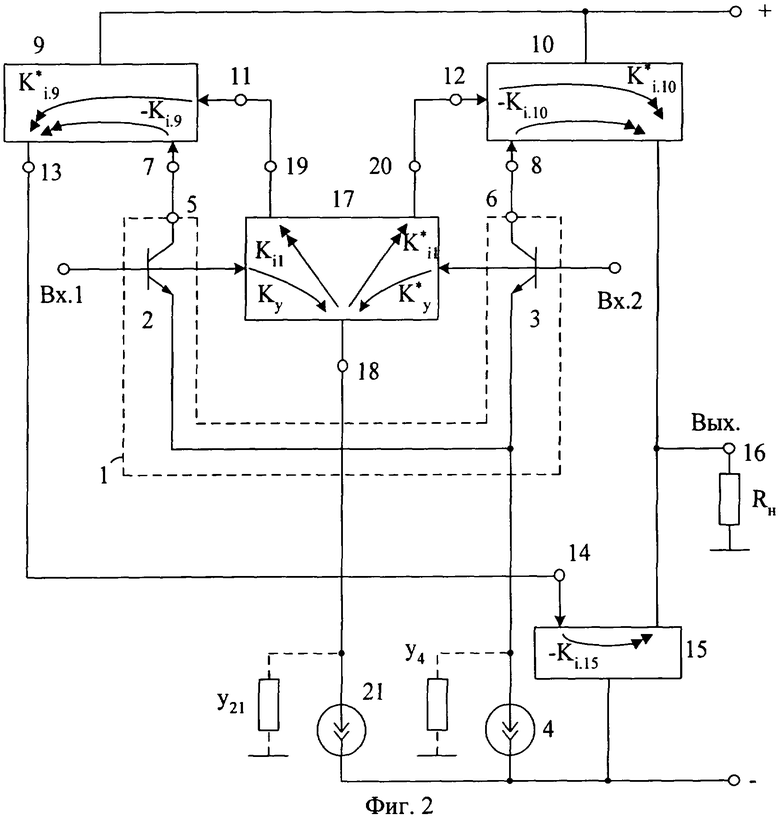

Схема усилителя-прототипа представлена на фиг.1. На фиг.2 показан заявляемый ДУ в соответствии с п.1-п.2 формулы изобретения. На фиг.3 представлен частный вариант построения каскада выделения входного синфазного сигнала 17 в соответствии с п.4 формулы изобретения, а ДУ, соответствующий п.4 и п.5, представлен на фиг.4. На фиг.5 показан вариант построения каскада 17 в соответствии с п.6 формулы изобретения. Эта схема используется в схеме ДУ фиг.6, которая соответствует п.3 и п.6 формулы изобретения. Схемы исследованных авторами устройств в среде компьютерного моделирования PSpice представлены на фиг.7 (прототип), фиг.8 (заявляемый ДУ), а на фиг.9 изображены результаты их компьютерного моделирования - частотная зависимость коэффициента ослабления входных синфазных сигналов Кос.сф.

Дифференциальный усилитель фиг.2 содержит входной дифференциальный каскад 1 на транзисторах 2 и 3 с источником опорного тока 4 в их общей эмиттерной цепи, первый 5 и второй 6 противофазные токовые выходы которого соединены с инвертирующими токовыми входами 7 и 8 первого 9 и второго 10 токовых зеркал, имеющих также неинвертирующие токовые входы 11 и 12, причем токовый выход 13 первого токового зеркала 9 соединен со входом 14 третьего токового зеркала 15, а токовые выходы второго 10 и третьего 15 токовых зеркал связаны с выходом 16 дифференциального усилителя. В схему введен каскад выделения входного синфазного сигнала 17, имеющий потенциальный 18, а также первый 19 и второй 20 токовые выходы и дополнительный источник опорного тока 21, соединенный с его потенциальным выходом 18 каскада, причем первый токовый выход 19 каскада выделения входного синфазного сигнала 17 соединен с неинвертирующим токовым входом 11 первого токового зеркала 9, а второй токовый выход 20 каскада выделения входного синфазного сигнала 17 соединен с неинвертирующим токовым входом 12 второго токового зеркала 10.

Каскад выделения входного синфазного сигнала 17, представленный на фиг.3, содержит первый 22 и второй 23 дополнительные транзисторы, эмиттеры которых объединены друг с другом и соединены с его потенциальным выходом 18, причем коллектор первого дополнительного транзистора 22 является вторым токовым выходом 20 каскада выделения входного синфазного сигнала 17, а коллектор второго дополнительного транзистора 23 является первым токовым выходом 19 каскада выделения входного синфазного сигнала 17.

В дифференциальном усилителе фиг.4 (п.4, п.5) каскад выделения входного синфазного сигнала 17 содержит первый 22 и второй 23 дополнительные транзисторы, эмиттеры которых объединены друг с другом и соединены с его потенциальным выходом 18, причем коллектор первого дополнительного транзистора 22 является вторым токовым выходом 20 каскада выделения входного синфазного сигнала 17, а коллектор второго дополнительного транзистора 23 является первым токовым выходом 19 каскада выделения входного синфазного сигнала 17. Кроме этого, к инвертирующим токовым входам 7 и 8 первого 9 и второго 10 токовых зеркал подключены дополнительные токостабилизирующие двухполюсники 24 и 25.

На фиг.5 показан каскад выделения входного синфазного сигнала, реализованный на транзисторах 26-27.

В дифференциальном усилителе фиг.6 входы каскада выделения входного синфазного сигнала 17 соединены с источником опорного тока 4 в общей эмиттерной цепи входного дифференциального каскада 1. Кроме этого, данный каскад 17 содержит третий 26 и четвертый 27 дополнительные транзисторы (фиг.5), эмиттеры которых объединены друг с другом и соединены с его потенциальным выходом 18, а коллекторы являются его соответствующими токовыми выходами 19 и 20. В данной схеме токовые зеркала 9 и 10 реализованы на элементах 28-35. Для выравнивания статических потенциалов на источниках опорного тока 4 и 21 введен р-n переход 36.

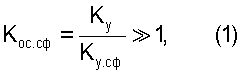

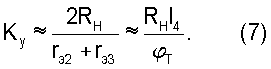

Рассмотрим работу заявляемого ДУ на примере анализа схемы фиг.4. Коэффициент ослабления входного синфазного сигнала ДУ фиг.4 определяется отношением

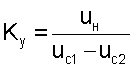

где  - коэффициент усиления дифференциального сигнала uвх;

- коэффициент усиления дифференциального сигнала uвх;

uн - выходное напряжение на нагрузке Rн, обусловленное uвх;

uвх=uс1-uc2 - входной дифференциальный сигнал ДУ;

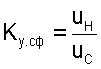

- коэффициент преобразования входного синфазного сигнала ДУ uc1=uc2=uc в выходное напряжение ДУ uн на нагрузке Rн.

- коэффициент преобразования входного синфазного сигнала ДУ uc1=uc2=uc в выходное напряжение ДУ uн на нагрузке Rн.

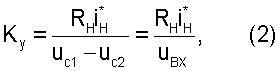

По определению

где  - ток в нагрузке ДУ, обусловленный дифференциальным сигналом.

- ток в нагрузке ДУ, обусловленный дифференциальным сигналом.

Для определения  положим, что uc2=0, a uc1=uвх. Тогда для дифференциального входного сигнала

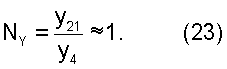

положим, что uc2=0, a uc1=uвх. Тогда для дифференциального входного сигнала

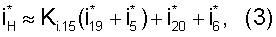

Ki.15≈1 - коэффициент передачи по току токового зеркала 15;

- токи выходов 19, 5, 20, 6 при uc2=0, uc1=uвх.

- токи выходов 19, 5, 20, 6 при uc2=0, uc1=uвх.

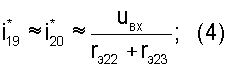

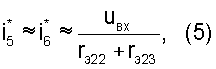

Причем

где rэi=ϕT/Iэi - дифференциальное сопротивление эмиттерного перехода i-го транзистора при статическом токе эмиттера Iэi;

ϕT≈25 мВ - температурный потенциал.

Поэтому коэффициент усиления по напряжению для дифференциального сигнала ДУ фиг.4

Если токи источников 2 (I2) и 4 (I4) одинаковы, то

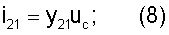

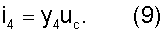

Рассмотрим далее факторы, влияющие на передачу синфазного сигнала с входа ДУ на его выход. Изменение uc1=uc2=uc (фиг.4) приводит к изменению токов через выходные проводимости у21 и у4 источников опорного тока 21 и 4:

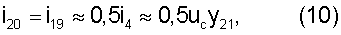

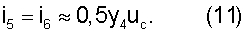

Это приводит к появлению приращений коллекторных токов транзисторов 22, 23 (i20, i19) и транзисторов 2 и 3 (i5, i6):

Приращение тока i19 поступает на вход 11 токового зеркала 9, а тока 20 - на вход 12 токового зеркала 10.

С другой стороны токи i5, i6 подаются на входы 7 и 8 этих же токовых зеркал.

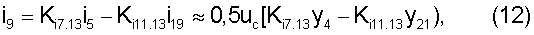

Поэтому выходные токи токовых зеркал 9 и 16

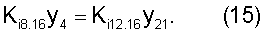

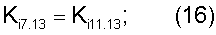

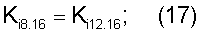

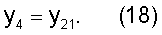

где Ki7.13≈1, Ki11.13≈1, Ki8.16≈1, Ki12.16≈1 - коэффициенты передачи по току между соответствующими входами и выходами токовых зеркал 9 и 10 соответственно.

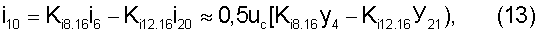

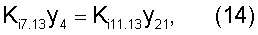

Из (12)-(13) следует, что токи i9 и i10 могут иметь нулевые значения, если

В частном случае для этого необходимо, чтобы

Учитывая, что токовые зеркала 9 и 10 идентичны, условия (16)÷(18) легко выполняются в практических схемах.

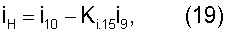

Если допустить, что из-за неточного выполнения условий (16)÷(18) i9≠0 и i10≠0, то необходимо заметить, что в токовом зеркале 15 происходит второе «вычитание» паразитных токов i9 и i10, обусловленных синфазным сигналом:

где Кi.15≈1

Это повышает общее ослабление синфазных сигналов.

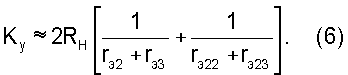

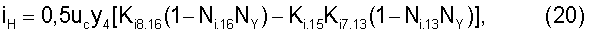

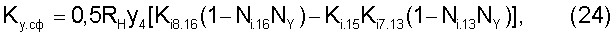

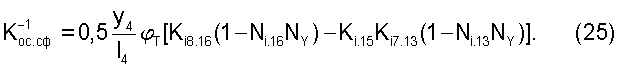

Для расчета Кос.сф, подставляя (12) и (13) в (19), находим

где

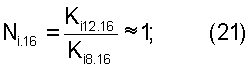

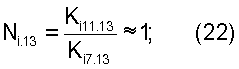

Параметры Ni.16, Ni.13, NY учитывают неидентичность коэффициентов передачи по току токовых зеркал 9 и 10, а также отличие друг от друга проводимостей у21 и у4.

Так как токовые зеркала 9 и 10 одинаковы, а схемотехника источников тока 21 и 4 также идентична, то легко обеспечиваются условия Ni.16=1, Ni.13=1, NY=1.

Численные значения коэффициента передачи синфазного сигнала заявляемого ДУ Ку.сф и его Кос.сф могут быть определены по формулам:

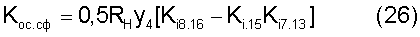

Анализ уравнения (25) показывает, что при Ni.16=1, Ni.13=1, NY=1 за счет «двойного» вычитания составляющих ошибки iн (19), обусловленной синфазным сигналом на входах ДУ, общее ослабление его синфазных сигналов повышается. В усилителе-прототипе этот эффект отсутствует. Поэтому передача синфазного сигнала на выход ДУ-прототипа более значительна

и, как следствие, Кос.сф принимает на один-два порядка меньшее значение.

Результаты компьютерного моделирования подтверждают данный теоретический вывод - заявляемый ДУ в сравнении с прототипом имеет на 39 дБ (≈100 раз) лучший коэффициент ослабления входных синфазных сигналов. Кроме этого, его дифференциальный коэффициент усиления не менее чем в 2 раза выше, чем у ДУ-прототипа.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №4783602.

2. Патент США №4176323.

3. Патент США №5371476.

4. Патент США RE 30.587.

5. Патент США №4241315.

6. Патент США №4267519.

7. Патент США №4361815.

8. Патент США №3439542.

9. Патент США №5880639.

10. Авт.св. СССР №361605.

11. Патент ФРГ №2551068.

12. Патент ФРГ №2620999.

13. М.Херпи. Аналоговые интегральные схемы / М.Херпи. - М.: Радио и связь, 1983. - С.185, рис.5.65.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ СИНФАЗНОГО СИГНАЛА | 2005 |

|

RU2292638C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2006 |

|

RU2319288C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ СИНФАЗНОГО СИГНАЛА | 2006 |

|

RU2319287C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ СИНФАЗНОГО СИГНАЛА | 2005 |

|

RU2292634C1 |

| ДВУХТАКТНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319289C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ СИНФАЗНОГО СИГНАЛА | 2007 |

|

RU2332782C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2011 |

|

RU2458455C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2005 |

|

RU2293433C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2011 |

|

RU2444117C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2346388C1 |

Изобретение относится к радиотехнике и связи для усиления широкополосных аналоговых сигналов и может быть использовано в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ) и компараторах, работающих с двумя сигналами, имеющими синфазную составляющую). Техническим результат заключается в повышении коэффициента ослабления входных синфазных сигналов. Дифференциальный усилитель (ДУ) содержит входной дифференциальный каскад (1) на транзисторах (2) и (3) с источником опорного тока (ИОТ) (4) в их общей эмиттерной цепи, противофазные токовые выходы (5) и (6) которого соединены с инвертирующими токовыми входами (7) и (8) первого (9) и второго (10) токовых зеркал (ТЗ), имеющих также неинвертирующие токовые входы (11) и (12), причем токовый выход (13) первого ТЗ (9) соединен со входом (14) третьего ТЗ (15), а токовые выходы второго (10) и третьего (15) ТЗ связаны с выходом (16) ДУ. Введен каскад выделения входного синфазного сигнала (17), имеющий потенциальный (18), а также первый (19) и второй (20) токовые выходы и дополнительный ИОТ (21), соединенный с его потенциальным выходом (18), причем первый токовый выход (19) каскада (17) соединен с неинвертирующим токовым входом (11) первого ТЗ (9), а второй токовый выход (20) каскада (17) соединен с неинвертирующим токовым входом (12) второго ТЗ (10). 5 з.п. ф-лы, 9 ил.

| US 3921090, 18.11.1975 | |||

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 0 |

|

SU361605A1 |

| US 4783602, 08.11.1988 | |||

| US4361815.30.11.1982 | |||

| DE 3043768 A1, 03.06.1982. | |||

Авторы

Даты

2008-02-20—Публикация

2006-06-19—Подача