Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, прецизионных решающих и операционных усилителях с малыми: значениями э.д.с. смещения нуля).

В современной радиоэлектронной аппаратуре находят применение дифференциальные усилители (ДУ) с существенными различными параметрами. Особое место занимают ОУ на базе «перегнутых» каскодов [1-15], получившие широкое применение в микроэлектронных изделиях. Предполагаемое изобретение относится к данному типу устройств.

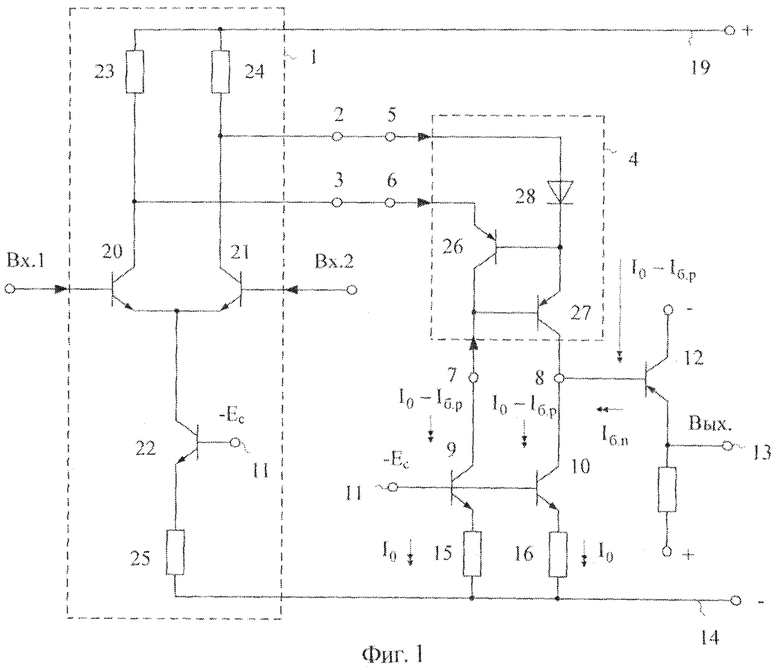

Наиболее близким по технической сущности к заявляемому ДУ является классическая схема фиг.1, представленная в патенте США фирмы Motorola № 5.734.296 fig.5, которая также присутствует в других патентах [2-15].

Существенный недостаток известного ДУ фиг.1 состоит в том, что он имеет повышенное значение систематической составляющей напряжения смещения нуля Uсм.

Основная задача предлагаемого изобретения состоит в уменьшении напряжения смещения нуля Uсм, а также его дрейфа в условиях температурных и радиационных воздействий.

Поставленная задача достигается тем, что в каскодном дифференциальном усилителе фиг.1, содержащем входной дифференциальнмй каскад 1 с первым 2 и вторым 3 токовыми выходами, токовое зеркало 4, имеющее первый 5 и второй 6 эмиттерный входы, базовый 7 ход и токовый выход 8, первый 5 эмиттерный вход токового зеркала 4 подключен к первому 2 токовому выходу входного дифференциального каскада 1, а второй 6 эмиттерный вход токового зеркала 4 соединен со вторым 3 токовым выходом входного дифференциального каскада 1, базовый 7 вход токового зеркала 4 подключен к коллектору первого 9 вспомогательного транзистора, токовый выход 8 токового зеркала 4 подключен к коллектору второго 10 вспомогательного транзистора, базы первого 9 и второго 10 вспомогательных транзисторов связаны друг с другом и подключены к источнику напряжения смещения 11, база входного транзистора выходного эмиттерного повторителя 12 подключена к коллектору второго 10 вспомогательного транзистора, а его эмиттер связан с выходом устройства 13, причем эмиттеры первого 9 и второго 10 вспомогательных транзисторов подключены к первому 14 источнику питания через первый 15, второй 16 вспомогательные резисторы, предусмотрены новые связи - в схему введен дополнительный транзистор 17, коллектор которого связан с выходом 13 устройства, база - соединена с эмиттером первого 9 вспомогательного транзистора, эмиттер - через первый 18 дополнительный резистор связан с первым 14 источником питания, а коллектор входного транзистора выходного эмиттерного повторителя 12 подключен ко второму 9 источнику питания, причем все вспомогательные 9, 10 и дополнительный 17 транзисторы имеют один тип проводимости.

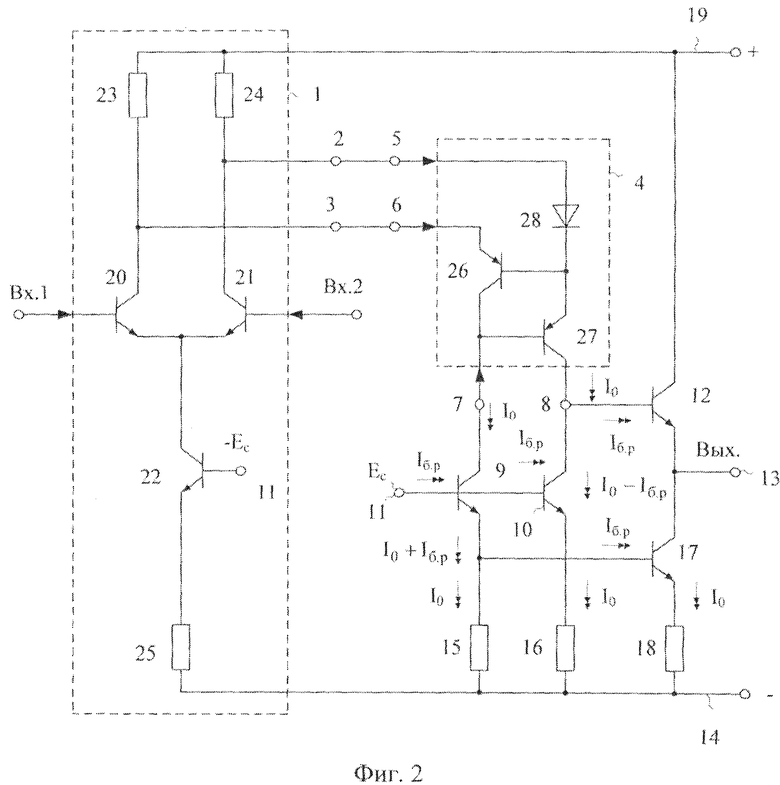

Схема усилителя-прототипа показана на фиг.1. На фиг.2 представлена схема заявляемого устройства в соответствии с п.1, п.2 и п.3 формулы изобретения.

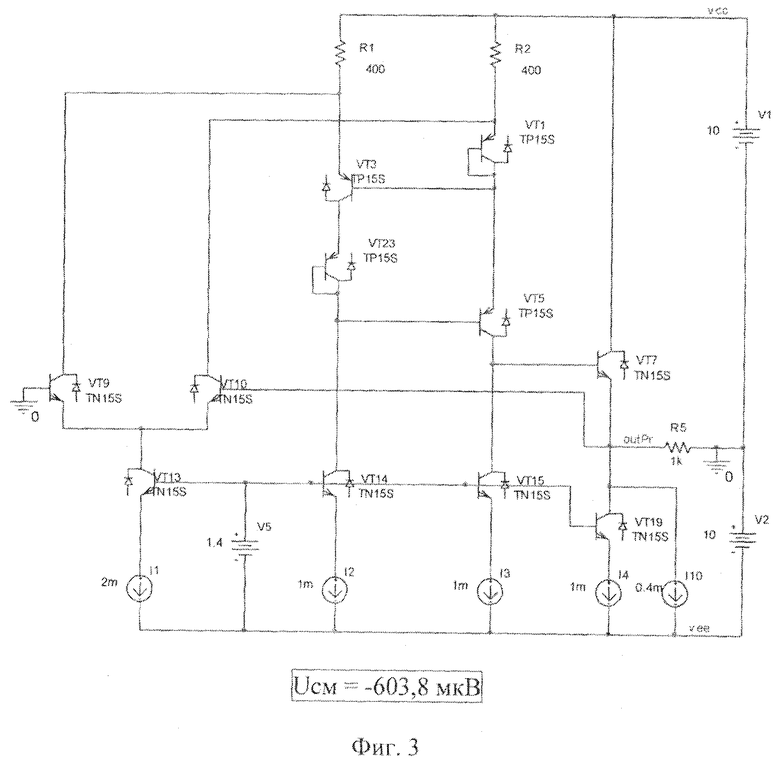

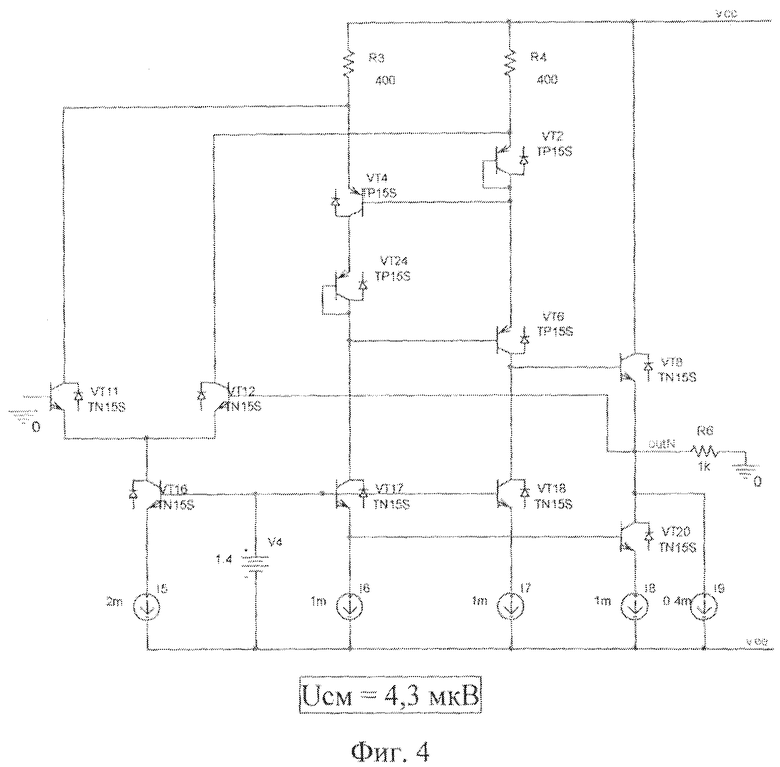

На фиг.3 и фиг.4 приведены схемы ДУ - аналога (фиг.3) и заявляемого ДУ (фиг.4) в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

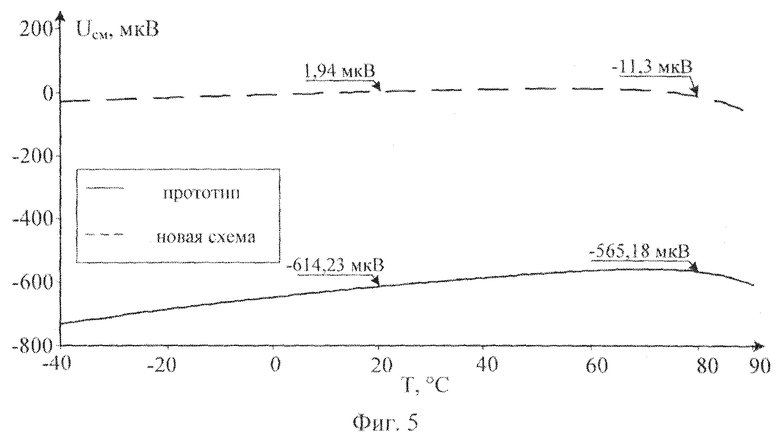

На фиг.5 показаны результаты компьютерного моделирования схем фиг.3 и фиг.4 - зависимость напряжения смещения нуля Uсм от температуры.

Каскодный дифференциальный усилитель с повышенной стабильностью нулевого уровня фиг.2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 токовыми выходами, токовое зеркало 4, имеющее первый 5 и второй 6 эмиттерный входы, базовый 7 вход и токовый выход 8, первый 5 эмиттерный вход токового зеркала 4 подключен к первому 2 токовому выходу входного дифференциального каскада 1, а второй 6 эмиттерный вход токового зеркала 4 соединен со вторым 3 токовым выходом входного дифференциального каскада 1, базовый 7 вход токового зеркала 4 подключен к коллектору первого 9 вспомогательного транзистора, токовый выход 8 токового зеркала 4 подключен к коллектору второго 10 вспомогательного транзистора, базы первого 9 и второго 10 вспомогательных транзисторов связаны друг с другом и подключены к источнику напряжения смещения 11, база входного транзистора выходного эмиттерного повторителя 12 подключена к коллектору второго 10 вспомогательного транзистора, а его эмиттер связан с выходом устройства 13, причем эмиттеры первого 9 и второго 10 вспомогательных транзисторов подключены к первому 14 источнику питания через первый 15, второй 16 вспомогательные резисторы. В схему введен дополнительный транзистор 17, коллектор которого связан с выходом 13 устройства, база - соединена с эмиттером первого 9 вспомогательного транзистора, эмиттер - через первый 18 дополнительный резистор связан с первым 14 источником питания, а коллектор входного транзистора выходного эмиттерного повторителя 12 подключен ко второму 19 источнику питания, причем все вспомогательные 9, 10 и дополнительный 17 транзисторы имеют один тип проводимости.

Кроме этого на фиг.2 в соответствии с п.2 формулы изобретения входной дифференциальный каскад 1 содержит первый 20 и второй 21 входные транзисторы, эмиттеры которых соединены с транзистором 22 источника опорного тока, коллектор первого 20 входного транзистора входного дифференциального каскада 1 соединен со вторым 3 токовым выходом входного дифференциального каскада 1 и соединен со вторым 19 источником питания через первый 23 коллекторный резистор, коллектор второго 21 входного транзистора входного дифференциального каскада 1 соединен с первым 2 токовым выходом входного дифференциального каскада 1 и связан со вторым 19 источником питания через второй 24 коллекторный резистор, эмиттер транзистора 22 источника опорного тока соединен с первым 14 источником питания через эмиттерный резистор 25, а база транзистора 22 источника опорного тока подключена к источнику напряжения смещения 11.

На фиг.2 в соответствии с п.3 формулы изобретения токовое зеркало 4 содержит первый 26 и второй 27 транзисторы, эмиттер первого 26 транзистора токового зеркала 4 соединен со вторым 6 эмиттерным входом токового зеркала 4, а коллектор - с базовым 7 входом токового зеркала 4, эмиттер второго 27 транзистора токового зеркала 4 через дополнительный p-n-переход 28 подключен к первому 5 эмиттерному входу токового зеркала 4, а коллектор соединен с токовым выходом 8 токового зеркала 4, база первого 26 транзистора токового зеркала 4 подключена к эмиттеру второго 27 транзистора токового зеркала 4, база второго 27 транзистора токового зеркала 4 подключена к коллектору первого 26 транзистора токового зеркала 4.

Рассмотрим работу заявляемого устройства фиг.2.

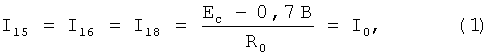

Статический режим по току транзисторов 9, 10 и 14, 17, 20, 21, а также элементов токового зеркала 4 устанавливается резисторами 15, 16, 18, 25 и зависит от величины напряжения источника смещения 11 (Ес). Будем считать, что за счет выбора номиналов этих элементов токи через них одинаковы:

где R0=R15=R16=R18.

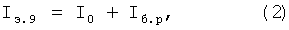

Тогда эмиттерный Iэ и коллекторный Iк токи транзисторов 9 и 10:

где Iб.р. - температурно-зависимый ток базы n-p-n транзистора при токе эмиттера I0.

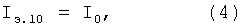

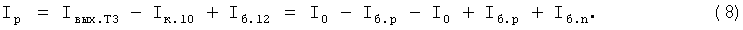

Коллекторный ток транзистора 9 поступает на базовый вход 7 токового зеркала 4. Поэтому выходной ток Iвых.Т3 токового зеркала 4, повторяющий его входной ток (Iвых.Т3):

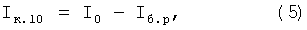

В результате в цепи базы транзистора 12 происходит взаимная компенсация трех токов Iвых.Т3, Iб.12 и Iк.10, что является необходимым условием для уменьшения напряжения смещения нуля ДУ:

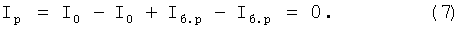

В усилителе-прототипе фиг.1 в узле 8 при его коротком замыкании на эквивалентную общую шину образуется разностный ток Iр:

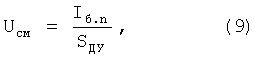

Для его компенсации необходимо на входы ДУ Вх.1, Вх.2 подать Uсм, равное:

где SДУ - крутизна преобразования входного напряжения uвх ДУ в выходной ток узла 8.

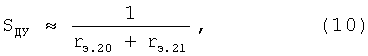

Для ДУ фиг.1:

где rэ.20, rэ.21 - сопротивления эмиттерных переходов транзисторов входного дифференциального каскада 1.

Следовательно, для ДУ-прототипа:

В предлагаемом ДУ разностный ток Iр равен нулю. Поэтому систематическая составляющая его напряжения смещения нуля (Ucм) значительно меньше (4,3 мкВ, фиг, 4, фиг.5), чем в известном устройстве (603,8 мкВ, фиг.3, фиг.5).

Данные выводы подтверждаются результатами компьютерного моделирования сравниваемых схем (фиг.5).

Таким образом, заявляемое устройство обладает существенными преимуществами в сравнении с прототипом по величине статической ошибки усиления сигналов постоянного тока.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США № 5.734.296, fig.5.

2. Патент США № 4.293.824.

3. Патент RU № 2331974.

4. Патент США № 4.600.893.

5. Патент США № 5.952.882, fig.2.

6. Патент RU № 2331965.

7. Патент США № 6.456.162, fig.1.

8. Патент США № 6.501,333.

9. Патент США № 6.542.030.

10. Патент США № 4.293.824.

11. Патент США № 6.717.466.

12. Патент США № 5.420.540.

13. Патент США № 5.523.718.

14. Патент США № 4.644.295.

15. Патент Англии № 2.035.003, кл.Н3Т.

| название | год | авторы | номер документа |

|---|---|---|---|

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2354041C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2390918C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2401507C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2411636C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2411638C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2416145C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402152C1 |

| ДВУХКАСКАДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2015 |

|

RU2621289C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2411635C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2411640C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, прецизионных решающих и операционных усилителях с малыми значениями э.д.с. смещения нуля). Технический результат: уменьшение напряжения смещения нуля Uсм, а также его дрейфа в условиях температурных и радиационных воздействий. Каскодный дифференциальный усилитель содержит входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, токовое зеркало (4), имеющее первый (5) и второй (6) эмиттерный входы, базовый (7) вход и токовый выход (8), первый (5) эмиттерный вход токового зеркала (4) подключен к первому (2) токовому выходу входного дифференциального каскада (1), а второй (6) эмиттерный вход токового зеркала (4) соединен со вторым (3) токовым выходом входного дифференциального каскада (1), базовый (7) вход токового зеркала (4) подключен к коллектору первого (9) вспомогательного транзистора, токовый выход (8) токового зеркала (4) подключен к коллектору второго (10) вспомогательного транзистора, базы первого (9) и второго (10) вспомогательных транзисторов связаны друг с другом и подключены к источнику напряжения смещения (11), база входного транзистора выходного эмиттерного повторителя (12) подключена к коллектору второго (10) вспомогательного транзистора, а его эмиттер связан с выходом устройства (13), причем эмиттеры первого (9) и второго (10) вспомогательных транзисторов подключены к первому (14) источнику питания через первый (15), второй (16) вспомогательные резисторы. В схему введен дополнительный транзистор (17), коллектор которого связан с выходом (13) устройства, база - соединена с эмиттером первого (9) вспомогательного транзистора, эмиттер - через первый 18 дополнительный резистор связан с первым (14) источником питания, а коллектор входного транзистора выходного эмиттерного повторителя (12) подключен ко второму (19) источнику питания, причем все вспомогательные (9), (10) и дополнительный (17) транзисторы имеют один тип проводимости. 2 з.п. ф-лы, 5 ил.

1. Каскодный дифференциальный усилитель с повышенной стабильностью нулевого уровня, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) токовыми выходами, токовое зеркало (4), имеющее первый (5) и второй (6) эмиттерный входы, базовый (7) вход и токовый выход (8), первый (5) эмиттерный вход токового зеркала (4) подключен к первому (2) токовому выходу входного дифференциального каскада (1), а второй (6) эмиттерный вход токового зеркала (4) соединен со вторым (3) токовым выходом входного дифференциального каскада (1), базовый (7) вход токового зеркала (4) подключен к коллектору первого (9) вспомогательного транзистора, токовый выход (8) токового зеркала (4) подключен к коллектору второго (10) вспомогательного транзистора, базы первого (9) и второго (10) вспомогательных транзисторов связанны друг с другом и подключены к источнику напряжения смещения (11), база входного транзистора выходного эмиттерного повторителя (12) подключена к коллектору второго (10) вспомогательного транзистора, а его эмиттер связан с выходом устройства (13), причем эмиттеры первого (9) и второго (10) вспомогательных транзисторов подключены к первому (14) источнику питания через первый (15), второй (16) вспомогательные резисторы, отличающийся тем, что в схему введен дополнительный транзистор (17), коллектор которого связан с выходом (13) устройства, база соединена с эмиттером первого (9) вспомогательного транзистора, эмиттер через первый (18) дополнительный резистор связан с первым (14) источником питания, а коллектор входного транзистора выходного эмиттерного повторителя (12) подключен ко второму (19) источнику питания, причем все вспомогательные (9), (10) и дополнительный (17) транзисторы имеют один тип проводимости.

2. Устройство по п.1, отличающееся тем, что входной дифференциальный каскад (1) содержит первый (20) и второй (21) входные транзисторы, эмиттеры которых соединены с транзистором (22) источника опорного тока, коллектор первого (20) входного транзистора входного дифференциального каскада (1) соединен со вторым (3) токовым выходом входного дифференциального каскада (1) и соединен со вторым (19) источником питания через первый (23) коллекторный резистор, коллектор второго (21) входного транзистора входного дифференциального каскада (1) соединен с первым (2) токовым выходом входного дифференциального каскада (1) и связан со вторым (19) источником питания через второй (24) коллекторный резистор, эмиттер транзистора (22) источника опорного тока соединен с первым (14) источником питания через эмиттерный резистор (25), а база транзистора (22) источника опорного тока подключена к источнику напряжения смещения (11).

3. Устройство по п.1, отличающееся тем, что токовое зеркало (4) содержит первый (26) и второй (27) транзисторы, эмиттер первого (26) транзистора токового зеркала (4) соединен со вторым (6) эмиттерным входом токового зеркала (4), а коллектор - с базовым (7) входом токового зеркала (4), эмиттер второго (27) транзистора токового зеркала (4) через дополнительный p-n-переход (28) подключен к первому (5) эмиттерному входу токового зеркала (4), а коллектор соединен с токовым выходом (8) токового зеркала (4), база первого (26) транзистора токового зеркала (4) подключена к эмиттеру второго (27) транзистора токового зеркала (4), база второго (27) транзистора токового зеркала (4) подключена к коллектору первого (26) транзистора токового зеркала (4).

| US 5734296 A, 31.03.1998 | |||

| Операционный усилитель | 1984 |

|

SU1283946A1 |

| US 6483382 B1, 19.11.2002 | |||

| US 6144234 A, 07.11.2000. | |||

Авторы

Даты

2011-05-20—Публикация

2010-02-12—Подача