Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления высокочастотных аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в драйверах линий связи, операционных усилителях (ОУ), быстродействующих компараторах двух напряжений и т.п.).

Известны схемы широкополосных усилителей (ШУ), у которых входной сигнал подается в цепь эмиттеров входных транзисторов. Такие ШУ в сравнении с классическими параллельно-балансными каскадами, у которых сигнал поступает в цепь базы входных транзисторов, имеют ряд существенных преимуществ при усилении быстроизменяющихся и СВЧ-сигналов. Например, они оказываются лучше по полосе пропускания, которая достигает максимальных значений для схем с общей базой, а также по величине входного сопротивления, которое (для согласования с источником сигнала) может быть установлено на уровне небольших волновых сопротивлений линий связи (десятки Ом). Следует также заметить, что в таких ШУ отсутствует эффект Миллера (умножение емкости коллектор-база транзисторов), что также положительно сказывается на их полосе пропускания.

Среди известных усилителей с эмиттерным входом [1-60] особое место занимают схемы на основе p-n-p и n-p-n входных транзисторов, образующих двухтактную структуру и имеющих два входа и два выхода (патент США №6.529.078 (фирма Analog Devices), патент США 5.742.154 (фирма Maxim), патент США №5.734.294 (фирма Raytheon), патент США №5.557.220, фиг.8 (фирма Mitsubishi)).

Их основное достоинство - низковольтные токовые входы и «привязка» двух выходов к разным шинам питания, что упрощает построение многокаскадных аналоговых устройств. Однако, несмотря на наличие двух входов, такие усилители не являются полностью дифференциальными усилителями в классическом понимании этого термина. Действительно, в данных архитектурах выходное напряжение, например, на первом (втором) выходе зависит только от входного сигнала на первом (втором) входе. Кроме этого, в известных устройствах не всегда решается проблема обеспечения работоспособности при наличии у двух входных сигналов синфазной составляющей.

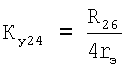

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте США №5.512.859 (фиг.3), содержащий первый 1 n-p-n и второй 2 p-n-p входные транзисторы, эмиттеры которых соединены с соответствующими первым 3 и вторым 4 токовыми входами дифференциального усилителя, первый 5 вспомогательный p-n-p транзистор, коллектор которого соединен с базой первого 1 n-p-n входного транзистора, второй 6 n-p-n вспомогательный транзистор, коллектор которого связан с базой второго 2 n-p-n входного транзистора, база первого 5 p-n-p вспомогательного транзистора соединена с первым 7 источником напряжения смещения, а эмиттер подключен к шине первого 8 источника питания через первый 9 вспомогательный двухполюсник, база второго 6 n-p-n вспомогательного транзистора соединена со вторым 10 источником напряжения смещения, а эмиттер подключен к шине второго 11 источника питания через второй 12 вспомогательный двухполюсник, причем коллекторы первого 5 вспомогательного p-n-p транзистора и второго 6 вспомогательного p-n-p транзистора соединены друг с другом по переменному току.

Существенный недостаток известного устройства состоит в том, что оно не обеспечивает передачу сигнала uвх.3 с первого 3 токового входа в коллекторную цепь второго 2 транзистора (при uвх.4=0). Кроме этого, сигнал uвx.4 на втором 4 токовом входе не влияет на ток коллектора транзистора 1. То есть известное устройство является псевдодифференциальным каскадом, что значительно сужает область его использования. Например, на базе известного усилителя невозможно построение преобразователя одного сигнала в два противофазных напряжения.

Основная цель предлагаемого изобретения состоит в повышении симметрии схемы по входам и, как следствие, обеспечении одинаковых величин коэффициентов передачи как от первого 3, так и от второго 4 входов к выходам, согласованным с разными шинами источников питания. По существу, авторами предлагается новый класс дифференциальных каскадов, сочетающих положительные свойства дифференциальных усилителей как с токовыми (низкоомными), так и с потенциальными (высокоомными) входами.

Поставленная цель достигается тем, что в дифференциальном усилителе фиг.1, содержащем первый 1 n-p-n и второй 2 p-n-p входные транзисторы, эмиттеры которых соединены с соответствующими первым 3 и вторым 4 токовыми входами дифференциального усилителя, первый 5 вспомогательный p-n-p транзистор, коллектор которого соединен с базой первого 1 n-p-n входного транзистора, второй 6 n-p-n вспомогательный транзистор, коллектор которого связан с базой второго 2 n-p-n входного транзистора, база первого 5 p-n-p вспомогательного транзистора соединена с первым 7 источником напряжения смещения, а эмиттер подключен к шине первого 8 источника питания чрез первый 9 вспомогательный двухполюсник, база второго 6 n-p-n вспомогательного транзистора соединена со вторым 10 источником напряжения смещения, а эмиттер подключен к шине второго 11 источника питания через второй 12 вспомогательный двухполюсник, причем коллекторы первого 5 вспомогательного p-n-p транзистора и второго 6 вспомогательного p-n-p транзистора соединены друг с другом по переменному току, предусмотрены новые элементы и связи - коллектор первого 1 n-p-n входного транзистора соединен с эмиттером первого 5 p-n-p вспомогательного транзистора, а коллектор второго 2 p-n-p входного транзистора соединен с эмиттером второго 6 вспомогательного n-p-n транзистора.

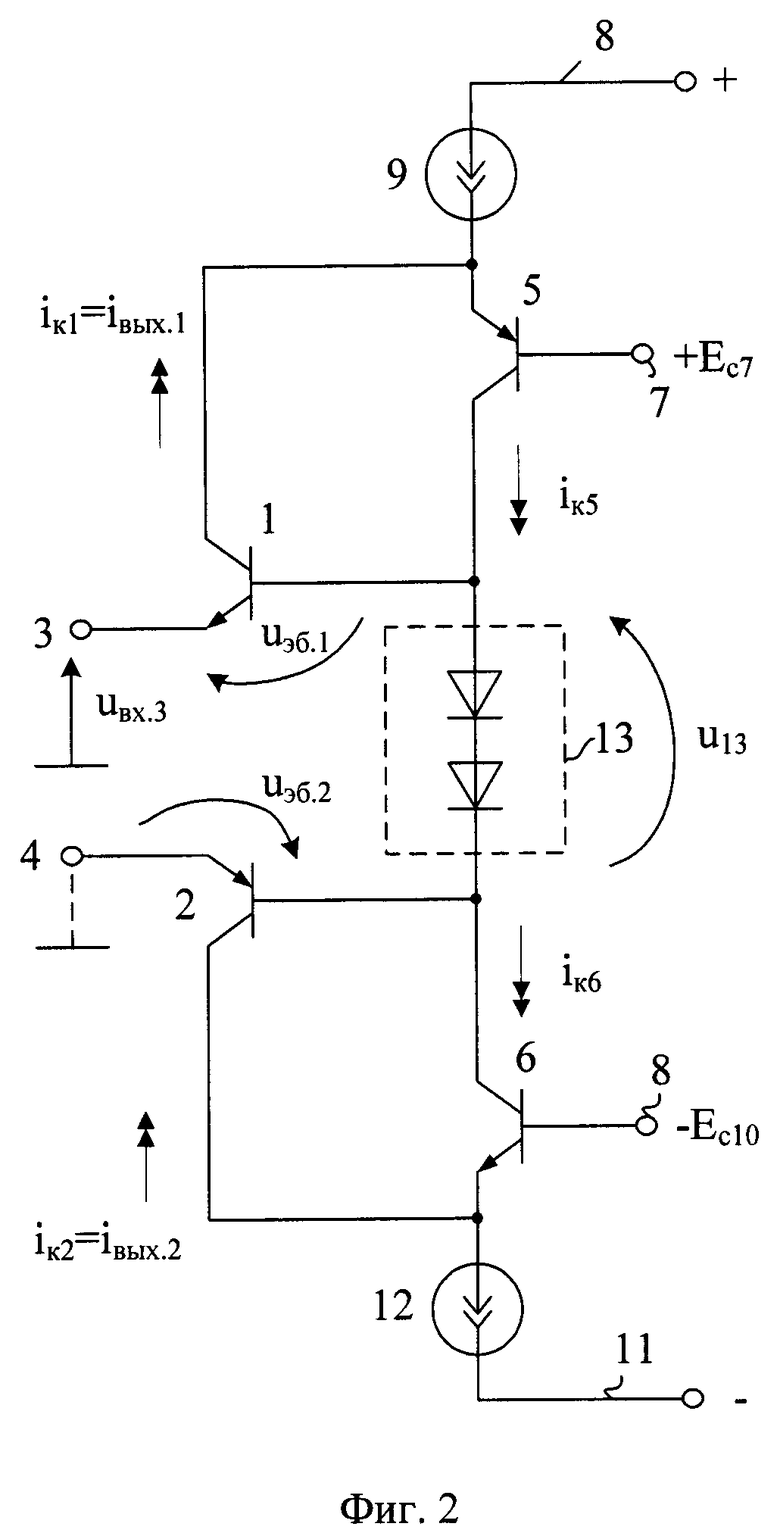

Схема заявляемого устройства, соответствующая п.1 и п.2 формулы изобретения, приведена на фиг.2.

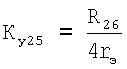

На фиг.3 показан заявляемый ДУ в соответствии с п.3, п.4, п.2 формулы изобретения.

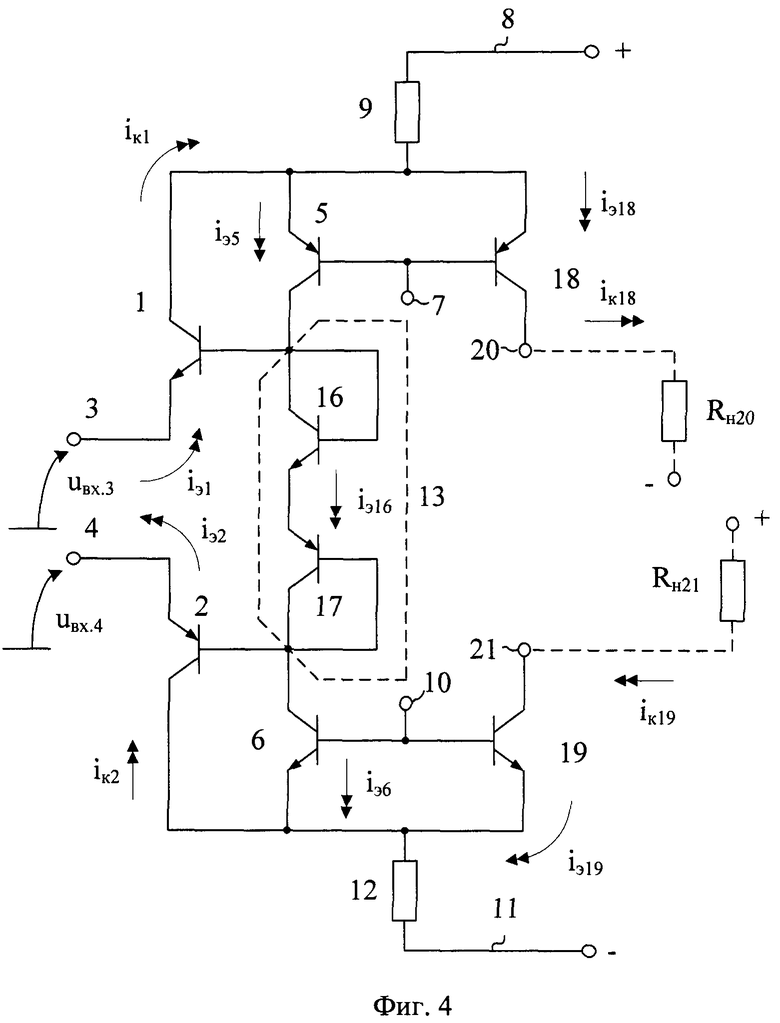

На фиг.4 представлен заявляемый ДУ в соответствии с п.5 и п.2 формулы изобретения.

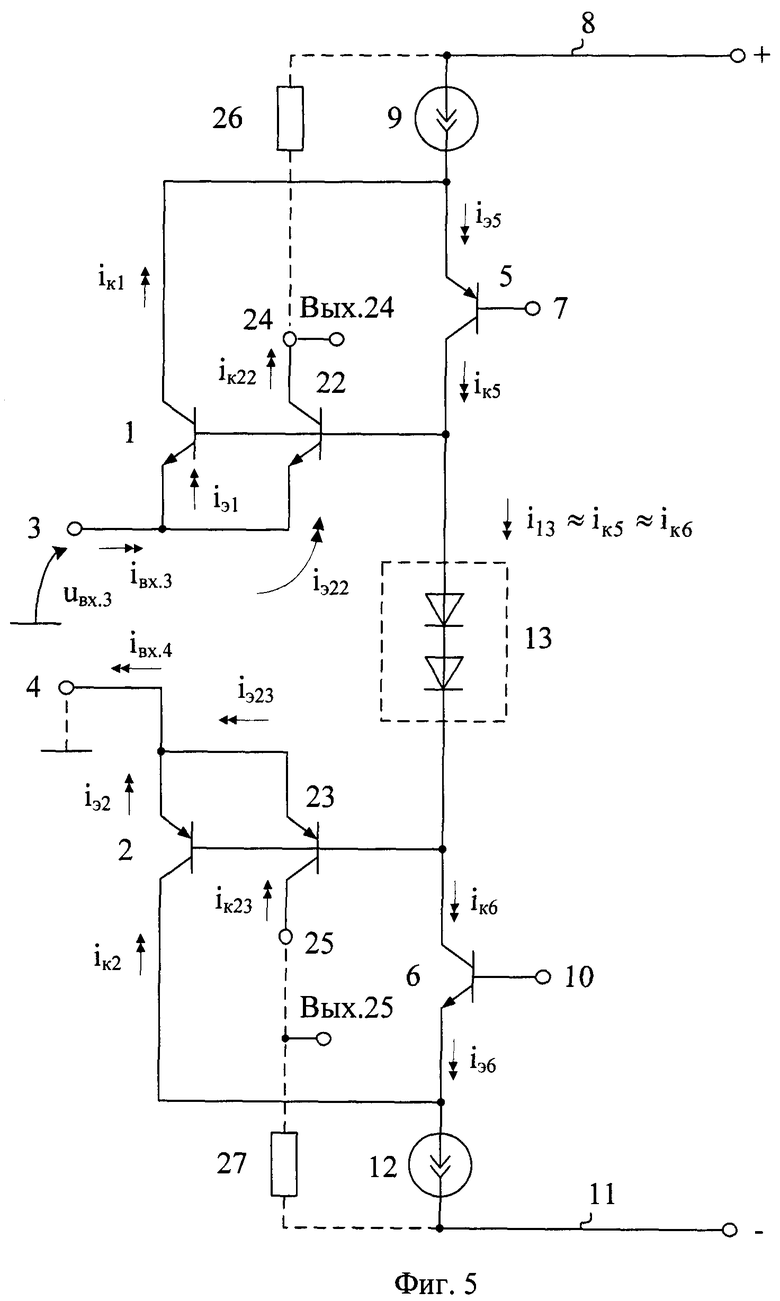

На фиг.5 представлен заявляемый ДУ в соответствии с п.6, п.7 и п.2 формулы изобретения.

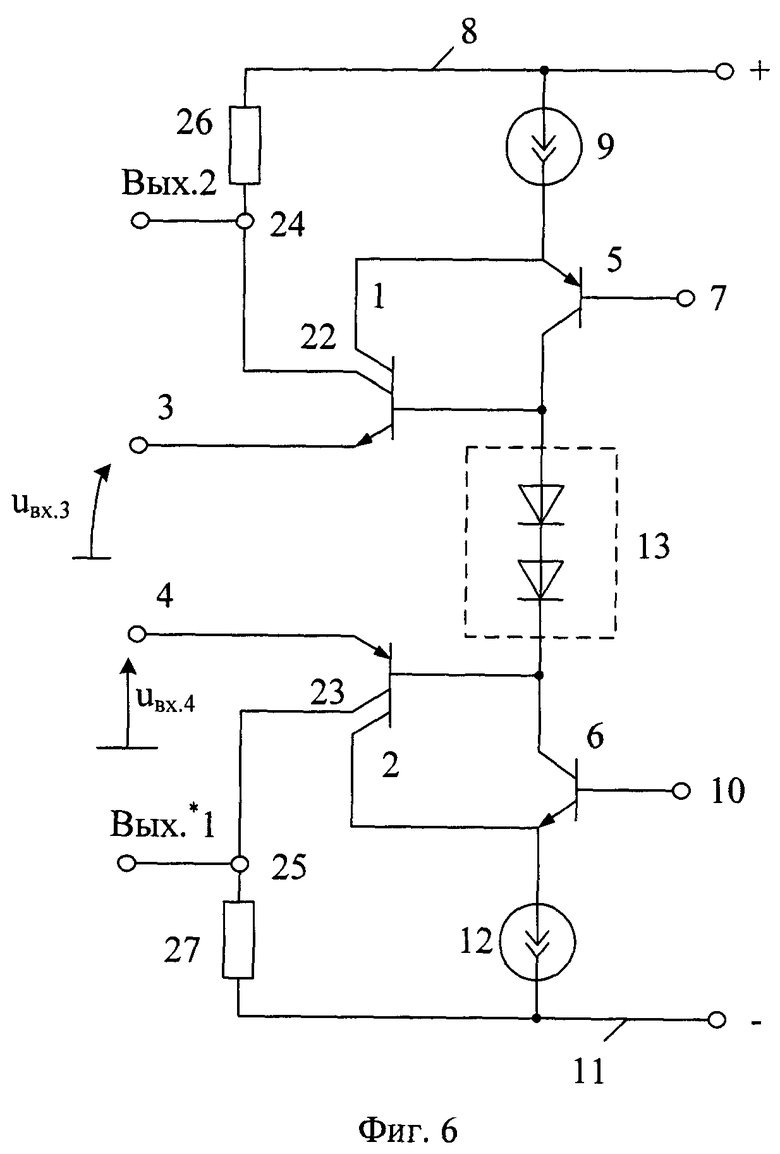

На фиг.6 показана схема, соответствующая фиг.5 (п.6, п.7 и п.2 формулы изобретения) в другом графическом обозначении.

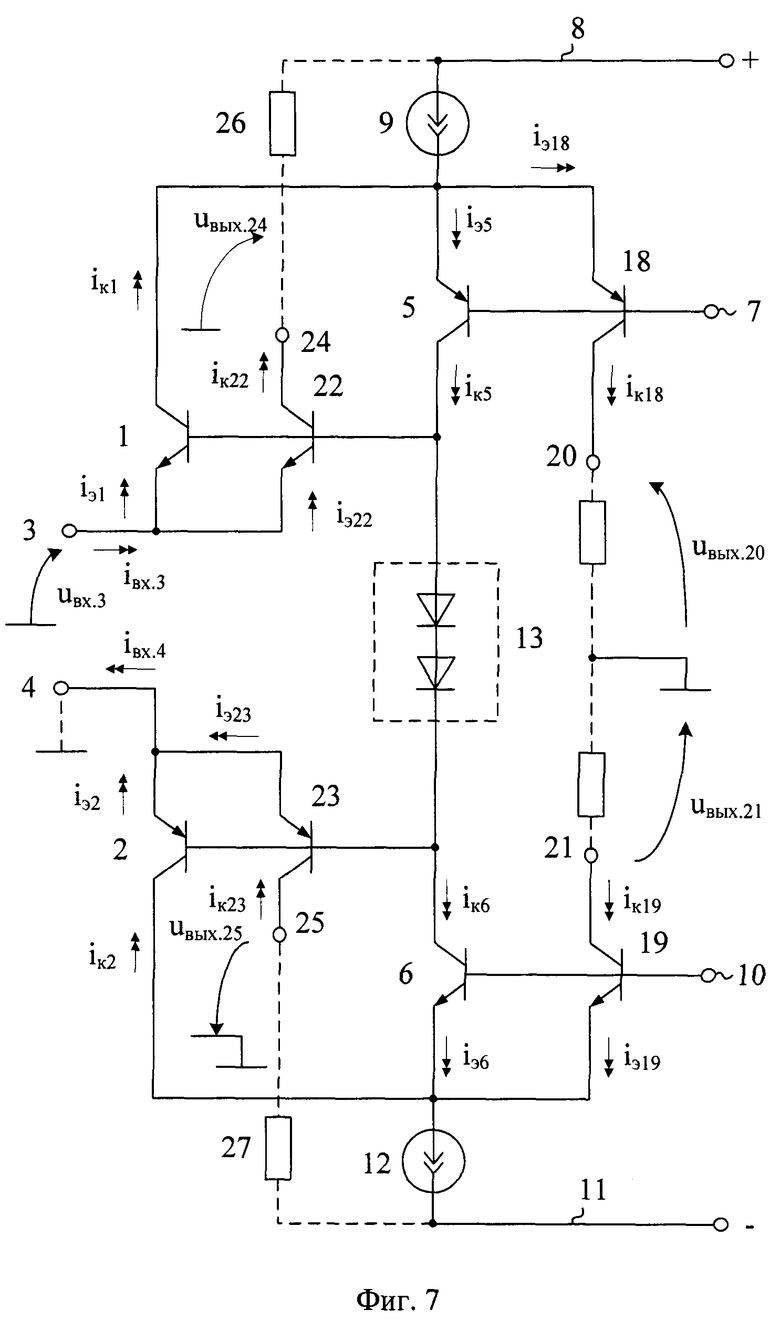

На фиг.7 показана схема, объединяющая в одной фигуре фиг.4 и фиг.5.

На фиг.8 представлен ДУ по п.8 и п.2 формулы изобретения.

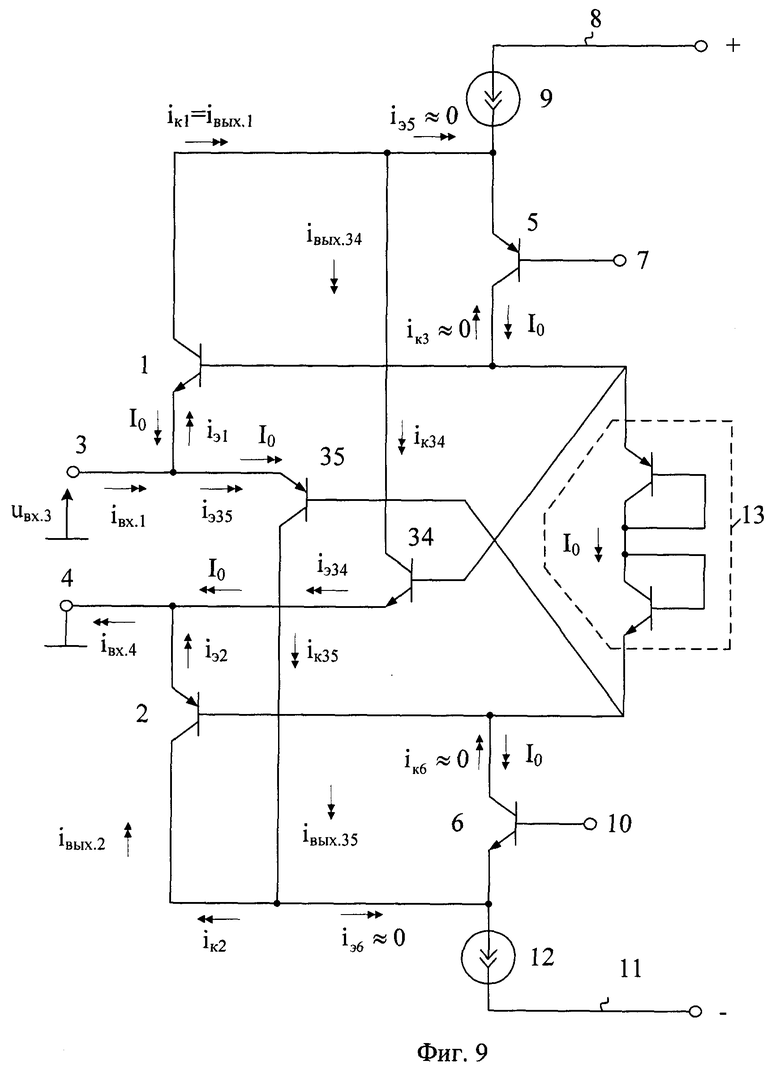

На фиг.9 представлен ДУ по п.9 и п.2 формулы изобретения.

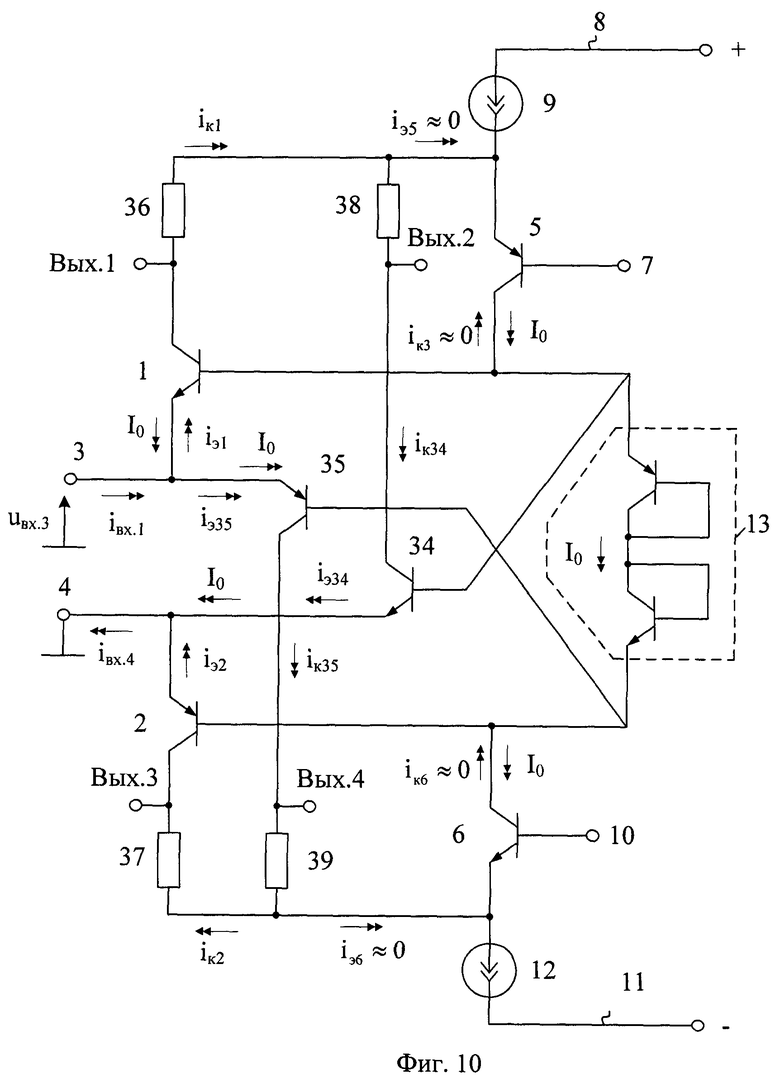

На фиг.10 изображена схема ДУ по п.10 и п.2 формулы изобретения.

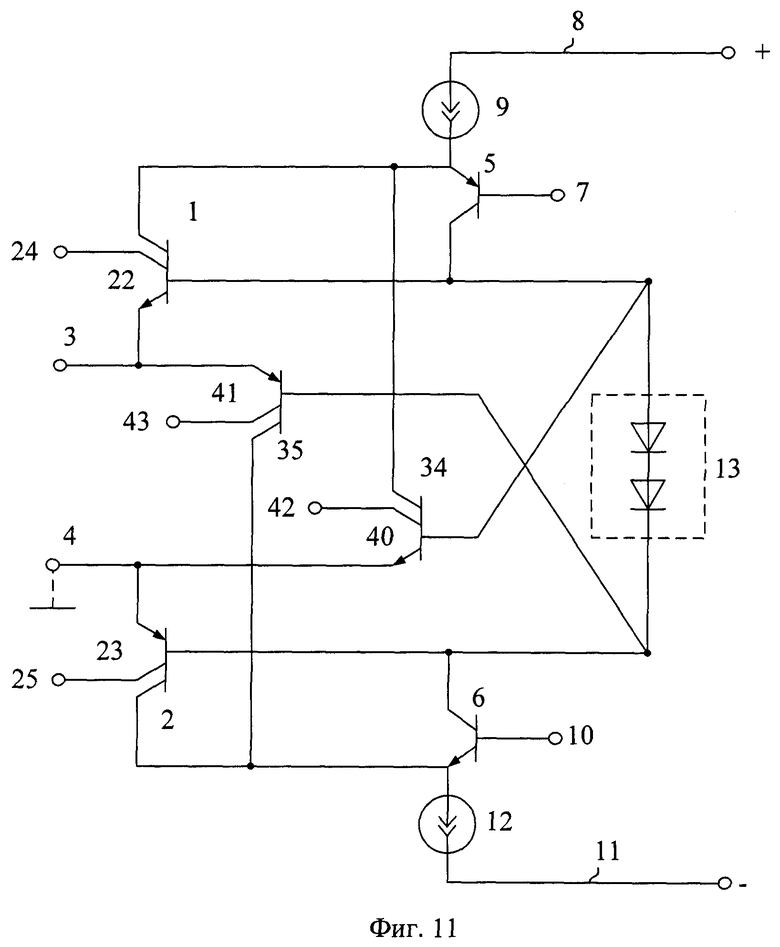

На фиг.11 представлен ДУ по по п.11 и п.2 формулы изобретения.

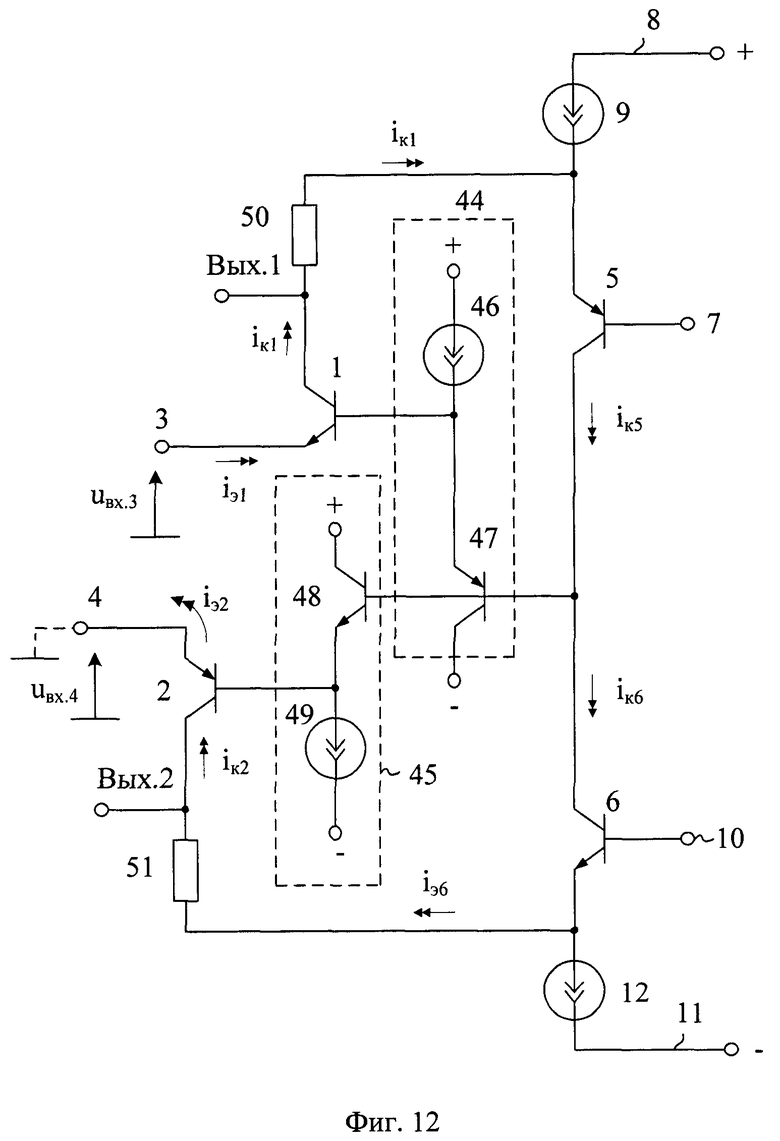

На фиг.12 представлен ДУ по п.12 формулы изобретения

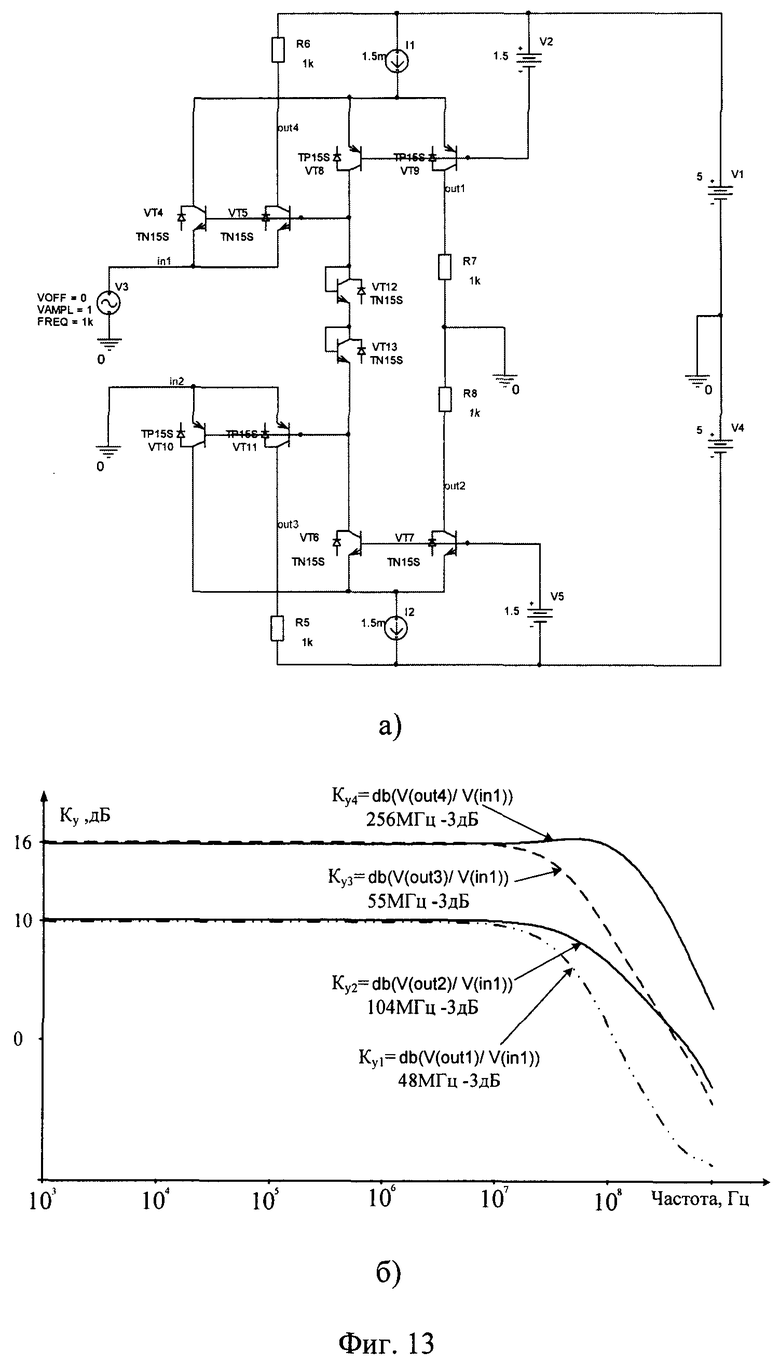

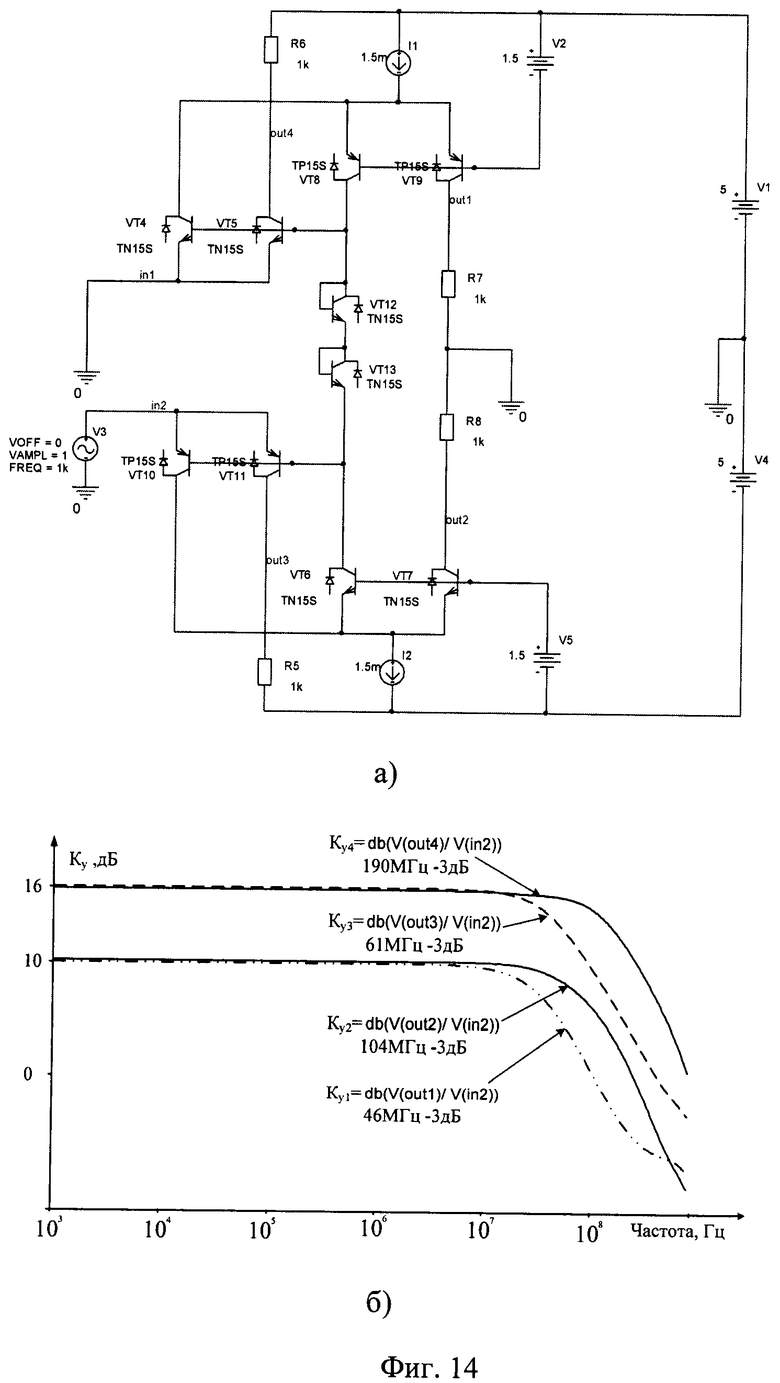

На фиг.13а приведена схема фиг.7 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар», а на фиг.13б показаны графики частотной зависимости ее четырех малосигнальных коэффициентов усиления со входа 3 (in1) к четырем выходам, «привязанным» к разным шинам питания.

Аналогично, на чертеже фиг.14 приведены результаты моделирования схемы фиг.13 для случая, когда входной сигнал подается только на второй 4 (in2) токовый вход.

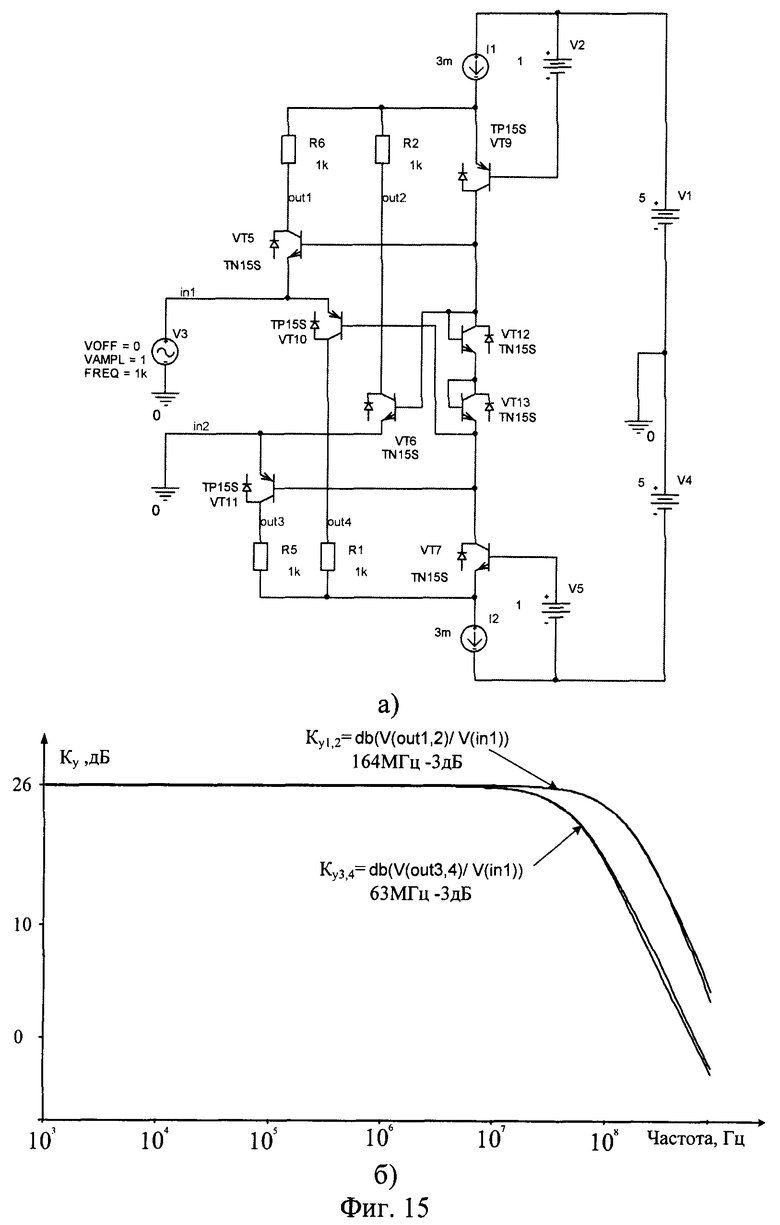

На фиг.15а представлена схема фиг.10 в среде PSpice, а на фиг.15б - малосигнальные амплитудно-частотные характеристики ее двух коэффициентов усиления со входа 3 (in1) к дифференциальным выходам.

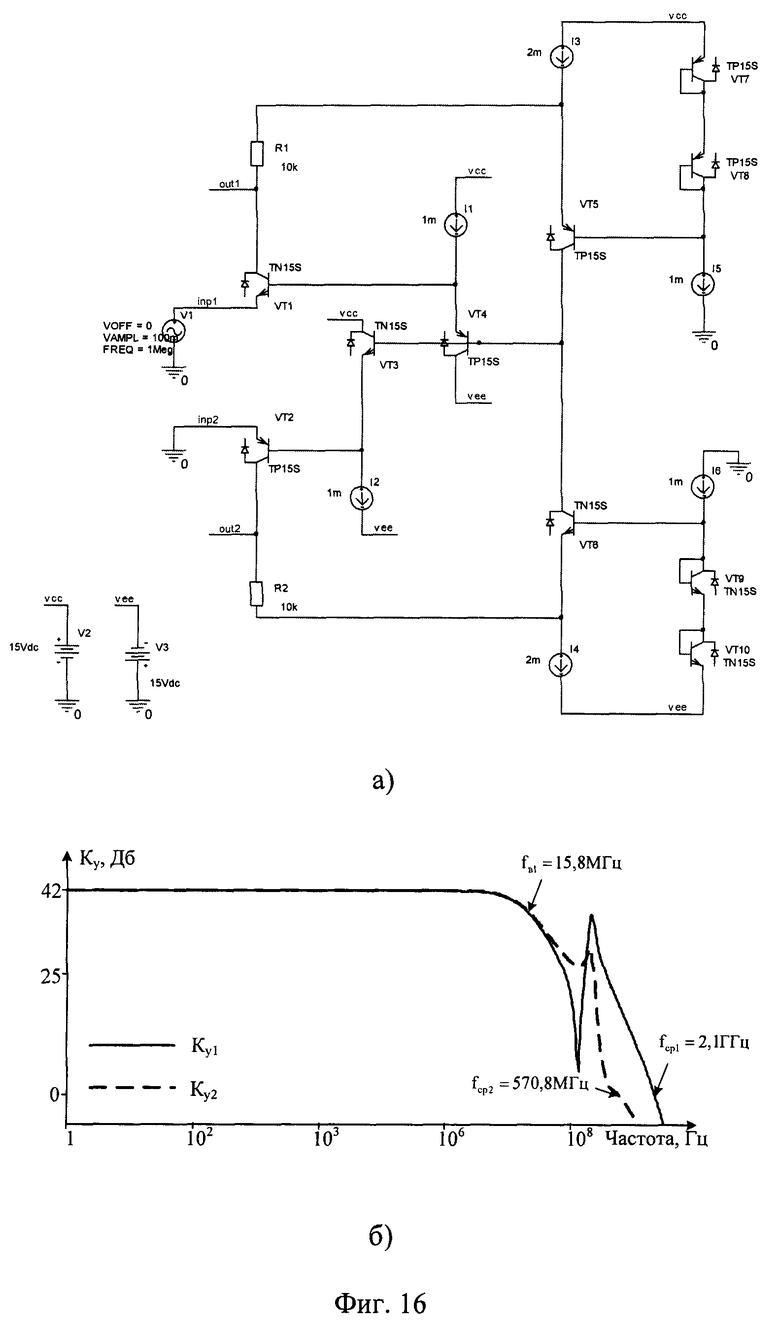

Компьютерная модель фиг.16а соответствует схеме фиг.12. Результаты исследования частотной зависимости ее двух коэффициентов усиления показаны на фиг.16б.

Дифференциальный усилитель фиг.2 содержит первый 1 n-p-n и второй 2 p-n-p входные транзисторы, эмиттеры которых соединены с соответствующими первым 3 и вторым 4 токовыми входами дифференциального усилителя, первый 5 вспомогательный p-n-p транзистор, коллектор которого соединен с базой первого 1 n-p-n входного транзистора, второй 6 n-p-n вспомогательный транзистор, коллектор которого связан с базой второго 2 n-p-n входного транзистора, база первого 5 p-n-p вспомогательного транзистора соединена с первым 7 источником напряжения смещения, а эмиттер подключен к шине первого 8 источника питания через первый 9 вспомогательный двухполюсник, база второго 6 n-p-n вспомогательного транзистора соединена со вторым 10 источником напряжения смещения, а эмиттер подключен к шине второго 11 источника питания через второй 12 вспомогательный двухполюсник, причем коллекторы первого 5 вспомогательного p-n-p транзистора и второго 6 вспомогательного p-n-p транзистора соединены друг с другом по переменному току. Коллектор первого 1 n-p-n входного транзистора соединен с эмиттером первого 5 p-n-p вспомогательного транзистора, а коллектор второго 2 p-n-p входного транзистора соединен с эмиттером второго 6 вспомогательного n-p-n транзистора.

На фиг.2 в соответствии с п.2 формулы изобретения между базами первого 1 n-p-n входного транзистора и второго 2 p-n-p входного транзистора включена цепь смещения статического потенциала 13, имеющая малое сопротивление на переменном токе.

На фиг.3 в соответствии с п.3 формулы изобретения коллектор первого 1 n-p-n входного транзистора соединен с эмиттером первого 5 p-n-p вспомогательного транзистора через первый 14 двухполюсник нагрузки.

На чертеже фиг.3 в соответствии с п.4 формулы изобретения коллектор второго 2 p-n-p входного транзистора соединен с эмиттером второго 6 n-p-n вспомогательного транзистора через второй 15 двухполюсник нагрузки.

На фиг.4 в соответствии с п.5 формулы изобретения в схему введены первый 18 и второй 19 дополнительные транзисторы, коллекторы которых соединены с первым 20 и вторым 21 токовыми выходами дифференциального усилителя, их базы подключены к соответствующим первому 7 и второму 10 источникам напряжения смещения, а эмиттеры связаны с эмиттерами соответствующих первого 5 p-n-p и второго 6 n-p-n вспомогательных транзисторов. В частном случае цепь смещения статического потенциала 13 выполнена на транзисторах 16 и 17.

На фиг.5 в соответствии с п.6 формулы изобретения в схему введены третий 22 и четвертый 23 дополнительные транзисторы, коллекторы которых соединены с третьим 24 и четвертым 25 токовыми выходами дифференциального усилителя, их базы подключены к базам соответствующих первого 1 n-p-n и второго 2 p-n-p входных транзисторов, а эмиттеры связаны с эмиттерами соответствующих первого 1 n-p-n и второго 2 p-n-p входных транзисторов.

На фиг.5 в соответствии с п.7 формулы изобретения к третьему 24 и четвертому 25 токовым выходам дифференциального усилителя подключены третий 26 и четвертый 27 двухполюсники нагрузки.

На фиг.8 в соответствии с п.8 формулы изобретения третий 24 токовый выход дифференциального усилителя соединен с эмиттером пятого 28 дополнительного транзистора, коллектор которого связан с пятым 29 токовым выходом дифференциального усилителя, четвертый токовый выход 25 дифференциального усилителя соединен с эмиттером шестого 30 дополнительного транзистора, коллектор которого связан с шестым 31 токовым выходом дифференциального усилителя, причем к эмиттерам пятого 28 и шестого 30 дополнительных транзисторов подключены первый 32 и второй 33 дополнительные двухполюсники.

На фиг.9 в соответствии с п.9 формулы изобретения в схему введены седьмой 34 и восьмой 35 дополнительные транзисторы, эмиттер седьмого 34 дополнительного транзистора подключен ко второму 4 токовому входу дифференциального усилителя, его коллектор соединен с эмиттером, а база - с коллектором первого 5 p-n-p вспомогательного транзистора, эмиттер восьмого 35 вспомогательного транзистора подключен к первому 3 токовому входу дифференциального усилителя, его коллектор соединен с эмиттером, а база с коллектором второго 6 n-p-n вспомогательного транзистора.

На фиг.10 в соответствии с п.10 формулы изобретения в коллекторные цепи первого 1 n-p-n и второго 2 p-n-p входных транзисторов, а также седьмого 34 и восьмого 35 дополнительных транзисторов включены пятый 36, шестой 37, седьмой 38 и восьмой 39 двухполюсники нагрузки.

На фиг.11 в соответствии с п.11 формулы изобретения параллельно эмиттерно-базовым р-n переходам седьмого 34 и восьмого 35 дополнительных транзисторов включены эмиттерно-базовые р-n переходы девятого 40 и десятого 41 дополнительных транзисторов, коллекторы которых являются вспомогательными токовыми выходами 42 и 43 дифференциального усилителя.

На фиг.12 в соответствии с п.12 формулы изобретения коллектор первого 5 вспомогательного p-n-p транзистора связан с базой первого 1 n-p-n входного транзистора через первый эмиттерный повторитель 44, коллектор второго 6 вспомогательного n-p-n транзистора соединен с базой второго 2 входного p-n-p транзистора через второй эмиттерный повторитель 45, коллектор первого 1 n-p-n входного транзистора связан с эмиттером первого 5 p-n-p вспомогательного транзистора через девятый 50 двухполюсник нагрузки, коллектор второго 2 p-n-p входного транзистора связан с эмиттером второго 6 n-p-n вспомогательного транзистора через десятый 51 двухполюсник нагрузки. Первый 44 и второго 45 эмиттерные повторители реализованы на основе элементов 46-47 и 48-49.

Рассмотрим работу заявляемого ДУ на примере анализа схемы фиг.2.

При нулевых значениях сигналов на входах (3) и (4) статический режим по току всех транзисторов устанавливается источниками опорного тока (двухполюсниками) 9 и 12.

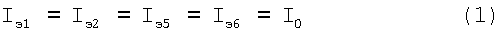

Если цепь смещения 13 содержит р-n переходы, идентичные р-n переходам транзисторов 1 и 2, то при I9=I12=2I0 токи эмиттера транзисторов

где Iэi - ток эмиттера i-го транзистора;

I9, I12 - токи двухполюсников 9 и 12.

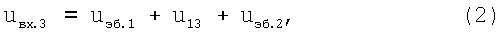

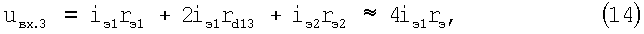

Если на вход 3 подается небольшое напряжение uвх.3, то это напряжение прикладывается к эмиттерно-базовому переходу транзистора 1 и транзистора 2, а также цепи смещения:

где u13 - приращение напряжения на двухполюснике 13.

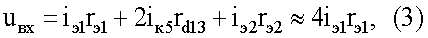

При выполнении двухполюсника 13 на базе двух р-n переходов и идентичности статических режимов по току (1) можно найти, что

где rэ - дифференциальное сопротивление эмиттерных переходов транзисторов 1 и 2;

rd13=rэ - дифференциальное сопротивление одного р-n перехода двухполюсника 13.

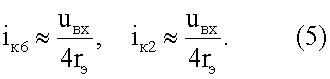

Таким образом, изменение uвх.3 вызывает изменение коллекторных токов всех транзисторов схемы на одинаковую величину:

Эти изменения токов (приращения выходных токовых координат ДУ) могут быть преобразованы в изменения выходных потенциалов за счет введения двухполюсников нагрузки 14 и 15 (фиг.3). Поэтому модули коэффициентов передачи по напряжению в ДУ фиг.3

При этом фаза напряжения на выходе «Вых.2» противоположна фазе напряжения на выходе Вых.1. То есть выход Вых.1 - неинвертирующий, а выход Вых.2 - инвертирующий, что является базовым свойством любого дифференциального усилителя.

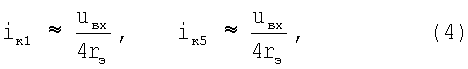

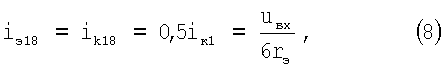

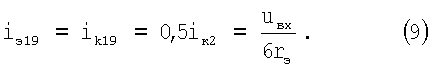

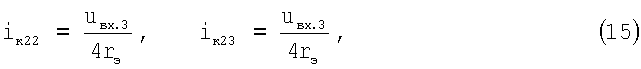

В схеме фиг.4 токи коллектора транзисторов 1 (iк1) и 2 (ik2) делятся между эмиттерами транзисторов 5 и 18 (6 и 19)

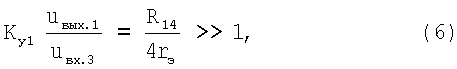

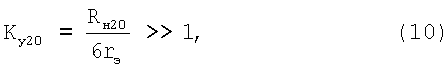

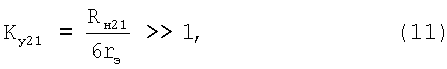

Поэтому коэффициенты усиления по напряжению в ДУ фиг.4 на выходы 20

где Rн20, Rн21 - эквивалентные сопротивления двухполюсников нагрузки, подключаемой к выходам 20 и 21.

При этом к выходу 20 сигнал не инвертируется, а к выходу 21 - инвертируется.

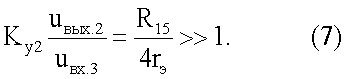

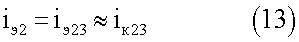

Особенность схемы фиг.5 состоит в том, что здесь выходной потенциальный сигнал образуется в коллекторной цепи транзисторов 22 и 23, так как здесь:

Причем на основании второго закона Кирхгофа

где rэ=rэ1≈rэ2=rd13.

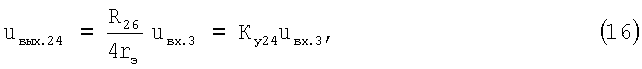

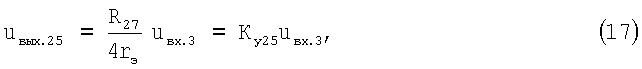

То есть выходные токи и выходные напряжения ДУ фиг.5

где  ,

,  - коэффициент усиления,

- коэффициент усиления,

R26, R27 - сопротивления двухполюсников нагрузки 26 и 27.

В схеме фиг.8, которая совпадает по структуре со схемой фиг.5, но имеет другое графическое описание с использованием обозначения «двухколлекторных транзисторов», на входы 3 и 4 подаются напряжения, имеющие синфазную составляющую.

Действительно, заявляемый ДУ может работать как от дифференциальных сигналов uвх=uвx.3-uвх.4, так и при наличии в этих сигналах синфазной составляющей

Увеличение, например, на 5 В синфазного сигнала на входах 3 и 4 (uвx.3=uвx.4=5B) передается на базы транзисторов 1 и 2. Как следствие, токи через транзисторы (1), (2), (5) и (6) не изменяются, то есть схема фиг.2 работоспособна при синфазном изменении входных сигналов uвх.3, uвx.4 - она обеспечивает преобразование разности uвх.3-uвх.4 в широком диапазоне

uc=(uвх.3+uвх.4)/2.

На фиг.7 показан ДУ с четырьмя выходами, использующий свойства схем фиг.4 и фиг.5. Здесь сигнал на выходах 24 и 20 имеет такую же фазу, что и uвх.3, а фаза выходных напряжений uвых.25 и uвых.21 противоположна фазе uвх.3. При этом следует особенно отметить, что противофазные выходы 20 и 25 согласованы с шиной отрицательного, а выходы 24 и 21 - положительного источников питания.

Схема фиг.8 имеет такие же коэффициенты усиления к выходам 29 и 31 по напряжению, что и схема фиг.5. Однако она более широкополосна, так как транзисторы 22 и 28 (23 и 30) образуют каскодную архитектуру.

Дифференциальный усилитель фиг.9 обладает более высокой симметрией входов при различных полярностях входного напряжения uвх.3 за счет введения транзисторов 34 и 35. Пример построения практической схемы усилителя напряжения на базе ДУ фиг.10 дан на фиг.10.

Дальнейшим развитием предлагаемых схем (фиг.5 и фиг.9) является схема фиг.11, которая имеет 4 токовых противофазных выхода (24, 42, 25 и 43), «привязанных» к разным шинам питания 8 и 11.

В схеме фиг.12 начальный статический режим ДУ устанавливается эмиттерными повторителями 44 и 45. В остальном ее работа описывается теми же уравнениями, что и работа других схем. Однако данная схема обеспечивает более высокое усиление по напряжению.

Компьютерное моделирование схемы фиг.7 в среде PSpice фиг.13 показывает, что заявляемое устройство является широкополосным дифференциальным усилителем. Однако его выходы «привязаны» (в отличие от классического ДУ) к разным шинам питания.

В схеме фиг.14а входной сигнал подается на второй вход ДУ, а первый вход связан с общей шиной. При этом свойства ДУ практически не изменяются (фиг.14б).

Схема фиг.15а соответствует ДУ фиг.10. Ее исследования (фиг.15б) показывают, что предлагаемое устройство обладает всеми свойствами классического дифференциального каскада, однако имеет низкоомные токовые входы.

Работоспособность схемы фиг.12 и ее модели фиг.16а иллюстрируют графики фиг.16б.

Таким образом, полученные выше теоретические выводы подтверждаются результатами моделирования предлагаемых схем в среде PSpice с использованием моделей интегральных транзисторов ФГУП НПП «Пульсар» (г.Москва).

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №5.734.294 (прототип)

2. Патент США №6.621.308

3. Патент США №6.639.473

4. Патентная заявка США US 2005/0140443

5. Патент США №5.900.779

6. Патент США №5.742.154

7. Патент США №5.834.951

8. Патент США №4.378.529

9. Патент США №4.510.459

10. Патент США №5.973.562

11. Патент Франции №2337969

12. Патент США №4.887.047

13. Патент Японии JP 2001308658

14. Патент США №3.972.003

15. Патент США №4.521.739

16. Патентная заявка US 2005/0140444

17. Патент США №4.277.756

18. Патентная заявка US 2004/0160275

19. Патент США №6.181.207

20. Патент США №4.521.737

21. Патент США №4.232.271

22. Патентная заявка US 2004/0227477

23. Патент США №5.734.294

24. Патент США №6.191.654

25. Патент США №4.065.724

26. Патент США RE 30.587, Кл. 330-257, 1981 г.

27. Патент США №6.825.723

28. Патент США №5.126.586

29. Патент США №5.258.723

30. Патент США №6.882.224

31. Патент США №5.671.272

32. Патентная заявка US 2005/0218994 A1

33. Патент США №5.671.272

34. Патент США №6.882.224

35. Патентная заявка US 2005/0140443

36. Патент США №3.748.588

37. Патентная заявка ЕР 1548932 A1

38. Патент США №5.742.154

39. Патент США №4.521.739

40. Патентная заявка US 2004/0160275

41. Патент США №4.232.271

42. Патент США №6.191.654

43. Патент США №5.126.586

44. Патент США №5.671.272

45. Патент США №6.822.514

46. Патент США №6.624.704

47. Патент США №4.446.443

48. Патент США №4.393.355

49. Патент США №3.748.588

50. Патентная заявка US 2006/0125565

51. Патентная заявка US 2005/0218994

52. Патент США №4.510.459

53. Патентная заявка US 2005/0140443

54. Патент США №4.887.047

55. Патент Японии JP 2001308658

56. Патент США №6.822.514

57. Патентная заявка US 2005/0140444

58. Патент США №4.277.756

59. Патент США №5.126.586

60. Патентная заявка US 2005/0218994

| название | год | авторы | номер документа |

|---|---|---|---|

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319296C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ АКТИВНОЙ РАБОТЫ | 2007 |

|

RU2331971C1 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2012 |

|

RU2509406C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПО НАПРЯЖЕНИЮ | 2007 |

|

RU2331972C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2394362C1 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2012 |

|

RU2504896C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2411638C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ СИНФАЗНОГО СИГНАЛА | 2006 |

|

RU2319287C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ АКТИВНОЙ РАБОТЫ | 2006 |

|

RU2321160C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ КЛАССА АВ | 2007 |

|

RU2331970C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления высокочастотных аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в драйверах линий связи, операционных усилителях (ОУ), быстродействующих компараторах двух напряжений и т.п.). Технический результат: повышение симметрии схемы по входам и, как следствие, обеспечение одинаковых величин коэффициентов передачи от входов к выходам, согласованным с разными шинами источников питания. Дифференциальный усилитель (ДУ) с токовыми входами содержит первый 1 n-p-n и второй (2) p-n-p входные транзисторы (Т), эмиттеры которых соединены с соответствующими первым (3) и вторым (4) токовыми входами ДУ, первый (5) вспомогательный p-n-p Т, коллектор которого соединен с базой первого (1) n-p-n входного Т, второй (6) n-p-n вспомогательный Т, коллектор которого связан с базой второго (2) n-p-n входного транзистора, база первого (5) p-n-p вспомогательного Т соединена с первым (7) источником напряжения смещения, а эмиттер подключен к шине первого (8) источника питания (ИП) через первый (9) вспомогательный двухполюсник, база второго (6) n-p-n вспомогательного Т соединена со вторым (10) источником напряжения смещения, а эмиттер подключен к шине второго (11) ИП через второй (12) вспомогательный двухполюсник, причем коллекторы первого (5) вспомогательного p-n-p Т и второго (6) вспомогательного p-n-p Т соединены друг с другом по переменному току. Коллектор первого (1) n-p-n входного Т соединен с эмиттером первого (5) p-n-p вспомогательного Т, а коллектор второго (2) p-n-p входного Т соединен с эмиттером второго (6) вспомогательного n-p-n Т. 11 з.п. ф-лы, 16 ил.

1. Дифференциальный усилитель с низкоомными входами, содержащий первый (1) n-p-n и второй (2) p-n-p входные транзисторы, эмиттеры которых соединены с соответствующими первым (3) и вторым (4) токовыми входами дифференциального усилителя, первый (5) вспомогательный p-n-p транзистор, коллектор которого соединен с базой первого (1) n-p-n входного транзистора, второй (6) n-p-n вспомогательный транзистор, коллектор которого связан с базой второго (2) n-p-n входного транзистора, база первого (5) p-n-p вспомогательного транзистора соединена с первым (7) источником напряжения смещения, а эмиттер подключен к шине первого (8) источника питания через первый (9) вспомогательный двухполюсник, база второго (6) n-p-n вспомогательного транзистора соединена со вторым (10) источником напряжения смещения, а эмиттер подключен к шине второго (11) источника питания через второй (12) вспомогательный двухполюсник, причем коллекторы первого (5) вспомогательного p-n-p транзистора и второго (6) вспомогательного p-n-p транзистора соединены друг с другом по переменному току, отличающийся тем, что коллектор первого (1) n-p-n входного транзистора соединен с эмиттером первого (5) p-n-p вспомогательного транзистора, а коллектор второго (2) p-n-p входного транзистора соединен с эмиттером второго (6) вспомогательного n-p-n транзистора.

2. Устройство по п.1, отличающееся тем, что между базами первого (1) n-p-n входного транзистора и второго (2) p-n-p входного транзистора включена цепь смещения статического потенциала (13), имеющая малое сопротивление на переменном токе.

3. Устройство по п.1, отличающееся тем, что коллектор первого (1) n-p-n входного транзистора соединен с эмиттером первого (5) p-n-p вспомогательного транзистора через первый (14) двухполюсник нагрузки.

4. Устройство по п.1, отличающееся тем, что коллектор второго (2) p-n-p входного транзистора соединен с эмиттером второго (6) n-p-n вспомогательного транзистора через второй (15) двухполюсник нагрузки.

5. Устройство по п.1, отличающееся тем, что в схему введены первый (18) и второй (19) дополнительные транзисторы, коллекторы которых соединены с первым (20) и вторым (21) токовыми выходами дифференциального усилителя, их базы подключены к соответствующим первому (7) и второму (10) источникам напряжения смещения, а эмиттеры связаны с эмиттерами соответствующих первого (5) p-n-p и второго (6) n-p-n вспомогательных транзисторов.

6. Устройство по п.1, отличающееся тем, что в схему введены третий (22) и четвертый (23) дополнительные транзисторы, коллекторы которых соединены с третьим (24) и четвертым (25) токовыми выходами дифференциального усилителя, их базы подключены к базам соответствующих первого (1) n-p-n и второго (2) p-n-p входных транзисторов, а эмиттеры связаны с эмиттерами соответствующих первого (1) n-p-n и второго (2) p-n-p входных транзисторов.

7. Устройство по п.6, отличающееся тем, что к третьему (24) и четвертому (25) токовым выходам дифференциального усилителя подключены третий (26) и четвертый (27) двухполюсники нагрузки.

8. Устройство по п.6, отличающееся тем, что третий (24) токовый выход дифференциального усилителя соединен с эмиттером пятого (28) дополнительного транзистора, коллектор которого связан с пятым (29) токовым выходом дифференциального усилителя, четвертый токовый выход (25) дифференциального усилителя соединен с эмиттером шестого (30) дополнительного транзистора, коллектор которого связан с шестым (31) токовым выходом дифференциального усилителя, причем к эмиттерам пятого (28) и шестого (30) дополнительных транзисторов подключены первый (32) и второй (33) дополнительные двухполюсники, осуществляющие согласование третьего (24) и четвертого (25) выходов дифференциального усилителя с шинами положительного и отрицательного источников питания.

9. Устройство по п.1, отличающееся тем, что в схему введены седьмой (34) и восьмой (35) дополнительные транзисторы, эмиттер седьмого (34) дополнительного транзистора подключен ко второму (4) токовому входу дифференциального усилителя, его коллектор соединен с эмиттером, а база - с коллектором первого (5) p-n-p вспомогательного транзистора, эмиттер восьмого (35) вспомогательного транзистора подключен к первому (3) токовому входу дифференциального усилителя, его коллектор соединен с эмиттером, а база - с коллектором второго (6) n-p-n вспомогательного транзистора.

10. Устройство по п.9, отличающееся тем, что в коллекторные цепи первого (1) n-p-n и второго (2) p-n-p входных транзисторов, а также седьмого (34) и восьмого (35) дополнительных транзисторов включены пятый (36), шестой (37), седьмой (38) и восьмой (39) двухполюсники нагрузки.

11. Устройство по п.5 или 9, отличающееся тем, что параллельно эмиттерно-базовым р-n переходам седьмого (34) и восьмого (35) дополнительных транзисторов включены эмиттерно-базовые р-n переходы девятого (40) и десятого (41) дополнительных транзисторов, коллекторы которых являются вспомогательными токовыми выходами (42) и (43) дифференциального усилителя.

12. Устройство по п.1, отличающееся тем, что коллектор первого (5) вспомогательного p-n-p транзистора связан с базой первого (1) n-p-n входного транзистора через первый эмиттерный повторитель (44), коллектор второго (6) вспомогательного n-p-n транзистора соединен с базой второго (2) входного p-n-p транзистора через второй эмиттерный повторитель (45), коллектор первого (1) n-p-n входного транзистора связан с эмиттером первого (5) p-n-p вспомогательного транзистора через девятый (50) двухполюсник нагрузки, коллектор второго (2) p-n-p входного транзистора связан с эмиттером второго (6) n-p-n вспомогательного транзистора через десятый (51) двухполюсник нагрузки.

| US 5512859 А, 30.04.1996 | |||

| Усилитель тока | 1988 |

|

SU1631703A2 |

| Усилительный каскад | 1984 |

|

SU1234949A1 |

| Дорожная спиртовая кухня | 1918 |

|

SU98A1 |

Авторы

Даты

2010-02-27—Публикация

2008-04-16—Подача