Изобретение относится к системам приема оптической информации с многоэлементных приемников и ее обработки средствами интегральной микроэлектроники.

Детекторы ИК излучения на материалах с большой квантовой эффективностью отличаются большой темновой и фоновой составляющей фототока (десятки и сотни наноампер), что требует значительных зарядовых емкостей (более 5 пФ) схем считывания. которые могли бы интегрировать фототок детекторов без переполнения в течение заданного времени. В ВЗН схемах емкость должна быть увеличена в n раз, где n - количество каскадов ВЗН, что делает проблематичным топологическое размещение таких емкостей на кристалле микросхемы и, тем самым, ограничивает количество каскадов ВЗН. С другой стороны, например, в низкофоновых ФПУ с малым аппертурным углом или в ФПУ, у которых в устройствах ввода из входного тока удаляется его фоновая и темновая составляющие, и сигнал чрезвычайно мал (менее 0,1 нА), для обнаружения низкоконтрастных объектов требуются большие коэффициенты преобразования заряда в напряжение, а следовательно, использование емкостей малой величины (менее 0,1 пФ). В КМДП ВЗН схемах паразитная емкость межсоединений таких емкостей становится сравнимой с самими емкостями, что ограничивает коэффициент преобразования и предельные обнаружительные параметры ФПУ в целом.

Известно устройство считывания в ВЗН с многоэлементных ИК фотоприемников (Патент RU 2236064 С1, Н01L 27/14). Данное устройство, выполненное на полупроводниковой подложке, содержит n устройств ввода и устройство считывания с ВЗН, каждое устройство ввода содержит первый транзистор, исток которого соединен с выходом фотодетектора, затвор с выходом усилителя, вход которого соединен с истоком первого транзистора, сток которого соединен с первой обкладкой интегрирующей емкости, вторая обкладка которой соединена с полупроводниковой подложкой, первую, вторую,..., n-ю емкости выборок, вторые обкладки которых соединены с полупроводниковой подложкой, а первые обкладки соединены с истоками соответственно первого, второго,..., n-го выходного транзистора, стоки которых объединены и соединены с выходом устройства.

Недостаток такого устройства заключается в том, что емкость истоков транзисторов и шин, по которым происходит передача заряда, могут быть значительными, что ограничивает максимальный коэффициент преобразования заряда в напряжение. Кроме того, емкости интегрирования занимают значительную площадь микросхемы, что ограничивает количество каскадов ВЗН, а значит, и чувствительность.

Известно также устройство считывания с двумерных ИК фотоматриц с режимом ВЗН [B.Kim. at al. Novel concept of TDI readout circuit for LWIR detector, SPIE. Vol.4028, p.166, (2000)].

Устройство считывания сигналов с ВЗН с многоэлементных ИК фотоприемников, выполненное на полупроводниковой подложке, содержащее n устройств ввода, где n - количество ВЗН каскадов, n устройств коммутации, (n+1) шин управления, (n+1) устройств выборок, каждое устройство ввода содержит первый транзистор, исток которого соединен с выходом фотодетектора, затвор с выходом усилителя, вход которого соединен с истоком первого транзистора, сток которого соединен с первой обкладкой интегрирующей емкости, вторая обкладка которой соединена с полупроводниковой подложкой, каждое устройство коммутации содержит первый, второй,..., (n+1) коммутационные транзисторы, истоки которых объединены и являются входом устройства коммутации, причем стоки i-х коммутационных транзисторов, где i от 1 до (n+1), из каждого устройства коммутации, объединены, а затворы первого, второго,..., (n+1) коммутационных транзисторов j-го устройства коммутации соединены соответственно с 1+(j-1), 2+(j-1),..., n, (n+1), 1, 2,..., (j-1)-й шиной управления, где j от 1 до n, в каждом устройстве выборок первые емкости выборок, одна обкладка которой соединена с подложкой, другая с истоком первого выходного транзистора, сток которого соединен с выходом устройства, затвор первого выходного транзистора первого, второго,..., (n+1) устройств выборок соединен соответственно с (n+1), первой, второй,..., n-й шинами управления.

Данное устройство является ближайшим к предлагаемому техническому решению.

Устройство работает следующим образом. При подаче последовательных, не пересекающихся во времени, равной длительности импульсов на шины управления, фототок от детекторов накапливается в интегрирующих емкостях, причем в каждой емкости суммирование фототока идет последовательно от первого до последнего детектора, чем и обеспечивается режим ВЗН.

Недостаток такого устройства заключается в том, что емкость истоков транзисторов и шин, по которым происходит передача заряда, могут быть значительными, что ограничивает максимальный коэффициент преобразования заряда в напряжение. Кроме того, емкости интегрирования занимают значительную площадь микросхемы, что ограничивает количество каскадов ВЗН, а значит, и чувствительность.

Техническим результатом изобретения является повышение чувствительности интегрального устройства считывания сигналов с ВЗН.

Технический результат достигается тем, что устройство считывания сигналов с ВЗН с многоэлементных ИК фотоприемников, выполненное на полупроводниковой подложке, содержащее n устройств ввода, где n - количество ВЗН каскадов, n устройств коммутации, (n+1) шин управления, (n+1) устройств выборок, каждое устройство ввода содержит первый транзистор, исток которого соединен с выходом фотодетектора, затвор с выходом усилителя, вход которого соединен с истоком первого транзистора, сток которого соединен с первой обкладкой интегрирующей емкости, вторая обкладка которой соединена с полупроводниковой подложкой, каждое устройство коммутации содержит первый, второй,..., (n+1) коммутационные транзисторы, истоки которых объединены и являются входом устройства коммутации, причем стоки i-х коммутационных транзисторов, где i от 1 до (n+1), из каждого устройства коммутации, объединены, а затворы первого, второго,..., (n+1) коммутационных транзисторов j-го устройства коммутации соединены соответственно с 1+(j-1), 2+(j-1),..., n, (n+1), 1, 2,..., (j-1)-й шиной управления, где j от 1 до n, в каждом устройстве выборок первые емкости выборок, одна обкладка которой соединена с подложкой, другая с истоком первого выходного транзистора, сток которого соединен с выходом устройства, затвор первого выходного транзистора первого, второго,..., (n+1) устройств выборок соединен соответственно с (n+1), первой, второй,..., n-ой шинами управления, отличающееся тем, что устройство содержит дополнительную шину управления сбросом, дополнительную шину напряжения сброса, в каждом устройстве ввода дополнительный транзистор сброса и повторитель напряжения, в каждом устройстве выборок n дополнительных коммутационных транзисторов, (n-1) дополнительных емкостей выборок, (n-1) дополнительных выходных транзисторов, причем исток дополнительного транзистора сброса устройства ввода соединен с дополнительной шиной напряжения сброса, его затвор с дополнительной шиной управления сбросом, а сток соединен, в каждом устройстве ввода, со стоком первого транзистора и входом повторителя напряжения, выход которого соединен с входом соответствующего устройства коммутации, в каждом устройстве выборок истоки первого, второго,..., n-го дополнительных коммутационных транзисторов объединены, их стоки соединены соответственно с истоками первого выходного транзистора и истоками второго, третьего,..., n-го дополнительных выходных транзисторов, стоки которых соединены с выходом устройства, одна обкладка второй, третьей,..., n-й дополнительных емкостей выборок соединены с подложкой, другие соединены соответственно с истоками второго, третьего,... n-го дополнительных выходных транзисторов, затворы которых соединены с затвором первого выходного транзистора, объединенные истоки дополнительных коммутационных транзисторов в первом, втором,..., (n+1) устройствах выборок соединены соответственно со стоками первого, второго,..., (n+1) коммутационных транзисторов первого устройства коммутации, затворы первого, второго,..., n-го дополнительных коммутационных транзисторов m-го устройства выборок соединены соответственно с m, (m+1),..., n, (n+1), 1, 2,..., (m-2) шинами управления, где m от 1 до (n+1).

Технических решений, содержащих признаки, сходные с отличительными, не выявлено, что позволяет сделать вывод о соответствии заявляемого технического решения критерию «новизна».

В ранее известных схемах с ВЗН каждая емкость интегрирования выполняла как бы двойную функцию: интегрирование фототока и хранение ранее накопленного заряда. В заявляемом техническом решении эти функции разделены, а каждая из емкостей оптимизированы. Повторитель напряжения, расположенный в каждой ячейке устройства ввода, исключает влияние на емкость интегрирования паразитных емкостей шин и истоков, стоков транзисторов устройств коммутации и выборок. Тем самым емкость интегрирования может быть уменьшена, что обеспечит больший коэффициент преобразования заряда в напряжение, и следовательно, увеличит чувствительность устройства считывания в целом.

Величина емкостей выборок устройств выборок не определяется током детекторов и временем интегрирования, и следовательно, может занимать меньшую площадь. Тем самым на кристалле микросхемы может быть размещено большее количество каскадов ВЗН.

Например, в схеме прототипа сумма всех емкостей составляет величину n·Синт·(n+1), где Синт - минимальная емкость интегрирования, которая позволяет накопить без переполнения (насыщения) заряд от одного детектора за заданное время интегрирования. В предлагаемом техническом решении, в случае если емкости выборок Свыб одинаковые, сумма емкостей составит величину n·Синт+n·(n+1)·Свыб=n·Синт[(n+1)·Свыб/Синт+1]. Видно, что значительная экономия площади кристалла появляется при Свыб<<Синт. Например, в случае приемников на КРТ фотодиодах, при фототоке I=100 нА, времени интегрирования Т=200 мкс, диапазоне рабочих напряжений U=4B имеем Синт=I*T/U=5 пФ. При Свыб=0,5 пФ и n=4 величина суммарной емкости для прототипа составляет 4·5 пФ·5=100 пФ, а для предложенного решения 4·5 пФ+4·5·0,5 пФ=30 пФ, то есть имеет место трехкратная экономия площади. Для n=8 экономия почти восьмикратная.

Тем самым, новая совокупность признаков позволяет сделать заключение о соответствии заявляемого технического решения критерию «изобретательский уровень».

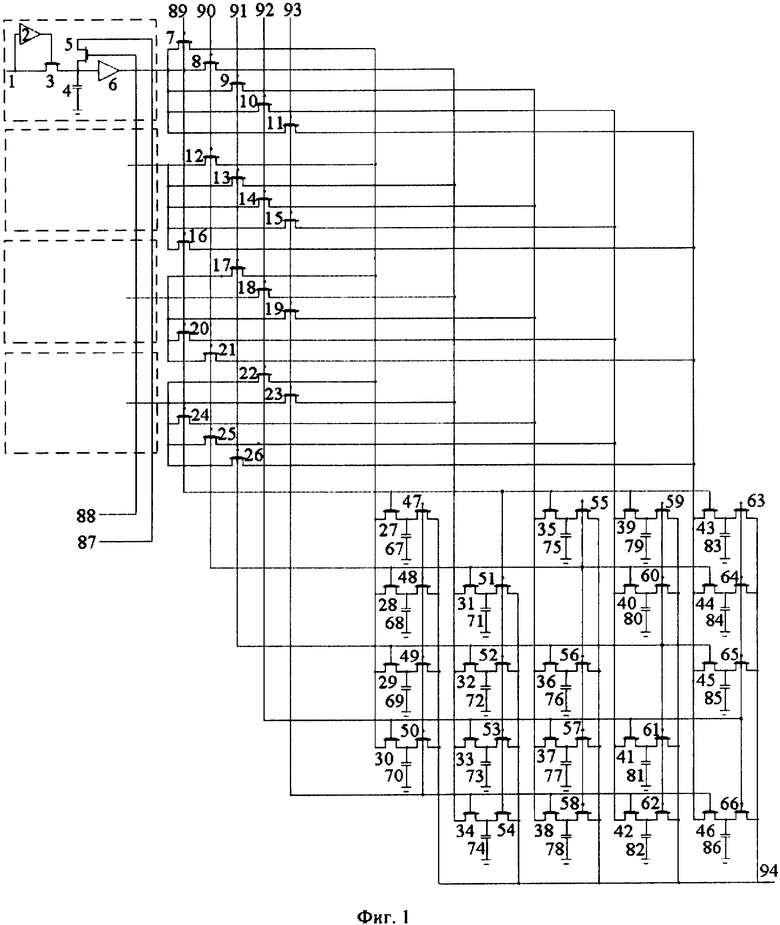

На Фиг.1 приведена принципиальная схема предлагаемого устройства с числом каскадов ВЗН n=4.

На Фиг.2 приведена диаграмма управляющих напряжений.

На Фиг.1 изображено: 1 - вход первой ячейки устройства ввода, 2 - усилитель первой ячейки устройства ввода, 3 - первый транзистор первой ячейки устройства ввода, 4 - интегрирующая емкость первой ячейки устройства ввода, 5 - дополнительный транзистор сброса первой ячейки устройства ввода, 6 - повторитель напряжения первой ячейки устройства ввода, 7, 8, 9, 10, 11 - первый, второй, третий, четвертый и пятый коммутационные транзисторы первого устройства коммутации, 12, 13, 14, 15, 16 - первый, второй, третий, четвертый и пятый коммутационные транзисторы второго устройства коммутации, 17, 18, 19, 20, 21 - первый, второй, третий, четвертый и пятый коммутационные транзисторы третьего устройства коммутации, 22, 23, 24, 25, 26 - первый, второй, третий, четвертый и пятый коммутационные транзисторы четвертого устройства коммутации, 27, 28, 29, 30 - первый, второй, третий и четвертый дополнительные коммутационные транзисторы первого устройства выборок, 31, 32, 33, 34 - первый, второй, третий и четвертый дополнительные коммутационные транзисторы второго устройства выборок, 35, 36, 37, 38 - первый, второй, третий и четвертый дополнительные коммутационные транзисторы третьего устройства выборок, 39, 40, 41, 42 - первый, второй, третий и четвертый дополнительные коммутационные транзисторы четвертого устройства выборок, 43, 44, 45, 46 - первый, второй, третий и четвертый дополнительные коммутационные транзисторы пятого устройства выборок, 47, 51, 56, 61, 66 - первые выходные транзисторы соответственно первого, второго, третьего, четвертого и пятого устройств выборок, 48, 49, 50 - соответственно второй, третий и четвертый дополнительные выходные транзисторы первого устройства выборок, 52, 53, 54 - соответственно второй, третий и четвертый дополнительные выходные транзисторы второго устройства выборок, 57, 58, 55 - соответственно второй, третий и четвертый дополнительные выходные транзисторы третьего устройства выборок, 62, 59, 60, - соответственно второй, третий и четвертый дополнительные выходные транзисторы четвертого устройства выборок, 63, 64, 65 - соответственно второй, третий и четвертый дополнительные выходные транзисторы пятого устройства выборок, 67, 71, 76, 81, 86 - первые емкости выборок соответственно первого, второго, третьего, четвертого и пятого устройств выборок, 68, 69, 70 - соответственно вторая, третья и четвертая дополнительные емкости выборок первого устройства выборок, 72, 73, 74 - соответственно вторая, третья и четвертая дополнительные емкости выборок второго устройства выборок, 77, 78, 75 - соответственно вторая, третья и четвертая дополнительные емкости выборок третьего устройства выборок, 82, 79, 80 - соответственно вторая, третья и четвертая дополнительные емкости выборок четвертого устройства выборок, 83, 84, 85 - соответственно вторая, третья и четвертая дополнительные емкости выборок пятого устройства выборок, 87 - дополнительная шина напряжения сброса, 88 - дополнительная шина управления сбросом, 89, 90, 91, 92, 93 - соответственно первая, вторая, третья, четвертая и пятая шины управления, 94 - выход устройства.

Как показано на Фиг.1, вход первой ячейки устройства ввода 1 электрически соединен с входом усилителя первой ячейки устройства ввода 2 и истоком первого транзистора первой ячейки устройства ввода 3, затвор которого соединен с выходом усилителя 2, а сток со стоком дополнительного транзистора сброса первой ячейки устройства ввода 5, входом повторителя напряжения первой ячейки устройства ввода 6 и первой обкладкой интегрирующей емкости первой ячейки устройства ввода 4, вторая обкладка которой соединена с подложкой, исток транзистора сброса 5 соединен с дополнительной шиной напряжения сброса 87, а затвор с дополнительной шиной управления сбросом 88, выход повторителя напряжений 6 является выходом первой ячейки устройства ввода и соединен с истоками первого, второго, третьего, четвертого и пятого коммутационных транзисторов 7, 8, 9, 10, 11 первого устройства коммутации, соответственно выходы второй, третьей и четвертой ячеек устройств ввода соединены с истоками коммутационных транзисторов 12, 13, 14, 15, 16, истоками коммутационных транзисторов 17, 18, 19, 20, 21, истоками коммутационных транзисторов 22, 23, 24, 25, 26. Затворы коммутационных транзисторов 7, 16, 20, 24 соединены с первой шиной управления 89, затворы коммутационных транзисторов 8, 12, 21, 25 соединены со второй шиной управления 90, затворы коммутационных транзисторов 9, 13, 17, 26 соединены с третьей шиной управления 91, затворы коммутационных транзисторов 10, 14, 18, 22 соединены с четвертой шиной управления 92, затворы коммутационных транзисторов 11, 15, 19, 23 соединены с пятой шиной управления 93. Стоки первых коммутационных транзисторов 7, 12, 17, 22 всех устройств коммутации объединены, стоки вторых коммутационных транзисторов 8, 13, 18, 23 всех устройств коммутации объединены, стоки третьих коммутационных транзисторов 9, 14, 19, 24 всех устройств коммутации объединены, стоки четвертых коммутационных транзисторов 10, 15, 20, 25 всех устройств коммутации объединены, стоки пятых коммутационных транзисторов 11, 16, 21, 26 всех устройств коммутации объединены. Истоки дополнительных коммутационных транзисторов 27, 28, 29, 30 первого устройства выборок объединены и соединены со стоком первого транзистора 7 первого устройства коммутации, истоки дополнительных коммутационных транзисторов 31, 32, 33, 34 второго устройства выборок объединены и соединены со стоком второго транзистора 8 первого устройства коммутации, истоки дополнительных коммутационных транзисторов 35, 36, 37, 38 третьего устройства выборок объединены и соединены со стоком третьего транзистора 9 первого устройства коммутации, истоки дополнительных коммутационных транзисторов 39, 40, 41, 42 четвертого устройства выборок объединены и соединены со стоком четвертого транзистора 10 первого устройства коммутации, истоки дополнительных коммутационных транзисторов 43, 44, 45, 46 пятого устройства выборок объединены и соединены со стоком пятого транзистора 11 первого устройства коммутации. Стоки дополнительных коммутационных транзисторов 27, 28, 29, 30 первого устройства выборок соединены соответственно с первыми обкладками емкости выборок 67 и дополнительными емкостями выборок 68, 69, 70, вторые обкладки которых соединены с подложкой, а также стоки соответственно соединены с истоками первого выходного транзистора 47 и истоками второго, третьего и четвертого дополнительных выходных транзисторов 48, 49, 50, затворы которых соединены с пятой шиной управления 93, а стоки с выходом устройства 94. Стоки дополнительных коммутационных транзисторов 31, 32, 33, 34 второго устройства выборок соединены соответственно с первыми обкладками емкости выборок 71 и дополнительными емкостями выборок 72, 73, 74, вторые обкладки которых соединены с подложкой, а также стоки соответственно соединены с истоками первого выходного транзистора 51 и истоками второго, третьего и четвертого дополнительных выходных транзисторов 52, 53, 54, затворы которых соединены с первой шиной управления 89, а стоки с выходом устройства 94. Стоки дополнительных коммутационных транзисторов 36, 37, 38, 35 третьего устройства выборок соединены соответственно с первыми обкладками емкости выборок 76 и дополнительными емкостями выборок 77, 78, 75, вторые обкладки которых соединены с подложкой, а также стоки соответственно соединены с истоками первого выходного транзистора 56 и истоками второго, третьего и четвертого дополнительных выходных транзисторов 57, 58, 55, затворы которых соединены с второй шиной управления 90, а стоки с выходом устройства 94. Стоки дополнительных коммутационных транзисторов 41, 42, 39, 40 четвертого устройства выборок соединены соответственно с первыми обкладками емкости выборок 81 и дополнительными емкостями выборок 82, 79, 80, вторые обкладки которых соединены с подложкой, а также стоки соответственно соединены с истоками первого выходного транзистора 61 и истоками второго, третьего и четвертого дополнительных выходных транзисторов 62, 59, 60, затворы которых соединены с третьей шиной управления 91, а стоки с выходом устройства 94. Стоки дополнительных коммутационных транзисторов 46, 43, 44, 45 пятого устройства выборок соединены соответственно с первыми обкладками емкости выборок 86 и дополнительными емкостями выборок 83, 84, 85, вторые обкладки которых соединены с подложкой, а также стоки соответственно соединены с истоками первого выходного транзистора 66 и истоками второго, третьего и четвертого дополнительных выходных транзисторов 63, 64, 65, затворы которых соединены с четвертой шиной управления 92, а стоки с выходом устройства 94.

Устройство работает следующим образом. Фототок от каждого из четырех детекторов интегрируется на соответствующих емкостях 4 в устройствах ввода. Периодически, при подаче импульса на дополнительную шину управления сбросом 88, напряжение на интегрирующих емкостях 4 сбрасывается до исходного значения, заданного на дополнительной шине напряжения сброса 87. В конце цикла интегрирования, на выходах устройств ввода, повторители напряжений 6 формируют напряжения, пропорциональные накопленному от детекторов заряду. В конце же цикла интегрирования подается импульс на первую шину управления 89 и напряжения, сформированные на выходах первого, второго, третьего и четвертого устройств ввода передаются соответственно на первую емкость выборки 67, вторую 83, третью 79 и четвертую 75 дополнительные емкости выборок первого, пятого, четвертого и третьего устройств выборок. Далее, после импульса сброса, подаваемого на дополнительную шину управления сбросом 88 и нового цикла интегрирования, подается импульс на вторую шину управления 90 и напряжения, сформированные на выходах первого, второго, третьего и четвертого устройств ввода передаются соответственно на первую емкость выборки 71, вторую 68, третью 84 и четвертую 80 дополнительные емкости выборок второго, первого, пятого и четвертого устройств выборок, и так далее. После четырех циклов интегрирования на, например, первой емкости выборки 67 и второй 68, третьей 69, четвертой 70 дополнительных емкостях выборок первого устройства выборок сформированы заряды, соответственно пропорциональные накопленным на интегрирующих емкостях первого, второго, третьего и четвертого устройств ввода за первый, второй, третьий и четвертый циклы интегрирования. Далее, при подаче импульса на пятую шину управления 93, на выходе устройства 94 формируется напряжение, пропорциональное сумме зарядов, последовательно накопленных от четырех детекторов за четыре предыдущие цикла интегрирования.

Преимущества предлагаемого технического решения заключаются в том, что оно позволяет:

1. Увеличить чувствительность устройства считывания за счет увеличения коэффициента преобразования заряда в напряжение и увеличения количества каскадов ВЗН на кристалле микросхемы.

2. Уменьшить площадь, занимаемую микросхемой, сделать ее более компактной, уменьшить шаг расположения устройств считывания.

Использование: в системах приема оптической информации с многоэлементных приемников и ее обработки средствами интегральной микроэлектроники. Техническим результатом изобретения является повышение чувствительности интегрального устройства считывания сигналов с временной задержкой и накоплением сигналов (ВЗН). Сущность изобретения: в устройстве считывания с ВЗН сигналов с многоэлементных фотоприемников каждая из n ячеек устройств ввода, где n - количество каскадов ВЗН, содержит повторитель напряжения и дополнительный транзистор сброса, сток которого соединен с входом повторителя и с первой обкладкой интегрирующей емкости, а каждое из устройств выборок содержит n дополнительных коммутационных транзисторов, истоки которых объединены, стоки соединены соответственно с первыми обкладками первой емкости выборки и (n-1) дополнительными емкостями выборок и, соответственно, с истоками первого выходного транзистора и (n-1) дополнительными выходными транзисторами, стоки которых соединены с выходом устройства. Вторые обкладки емкостей выборок соединены с подложкой. Истоки дополнительных транзисторов сброса соединены с дополнительной шиной напряжения сброса, а их затворы с дополнительной шиной управления сбросом. Затворы дополнительных коммутационных транзисторов и дополнительных выходных транзисторов соединены с шинами управления устройства. 2 ил.

Устройство считывания сигналов с временной задержкой и накоплением (ВЗН) с многоэлементных ИК фотоприемников, выполненное на полупроводниковой подложке, содержащее n устройств ввода, где n-количество ВЗН каскадов, n устройств коммутации, (n+1) шин управления, (n+1) устройств выборок, каждое устройство ввода содержит первый транзистор, исток которого соединен с выходом фотодетектора, затвор с выходом усилителя, вход которого соединен с истоком первого транзистора, сток которого соединен с первой обкладкой интегрирующей емкости, вторая обкладка которой соединена с полупроводниковой подложкой, каждое устройство коммутации содержит первый, второй,..., (n+1) коммутационные транзисторы, истоки которых объединены и являются входом устройства коммутации, причем стоки i-х коммутационных транзисторов, где i от 1 до (n+1), из каждого устройства коммутации объединены, а затворы первого, второго,..., (n+1) коммутационных транзисторов j-го устройства коммутации соединены соответственно с 1+(j-1), 2+(j-1),..., n, (n+1), 1, 2,..., (j-1)-й шиной управления, где j от 1 до n, в каждом устройстве выборок первые емкости выборок, одна обкладка которой соединена с подложкой, другая с истоком первого выходного транзистора, сток которого соединен с выходом устройства, затвор первого выходного транзистора первого, второго,..., (n+1) устройств выборок соединен соответственно с (n+1), первой, второй,..., n-й шинами управления, отличающееся тем, что устройство содержит дополнительную шину управления сбросом, дополнительную шину напряжения сброса, в каждом устройстве ввода дополнительный транзистор сброса и повторитель напряжения, в каждом устройстве выборок n дополнительных коммутационных транзисторов, (n-1) дополнительных емкостей выборок, (n-1) дополнительных выходных транзисторов, причем исток дополнительного транзистора сброса устройства ввода соединен с дополнительной шиной напряжения сброса, его затвор с дополнительной шиной управления сбросом, а сток соединен в каждом устройстве ввода, со стоком первого транзистора и входом повторителя напряжения, выход которого соединен с входом соответствующего устройства коммутации, в каждом устройстве выборок истоки первого, второго,..., n-го дополнительных коммутационных транзисторов объединены, их стоки соединены соответственно с истоками первого выходного транзистора и истоками второго, третьего,..., n-го дополнительных выходных транзисторов, стоки которых соединены с выходом устройства, одна обкладка второй, третьей,..., n-й дополнительных емкостей выборок соединены с подложкой, другие соединены соответственно с истоками второго, третьего,..., n-го дополнительных выходных транзисторов, затворы которых соединены с затвором первого выходного транзистора, объединенные истоки дополнительных коммутационных транзисторов в первом, втором,..., (n+1) устройствах выборок соединены соответственно со стоками первого, второго,..., (n+1) коммутационных транзисторов первого устройства коммутации, затворы первого, второго,..., n-го дополнительных коммутационных транзисторов m-го устройства выборок соединены соответственно с m, (m+1),..., n, (n+1), 1, 2,..., (m-2) шинами управления, где m от 1 до (n+1).

| B.Kim | |||

| at al | |||

| Novel concept of TDI readout circuit for LWIR detector | |||

| SPIE | |||

| Движитель для самолета | 1925 |

|

SU4028A1 |

| УСТРОЙСТВО СЧИТЫВАНИЯ С ВРЕМЕННОЙ ЗАДЕРЖКОЙ И НАКОПЛЕНИЕМ СИГНАЛОВ С МНОГОЭЛЕМЕНТНЫХ ИК ФОТОПРИЕМНИКОВ | 2002 |

|

RU2236064C1 |

| УСТРОЙСТВО СЧИТЫВАНИЯ НА ПРИБОРАХ С ЗАРЯДОВОЙ СВЯЗЬЮ ДЛЯ ДВУМЕРНЫХ ПРИЕМНИКОВ ИЗОБРАЖЕНИЯ | 1993 |

|

RU2054753C1 |

| US 5517029 А, 14.05.1996 | |||

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

Авторы

Даты

2008-05-27—Публикация

2006-07-28—Подача