ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Настоящее изобретение, в целом, относится к системе мобильной связи и, в частности, к устройству и способу для кодирования/декодирования блочных кодов разреженного контроля четности (LDPC).

ОПИСАНИЕ ПРЕДШЕСТВУЮЩЕГО УРОВНЯ ТЕХНИКИ

Из-за бурного развития систем мобильной связи необходимо развивать технологию, допускающую передачу большого количества данных с приближением к пропускной способности проводной сети даже в беспроводной среде. Чтобы удовлетворить растущие потребности в высокоскоростной высокопроизводительной системе связи, допускающей обработку и передачу различных данных, таких как данные изображения и радиосвязи, вне ориентированной на голос службы, необходимо повышать эффективность передачи системы посредством использования надлежащей схемы кодирования канала, чтобы, тем самым, улучшить эксплуатационные характеристики всей системы. Однако система мобильной связи, вследствие своих характеристик, неизбежно порождает ошибки во время передачи данных, обусловленные шумами, помехами и замиранием согласно канальным условиям. Порождение ошибок служит причиной потери большого количества информационных данных.

Для того чтобы избежать потери информационных данных, обусловленной образованием ошибок, различные схемы контроля ошибок в настоящее время применяются и, отчасти, основаны на характеристиках канала, чтобы, тем самым, улучшить надежность системы мобильной связи. Наиболее типичная схема контроля ошибок использует коды с исправлением ошибок.

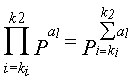

Со ссылкой на фиг.1 далее будет приведено описание структуры передатчика/приемника в обычной системе мобильной связи.

Фиг.1 - схема, иллюстрирующая структуру приемника/передатчика в обычной системе мобильной связи. Со ссылкой на фиг.1, передатчик 100 включает в себя кодировщик 111, модулятор 113 и радиочастотный (РЧ) процессор 115, а приемник 150 включает в себя РЧ-процессор 151, демодулятор 153 и декодер 155.

В передатчике 100, информационные данные 'u' передачи, если сформированы, поставляются в кодировщик 111. Кодировщик 111 формирует кодированный символ 'c' посредством кодирования информационных данных 'u' в зависимости от предопределенной схемы кодирования и выводит кодированный символ 'c' в модулятор 113. Модулятор 113 формирует символ 's' модуляции посредством модуляции кодированного символа 'c' в зависимости от предопределенной схемы модуляции и выводит символ 's' модуляции в РЧ-процессор 115. РЧ-процессор 115 подвергает РЧ-обработке символ 's' модуляции, выведенный из модулятора 113, и передает подвергнутый РЧ-обработке сигнал по эфиру через антенну ANT.

Сигнал, переданный по эфиру передатчиком 100 таким образом, принимается в приемнике 150 посредством антенны ANT, а сигнал, принятый посредством антенны, поставляется в РЧ-процессор 151. РЧ-процессор 151 подвергает РЧ-обработке принятый сигнал и выводит подвергнутый РЧ-обработке сигнал 'r' в демодулятор 153. Демодулятор 153 демодулирует подвергнутый РЧ-обработке сигнал 'r', выведенный из РЧ-процессора 151, с использованием схемы демодуляции, соответствующей схеме модуляции, применяемой в модуляторе 113, и выводит демодулированный сигнал 'x' в декодер 155. Декодер 155 декодирует демодулированный сигнал 'x', выведенный из демодулятора 153, с использованием схемы декодирования, соответствующей схеме кодирования, примененной в кодировщике 111, и выводит декодированный сигнал ' ' в качестве окончательно декодированных информационных данных.

' в качестве окончательно декодированных информационных данных.

Для того чтобы приемнику 150 без ошибок декодировать информационные данные 'u', переданные передатчиком 100, есть потребность в высокопроизводительном кодировщике и декодере. В частности, так как среда радиоканала должна приниматься во внимание из-за характеристик системы мобильной связи, ошибки, которые могут порождаться вследствие среды радиоканала, должны учитываться более серьезно.

Наиболее типичные коды исправления ошибок включают в себя турбокоды и коды разреженного контроля четности (LDPC).

Хорошо известно, что турбокоды являются превосходящими по производительности по отношению к сверточному коду, который традиционно используется для исправления ошибок во время высокоскоростной передачи данных. Турбокод является преимущественным в том, что он может эффективно исправлять ошибки, вызванные шумами, порожденными в канале передачи, тем самым повышая надежность передачи данных. Код LDPC может декодироваться с использованием итерационного алгоритма декодирования, основанного на алгоритме суммы-произведения в факторном графе. Так как декодер для кода LDPC использует основанный на алгоритме суммы-произведения итерационный алгоритм декодирования, он является менее сложным, чем декодер для турбокода. В дополнение, декодер для кода LDPC легок для реализации декодера параллельной обработки в сравнении с декодером для турбокода.

Теорема Шеннона кодирования канала иллюстрирует, что надежная связь возможна только при скорости передачи данных, не превышающей пропускную способность канала. Однако теорема Шеннона кодирования канала не предложила никакого детализированного способа кодирования/декодирования для поддержания скорости передачи данных вплоть до предела максимальной пропускной способности канала. Вообще, несмотря на то, что случайный код, обладающий очень большим размером блока, демонстрирует быстродействие, приближающееся к пределу пропускной способности канала по теореме Шеннона кодирования канала, когда используется способ декодирования MAP (с максимумом апостериорной вероятности) или ML (максимальной достоверностью), фактически невозможно реализовать способ декодирования вследствие его тяжелой вычислительной нагрузки.

Турбокод был предложен Берроу, Главиуксом и Титимаджимой в 1993 году и демонстрирует превосходное быстродействие, которое приближается к пределу пропускной способности канала по теореме Шеннона кодирования канала. Предложение турбокода дало начало активным исследованиям по итерационному декодированию и графическому представлению кодов, и коды LDPC, предложенные Галагером в 1962 году, были вновь выдвинуты на первый план в исследованиях. В факторном графе турбокода и кода LDPC существуют циклы, и хорошо известно, что итерационное кодирование в факторном графе кода LDPC, где существуют циклы, является квазиоптимальным. К тому же, было экспериментально доказано, что код LDPC обладает прекрасным быстродействием, благодаря итерационному декодированию. Код LDPC, известный как обладающий наивысшей производительностью, всегда демонстрирует рабочие характеристики, имеющие различие всего лишь в приблизительно 0,04 [дБ] с пределом пропускной способности канала по теореме Шеннона кодирования канала при частоте двоичных ошибок (BER) 10-5, с использованием размера блока 107. В дополнение, несмотря на то, что код LDPC, определенный на поле Галуа (GF) с q > 2, то есть GF(q), возрастает по сложности в последовательности операций его декодирования, он является гораздо лучшим по быстродействию по отношению к двоичному коду. Однако нет удовлетворительного теоретического описания успешного кодирования посредством алгоритма итерационного декодирования для кода LDPC, определенного на GF(q).

Код LDPC, предложенный Галагером, определен матрицей контроля четности, в которой большинство элементов имеют значение 0, и меньшинство элементов, кроме элементов, имеющих значение 0, имеют ненулевое значение, например, значение 1. В последующем описании будет принято, что ненулевым значением является значение 1.

Например, код LDPC (N, j, k) является линейным блочным кодом, имеющим длину блока N, и определен матрицей разреженного контроля четности, в которой каждый столбец содержит j элементов, имеющих значение 1, каждая строка содержит k элементов, имеющих значение 1, а все из элементов, кроме элементов, имеющих значение 1, имеют значение 0.

Код LDPC, в котором вес каждого столбца в матрице контроля четности установлен в 'j', а вес каждой строки в матрице контроля четности установлен в 'k', как описано выше, назван «регулярным кодом LDPC». Здесь «вес» относится к количеству элементов, обладающих ненулевым значением, среди элементов, составляющих матрицу контроля четности. В отличие от регулярного кода LDPC, код LDPC, в котором вес каждого столбца в матрице контроля четности и вес каждой строки в матрице контроля четности не зафиксированы, назван «нерегулярным кодом LDPC». Широко известно, что нерегулярный код LDPC является превосходным по быстродействию по отношению к регулярному коду LDPC. Однако в случае нерегулярного кода LDPC, так как вес каждого столбца и вес каждой строки в матрице контроля четности непостоянны, то есть являются нерегулярными, вес каждого столбца в матрице контроля четности и вес каждой строки в матрице контроля четности должны настраиваться надлежащим образом для того, чтобы гарантировать лучшее быстродействие.

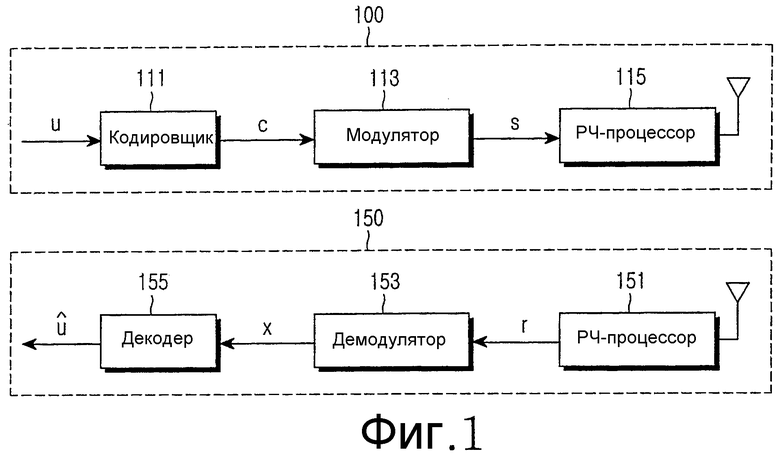

Со ссылкой на фиг.2 далее будет приведено описание матрицы контроля четности кода LDPC (8, 2, 4) в качестве примера кода LDPC (N, j, k).

Фиг.2 иллюстрирует матрицу контроля четности обычного кода LDPC (8, 2, 4). Со ссылкой на фиг.2 матрица H контроля четности кода LDPC (8, 2,4) составлена из 8 столбцов и 4 строк, при этом вес каждого столбца установлен в 2, а вес каждой строки установлен в 4. Так как вес каждого столбца и вес каждой строки в матрице контроля четности являются постоянными, как изложено выше, код LDPC (8, 2, 4), проиллюстрированный на фиг.2, становится регулярным кодом.

До сих пор, со ссылкой на фиг.2, описывалась матрица контроля четности кода LDPC (8, 2, 4). Затем, далее в материалах настоящей заявки, со ссылкой на фиг.3 будет описан факторный граф кода LDPC (8, 2, 4), описанного в связи с фиг.2.

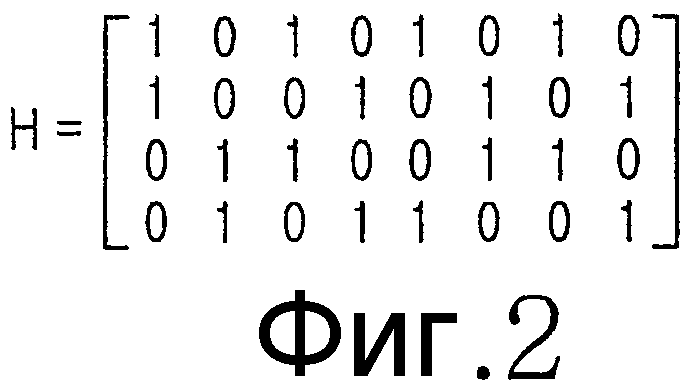

Фиг.3 - схема, иллюстрирующая факторный граф кода LDPC (8, 2, 4) по фиг.2. Со ссылкой на фиг.3 факторный граф кода LDPC (8, 2, 4) составлен из 8 узлов переменных x1 300, x2 302, x3 304, x4 306, x5 308, x6 310, x7 312 и x8 314 и 4-х узлов 316, 318, 320 и 322 контроля. Когда элемент, имеющий значение 1, то есть ненулевое значение, существует в точке, где пересекаются друг с другом j-й столбец и i-я строка матрицы контроля четности кода LDPC (8, 2, 4), создана ветвь между узлом xi переменной и j-м узлом контроля.

Так как матрица контроля четности кода LDPC имеет небольшой вес, как описано выше, возможно выполнять декодирование посредством итерационного декодирования даже в блочном коде, обладающем относительно большой длиной, который демонстрирует производительность, приближающуюся к пределу пропускной способности по теореме Шеннона кодирования канала, таком как турбокод, при постоянном росте длины блока блочного кода. Маккей и Нил доказали, что процесс итерационного декодирования кода LDPC с использованием схемы потоковой передачи приближается по производительности к процессу итерационного декодирования турбокода.

Для того чтобы сформировать высокопроизводительный код LDPC, должны быть удовлетворены следующие условия.

(1) Должны приниматься во внимание циклы в факторном графе кода LDPC.

Термин «цикл» относится к замкнутой цепи, сформированной ребрами, присоединяющими узлы переменных к узлам контроля в факторном графе кода LDPC, а длина цикла определена как количество ребер, составляющих замкнутую цепь. Длинный цикл означает, что количество ребер, присоединяющих узлы переменных к узлам контроля, составляющих замкнутую цепь в факторном графе кода LDPC, является большим. В противоположность, короткий цикл означает, что количество ребер, присоединяющих узлы переменных к узлам контроля, составляющих замкнутую цепь в факторном графе кода LDPC, является небольшим.

В то время как циклы в факторном графе кода LDPC становятся длиннее, относительный уровень производительности кода LDPC возрастает по следующим причинам. То есть когда формируются длинные циклы в факторном графе кода LDPC, возможно избежать ухудшения эксплуатационных показателей, таких как минимальный уровень ошибок, возникающих, когда слишком много циклов с короткой длиной существует в факторном графе кода LDPC.

(2) Должно приниматься во внимание эффективное кодирование кода LDPC.

Для кода LDPC является затруднительным подвергаться кодированию в реальном времени в сравнении со сверточным кодом или турбокодом вследствие высокой сложности его кодирования. Для того чтобы уменьшить сложность кодирования кода LDPC, был предложен код с повторным накоплением (RA). Однако код RA также имеет предел в снижении сложности кодирования кода LDPC. Поэтому эффективное кодирование кода LDPC должно приниматься во внимание.

(3) Должно приниматься во внимание распределение степеней в факторном графе кода LDPC.

Вообще, нерегулярный код LDPC является превосходным по производительности по отношению к регулярному LDPC, так как факторный граф нерегулярного кода LDPC содержит различные степени. Термин «степень» относится к количеству ребер, присоединенных к узлам переменных и узлам контроля, в факторном графе кода LDPC. Кроме того, фраза «распределение степеней» по факторному графу кода LDPC относится к отношению количества узлов, имеющих конкретную степень, к общему количеству узлов. Ричардсоном было доказано, что код LDPC, обладающий конкретным распределением степеней, является лучшим по производительности.

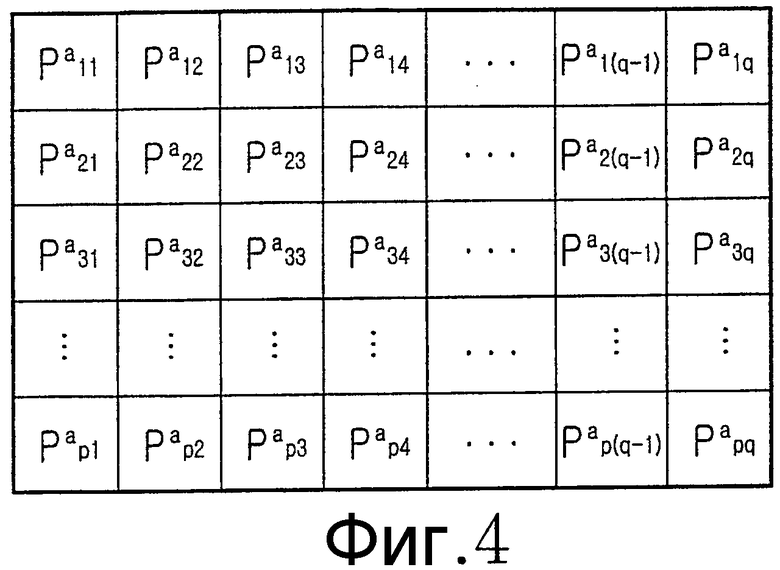

Со ссылкой на фиг.4, далее будет приведено описание матрицы контроля четности блочного кода LDPC.

Фиг.4 - таблица, иллюстрирующая матрицу контроля четности обычного блочного кода LDPC. До того, как дано описание по фиг.4, должно быть отмечено, что блочный код LDPC является новым кодом LDPC, для которого принималось во внимание не только эффективное кодирование, но также и эффективное хранение и улучшение производительности матрицы контроля четности, и блочный код LDPC является кодом LDPC, расширенным посредством обобщения структуры регулярного кода LDPC. Со ссылкой на фиг.4, матрица контроля четности блочного кода LDPC разделена на множество частичных блоков, и матрица перестановок внесена в каждый из частичных блоков. На фиг.4 'P' представляет матрицу перестановок, имеющую размер Ns ×Ns, а верхним индексом (или показателем) apq матрицы P перестановок является 0 ≤ apq ≤ Ns - 1, либо apq = ∞.

В дополнение, 'p' указывает, что соответствующая матрица перестановок расположена в p-й строке частичных блоков матрицы контроля четности, а 'q' указывает, что соответствующая матрица перестановок расположена в q-м столбце частичных блоков матрицы контроля четности. То есть  представляет матрицу перестановок, расположенную в частичном блоке, где пересекаются друг с другом p-я строка и q-й столбец матрицы контроля четности, составленной из множества частичных блоков. То есть 'p' и 'q' представляют, соответственно, количество строк и количество столбцов частичных блоков, соответствующих информационной части в матрице контроля четности.

представляет матрицу перестановок, расположенную в частичном блоке, где пересекаются друг с другом p-я строка и q-й столбец матрицы контроля четности, составленной из множества частичных блоков. То есть 'p' и 'q' представляют, соответственно, количество строк и количество столбцов частичных блоков, соответствующих информационной части в матрице контроля четности.

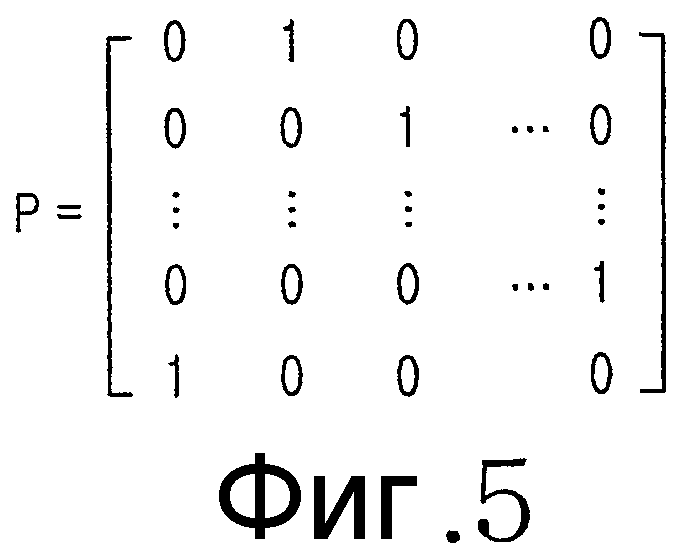

Далее со ссылкой на фиг.5 будет описана матрица перестановок.

Фиг.5 иллюстрирует матрицу P перестановок по фиг.4. Как проиллюстрировано на фиг.5, матрицей P перестановок является квадратная матрица, имеющая размер Ns ×Ns, и каждый из Ns столбцов, составляющих матрицу P перестановок, имеет вес 1, а каждая из Ns строк, составляющих матрицу P перестановок, также имеет вес 1. В материалах настоящей заявки, хотя размер матрицы P перестановок представлен как Ns ×Ns, он также будет выражаться как Ns, так как матрица P перестановок является квадратной матрицей.

На фиг.4 матрица P перестановок с верхним индексом apq =0, то есть матрица P0 перестановок представляет единичную матрицу  , а матрица P перестановок с верхним индексом apq =∞, то есть матрица P∞ перестановок, представляет нулевую матрицу. Здесь

, а матрица P перестановок с верхним индексом apq =∞, то есть матрица P∞ перестановок, представляет нулевую матрицу. Здесь  представляет единичную матрицу с размером Ns ×Ns.

представляет единичную матрицу с размером Ns ×Ns.

В полной матрице контроля четности блочного кода LDPC, проиллюстрированной на фиг.4, так как общим количеством строк является Ns ×p, а общим количеством столбцов является Ns ×q (для p≤q), когда полная матрица контроля четности кода LDPC имеет полный ранг, скорость кодирования может быть выражена в виде равенства (1), независимо от размера частичных блоков.

(1)

(1)

Если apq ≠∞ для p и q, матрицы перестановок, соответствующие частичным блокам, не являются нулевыми матрицами, а частичные блоки составляют регулярный код LDPC, в котором значением веса каждого столбца и значением веса каждой строки в каждой из матриц перестановок, соответствующих частичным блокам, являются p и q, соответственно. В материалах настоящей заявки каждая из матриц перестановок, соответствующих частичным блокам, будет упоминаться ссылкой как «частичная матрица».

Так как существуют (p - 1) независимых строк в полной матрице контроля четности, скорость кодирования является большей, чем скорость кодирования, вычисленная согласно равенству (1). В случае блочного кода LDPC, если весовая позиция первой строки каждой из частичных матриц, составляющих полную матрицу контроля четности, определена, могут быть определены весовые позиции оставшихся (Ns - 1) строк. Поэтому требуемый размер памяти снижен до 1/Ns, по сравнению со случаем, где веса выбраны нерегулярно, для хранения информации по полной матрице контроля четности.

Как описано выше, термин «цикл» относится к замкнутой цепи, сформированной ребрами, присоединяющими узлы переменных к узлам контроля в факторном графе кода LDPC, а длина цикла определена как количество ребер, составляющих замкнутую цепь. Длинный цикл означает, что количество ребер, присоединяющих узлы переменных к узлам контроля, составляющих замкнутую цепь в факторном графе кода LDPC, является большим. В то время как циклы в факторном графе кода LDPC становятся длиннее, относительный уровень производительности кода LDPC возрастает.

В противоположность, в то время как циклы в факторном графе кода LDPC становятся короче, способность исправления ошибок кода LDPC уменьшается, так как происходит ухудшение эксплуатационных характеристик, таких как минимальный уровень ошибок. То есть когда в факторном графе кода LDPC есть много циклов с короткой длиной, информация в конкретном узле, принадлежащем циклу с короткой длиной, начинающемуся из него, возвращается после небольшого количества итераций. В то время как количество итераций возрастает, информация возвращается в соответствующий узел чаще, так что информация не может корректно обновляться, тем самым, вызывая ухудшение в способности исправления ошибок кода LDPC.

Со ссылкой на фиг.6, далее будет приведено описание циклической структуры блочного кода LDPC.

Фиг.6 - схема, иллюстрирующая циклическую структуру блочного кода LDPC, по которой матрица контроля четности составлена из 4 частичных матриц. До того, как дано описание по фиг.6, должно быть отмечено, что блочный код LDPC является новым кодом LDPC, для которого были продуманы не только эффективное кодирование, но также и эффективное хранение и улучшение производительности матрицы контроля четности. Блочный код LDPC также является кодом LDPC, расширенным посредством обобщения структуры регулярного кода LDPC. Матрица контроля четности блочного кода LDPC, проиллюстрированного на фиг.6, составлена из 4-х частичных блоков, линия диагонали представляет позиции, где расположены элементы, имеющие значение 1, а части, отличные от расположенных по линии диагонали частей, представляют позиции, где расположены элементы, имеющие значение 0. В дополнение, 'P' является изображением такой же матрицы перестановок, как матрица перестановок, описанная в связи с фиг.5.

Для того чтобы проанализировать циклическую структуру блочного кода LDPC, проиллюстрированного на фиг.6, элемент, имеющий значение 1, расположенное в i-й строке частичной матрицы Pa, определен как опорный элемент, и элемент, имеющий значение 1, расположенное в i-й строке, будет упоминаться как «точка 0». В материалах настоящей заявки «частичная матрица» будет относиться к матрице, соответствующей частичному блоку. Точка 0 расположена в (I + a)-м столбце частичной матрицы Pa.

Элемент, имеющий значение 1 в частичной матрице Pb, расположенный в той же строке, что и точка 0, будет упоминаться как «точка 1». По той же причине, что и точка 0, точка 1 расположена в (i + b)-м столбце частичной матрицы Pb.

Далее, элемент, имеющий значением 1 в частичной матрице Pс, расположенный в том же самом столбце, что и точка 1, будет упоминаться как «точка 2». Так как частичная матрица Pc является матрицей, полученной сдвигом соответствующих столбцов единичной матрицы I вправо по остатку от деления Ns на c, точка 2 расположена в (i + b - c)-й строке частичной матрицы Pc.

В дополнение, элемент, имеющий значение 1 в частичной матрице Pd, расположенный в той же самой строке, что и точка 2, будет упоминаться как «точка 3». Точка 3 расположена в (i + b - c + d)-м столбце частичной матрицы Pd.

В заключение, элемент, имеющий значение 1 в частичной матрице Pa, расположенный в том же самом столбце, что и точка 3, будет упоминаться как «точка 4». Точка 4 расположена в (i + b - c + d - a)-й строке частичной матрицы Pa.

В циклической структуре кода LDPC, проиллюстрированной на фиг.6, если существует цикл с длиной 4, точка 0 и точка 4 расположены в одной и той же позиции. То есть соотношение между точкой 0 и точкой 4 определено равенством (2)

i ≅ i + b - c + d - a(mod Ns)или

i + a ≅ i + b - c + d(mod Ns) (2)

(2)

Равенство (2) может быть переписано в виде равенства (3)

a + c ≅ b + d(mod Ns)

(3)

(3)

Как результат, когда удовлетворено соотношение по равенству (3), сформирован цикл с длиной 4. Вообще, когда точка 0 и точка 4 изначально идентичны друг другу, задано соотношение i ≅ i + p(b - c + d - e)(mod Ns), и удовлетворено следующее соотношение, показанное в равенстве (4).

p(a - b + c - d)≅0(mod Ns).

(4)

(4)

Другими словами, если положительное целое число, обладающее минимальным значением среди положительных целых чисел, удовлетворяющих равенству (4) для заданных a, b, c и d, определено как 'p', цикл с длиной 4p становится циклом, имеющим минимальную длину в циклической структуре блочного кода LDPC, проиллюстрированной на фиг.6.

В итоге, как описано выше, для (a - b + c - d) ≠ 0, если удовлетворено gcd(Ns, a - b + c - d) = 1, то p = Ns. Здесь, gcd(Ns, a - b + c - d) является функцией для расчета «наибольшего общего делителя» целых чисел Ns и a - b + c - d. Поэтому цикл с длиной 4Ns становится циклом с минимальной длиной.

Метод Ричардсона-Урбанке будет использован в качестве технологии кодирования для блочного кода LDPC. Так как метод Ричардсона-Урбанке используется в качестве технологии кодирования, сложность кодирования может быть минимизирована, в то время как вид матрицы контроля четности становится подобным виду нижней треугольной матрицы.

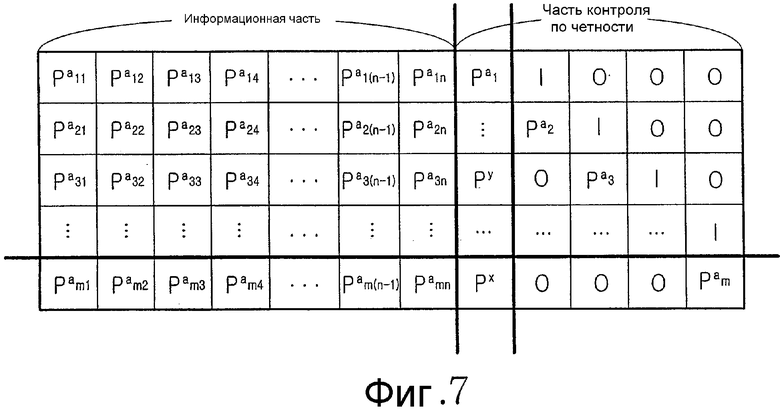

Со ссылкой на фиг.7, далее будет приведено описание матрицы контроля четности, имеющей вид, подобный виду полной нижней треугольной матрицы.

Фиг.7 иллюстрирует матрицу контроля четности, имеющую вид, подобный виду полной нижней треугольной матрицы. Матрица контроля четности, проиллюстрированная на фиг.7, отлична от матрицы контроля четности, имеющей вид полной нижней треугольной матрицы в представлении части контроля по четности. На фиг.7 верхним индексом (или показателем) apq матрицы P перестановок информационной части является 0 ≤ apq ≤ Ns - 1 или apq = ∞, как описано выше. Матрица P перестановок с верхним индексом apq = 0, то есть матрица P0 перестановок информационной части, представляет единичную матрицу  , а матрица P перестановок с верхним индексом apq =∞, то есть матрица P∞ перестановок, представляет нулевую матрицу. На фиг.7 'p' представляет количество строк частичных блоков, помещенных в информационную часть, а 'q' представляет количество столбцов частичных блоков, помещенных в часть контроля по четности. К тому же верхние индексы ap, x и y матриц P перестановок, помещенных в часть контроля по четности, представляют показатели матрицы P перестановок. Однако для удобства разъяснения, разные верхние индексы ap, x и y используются для проведения различия части контроля по четности от информационной части. То есть на фиг.7,

, а матрица P перестановок с верхним индексом apq =∞, то есть матрица P∞ перестановок, представляет нулевую матрицу. На фиг.7 'p' представляет количество строк частичных блоков, помещенных в информационную часть, а 'q' представляет количество столбцов частичных блоков, помещенных в часть контроля по четности. К тому же верхние индексы ap, x и y матриц P перестановок, помещенных в часть контроля по четности, представляют показатели матрицы P перестановок. Однако для удобства разъяснения, разные верхние индексы ap, x и y используются для проведения различия части контроля по четности от информационной части. То есть на фиг.7,  и

и  также являются матрицами перестановок, а верхние индексы с a1 по ap пронумерованы последовательно по отношению к частичным матрицам в диагональной части у части контроля по четности. В дополнение, Px и Py также являются матрицами перестановок, и, для удобства разъяснения, они проиндексированы разным способом, чтобы отличать часть контроля по четности от информационной части. Если предполагается, что длиной блока блочного кода LDPC, обладающего матрицей контроля четности, проиллюстрированной на фиг.7, является N, сложность кодирования блочного кода LDPC линейно возрастает относительно длины N блока (0(N)).

также являются матрицами перестановок, а верхние индексы с a1 по ap пронумерованы последовательно по отношению к частичным матрицам в диагональной части у части контроля по четности. В дополнение, Px и Py также являются матрицами перестановок, и, для удобства разъяснения, они проиндексированы разным способом, чтобы отличать часть контроля по четности от информационной части. Если предполагается, что длиной блока блочного кода LDPC, обладающего матрицей контроля четности, проиллюстрированной на фиг.7, является N, сложность кодирования блочного кода LDPC линейно возрастает относительно длины N блока (0(N)).

Наибольшая проблема кода LDPC, обладающего матрицей контроля четности по фиг.7, состоит в том, что если частичный блок определен как Ns, формируется Ns узлов контроля, чьими степенями всегда являются 1, в факторном графе блочного кода LDPC. Узлы контроля со степенью 1 не могут влиять на улучшение производительности на основании итерационного декодирования. Поэтому стандартный нерегулярный код LDPC, основанный на методике Ричардсона-Урбанке, не включает в себя узел контроля со степенью 1. Поэтому матрица контроля четности по фиг.7 будет предполагаться в качестве базисной матрицы контроля четности для того, чтобы конструировать матрицу контроля четности, из условия, чтобы она давала возможность эффективного кодирования, наряду с исключением узла контроля со степенью 1. В матрице контроля четности по фиг.7, составленной из частичных матриц, выбор частичной матрицы является очень важным фактором для улучшения производительности блочного кода LDPC, так что нахождение подходящего критерия выбора для частичной матрицы также становится очень важным фактором.

Далее будет приведено описание способа для конструирования матрицы контроля четности блочного кода LDPC на основании вышеприведенного блочного кода LDPC.

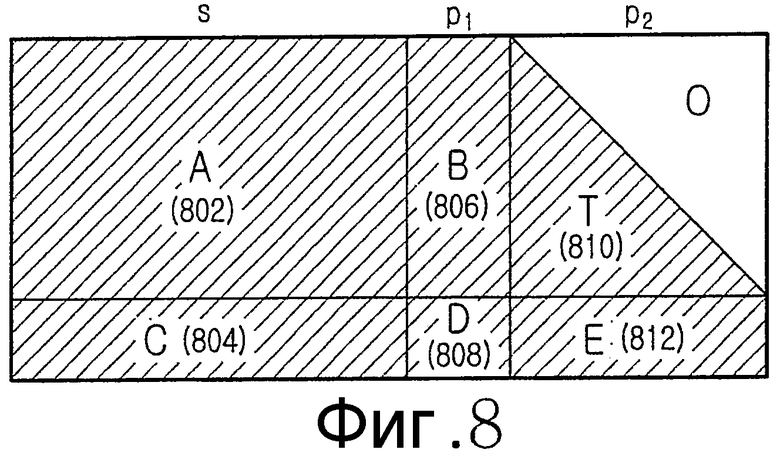

Для того чтобы облегчить способ конструирования матрицы контроля четности блочного кода LDPC и способа для кодирования блочного кода LDPC, матрица контроля четности, проиллюстрированная на фиг.7, предполагается сформированной 6 частичными матрицами, как проиллюстрировано на фиг.8.

Фиг.8 - схема, иллюстрирующая матрицу контроля четности по фиг.7, которая разделена на 6 частичных блоков. Со ссылкой на фиг.8, матрица контроля четности блочного кода LDPC, проиллюстрированная на фиг.7, разделена на информационную часть 's', первую часть p1 контроля по четности и вторую часть p2 контроля по четности. Информационная часть 's' представляет часть матрицы контроля четности, отображаемую в реальное информационное слово во время процесса кодирования блочного кода LDPC, аналогично информационной части, описанной в связи с фиг.7, но для удобства разъяснения, информационная часть 's' изображена другими ссылочными символами. Первая часть p1 контроля по четности и вторая часть p2 контроля по четности представляют части матрицы контроля четности, отображаемые в реальный контроль по четности во время процесса кодирования блочного кода LDPC, аналогично части контроля по четности, описанной в связи с фиг.7, и часть контроля по четности разделена на две части.

Частичные матрицы A и C соответствуют частичным блокам A(802) и C(804) информационной части 's', частичные матрицы B и D соответствуют частичным блокам B(806) и D(808) первой части p1 контроля по четности, а частичные матрицы T и E соответствуют частичным блокам T(810) и E(812) второй части p2 контроля по четности. Хотя матрица контроля четности разделена на 7 частичных блоков на фиг.8, должно быть отмечено, что '0' не является отдельным частичным блоком, и, так как частичная матрица Т, соответствующая частичному блоку T(810), имеет вид полной нижней треугольной формы, область, где нулевые матрицы скомпонованы на основе диагонали, представлена посредством '0'. Процесс по упрощению способа кодирования с использованием частичных матриц информационной части 's', первой части p1 контроля по четности и второй части p2 контроля по четности будет описан позже, со ссылкой на фиг.10.

Далее, частичные матрицы по фиг.8 будут описаны ниже в материалах настоящей заявки, со ссылкой на фиг.9.

Фиг.9 - схема, иллюстрирующая транспонированную матрицу частичной матрицы B, показанной на фиг.8, частичную матрицу E, частичную матрицу T и обратную матрицу частичной матрицы Т в матрице контроля четности по фиг.7.

Со ссылкой на фиг.9 частичная матрица BT представляет транспонированную матрицу частичной матрицы В, а частичная матрица T-1 представляет обратную матрицу частичной матрицы T.

представляет

представляет  . Матрицы перестановок, проиллюстрированные на фиг.9, например,

. Матрицы перестановок, проиллюстрированные на фиг.9, например,  , могут быть единичной матрицей. Как описано выше, если верхним индексом матрицы перестановок, то есть a1, является 0,

, могут быть единичной матрицей. Как описано выше, если верхним индексом матрицы перестановок, то есть a1, является 0,  будет единичной матрицей. К тому же, если верхний индекс матрицы перестановок, то есть a1, увеличивается на предопределенное значение, матрица перестановок циклически сдвигается на предопределенное значение, так что матрица

будет единичной матрицей. К тому же, если верхний индекс матрицы перестановок, то есть a1, увеличивается на предопределенное значение, матрица перестановок циклически сдвигается на предопределенное значение, так что матрица  перестановок будет единичной матрицей.

перестановок будет единичной матрицей.

Со ссылкой на фиг.10 далее будет приведено описание последовательности операций конструирования матрицы контроля четности блочного кода LDPC.

Фиг.10 - блок-схема последовательности операций способа, иллюстрирующая процедуру формирования матрицы контроля четности обычного блочного кода LDPC. До того как дано описание по фиг.10, должно быть отмечено, что, для того чтобы сформировать блочный код LDPC, должны быть определены размер кодовой комбинации и скорость кодирования блочного кода LDPC, который должен формироваться, а размер матрицы контроля четности должен устанавливаться согласно определенному размеру кодовой комбинации и скорости кодирования. Если размер кодовой комбинации блочного кода LDPC представлен посредством N, скорость кодирования представлена посредством R, размером матрицы контроля четности становится N(1 - R) × N. Фактически, процедура для формирования матрицы контроля четности блочного кода LDPC, проиллюстрированная на фиг.10, выполняется только однажды, так как матрица контроля четности первоначально формируется, чтобы быть подходящей для состояния системы связи, и после этого сформированная матрица контроля четности используется.

Со ссылкой на фиг.10 на этапе 1011 контроллер разделяет матрицу контроля четности с размером N(1 - R) × N всего на p × q блоков, в том числе, p блоков по горизонтальной оси и q блоков по вертикальной оси, а затем переходит на этап 1013. Так как каждый из блоков имеет размер Ns ×Ns, матрица контроля четности составлена из Ns ×p столбцов и Ns ×q строк. На этапе 1013 контроллер сортирует p×q блоков, выделенных из матрицы контроля четности, в информационную часть 's', первую часть p1 контроля по четности и вторую часть p2 контроля по четности, а затем переходит на этап 1015 и 1021.

На этапе 1015 контроллер разделяет информационную часть 's' на ненулевые блоки или ненулевые матрицы и нулевые блоки или нулевые матрицы согласно степени распределения для гарантирования хорошей производительности блочного кода LDPC, а затем переходит на этап 1017. Так как степень распределения для гарантирования хорошей производительности блочного кода LDPC была описана выше, ее подробное описание здесь будет опущено. На этапе 1017 контроллер определяет матрицы  перестановок, из условия, что минимальная длина блочного цикла должна быть максимизирована, как описано выше, в ненулевых матричных частях в блоках, имеющих низкую степень из числа блоков, определенных согласно распределению степеней, для гарантирования хорошей производительности блочного кода LDPC, а затем переходит на этап 1019. Матрицы

перестановок, из условия, что минимальная длина блочного цикла должна быть максимизирована, как описано выше, в ненулевых матричных частях в блоках, имеющих низкую степень из числа блоков, определенных согласно распределению степеней, для гарантирования хорошей производительности блочного кода LDPC, а затем переходит на этап 1019. Матрицы  перестановок должны определяться, принимая во внимание блочные циклы не только информационной части 's', но также и первой часть p1 контроля по четности и второй части p2 контроля по четности.

перестановок должны определяться, принимая во внимание блочные циклы не только информационной части 's', но также и первой часть p1 контроля по четности и второй части p2 контроля по четности.

На этапе 1019 контроллер случайным образом определяет матрицы  перестановок в ненулевых матричных частях в блоках, имеющих высокую степень, среди блоков, определенных согласно распределению степеней, для гарантирования хорошей производительности блочного кода LDPC, а затем заканчивает процедуру. Даже когда определены матрицы

перестановок в ненулевых матричных частях в блоках, имеющих высокую степень, среди блоков, определенных согласно распределению степеней, для гарантирования хорошей производительности блочного кода LDPC, а затем заканчивает процедуру. Даже когда определены матрицы  перестановок, которые должны применяться к ненулевым матричным частям в блоках, имеющих высокую степень, матрицы

перестановок, которые должны применяться к ненулевым матричным частям в блоках, имеющих высокую степень, матрицы  перестановок должны определяться так, что минимальная длина цикла блочного цикла максимизирована, а матрицы

перестановок должны определяться так, что минимальная длина цикла блочного цикла максимизирована, а матрицы  перестановок определены с учетом блочных циклов не только информационной части 's', но также первой части p1 контроля по четности и второй части p2 контроля по четности. Пример матриц

перестановок определены с учетом блочных циклов не только информационной части 's', но также первой части p1 контроля по четности и второй части p2 контроля по четности. Пример матриц  перестановок, скомпонованных в информационной части 's' матрицы контроля четности, проиллюстрирован на фиг.7.

перестановок, скомпонованных в информационной части 's' матрицы контроля четности, проиллюстрирован на фиг.7.

На этапе 1021 контроллер разделяет первую часть p1 контроля по четности и вторую часть p2 контроля по четности на 4 частичные матрицы B, T, D и E, а затем переходит на этап 1023. На этапе 1023 контроллер вводит ненулевые матрицы Py и  перестановок в два частичных блока из числа частичных блоков, составляющих частичную матрицу В, а затем переходит на этап 1025. Структура для ввода ненулевых матриц Py и

перестановок в два частичных блока из числа частичных блоков, составляющих частичную матрицу В, а затем переходит на этап 1025. Структура для ввода ненулевых матриц Py и  перестановок в два частичных блока из числа частичных блоков, составляющих частичную матрицу В, была описана со ссылкой на фиг.9.

перестановок в два частичных блока из числа частичных блоков, составляющих частичную матрицу В, была описана со ссылкой на фиг.9.

На этапе 1025 контроллер вводит единичные матрицы I в диагональные частичные блоки частичной матрицы Т, вводит конкретные матрицы  ,

,  ,...,

,...,  перестановок в (i, i + 1)-е частичные блоки под диагональными элементами частичной матрицы Т, а затем переходит на этап 1027. Структура для ввода единичных матриц I в диагональные частичные блоки частичной матрицы Т и ввода конкретных матриц

перестановок в (i, i + 1)-е частичные блоки под диагональными элементами частичной матрицы Т, а затем переходит на этап 1027. Структура для ввода единичных матриц I в диагональные частичные блоки частичной матрицы Т и ввода конкретных матриц  ,

,  ,...,

,...,  перестановок в (i, i + 1)-е частичные блоки под диагональными элементами частичной матрицы Т была описана со ссылкой на фиг.9.

перестановок в (i, i + 1)-е частичные блоки под диагональными элементами частичной матрицы Т была описана со ссылкой на фиг.9.

На этапе 1027 контроллер вводит частичную матрицу Px в частичную матрицу D, а затем переходит на этап 1029. На этапе 1029 контроллер вводит матрицу  перестановок только в последний частичный блок в частичной матрице E, а затем заканчивает процедуру. Структура для ввода 2-х матриц

перестановок только в последний частичный блок в частичной матрице E, а затем заканчивает процедуру. Структура для ввода 2-х матриц  перестановок только в последний частичный блок из числа частичных блоков, составляющих частичную матрицу Е, была описана со ссылкой на фиг.9.

перестановок только в последний частичный блок из числа частичных блоков, составляющих частичную матрицу Е, была описана со ссылкой на фиг.9.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Как описано выше, известно, что код LDPC, вместе с турбокодом, обладает высоким приростом производительности во время высокоскоростной передачи данных и эффективно исправляет ошибки, вызванные шумами, порожденными в канале передачи, способствуя повышению надежности передачи данных. Однако код LDPC невыгоден по скорости кодирования, так как код LDPC обладает относительно высокой скоростью кодирования, и он имеет ограничение в показателях скорости кодирования. Среди имеющихся в распоряжении в настоящее время кодов LDPC, относящиеся к большинству коды LDPC имеют скорость кодирования 1/2, и только относящиеся к меньшинству коды LDPC имеют скорость кодирования 1/3. Ограничение по скорости кодирования оказывает фатальное влияние на высокоскоростную, высокопроизводительную передачу данных. Конечно, несмотря на то, что степень распределения, представляющая лучшее быстродействие, может быть вычислена с использованием схемы роста плотности для того, чтобы реализовать относительно низкую скорость кодирования для кода LDPC, является затруднительным реализовать код LDPC, обладающий распределением степеней, представляющим наилучшую производительность, обусловленную различными ограничениями, такими как циклическая структура в факторном графе и аппаратная реализация.

Поэтому цель настоящего изобретения состоит в том, чтобы предоставить устройство и способ для кодирования/декодирования кода LDPC, обладающего переменной длиной блока, в системе мобильной связи.

Еще одна цель настоящего изобретения состоит в том, чтобы предоставить устройство и способ для кодирования/декодирования кода LDPC, обладающего переменной длиной блока, сложность кодирования которого минимизирована, в системе мобильной связи.

Согласно одному из аспектов настоящего изобретения, предоставлен способ кодирования блочного кода разреженного контроля четности (LDPC), обладающего переменной длиной. Способ включает в себя прием информационного слова; и кодирование информационного слова в блочный код LDPC на основании одной из первой матрицы контроля четности и второй матрицы контроля четности в зависимости от длины, которая должна применяться при формировании информационного слова в блочный код LDPC.

Согласно еще одному аспекту настоящего изобретения, предоставлено устройство для кодирования блочного кода разреженного контроля четности (LDPC), обладающего переменной длиной. Устройство включает в себя кодировщик для кодирования информационного слова в блочный код LDPC на основании первой матрицы контроля четности и второй матрицы контроля четности в зависимости от длины, которая должна применяться при формировании информационного слова в блочный код LDPC; и модулятор для модуляции блочного кода LDPC в символ модуляции с использованием схемы модуляции.

Согласно еще одному дополнительному аспекту настоящего изобретения, предоставлен способ декодирования блочного кода разреженного контроля четности (LDPC), обладающего переменной длиной. Способ включает в себя прием сигнала; и выбор одной из первой матрицы контроля четности и второй матрицы контроля четности согласно длине блочного кода LDPC, который должен декодироваться, и декодирование принятого сигнала согласно выбранной матрице контроля четности, тем самым детектирование блочного кода LDPC.

Согласно еще одному дополнительному аспекту настоящего изобретения, предоставлено устройство для декодирования блочного кода разреженного контроля четности (LDPC), обладающего переменной длиной. Устройство включает в себя приемник для приема сигнала; и декодер для выбора одной из первой матрицы контроля четности и второй матрицы контроля четности согласно длине блочного кода LDPC, который должен декодироваться, и декодирования принятого сигнала согласно выбранной матрице контроля четности, тем самым, детектирования блочного кода LDPC.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Вышеприведенные и другие цели, признаки и преимущества настоящего изобретения станут более очевидными из последующего подробного описания, при восприятии в соединении с сопроводительными чертежами, на которых:

фиг.1 - схема, иллюстрирующая структуру приемника/передатчика в обычной системе мобильной связи;

фиг.2 - схема, иллюстрирующая матрицу контроля четности обычного кода LDPC (8, 2, 4);

фиг.3 - схема, иллюстрирующая факторный граф кода LDPC (8, 2,4) по фиг.2;

фиг.4 - схема, иллюстрирующая матрицу контроля четности обычного блочного кода LDPC;

фиг.5 - схема, иллюстрирующая матрицу P перестановок по фиг.4;

фиг.6 - схема, иллюстрирующая циклическую структуру блочного кода LDPC, матрица контроля четности которого составлена из 4 частичных матриц;

фиг.7 - схема, иллюстрирующая матрицу контроля четности, имеющую вид, подобный виду полной нижней треугольной матрицы;

фиг.8 - схема, иллюстрирующая матрицу контроля четности по фиг.7, которая разделена на 6 частичных блоков;

фиг.9 - схема, иллюстрирующая транспонированную матрицу частичной матрицы В, показанной на фиг.8, частичную матрицу Е, частичную матрицу Т и обратную матрицу частичной матрицы Т;

фиг.10 - блок-схема последовательности операций способа, иллюстрирующая процедуру формирования матрицы контроля четности обычного блочного кода LDPC;

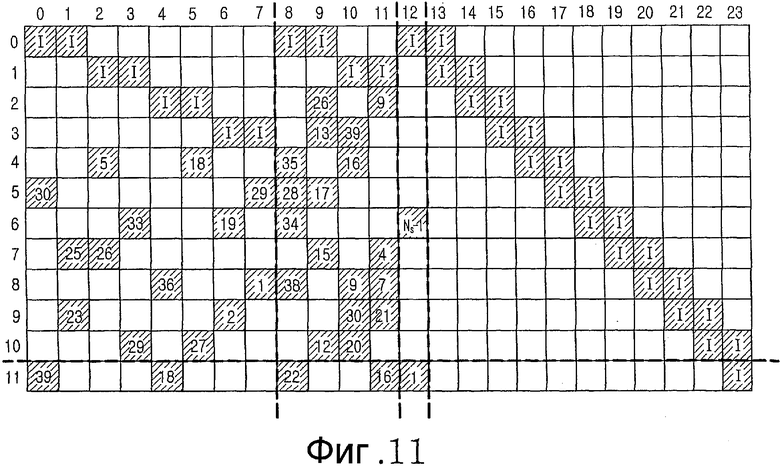

фиг.11 - схема, иллюстрирующая матрицу контроля четности блочного кода LDPC переменной длины согласно первому варианту осуществления настоящего изобретения;

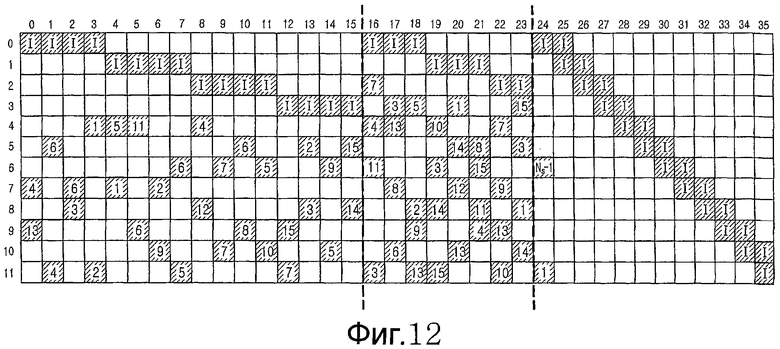

фиг.12 - схема, иллюстрирующая матрицу контроля четности блочного кода LDPC переменной длины согласно второму варианту осуществления настоящего изобретения;

фиг.13 - схема, иллюстрирующая матрицу контроля четности блочного кода LDPC переменной длины согласно третьему варианту осуществления настоящего изобретения;

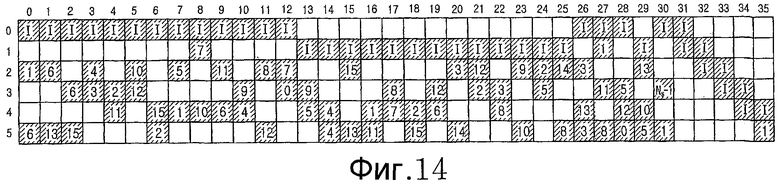

фиг.14 - схема, иллюстрирующая матрицу контроля четности блочного кода LDPC переменной длины согласно четвертому варианту осуществления настоящего изобретения;

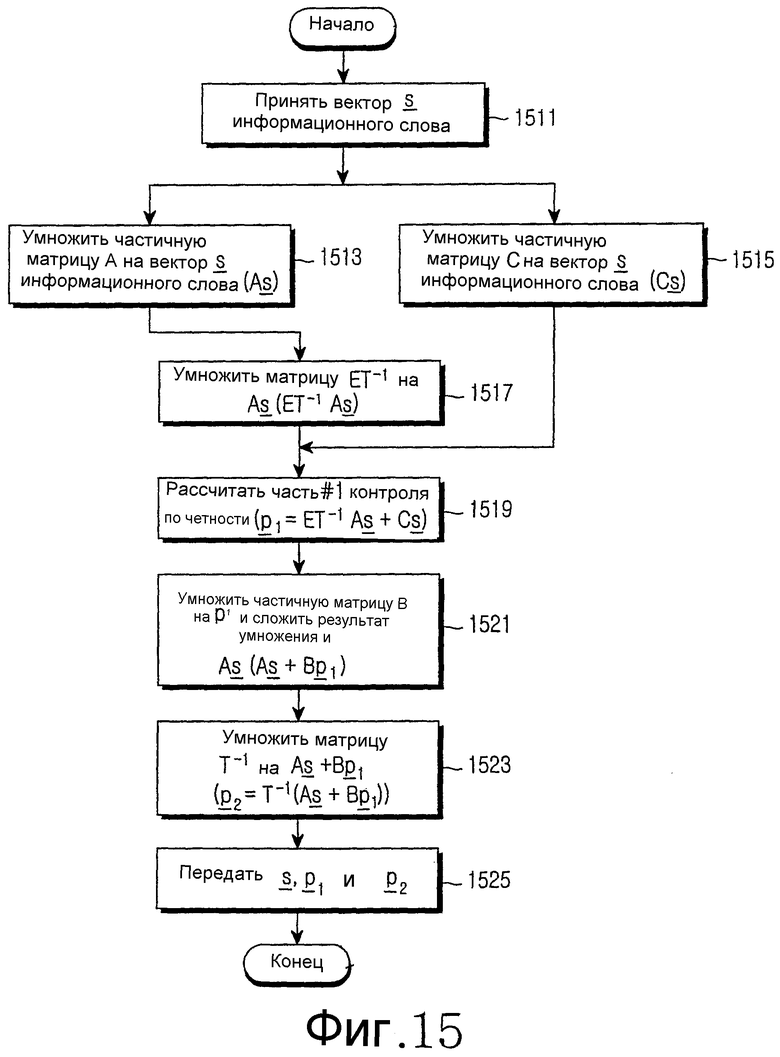

фиг.15 - блок-схема последовательности операций способа, иллюстрирующая последовательность операций кодирования блочного кода LDPC переменной длины согласно, с первого по четвертый, вариантам осуществления настоящего изобретения;

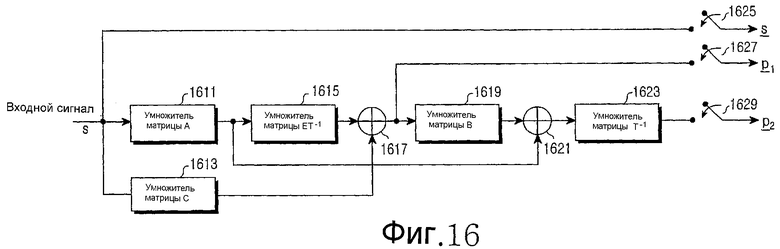

фиг.16 - структурная схема, иллюстрирующая внутреннюю структуру устройства для кодирования блочного кода LDPC переменной длины согласно вариантам осуществления настоящего изобретения; и

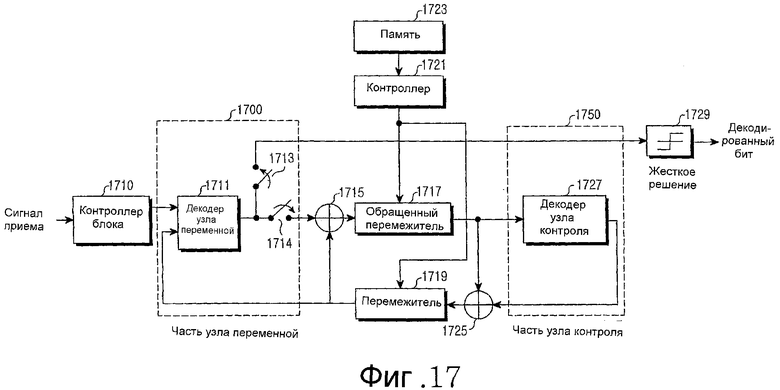

фиг.17 - структурная схема, иллюстрирующая внутреннюю структуру устройства для декодирования блочного кода LDPC переменной длины согласно вариантам осуществления настоящего изобретения.

ПОДРОБНОЕ ОПИСАНИЕ ПРЕДПОЧТИТЕЛЬНОГО ВАРИАНТА ОСУЩЕСТВЛЕНИЯ

Несколько предпочтительных вариантов осуществления настоящего изобретения далее будут подробно описаны со ссылкой на прилагаемые чертежи. В последующем описании, подробное описание известных функций и конфигураций, включенных в материалы настоящей заявки, опущено для краткости.

Настоящее изобретение предлагает устройство и способ для кодирования и декодирования блочного кода разреженного контроля четности (LDPC), обладающего переменной длиной (в дальнейшем упоминаемого как «блочный код LDPC переменной длины»). То есть настоящее изобретение предлагает устройство и способ для кодирования и декодирования блочного кода LDPC переменной длины, в котором длина минимального цикла в факторном графе блочного кода LDPC максимизирована, сложность кодирования блочного кода LDPC минимизирована, распределение степеней в факторном графе блочного кода LDPC имеет оптимальное значение 1, и поддерживаются переменные длины блоков. Хотя отдельно не проиллюстрировано в описании изобретения, устройство кодирования и декодирования для блочного кода LDPC переменной длины согласно настоящему изобретению может быть применено к передатчику/приемнику, описанным со ссылкой на фиг.1.

Система мобильной связи следующего поколения развилась в систему связи пакетного обслуживания, а система связи пакетного обслуживания, которая является системой для передачи пакетных данных пачки импульсов на множество мобильных станций, была спроектирована подходящей для высокопроизводительной передачи данных. Для того чтобы повысить пропускную способность, были предложены схема гибридного автоматического запроса на повторную передачу (HARQ) и схема адаптивной модуляции и кодирования (AMC). Так как схема HARQ и схема AMC поддерживают переменную скорость кодирования, есть необходимость в блочных кодах LDPC, имеющих различные длины блоков.

Конструкция блочного кода LDPC переменной длины, подобная схеме обычного кода LDPC, реализована посредством конструирования матрицы контроля четности. Однако в системе мобильной связи, для того чтобы предоставить блочный код LDPC переменной длины одним кодером-декодером, то есть для того, чтобы предусматривать блочные коды LDPC, обладающие различными длинами блоков, матрица контроля четности должна включать в себя матрицы контроля четности, допускающие представление блочных кодов LDPC, обладающих разными длинами блоков. Далее будет приведено описание матрицы контроля четности блочного кода LDPC, предусматривающей переменную длину блока.

Сначала блочный код LDPC, обладающий минимальной длиной, требуемой в системе, конструируется ради требуемой скорости кодирования. В матрице контроля четности, если Ns, указывающее размер частичной матрицы, возрастает, формируется блочный код LDPC, обладающий протяженной длиной блока. «Частичная матрица», как описано выше, относится к матрице перестановок, соответствующей каждому из частичных блоков, полученных разделением матрицы контроля четности на множество частичных блоков. При условии, что блочный код LDPC расширен таким образом, что блочный код LDPC с короткой длиной конструируется первым, затем сконструирован блочный код LDPC с протяженной длиной, так как увеличение в размере Ns частичной матрицы ведет к модификации циклической структуры, показатели матриц перестановок матрицы контроля четности выбираются из условия, что длина цикла должна быть максимизирована. Здесь, размер частичной матрицы, будучи Ns, означает, что частичная матрица является квадратной матрицей, имеющей размер Ns ×Ns и, для удобства описания, размер частичной матрицы представлен посредством Ns.

Например, при условии, что размером частичного блока базисного блочного кода LDPC является Ns =2, когда требуется расширить базисный блочный код LDPC с Ns =2 до блочного кода LDPC с Ns =4, который является в 2 раза более протяженным по длине, чем базисный блочный код LDPC, частичная матрица, показателем которой является 0, в матрице перестановок может выбирать значение 0 или 2, если его длина повышается с Ns =2 до Ns =4. Среди двух значений должно быть выбрано значение, допускающее максимизацию цикла. Подобным образом, в блочном коде LDPC с Ns =2, частичная матрица с показателем 1 может выбирать значение 1 или 3, если длина возрастает от Ns =2 до Ns =4.

Как описано выше, возможно конструировать блочный код LDPC, обладающий максимальной производительностью для каждой длины блока, посредством конструирования блочного кода LDPC с использованием базисного блочного кода LDPC, при возрастании значения Ns. В дополнение, один произвольный блочный код LDPC из числа блочных кодов LDPC, имеющих различные длины, может быть определен в качестве базисного блочного кода LDPC, способствуя повышению эффективности использования памяти. Далее будет приведено описание способа формирования матрицы контроля четности блочного кода LDPC переменной длины. Настоящее изобретение предлагает 4 типа матриц контроля четности для блочного кода LDPC переменной длины согласно скоростям кодирования, а скорости кодирования, принятые во внимание в настоящем изобретении, включают в себя 1/2, 2/3, 3/4 и 5/6.

Перед тем, как будет дано описание матриц контроля четности блочного кода LDPC переменной длины для скоростей кодирования 1/2, 2/3, 3/4 и 5/6, далее, со ссылкой на фиг.15, будет описана последовательность операций кодирования блочного кода LDPC переменной длины с использованием матрицы контроля четности, сконструированной в настоящем изобретении.

Фиг.15 - блок-схема последовательности операций способа, иллюстрирующая последовательность операций кодирования блочного кода LDPC переменной длины согласно первому варианту осуществления настоящего изобретения. Перед тем, как дано описание по фиг.15, предполагается, что матрица контроля четности для блочного кода LDPC переменного кода составлена из 6 частичных матриц, как описано со ссылкой на фиг.8.

Со ссылкой на фиг.15, на этапе 1511 контроллер (не показан) принимает вектор 's' информационного слова, который должен быть закодирован в блочный код LDPC переменной длины, а затем переходит на этапы 1513 и 1515. Здесь предполагается, что длиной вектора 's' информационного слова, принятого, чтобы кодироваться в блочный код LDPC, является k. На этапе 1513 контроллер осуществляет матричное умножение принятого вектора 's' информационного слова на частичную матрицу А матрицы контроля четности (As), а затем переходит на этап 1517. Здесь, так как количество элементов, имеющих значение 1, расположенных в частичной матрице А, является гораздо меньшим, чем количество элементов, имеющих значение 0, матричное умножение (As) вектора s и частичной матрицы А матрицы контроля четности может быть выполнено с относительно небольшим количеством операций сложения-умножения. В дополнение, в частичной матрице А, так как позиция, где расположены элементы, имеющие значение 1, может быть выражена в виде умножения показателей позиции ненулевого блока и матрицы перестановок блока, матричное умножение может быть выполнено очень простой операцией по сравнению с произвольной матрицей контроля четности. На этапе 1515 контроллер выполняет матричное умножение (Cs) над частичной матрицей С матрицы контроля четности и принятым вектором 's' информационного слова, а затем переходит на этап 1519.

На этапе 1517 контроллер выполняет матричное умножение (ET-1As) над матрицей результата (As) умножения вектора 's' информационного слова и частичной матрицы А матрицы контроля четности, и матрицей ET-1, а затем переходит на этап 1519. Здесь, так как количество элементов, имеющих значение 1, в матрице ET-1 очень мало, как описано выше, если задан показатель матрицы перестановок блока, матричное умножение может выполняться несложно. На этапе 1519 контроллер рассчитывает первый вектор P1 контроля по четности посредством сложения ET-lAs и Cs (P1 = ET-1As + Сs), а затем переходит на этап 1521. Здесь, операцией сложения является операция исключающего ИЛИ (XOR), а ее результат становится 0 для операции между битами, имеющими одинаковое значение, и 1 для операции между битами, имеющими разные значения. То есть последовательностью операций вплоть до этапа 1519 является последовательность операций для расчета первого вектора P1 контроля по четности.

На этапе 1521 контроллер умножает частичную матрицу В матрицы контроля четности на первый вектор P1 контроля по четности, (BP1), прибавляет результат (BP1) умножения к As (As + BP1), а затем переходит на этап 1523. Если заданы вектор 's' информационного слова и первый вектор P1 контроля по четности, они могут быть умножены на обратную матрицу T-1 частичной матрицы T матрицы контроля четности для расчета второго вектора P2 контроля по четности. Поэтому на этапе 1523 контроллер умножает результат (As + BP1) расчета этапа 1521 на обратную матрицу T-1 частичной матрицы Т, чтобы рассчитать второй вектор P2 контроля по четности (P2 = T-1(As + BP1)), а затем переходит на этап 1525. Как описано выше, если задан вектор 's' информационного слова блочного кода LDPC, который должен кодироваться, могут быть рассчитаны первый вектор P1 контроля по четности и второй вектор P2 контроля по четности и, как результат, могут быть получены все векторы кодовых комбинаций. На этапе 1525 контроллер формирует вектор 'c' кодовой комбинации с использованием вектора 's' информационного слова, первого вектора P1 контроля по четности и второго вектора P2 контроля по четности и передает сформированный вектор 'c' кодовой комбинации.

Затем, со ссылкой на фиг.16, будет приведено описание внутренней структуры устройства для кодирования блочного кода

LDPC переменной длины согласно вариантам осуществления настоящего изобретения.

Фиг.16 - структурная схема, иллюстрирующая внутреннее строение устройства для кодирования блочного кода LDPC переменной длины согласно вариантам осуществления настоящего изобретения. Со ссылкой на фиг.16, устройство для кодирования блочного кода LDPC переменной длины включает в себя умножитель 1611 матрицы А, умножитель 1613 матрицы С, умножитель 1615 матрицы ET-1, сумматор 1617, умножитель 1619 матрицы В, сумматор 1621 и умножитель 1623 матрицы T-1 и переключатели 1625, 1627 и 1629.

Если принимается входной сигнал, например, вектор 's' информационного слова с длиной k, который должен быть закодирован в блочный код LDPC переменной длины, принятый вектор 's' информационного слова с длиной k подается на переключатель 1625, умножитель 1611 матрицы А и умножитель 1613 матрицы С. Умножитель 1611 матрицы А умножает вектор 's' информационного слова на частичную матрицу А полной матрицы контроля четности и выдает результат умножения в умножитель 1615 матрицы ET-1 и сумматор 1621. Умножитель 1613 матрицы С умножает вектор 's' информационного слова на частичную матрицу С полной матрицы контроля четности и выдает результат умножения в сумматор 1617. Умножитель 1615 матрицы ET-1 умножает сигнал, выведенный из умножителя 1611 матрицы А, на частичную матрицу ET-1 полной матрицы контроля четности и выдает результат умножения в сумматор 1617.

Сумматор 1617 прибавляет сигнал, выведенный из вычислителя 1615 матрицы ET-1, к сигналу, выведенному из умножителя 1613 матрицы С, и выдает результат сложения на умножитель 1619 матрицы В и переключатель 1627. Здесь, сумматор 1617 выполняет операцию XOR на побитовой основе. Например, если вектор с длиной 3 x = (x1, x2, x3) и вектор с длиной 3 y = (y1, y2,y3) вводятся в сумматор 1617, сумматор 1617 выдает вектор с длиной 3 z = (x1⊕y1, x2⊕y2, x3⊕y3), выполняя операцию XOR над вектором с длиной 3 x = (xl, x2, x3) и вектором с длиной 3 y = (y1, y2, y3). Здесь, операция ⊕ представляет операцию XOR, результат которой становится 0 для операции между битами, имеющими одинаковое значение, и 1 для операции между битами, имеющими разные значения. Сигнал, выведенный из сумматора 1617, становится первым вектором P1 контроля по четности.

Умножитель 1619 матрицы В умножает сигнал, выведенный из сумматора 1617, то есть первый вектор P1 контроля по четности, на частичную матрицу В полной матрицы контроля четности и выдает результат умножения в сумматор 1621. Сумматор 1621 прибавляет сигнал, выведенный из умножителя 1619 матрицы В, к сигналу, выведенному из умножителя 1611 матрицы А, и выдает результат сложения в умножитель 1623 матрицы T-1. Сумматор 1621, подобный сумматору 1617, выполняет операцию XOR над сигналом, выведенным из умножителя 1619 матрицы В, и сигналом, выведенным из умножителя 1611 матрицы А, и выдает результат операции XOR в умножитель 1623 матрицы T-1.

Умножитель 1623 матрицы T-1 умножает сигнал, выведенный из сумматора 1621, на обратную матрицу T-1 частичной матрицы Т полной матрицы контроля четности и выдает результат умножения на переключатель 1629. Выходной сигнал умножителя 1623 матрицы T-1 становится вторым вектором P2 контроля по четности. Каждый из переключателей 1625, 1627 и 1629 включен только во время своей передачи для передачи своего ассоциативно связанного сигнала. Переключатель 1625 включается на время передачи вектора 's' информационного слова, переключатель 1627 включается на время передачи первого вектора P1 контроля по четности, а переключатель 1629 включается на время передачи второго вектора P2 контроля по четности.

Так как варианты осуществления настоящего изобретения должны быть пригодны для формирования блочного кода LDPC переменной длины, каждая из матриц, используемых в устройстве кодирования по фиг.16 для блочного кода LDPC переменной длины, изменяется каждый раз, когда изменяется матрица контроля четности блочного кода LDPC переменной длины, как будет описано со ссылкой на фиг.17. Поэтому, хотя не проиллюстрировано отдельно на фиг.16, контроллер модифицирует матрицы с использованием устройства кодирования для блочного кода LDPC переменной длины соответственно тому, как изменяется матрица контроля четности блочного кода LDPC переменной длины.

Было приведено описание способа для формирования блочного кода LDPC переменной длины, принимающего во внимание эффективное кодирование. Как описано выше, блочный код LDPC переменной длины, вследствие его структурной характеристики, является превосходным в показателях эффективности использования памяти для хранения относящейся к матрице контроля четности информации и дает возможность эффективного кодирования посредством надлежащего выбора частичных матриц матрицы контроля четности. Однако, поскольку матрица контроля четности формируется на поблочной основе, беспорядочность снижается, а уменьшение в беспорядочности может послужить причиной ухудшения эксплуатационных характеристик блочного кода LDPC. То есть, так как нерегулярный блочный код LDPC является превосходящим по производительности по отношению к регулярному блочному коду LDPC, как описано выше, очень важно надлежащим образом выбирать частичные матрицы из полной матрицы контроля четности в последовательности операций конструирования блочного кода LDPC.

Со ссылкой на фиг.11, далее будет приведено описание детализированного способа для формирования блочного кода LDPC переменной длины для скорости кодирования 1/2.

Фиг.11 - схема, иллюстрирующая матрицу контроля четности блочного кода LDPC переменной длины согласно первому варианту осуществления настоящего изобретения. До того, как дано описание по фиг.11, должно быть отмечено, что первый вариант осуществления настоящего изобретения предлагает матрицу контроля четности блочного кода LDPC переменной длины для скорости кодирования 1/2. Со ссылкой на фиг.11, если принято, что возможным размером Ns частичных матриц являются 4, 8, 12, 16, 20, 24, 28, 32, 36 и 40, возможно формировать блочный код LDPC, имеющий длину 96, 192, 288, 384, 480, 576, 672, 768, 864 и 960 с использованием матрицы контроля четности, проиллюстрированной на фиг.11. Значение, записанное в каждом из частичных блоков, то есть частичных матриц, проиллюстрированных на фиг.11, представляет значение показателя соответствующей матрицы перестановок. Здесь, матрица контроля четности блочного кода LDPC переменной длины составлена из множества частичных блоков, и частичные матрицы, по отдельности соответствующие частичным блокам, составляют матрицу перестановок. Например, если матрица контроля четности блочного кода LDPC переменной длины составлена из p × q частичных блоков, то есть, если количеством строк частичных блоков в матрице контроля четности для блочного кода LDPC переменной длины является 'p', а количеством столбцов частичных блоков в матрице контроля четности для блочного кода LDPC переменной длины является 'q', матрицы перестановок, составляющие матрицу контроля четности блочного кода LDPC переменной длины, могут быть выражены как  , а верхним индексом apq матрицы Р перестановок является 0 ≤ apq ≤ Ns - 1, либо apq = ∞. То есть матрица

, а верхним индексом apq матрицы Р перестановок является 0 ≤ apq ≤ Ns - 1, либо apq = ∞. То есть матрица  перестановок представляет матрицу перестановок, расположенную в частичном блоке, где пересекаются друг с другом p-я строка и q-й столбец матрицы контроля четности блочного кода LDPC, составленной из множества частичных блоков. Поэтому, значение показателя матрицы перестановок, проиллюстрированной на фиг.11, задано как apq, и, посредством выполнения операции взятия остатка от деления на Ns (где Ns соответствует размеру частичной матрицы) над значением показателя матрицы перестановок, возможно рассчитывать значение показателя матрицы перестановок матрицы контроля четности для блочного кода LDPC переменной длины, имеющего значение Ns. Если результирующим значением, полученным посредством выполнения операции взятия остатка от деления на Ns над показателем матрицы перестановок, является 0, соответствующая матрица перестановок становится единичной матрицей.

перестановок представляет матрицу перестановок, расположенную в частичном блоке, где пересекаются друг с другом p-я строка и q-й столбец матрицы контроля четности блочного кода LDPC, составленной из множества частичных блоков. Поэтому, значение показателя матрицы перестановок, проиллюстрированной на фиг.11, задано как apq, и, посредством выполнения операции взятия остатка от деления на Ns (где Ns соответствует размеру частичной матрицы) над значением показателя матрицы перестановок, возможно рассчитывать значение показателя матрицы перестановок матрицы контроля четности для блочного кода LDPC переменной длины, имеющего значение Ns. Если результирующим значением, полученным посредством выполнения операции взятия остатка от деления на Ns над показателем матрицы перестановок, является 0, соответствующая матрица перестановок становится единичной матрицей.

Ради подробного описания настоящего изобретения будет дано определение следующих параметров.

Матрица контроля четности блочного кода LDPC переменной длины, проиллюстрированная на фиг.11, упоминается как «материнская матрица», количество ненулевых матриц перестановок из числа частичных матриц, то есть матриц перестановок, составляющих материнскую матрицу, определено как L, показатели L ненулевых матриц перестановок из числа матриц перестановок, составляющих материнскую матрицу, представлены посредством a1, a2, ..., aL, а размер матриц перестановок, составляющих материнскую матрицу, предполагается являющимся Ns. Так как количеством ненулевых матриц перестановок из числа матриц перестановок, составляющих материнскую матрицу, является L, показателем первой матрицы перестановок становится a1, показателем второй матрицы перестановок становится a2, и, таким образом, показателем последней матрицы перестановок становится aL.

В отличие от материнской матрицы, матрица контроля четности, которая должна быть сформирована вновь, упоминается как «дочерняя матрица», количество ненулевых матриц перестановок из числа частичных матриц, то есть матриц перестановок, составляющих дочернюю матрицу, определено как L, размер матриц перестановок, составляющих дочернюю матрицу, определен как Ns', а показатели матриц перестановок, составляющих дочернюю матрицу, представлены посредством a1', a2', ..., aL'. Так как количеством ненулевых матриц перестановок из числа матриц перестановок, составляющих дочернюю матрицу, является L, показателем первой матрицы перестановок становится a1', показателем второй матрицы перестановок становится a2', и, таким образом, показателем последней матрицы перестановок становится aL'.

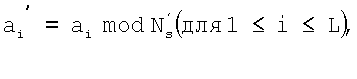

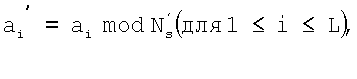

С использованием равенства (5), приведенного ниже, возможно формировать дочернюю матрицу, имеющую переменную длину блока, посредством выбора размера Ns' матриц перестановок, составляющих дочернюю матрицу, которая должна быть сформирована из одной материнской матрицы.

ai' = ai mod Ns' (для 1 ≤ i ≤ L) (5)

(5)

Затем, со ссылкой на фиг.12, будет приведено описание детализированного способа для формирования блочного кода LDPC переменной длины для скорости кодирования 2/3.

Фиг.12 - схема, иллюстрирующая матрицу контроля четности блочного кода LDPC переменной длины согласно второму варианту осуществления настоящего изобретения. До того, как дано описание по фиг.12, должно быть отмечено, что второй вариант осуществления настоящего изобретения предлагает матрицу контроля четности блочного кода LDPC переменной длины для скорости кодирования 2/3. Со ссылкой на фиг.12, если принято, что возможным размером Ns частичных матриц являются 8 и 16, возможно формировать блочный код LDPC, имеющий длину 288 и 576, с использованием матрицы контроля четности, проиллюстрированной на фиг.12. Значение, записанное в каждом из частичных блоков, то есть частичных матриц, проиллюстрированных на фиг.12, представляет значение показателя соответствующей матрицы перестановок. Поэтому посредством выполнения операции взятия остатка от деления на Ns (Ns соответствует размеру частичной матрицы) над значением показателя матрицы перестановок, возможно рассчитывать значение показателя матрицы перестановок матрицы контроля четности для блочного кода LDPC, имеющего значение Ns. Если результирующим значением, полученным посредством выполнения операции взятия остатка от деления на Ns над показателем матрицы перестановок, является 0, соответствующая матрица перестановок становится единичной матрицей.

Затем, со ссылкой на фиг.13, будет приведено описание детализированного способа для формирования блочного кода LDPC переменной длины для скорости кодирования 3/4.

Фиг.13 - схема, иллюстрирующая матрицу контроля четности блочного кода LDPC переменной длины согласно третьему варианту осуществления настоящего изобретения. До того, как дано описание по фиг.13, должно быть отмечено, что третий вариант осуществления настоящего изобретения предлагает матрицу контроля четности блочного кода LDPC переменной длины для скорости кодирования 3/4. Со ссылкой на фиг.13, если принято, что возможным размером Ns частичных матриц являются 3, 6, 9, 12, 15 и 18, возможно формировать блочный код LDPC, имеющий переменную длину 96, 192, 288, 384, 480 и 576, с использованием матрицы контроля четности, проиллюстрированной на фиг.13. Значение, записанное в каждом из частичных блоков, то есть частичных матриц, проиллюстрированных на фиг.13, представляет значение показателя соответствующей матрицы перестановок. Поэтому посредством выполнения операции взятия остатка от деления на Ns (Ns соответствует размеру частичной матрицы) над значением показателя матрицы перестановок, возможно рассчитывать значение показателя матрицы перестановок матрицы контроля четности для блочного кода LDPC, имеющего значение Ns. Если результирующим значением, полученным посредством выполнения операции взятия остатка от деления на Ns над показателем матрицы перестановок, является 0, соответствующая матрица перестановок становится единичной матрицей.

Затем, со ссылкой на фиг.14, будет приведено описание детализированного способа формирования блочного кода LDPC переменной длины для скорости кодирования 5/6.

Фиг.14 - схема, иллюстрирующая матрицу контроля четности блочного кода LDPC переменной длины согласно четвертому варианту осуществления настоящего изобретения. До того, как дано описание по фиг.14, должно быть отмечено, что четвертый вариант осуществления настоящего изобретения предлагает матрицу контроля четности блочного кода LDPC переменной длины для скорости кодирования 5/6. Со ссылкой на фиг.14, если принято, что возможным размером Ns частичных матриц являются 8 и 16, возможно формировать блочный код LDPC, имеющий длину 288 и 576, с использованием матрицы контроля четности, проиллюстрированной на фиг.14. Значение, записанное в каждом из частичных блоков, то есть частичных матриц, проиллюстрированных на фиг.14, представляет значение показателя соответствующей матрицы перестановок. Поэтому посредством выполнения операции взятия остатка от деления на Ns (Ns соответствует размеру частичной матрицы) над значением показателя матрицы перестановок, возможно рассчитывать значение показателя матрицы перестановок матрицы контроля четности для блочного кода LDPC, имеющего значение Ns. Если результирующим значением, полученным посредством выполнения операции взятия остатка от деления на Ns над показателем матрицы перестановок, является 0, соответствующая матрица перестановок становится единичной матрицей.

Все коды семейства LDPC могут быть декодированы в факторном графе с использованием алгоритма подпроизведения. Схема декодирования кода LDPC может быть грубо разделена на схему двунаправленной передачи и схему потоковой передачи. Когда операция декодирования выполняется с использованием схемы двунаправленной передачи, каждый узел контроля имеет узловой процессор, с повышением сложности декодирования прямо пропорционально количеству узлов контроля. Однако, так как все из узлов контроля обновляются одновременно, скорость декодирования необыкновенно возрастает.

В отличие от этого, схема потоковой передачи содержит одиночный узловой процессор, и узловой процессор обновляет информацию, проходящую через все из узлов в факторном графе. Поэтому схема потоковой передачи является более низкой по сложности декодирования, но увеличение в размере матрицы контроля четности, то есть увеличение в количестве узлов, вызывает снижение в скорости декодирования. Однако, если матрица контроля четности формируется поблочно, аналогично блочному коду LDPC переменной длины, имеющему различные длины блоков, согласно скоростям кодирования, предложенным в настоящем изобретении, то используется количество узловых процессоров, равное количеству блоков, составляющих матрицу контроля четности. В этом случае, возможно реализовать декодер, который является меньшим, чем при схеме двунаправленной передачи, в сложности декодирования, и большим, чем при схеме потоковой передачи, в скорости декодирования.

Затем, со ссылкой на фиг.17, будет приведено описание внутреннего строения устройства декодирования для декодирования блочного кода LDPC переменной длины с использованием матрицы контроля четности согласно варианту осуществления настоящего изобретения.

Фиг.17 - структурная схема, иллюстрирующая внутреннее строение устройства для декодирования блочного кода LDPC переменной длины согласно вариантам осуществления настоящего изобретения. Со ссылкой на фиг.17, устройство декодирования для декодирования блочного кода LDPC переменной длины включает в себя контроллер 1710 блока, часть 1700 узла переменной, сумматор 1715, обращенный перемежитель 1717, перемежитель 1719, контроллер 1721, память 1723, сумматор 1725, часть 1750 узла контроля и узел 1729 жесткого решения. Часть 1700 узла переменной включает в себя декодер 1711 узла переменной и переключатели 1713 и 1714, а часть 1750 узла контроля включает в себя декодер 1727 узла контроля.

Сигнал, принятый по радиоканалу, вводится в контроллер 1710 блока. Контроллер 1710 блока определяет размер блока из принятого сигнала. Если есть часть информационного слова, подвергнутая выкалыванию в устройстве кодирования, соответствующем устройству декодирования, контроллер 1710 блока вставляет '0' в подвергнутую выкалыванию часть информационного слова, чтобы откорректировать полный размер блока, и выводит результирующий сигнал в декодер 1711 узла переменной.

Декодер 1711 узла переменной рассчитывает значения вероятности сигнала, выведенного из контроллера 1710 блока, обновляет рассчитанные значения вероятности и выводит обновленные значения вероятности на переключатели 1713 и 1714. Декодер 1711 узла переменной соединяет узлы переменных согласно матрице контроля четности, предварительно заданной в устройстве декодирования для нерегулярного блочного кода LDPC, и выполняет операцию обновления над таким количеством входных и выходных значений, как количество 1s, присоединенное к узлам переменных. Количество 1s, присоединенное к узлам переменных, равно весу каждого из столбцов, составляющих матрицу контроля четности. Внутренняя работа декодера 1711 узла переменной различается согласно весу каждого столбца, составляющего матрицу контроля четности. Кроме случаев, когда включен переключатель 1713, переключатель 1714 включен для вывода выходного сигнала декодера 1711 узла переменной в сумматор 1715.

Сумматор 1715 принимает сигнал, выведенный из декодера 1711 узла переменной, и выходной сигнал перемежителя 1719 в предыдущей последовательности операций итерационного декодирования, вычитает выходной сигнал перемежителя 1719 в предыдущей последовательности операций итерационного декодирования из выходного сигнала декодера 1711 узла переменной и выводит результат вычитания в обращенный перемежитель 1717. Если последовательность операций декодирования является начальной последовательностью операций декодирования, должно быть принято во внимание, что выходным сигналом перемежителя 1719 является 0.

Обращенный перемежитель 1717 подвергает обращенному перемежению сигнал, выведенный из сумматора 1715, согласно предопределенной схеме перемежения и выводит подвергнутый обращенному перемежению сигнал в сумматор 1725 и декодер 1727 узла контроля. Обращенный перемежитель 1717 обладает внутренним строением, соответствующим матрице контроля четности, так как выходное значение для входного значения перемежителя 1719, соответствующего обращенному перемежителю 1717, является различным согласно позициям элементов, имеющих значение 1 в матрице контроля четности.

Сумматор 1725 принимает выходной сигнал декодера 1711 узла контроля в предыдущей последовательности операций итерационного декодирования и выходной сигнал обращенного перемежителя 1717, вычитает выходной сигнал обращенного перемежителя 1717 из выходного сигнала декодера 1727 узла контроля в предыдущей последовательности операций итерационного декодирования и выводит результат вычитания в перемежитель 1719. Декодер 1727 узла контроля соединяет узлы контроля согласно матрице контроля четности, предварительно заданной в устройстве декодирования для блочного кода LDPC, и выполняет операцию обновления над некоторым количеством входных значений и выводит значения, равные количеству 1s, присоединенному к узлам контроля. Количество 1s, присоединенное к узлам контроля, равно весу каждой из строк, составляющих матрицу контроля четности. Поэтому внутренняя работа декодера 1727 узла контроля различается согласно весу каждой из строк, составляющих матрицу контроля четности.

Перемежитель 1719, под управлением контроллера 1721, перемежает сигнал, выведенный из сумматора 1725, согласно предопределенной схеме перемежения, и выводит перемеженный сигнал в сумматор 1715 и декодер 1711 узла переменной. Контроллер 1721 считывает имеющую отношение к схеме перемежения информацию, предварительно сохраненную в памяти 1723, а также управляет схемой перемежения перемежителя 1719 и схемой обращенного перемежения обращенного перемежителя 1717 согласно считанной информации о схеме перемежения. Так как память 1723 хранит только материнскую матрицу, с помощью которой может быть сформирован блочный код LDPC переменной длины, контроллер 1721 считывает материнскую матрицу, сохраненную в памяти 1723, и формирует показатели матриц перестановок, составляющих соответствующую дочернюю матрицу, с использованием размера Ns' матрицы перестановок, соответствующего предопределенному размеру блока. В дополнение, контроллер 1721 управляет схемой перемежения перемежителя 1719 и схемой обращенного перемежения обращенного перемежителя 1717 с использованием сформированной дочерней матрицы. Подобным образом, если последовательность операций декодирования является начальной последовательностью операций декодирования, должно быть принято во внимание, что выходным сигналом обращенного перемежителя 1717 является 0.

Посредством итерационного выполнения вышеприведенных последовательностей операций устройство декодирования выполняет свободное от ошибок, надежное декодирование. После того, как итерационное декодирование выполнено предопределенное количество раз, переключатель 1714 отключает соединение между декодером 1711 узла переменной и сумматором 1715, а переключатель 1713 включает соединение между декодером 1711 узла переменной и узлом 1729 жесткого решения, чтобы подать сигнал, выведенный из декодера 1711 узла переменной в узел 1729 жесткого решения. Узел 1729 жесткого решения выполняет жесткое решение над сигналом, выведенным из декодера 1711 узла переменной, и выводит результат жесткого решения, а выходное значение узла 1729 жесткого решения становится окончательно декодированным значением.

Как может быть принято во внимание из вышеприведенного описания, настоящее изобретение предлагает блочный код LDPC переменной длины, длина минимального цикла которого максимизирована, в системе мобильной связи, тем самым максимизацию возможности исправления ошибок, а соответственно, улучшение эксплуатационных характеристик системы. В дополнение, настоящее изобретение формирует рациональную матрицу контроля четности, тем самым минимизируя сложность декодирования блочного кода LDPC переменной длины. Более того, настоящее изобретение конструирует блочный код LDPC переменной длины из условия, чтобы сложность его декодирования была прямо пропорциональна длине его блока, тем самым давая возможность эффективного кодирования. В частности, настоящее изобретение формирует блочный код LDPC, который применим к различным скоростям кодирования и обладает различными длинами блока, тем самым способствуя минимизации аппаратной сложности.