Область техники, к которой относится изобретение

Настоящее изобретение относится к системе мобильной связи и, более конкретно, к устройству и способу передачи и приема кодированных данных посредством кодера, имеющего неравные значения вероятности ошибок.

Уровень техники

С появлением системы сотовой мобильной связи в США в конце 70-ых гг. Южная Корея начала предоставлять услугу голосовой связи в системе усовершенствованной службы мобильных телефонов (AMPS), аналоговой системе мобильной связи первого поколения (1G). В середине 90-ых гг. Южная Корея осуществила промышленное внедрение системы множественного доступа с кодовым разделением сигналов, системы мобильной связи второго поколения (2G) для того, чтобы предоставлять голосовые услуги и услуги низкоскоростной передачи данных.

В конце 90-ых гг. Южная Корея частично развернула систему IMT-2000 (Международная служба мобильной связи-2000), систему мобильной связи третьего поколения (3G), предназначенную для предоставления беспроводных мультимедийных услуг, роуминга по всему миру и услуг высокоскоростной передачи данных. Система мобильной связи 3G была специально разработана для того, чтобы передавать данные на высокой скорости в соответствии с быстрым ростом объема обслуживаемых данных. Т.е. система мобильной связи 3G развернулась в систему связи с услугами пакетной передачи, а система связи с услугами пакетной передачи передает пакетные данные множеству мобильных станций и предназначена для передачи значительных объемов данных. Система связи с услугами пакетной передачи разрабатывается для услуги высокоскоростной пакетной передачи.

Система мобильной связи 3G развивается в систему мобильной связи четвертого поколения (4G). Система мобильной связи 4G в настоящее время разрабатывается для стандартизации межсетевого взаимодействия и интеграции между сетью проводной связи и сетью беспроводной связи помимо простой услуги беспроводной связи, которую предоставляли системы мобильной связи предыдущих поколений. Технология передачи больших объемов данных вплоть до уровня пропускной способности, доступной в сети проводной связи, должна быть разработана для сети беспроводной связи.

Между тем, растет важность управляющей информации, а также увеличивается необходимость в высококачественной и высоконадежной системе связи. Один из способов, предложенных для такой высококачественной и высоконадежной системы связи, - это схема адаптивной модуляции и кодирования (AMC).

Схема AMC применяет различные скорости кодирования и различные схемы модуляции согласно параметрам состояния канала. Конкретно, схема AMC применяет высокую скорость кодирования и высокосложную схему модуляции высокой степени к каналу высокого качества, с тем чтобы данные могли передаваться посредством канала высокого качества на высокой скорости, и низкую скорость кодирования и низкосложную схему модуляции к каналу низкого качества, тем самым повышая надежность передаваемого сигнала.

Тем не менее, когда управляющая информация, указывающая параметры состояния канала, ошибочна, управляющая информация может быть ошибочно декодирована, несмотря на низкие значения параметров канала, и скорость кодирования и схема модуляции для канала высокого качества может быть ошибочно использована при передаче данных посредством канала низкого качества. Т.е. невозможно создать высококачественную систему связи.

Далее подробно описывается управляющая информация, используемая в схеме AMC, в качестве примера информации, требующей информации о неравных ошибках. Управляющая информация, используемая в схеме AMC, классифицирует параметры состояния канала на 16 уровней от 0 до максимума. В общем, управляющая информация имеет 4 или 5 бит. Для удобства, при допущении, что управляющая информация имеет одно из значений от 0 до 15, выраженное 4 (двоичными) битами, управляющая информация может быть выражена посредством табл. 1, показанной ниже.

Ссылаясь на табл. 1, когда передается управляющая информация 1111 пятнадцатой степени, если последний бит ошибочен, и информация ошибочно принимается как 1110, уровень AMC неверно интерпретируется как четырнадцатая степень вместо пятнадцатой степени. Наоборот, если первый бит управляющей информации 1111 пятнадцатой степени является ошибочным и информация ошибочно принимается как 0111 вместо 1111, уровень AMC неверно интерпретируется как седьмая степень. Поэтому управляющая информация, имеющая ошибочный первый бит, имеет большую потерю передаваемой по каналам информации, чем управляющая информация, имеющая ошибочный последний бит. Поэтому предпочтительно, чтобы управляющая информация имела меньше ошибок в первом бите, чем в последнем бите.

Как описано выше, для того чтобы создать систему связи, имеющую высокое качество и высокую надежность, коды для применения неравных значений вероятности ошибок или различных приоритетов важности к битам, а также предоставление возможности битам иметь меньше ошибок в первом бите, чем в последнем бите, являются необходимыми при передаче данных, таких как управляющая информация, биты которой имеют разную надежность.

Тем не менее, трудно создать структуру для предоставления неравных значений вероятности ошибок типичным линейным блочным кодам с помощью традиционного неитеративного декодирования, которое присваивает вес минимальному расстоянию. Т.е. каждый бит типичного блочного кода имеет практически одинаковое значение вероятности ошибки, и очень трудно разработать кодер, допускающий кодирование передаваемых бит с различными значениями вероятности ошибки.

Раскрытие изобретения

Следовательно, настоящее изобретение выполнено для того, чтобы разрешить вышеуказанные проблемы, возникающие в предшествующем уровне техники, и цель настоящего изобретения - предоставить устройство и способ передачи бит при применении различных значений вероятности ошибки к передаваемым битам посредством использования неравных кодов разреженного контроля четности (LDPC).

Еще одна цель настоящего изобретения - предоставить устройство и способ передачи данных более высокого качества посредством кодирования управляющей информации, требующей неравных значений вероятности ошибок, с помощью неравных кодов LDPC.

Чтобы достичь этих целей, предусмотрено устройство передачи информационных бит после кодирования информационных бит с помощью кодов разреженного контроля четности (LDPC), имеющих неравные значения вероятности ошибок в системе беспроводной связи, которая канально кодирует и передает информационные биты. Устройство содержит кодер LDPC для преобразования высоких информационных бит к низким переменным узлам и низких информационных бит к высоким переменным узлам, при этом высокие информационные биты имеют высокие приоритеты важности, а низкие информационные биты имеют низкие приоритеты важности из информационных бит, причем низкие переменные узлы - это переменные узлы, имеющие низкие значения вероятности ошибок, а высокие переменные узлы - это переменные узлы, имеющие высокие значения вероятности ошибок на графе коэффициентов кодов LDPC.

В соответствии с другим аспектом настоящего изобретения, предусмотрено устройство приема информационных бит, закодированных с помощью кодов разреженного контроля четности (LDPC), имеющих неравные значения вероятности ошибок в системе беспроводной связи, которая канально кодирует и передает информационные биты. Устройство содержит декодер LDPC для обратного преобразования, соответствующий заранее определенному кодеру для преобразования высоких информационных бит к низким переменным узлам и низких информационных бит к высоким переменным узлам, при этом высокие информационные биты имеют высокие приоритеты важности, а низкие информационные биты имеют низкие приоритеты важности из информационных бит, причем низкие переменные узлы - это переменные узлы, имеющие низкие значения вероятности ошибок, а высокие переменные узлы - это переменные узлы, имеющие высокие значения вероятности ошибок на графе коэффициентов кодов LDPC.

В соответствии с другим аспектом настоящего изобретения, предусмотрен способ передачи информационных бит после кодирования информационных бит с помощью кодов разреженного контроля четности (LDPC), имеющих неравные значения вероятности ошибок в системе беспроводной связи, которая канально кодирует и передает информационные биты. Способ содержит этапы, на которых преобразуют информационные биты, имеющие высокие приоритеты важности из информационных бит, к переменным узлам, имеющим низкие значения вероятности ошибок на графе коэффициентов кодов LDPC, и преобразуют информационные биты, имеющие низкие приоритеты важности из информационных бит, к переменным узлам, имеющим высокие значения вероятности ошибок на графе коэффициентов кодов LDPC.

В соответствии с другим аспектом настоящего изобретения, предусмотрен способ приема информационных бит, закодированных с помощью кодов разреженного контроля четности (LDPC), имеющих неравные значения вероятности ошибок в системе беспроводной связи, которая канально кодирует и передает информационные биты. Способ содержит этапы, на которых обратно преобразуют информационные биты, соответствующие заранее определенному правилу для преобразования информационных бит, имеющих высокие приоритеты важности из информационных бит, к переменным узлам, имеющим низкие значения вероятности ошибки на графе коэффициентов кодов LDPC, и обратно преобразуют информационные биты, соответствующие заранее определенному правилу для преобразования информационных бит, имеющих низкие приоритеты важности из информационных бит, к переменным узлам, имеющим высокие значения вероятности ошибки на графе коэффициентов кодов LDPC.

В соответствии с другим аспектом настоящего изобретения, предусмотрен способ кодирования и передачи данных в системе беспроводной связи, которая канально кодирует и передает информационные биты. Способ содержит этапы, на которых генерируют информационные биты и преобразуют сгенерированные информационные биты к входным узлам кодера согласно приоритетам важности сгенерированных информационных бит, выполняют канальное кодирование преобразованных информационных бит в соответствии с кодированием кодера неравнозначного разреженного контроля четности, сигнально преобразуют канально кодированные информационные биты и модулируют преобразованный сигнал согласно схеме, заданной заранее в системе мобильной связи, и передают окончательные данные, выводимые после модуляции.

В соответствии с другим аспектом настоящего изобретения, предусмотрен способ декодирования принятых данных в системе беспроводной связи, которая канально кодирует и передает информационные биты. Способ содержит этапы, на которых принимают сигнал, переданный от передающей стороны посредством канала, и декодируют принятый сигнал согласно схеме демодуляции, соответствующей схеме модуляции, которая была первоначально применена к сигналу, обратно преобразуют декодированные данные и выполняют канальное декодирование посредством преобразования обратно преобразованных сигналов к кодам разреженного контроля четности (LDPC), имеющим неравные значения вероятности ошибок, согласно приоритетам важности обратно преобразованных сигналов, и выводят канально декодированные данные как окончательные выходные данные.

В соответствии с другим аспектом настоящего изобретения, предусмотрен способ преобразования информационных бит к кодам разреженного контроля четности (LDPC) согласно приоритетам важности информационных бит в системе беспроводной связи, которая канально кодирует и передает информационные биты. Способ содержит этапы, на которых (a) размещают переменные узлы на графе коэффициентов матрицы контроля четности кодов LDPC согласно последовательности, в которой переменные наивысшей степени предшествуют любой другой переменной, и задают первый индекс последовательности для назначения информационных бит, имеющих высокие приоритеты; (b) устанавливают набор переменных узлов, включающий в себя переменные узлы, имеющие наивысшую степень из не назначенных переменных узлов, и подтверждают элементы набора переменных узлов; (c) назначают один переменный узел информационному биту, когда набор переменных узлов включает в себя один переменный узел, и задают второй индекс последовательности для назначения информационных бит, включенных в набор переменных узлов, когда набор переменных узлов включает в себя несколько элементов; и (d) определяют переменные узлы, имеющие наивысшую степень согласно второму индексу последовательности, и назначают информационные биты переменным узлам, имеющим наибольший цикл из переменных узлов, имеющих одинаковую степень.

В соответствии с другим аспектом настоящего изобретения, предусмотрено устройство декодирования кодов разреженного контроля четности (LDPC), имеющих неравные значения вероятности ошибок в системе беспроводной связи, которая канально кодирует и передает информационные биты. Устройство содержит декодер переменных узлов для связывания переменных узлов со столбцами контрольной матрицы кодов LDPC согласно весам столбцов, тем самым, получая значения вероятности; первый сумматор для вычитания сигнала, сгенерированного при предыдущем декодировании, из выходного сигнала декодера переменных узлов; обращенный перемежитель для обращенного перемежения выходного сигнала первого сумматора в соответствии с матрицей контроля четности; декодер контрольных узлов для связывания контрольных узлов со столбцами контрольной матрицы кодов LDPC согласно весам столбцов, тем самым, получая значения вероятности сигналов, выводимых из обращенного перемежителя; второй сумматор для вычитания выходного сигнала обращенного перемежителя из выходного сигнала декодера контрольных узлов; перемежитель для перемежения выходного сигнала второго сумматора в соответствии с матрицей контроля четности; контроллер для генерирования матрицы контроля четности и управления обращенным перемежением и перемежением в соответствии с матрицей контроля четности; и память для сохранения матрицы контроля четности кодов LDPC, имеющих неравные значения вероятности ошибок для кодирования или декодирования информационных бит согласно приоритетам важности информационных бит, при этом обращенный перемежитель управляется контроллером на основе матрицы контроля четности, сохраненной в памяти.

Краткое описание чертежей

Вышеуказанная и другие цели, признаки и преимущества настоящего изобретения станут более понятными из последующего подробного описания, рассматриваемого вместе с прилагаемыми чертежами, из которых:

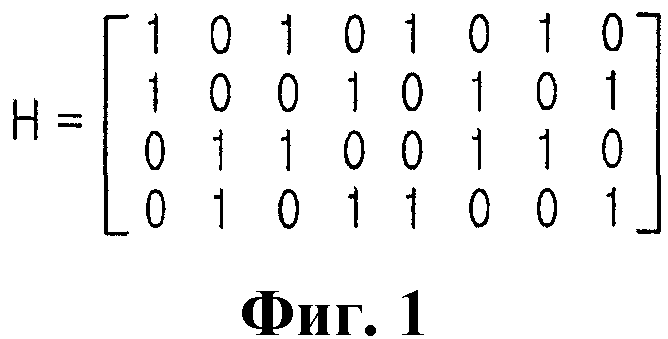

Фиг.1 иллюстрирует типичную матрицу контроля четности кода LDPC (8, 2, 4);

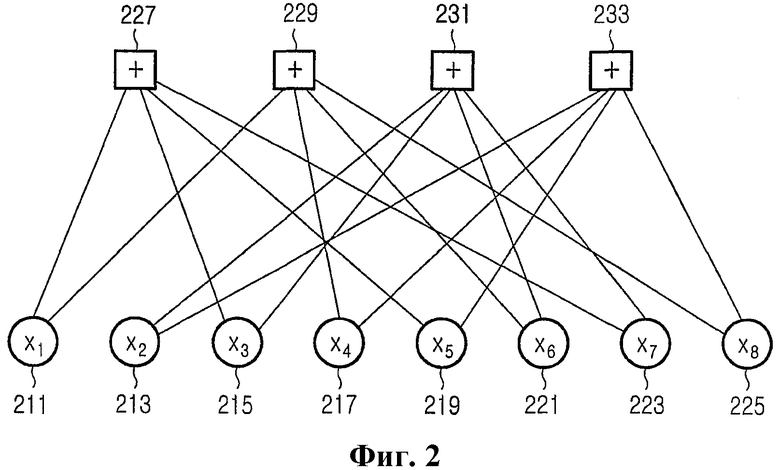

Фиг.2 иллюстрирует граф коэффициентов матрицы контроля четности кода LDPC (8, 2, 4), показанной на фиг.1;

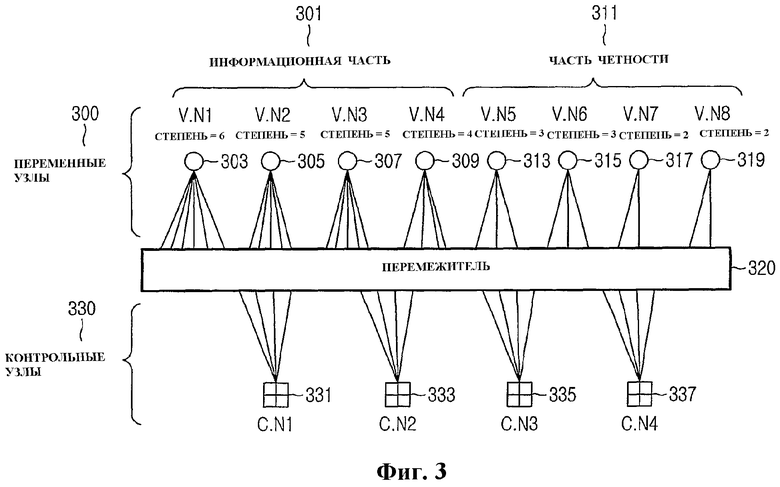

Фиг.3 иллюстрирует граф коэффициентов кода LDPC, имеющего неравнозначные значения вероятности ошибок согласно варианту осуществления настоящего изобретения;

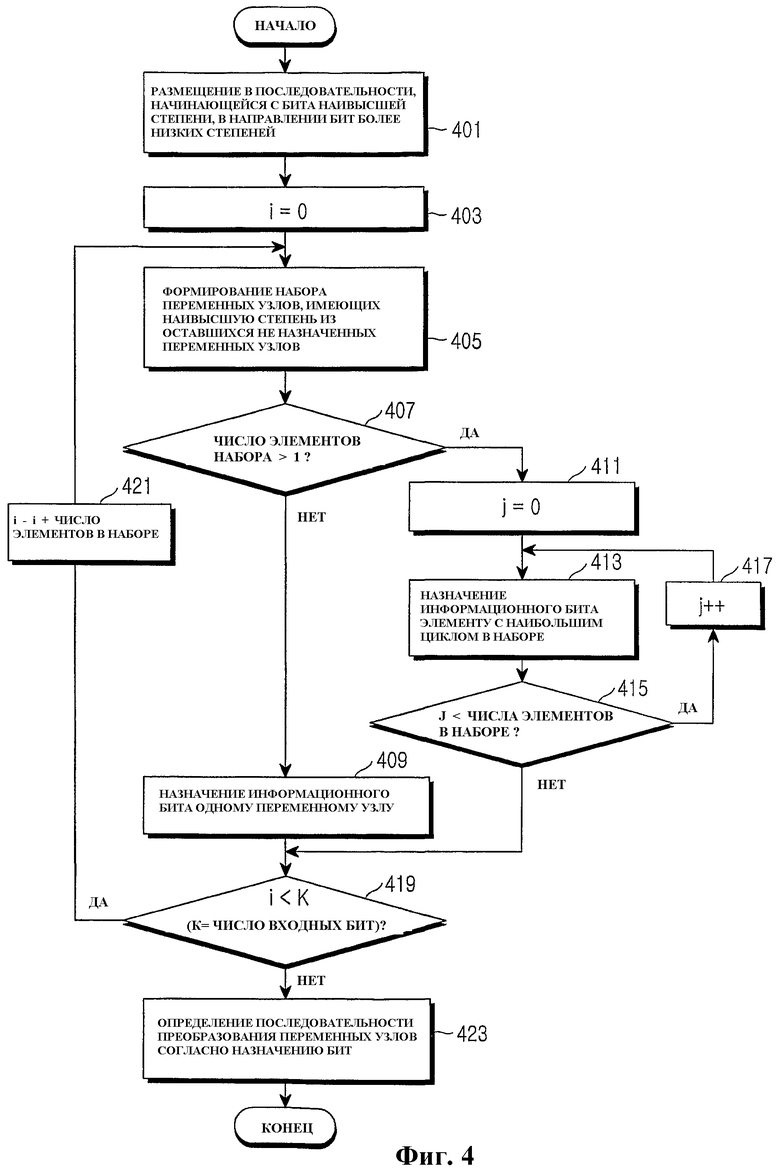

Фиг.4 - это блок-схема последовательности операций процесса преобразования информационных бит к кодам LDPC согласно приоритетам важности бит согласно варианту осуществления настоящего изобретения;

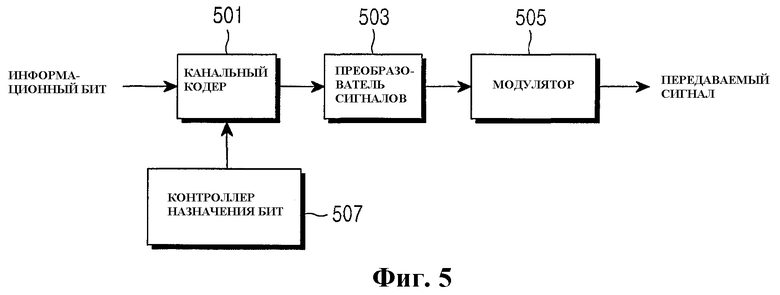

Фиг.5 - это блок-схема устройства передачи данных согласно варианту осуществления настоящего изобретения;

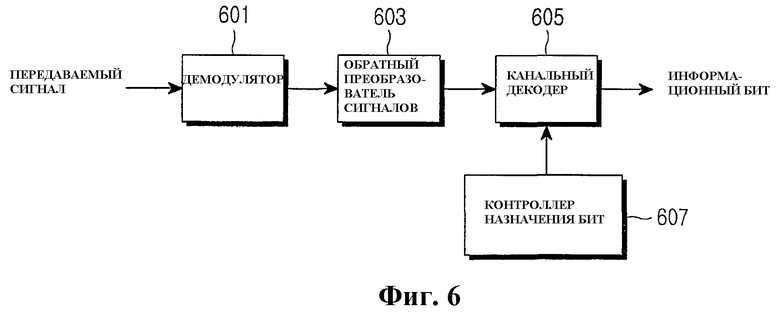

Фиг.6 - это блок-схема устройства приема данных согласно варианту осуществления настоящего изобретения;

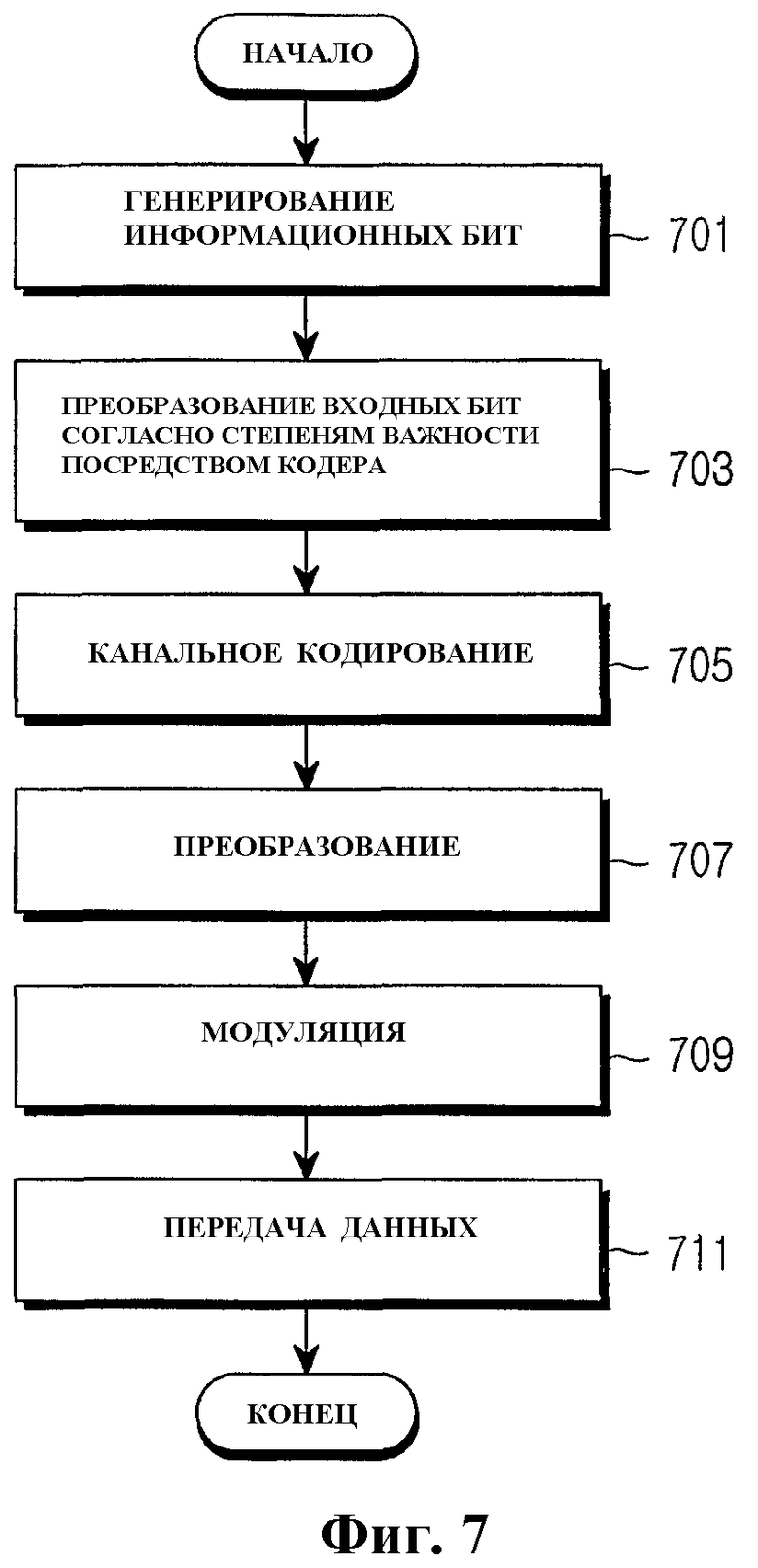

Фиг.7 - это блок-схема последовательности операций способа передачи данных согласно варианту осуществления настоящего изобретения;

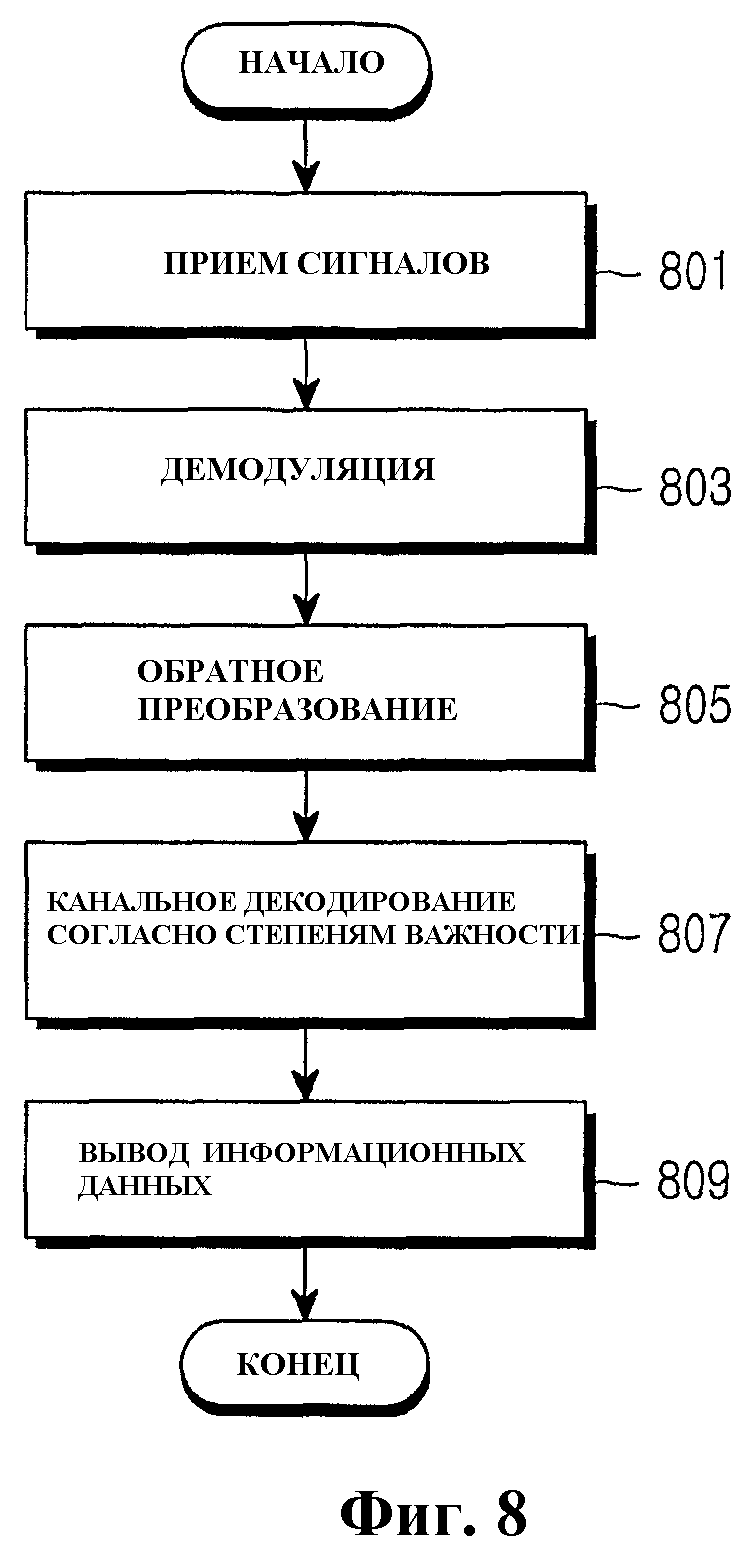

Фиг.8 - это блок-схема последовательности операций способа приема данных согласно варианту осуществления настоящего изобретения;

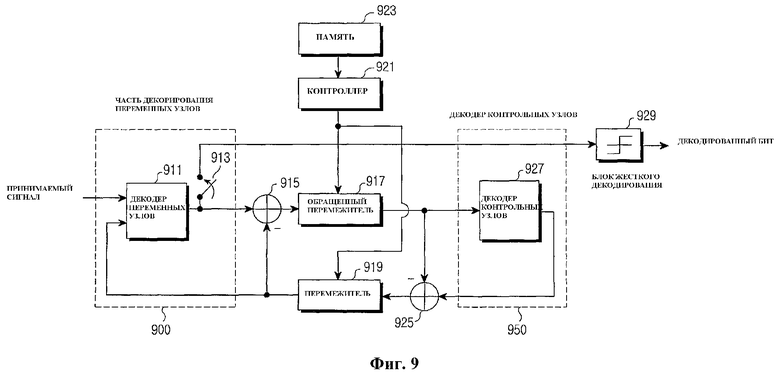

Фиг.9 - это блок-схема, показывающая внутреннюю структуру декодера для неравнозначных блочных кодов LDPC согласно варианту осуществления настоящего изобретения.

Подробное описание предпочтительного варианта осуществления

Далее описаны предпочтительные варианты осуществления настоящего изобретения со ссылками на прилагаемые чертежи. В последующем подробное описание известных функций и конфигураций, содержащихся в данном документе, опущено в случаях, когда это может отвлечь от предмета настоящего изобретения.

Настоящее изобретение использует коды разреженного контроля четности (LDPC) для того, чтобы реализовать коды, имеющие неравнозначные значения вероятности ошибок, тем самым разрешая проблему предшествующего уровня техники, заключающуюся в том, что традиционные линейные блочные коды не могут иметь неравнозначные значения вероятности ошибок.

Поэтому настоящее изобретение предлагает неравнозначные коды LDPC для преобразования бит, требующих высокой надежности, к узлу, имеющему низкое значение вероятности ошибки, и бит, требующих низкой надежности, к узлу, имеющему высокое значение вероятности ошибки, на графе коэффициентов кода LDPC.

Между тем, значение вероятности ошибки каждого узла на графе коэффициентов кода LDPC зависит от цикла и степени каждого узла. Конкретно, чем длиннее цикл каждого узла, тем ниже значение вероятности ошибки. Кроме того, чем выше степень каждого узла, тем ниже значение вероятности ошибки.

В общем, в коде LDPC чем выше степень переменного узла, тем выше надежность. Поэтому данное свойство может быть использовано для того, чтобы создавать коды, имеющие неравнозначные значения вероятности ошибки, посредством назначения более высокой степени биту, имеющему более высокий приоритет важности из данных, имеющих биты с различными степенями важности.

Дополнительно, коды LDPC не только могут быть использованы в итеративном декодировании, но также могут иметь различные значения вероятности ошибки для битов. Поэтому коды LDPC подходят для структуры кодов, имеющих неравнозначные значения вероятности ошибки.

Далее вкратце описывается код LDPC для того, чтобы помочь в понимании настоящего изобретения.

Код LDPC может быть декодирован с помощью алгоритма итеративного декодирования на основе алгоритма суммы-произведения графа коэффициентов. Поскольку декодер для кода LDPC использует основанный на алгоритме суммы-произведения алгоритм итеративного декодирования, он менее сложен, чем декодер турбокода. Помимо этого, декодер кода LDPC легко реализовать с помощью декодера параллельной обработки по сравнению с декодером для турбокода.

Когда код LDPC выражается с помощью графа коэффициентов, циклы существуют на графе коэффициентов кода LDPC. Хорошо известно, что итеративное декодирование на графе коэффициентов кода LDPC, где существуют циклы, не оптимизировано (субоптимально). Кроме того, экспериментально доказано, что код LDPC имеет превосходную производительность в течение итеративного декодирования. Тем не менее, когда существует много циклов короткой длины на графе коэффициентов кода LDPC, код LDPC испытывает снижение производительности. Поэтому постоянно проводятся исследования с целью разработать методику создания кода LDPC таким образом, чтобы не было циклов короткой длины на графе коэффициентов кода LDPC.

Процесс кодирования кода LDPC эволюционировал в процесс кодирования, который использует матрицу контроля четности, имеющую низкую плотность весов вследствие характеристики порождающей матрицы, имеющей высокую плотность весов. "Вес" представляет элемент, имеющий ненулевое значение из элементов, составляющих порождающую матрицу и матрицу контроля четности. В частности, если частичная матрица, соответствующая четности в матрице контроля четности, имеет обычный формат, возможно более эффективное кодирование.

Код LDPC предложен Галлагером, и один код LDPC задан посредством матрицы контроля четности, в которой основные элементы имеют значение 0, а вспомогательные элементы, за исключением элементов, имеющих значение 0, имеют значение 1.

Чтобы быть более конкретным, схема кодирования LDPC - это схема кодирования блочным кодом, которая кодирует передаваемые данные I посредством осуществления действий с данными I с помощью порождающей матрицы G. При этом, когда кодированные данные помещаются как C, кодированные данные C выражаются в соответствии с уравнением 1 ниже:

IxG = C (1)

Когда кодированные данные C декодируются, с кодированными данными C осуществляются действия с помощью матрицы контроля четности H и определяется, что нет ошибки, когда результаты операции матрицы контроля четности для всех C такие, как показаны в уравнении 2 ниже:

HxC = 0,∀C (2)

Поэтому и код LDPC, и сложность операции для LDPC может быть задана посредством матрицы контроля четности H.

Например, код LDPC (N, j, k) - это линейный блочный код, имеющий длину блока N, и он задается посредством разреженной матрицы контроля четности, в которой каждый столбец имеет j элементов, имеющих значение 1, каждая строка имеет k элементов, имеющих значение 1, и все элементы, за исключением элементов, имеющих значение 1, имеют значение 0.

Код LDPC, в котором значение веса каждого столбца в матрице контроля четности фиксировано как j, а значение веса каждой строки в матрице контроля четности фиксировано как k, как указано выше, называется "регулярным кодом LDPC". В данном документе значение веса представляет число весов. В отличие от регулярного кода LDPC, код LDPC, в котором значение веса каждого столбца в матрице контроля четности и значение веса каждой строки в матрице контроля четности не фиксировано, называется "нерегулярным кодом LDPC". В целом известно, что нерегулярный код LDPC имеет большую производительность, чем регулярный код LDPC. Тем не менее, в случае нерегулярного кода LDPC, поскольку значение веса каждого столбца и значение веса каждой строки в матрице контроля четности не является фиксированным, т.е. нерегулярно, значение веса каждого столбца в матрице контроля четности и значение веса каждой строки в матрице контроля четности должно быть надлежащим образом настроено для того, чтобы гарантировать отличную производительность.

Ссылаясь на фиг.1 и 2, далее приводится описание матрицы контроля четности кода LDPC (8, 2, 4) в качестве примера кода LDPC (N, j, k).

Фиг.1 - это схема, иллюстрирующая матрицу контроля четности кода общего кода LDPC (8, 2, 4).

Ссылаясь на фиг.1, матрица контроля четности H кода LDPC (8, 2, 4) составлена из 8 столбцов и 4 строк, при этом значение веса каждого столбца фиксировано как 2, а значение веса каждой строки фиксировано как 4. Поскольку значение веса каждого столбца и значение веса каждой строки в матрице контроля четности является регулярным, как указано выше, код LDPC (8, 2, 4), проиллюстрированный на фиг.1, становится регулярным кодом LDPC.

Граф коэффициентов кода LDPC (8, 2, 4), описанный в связи с фиг.1, далее описывается со ссылкой на фиг.2.

Фиг.2 - это схема, иллюстрирующая граф коэффициентов кода LDPC (8, 2, 4) фиг.1.

Ссылаясь на фиг.2, граф коэффициентов кода LDPC (8, 2, 4) составлен из 8 переменных узлов x1 211, x2 213, x3 215, x4 217, x5 219, x6 221, x7 223 и x8 225, и 4 контрольных узлов 227, 229, 231 и 233. Когда элемент, имеющий вес, т.е. значение 1, существует в точке, где i-ая строка и j-ый столбец матрицы контроля четности кода LDPC (8, 2, 4) пересекаются, формируется ветвь между переменным узлом xj и i-ым контрольным узлом.

Поскольку матрица контроля четности кода LDPC имеет небольшое значение веса, как описано выше, можно выполнить декодирование посредством процесса итеративного декодирования даже в блочном коде, имеющем относительно большую длину, который представляет производительность, аппроксимирующую ограничение пропускной способности канала Шэннона, таком как турбокод, при этом постоянно увеличивая длину блока блочного кода. Доказано, что процесс итеративного декодирования кода LDPC с помощью методики переноса потоков практически аппроксимирует процесс итеративного декодирования турбокода по производительности.

Чтобы сгенерировать высокопроизводительный код LDPC, следующие условия должны быть удовлетворены.

(1) Циклы на графе коэффициентов кода LDPC должны приниматься во внимание.

"Цикл" ссылается на контур, сформированный ребрами, соединяющими переменные узлы с контрольными узлами на графе коэффициентов кода LDPC, и длина цикла задается как число ребер, составляющих контур. Длинный цикл означает, что число ребер, соединяющих переменные узлы с контрольными узлами, составляющих контур на графе коэффициентов кода LDPC, большое. Наоборот, короткий цикл означает, что число ребер, соединяющих переменные узлы с контрольными узлами, составляющих контур на графе коэффициентов кода LDPC, небольшое.

По мере того, как циклы на графе коэффициентов кода LDPC становятся длиннее, относительный уровень производительности кода LDPC увеличивается по следующим причинам. Т.е. когда длинные циклы генерируются на графе коэффициентов кода LDPC, можно предотвратить снижение производительности, такое как минимальный уровень ошибок, возникающих, когда слишком много циклов короткой длины существует на графе коэффициентов кода LDPC.

(2) Биты, имеющие более высокую степень, имеют лучшую производительность на графе коэффициентов кода LDPC.

Как правило, биты, имеющие более высокую степень, имеют лучшую производительность на графе коэффициентов кода LDPC, поскольку биты, имеющие более высокую степень, могут быть восстановлены посредством итеративного декодирования другими битами, соединенными посредством ребер. "Степень" ссылается на число ребер, идущих к переменным узлам и контрольным узлам на графе коэффициентов кода LDPC. Дополнительно, "распределение степеней" на графе коэффициентов кода LDPC ссылается на отношение числа узлов, имеющих конкретную степень, к общему числу узлов.

Поэтому настоящее изобретение предлагает способ эффективного кодирования и декодирования информации, имеющей биты различных степеней важности (например, управляющей информации) посредством использования разности между значениями вероятности ошибок узлов в неравнозначном коде LDPC, как описано выше.

Фиг.3 - это схема, иллюстрирующая граф коэффициентов кода LDPC, имеющего неравнозначные значения вероятности ошибки согласно варианту осуществления настоящего изобретения. Фиг.3 показывает код LDPC, имеющий скорость кодирования 1/2, который принимает четыре информационных бита и генерирует восемь кодированных битов.

Ссылаясь на фиг.3, граф коэффициентов кода LDPC, имеющего неравнозначные значения вероятности ошибки, согласно варианту осуществления настоящего изобретения, может быть выражен посредством переменных узлов 300, контрольных узлов 330 и перемежителя 320. Например, граф коэффициентов может включать в себя восемь переменных узлов V.N1-V.N8 303-319 соответственно и четыре контрольных узла C.N1-C.N4 331-337 соответственно. Перемежитель 320 соединяет переменные узлы 300 и контрольные узлы 330 согласно определенным кодам LDPC5.

Между тем, из переменных узлов 300, V.N1 303, V.N2 305, V.N3 307 и V.N4 309 - это переменные узлы информационной части 301, в которой информационные биты преобразуются и с ними осуществляются действия, а V.N5 313, V.N6 315, V.N7 317 и V.N8 319 - это переменные узлы части 311 четности, в которых биты четности, сгенерированные посредством преобразования информационных бит, преобразуются и с ними осуществляются действия.

Линии, идущие к каждому переменному узлу, представляют ребра, идущие к нескольким контрольным узлам, и число ребер, идущих к каждому узлу, подразумевает степень узла. Т.е. V.N1 303 имеет степень 6, поскольку 6 ребер идет к V.N1 303, а V.N2 305 имеет степень 5, поскольку 5 ребер идет к V.N2 305. Как описано выше, чем выше степень, тем меньше значение вероятности ошибки информационных бит, преобразованных к соответствующему узлу.

Поэтому в настоящем изобретении выполняется кодирование, отражающее степени важности информационных бит согласно степени каждого узла, т.е. согласно числу ребер, идущих к каждому узлу. Другими словами, из информационных бит, которые должны быть закодированы и переданы, биты, имеющие высокий вес, преобразуются к узлам высокой степени, а биты, имеющие низкий вес, преобразуются к узлам низкой степени. Дополнительно, между узлами, имеющими одинаковую степень, биты, имеющие более высокий вес, преобразуются к узлам, имеющим больший цикл, поскольку узлы, имеющие больший цикл, имеют меньшее значение вероятности ошибки.

Далее подробно описан способ преобразования бит согласно одному варианту осуществления со ссылкой на фиг.3.

Сначала получается назначение бит с наивысшим приоритетом {V.N1} как набор переменных узлов, имеющих наивысшую степень. При этом полученный набор включает в себя только один элемент, бит, имеющий наивысший приоритет (т.е. наивысший вес), назначается узлу V.N1 303.

Далее для назначения бит со вторым наивысшим приоритетом получается набор переменных узлов, имеющих наивысшую степень из не назначенных переменных узлов. Поскольку наивысшая степень переменных узлов, исключая уже назначенный переменный узел, - это 5, {V.N2, V.N3} получается как набор переменных узлов, имеющих степень 5. Полученный набор включает в себя 2 элемента. В этом случае, поскольку два переменных узла имеют одинаковую степень, циклы двух переменных узлов сравниваются, и переменный узел, имеющий больший цикл, выбирается. Если V.N3 307 имеет больший цикл, чем цикл V.N2 305, бит, имеющий второй наивысший приоритет, назначается V.N3 307, а бит, имеющий третий наивысший приоритет, назначается V.N2 305. Наоборот, если V.N3 307 имеет меньший цикл, чем цикл V.N2 305, бит, имеющий второй наивысший приоритет, назначается V.N2 305, а бит, имеющий третий наивысший приоритет, назначается V.N3 307.

Далее для назначения бит с четвертым наивысшим приоритетом выбирается V.N4 309, имеющий степень 4. В заключение, биты, имеющие наивысший приоритет, преобразуются к V.N1 303, биты, имеющие второй наивысший приоритет, преобразуются к V.N3 307, биты, имеющие третий наивысший приоритет, преобразуются к V.N2 305, а биты, имеющие четвертый наивысший приоритет, преобразуются к V.N4 309. Между тем, биты четности назначаются другим переменным узлам.

При этом способ преобразования информационных бит к переменным узлам включает в себя способ выполнения преобразования после перекомпоновки информационных бит согласно последовательности преобразования, описанной выше, и способ обмена столбцами матрицы контроля четности в коде LDPC при фиксации введенных информационных бит.

Например, когда передаваемые информационные биты имеют степени важности, уменьшающиеся по мере того, как они проходят от самого старшего бита (MSB) к самому младшему биту (LSB), как показано в табл. 1, второй столбец и третий столбец бита контроля четности могут быть заменены для того, чтобы выполнить эффективное преобразование. Вместо этого, вторые биты и третьи биты введенных информационных бит могут быть заменены для того, чтобы выполнять эффективное преобразование.

Между тем, при проектировании кодов LDPC полная производительность кода может быть повышена посредством усовершенствования минимального цикла за счет надлежащей структуры перемежителя 320.

Далее со ссылкой на фиг.4 обобщен и описан способ преобразования кодов LDPC и информационных бит согласно варианту осуществления настоящего изобретения, описанному со ссылкой на фиг.3.

Фиг.4 - это блок-схема последовательности операций процесса преобразования информационных бит к кодам LDPC согласно приоритетам важности бит.

Ссылаясь на фиг.4, граф коэффициентов согласно матрице контроля четности данного кода LDPC сначала размещен в последовательности, в которой бит, имеющий наивысшую степень, предшествует любому другому биту (этап 401). При этом индексу i, который указывает очередь назначения соответствующего бита согласно последовательности, в которой бит, имеющий наивысшую степень, предшествует любому другому, присваивается значение 0 (этап 403). Затем набор переменных узлов, имеющих наивысшую степень из оставшихся не назначенных переменных узлов, получается (этап 405). После этого анализируется число элементов, содержащихся в полученном наборе переменных узлов (этап 407).

Как результат определения, получающегося из этапа 407, когда набор переменных узлов, полученный на этапе 405, включает в себя один элемент, информационный бит назначается одному переменному узлу на этапе 409. Наоборот, как результат определения, получающегося из этапа 407, когда набор переменных узлов, полученный на этапе 405, включает в себя несколько элементов, следующий процесс выполняется для того, чтобы определить приоритеты переменных узлов в наборе, имеющих одинаковую степень.

Сначала для того, чтобы назначить биты, принадлежащие набору, индексу последовательности j присваивается значение 0 (этап 411). Далее узел, имеющий наибольший цикл из переменных узлов наивысшей степени, выбирается, и ему назначается информационный бит (этап 413). После этого индекс последовательности j сравнивается с числом элементов в наборе (этап 415). Когда индекс последовательности j меньше числа элементов в наборе, один добавляется к индексу последовательности j (этап 417). Затем вышеуказанный процесс повторяется до тех пор, пока всем переменным узлам не будут назначены информационные биты.

Между тем, когда все переменные узлы набора назначены информационным битам посредством сравнения на этапе 415, индекс последовательности i сравнивается с числом K входных бит на этапе 419. При этом если индекс последовательности i меньше числа K входных битов, число элементов в наборе прибавляется к индексу последовательности i на этапе 421. Затем процесс повторяется с этапа 405. Наконец, когда назначение всех входных бит завершено, переменные узлы в матрице контроля четности размещаются согласно назначению бит, и последовательность преобразования определяется на этапе 423. Т.е. последовательность переменных узлов определяется согласно последовательности информационных бит, которые должны быть переданы.

При этом способ преобразования информационных бит к кодам LDPC согласно их степени важности включает в себя, как описано выше, способ выполнения преобразования после перекомпоновки информационных бит согласно последовательности преобразования при фиксации кодов LDPC, и способ обмена столбцами матрицы контроля четности в коде LDPC при фиксации введенных информационных бит.

При этом посредством выполнения вышеописанного процесса информационные биты, которые должны быть переданы, преобразуются к кодам LDPC согласно их степеням важности или приоритетам. Дополнительно, схема преобразования определяется посредством цикла каждого переменного узла и номера ребра (т.е. степени) каждого переменного узла, определяющим значение вероятности ошибки кода LDPC. Т.е. из информационных бит, которые должны быть переданы, биты, имеющие высокий вес, преобразуются так, чтобы быть закодированными переменными узлами, имеющими низкое значение вероятности ошибки, из переменных узлов на графе коэффициентов кода LDPC, тогда как биты, имеющие низкий вес, преобразуются так, чтобы быть закодированными переменными узлами, имеющими высокое значение вероятности ошибки, из переменных узлов на графе коэффициентов кода LDPC.

Далее описывается устройство и способ передачи/приема данных на основе схемы кодирования LDPC согласно варианту осуществления настоящего изобретения со ссылкой на фиг.5-8.

Сначала описывается устройство передачи данных и устройство приема данных со ссылкой на фиг.5 и 6.

Фиг.5 - это блок-схема устройства передачи данных согласно варианту осуществления настоящего изобретения.

Ссылаясь на фиг.5, аналогично типичному передающему устройству в системе мобильной связи устройство передачи данных согласно варианту осуществления настоящего изобретения включает в себя канальный кодер 501, преобразователь 503 сигналов и модулятор 505.

Во-первых, информационные биты, которые должны быть переданы, входят в канальный кодер 501. Затем канальный кодер 501 кодирует входные информационные биты в кодированные биты. При этом процесс кодирования необходим для того, чтобы добавлять дополнительную информацию в информационные биты, тем самым, корректируя любые ошибки, которые могут возникать в канале, и достигая связи с большей надежностью. Канальный кодер 501 может быть сверточным кодером, турбокодером или кодером LDPC в типичной системе мобильной связи.

Канальный кодер согласно варианту осуществления настоящего изобретения может быть неравнозначным кодером LDPC, и информационные биты, требующие неравнозначных значений вероятности ошибки, из входных информационных бит, могут быть закодированы согласно способу согласно варианту осуществления настоящего изобретения. Т.е. неравнозначный кодер LDPC согласно варианту осуществления настоящего изобретения преобразует входные информационные биты к переменным узлам на графе коэффициентов кода LDPC при применении различных значений вероятности ошибок к информационным битам согласно приоритетам важности информационных бит.

Устройство передачи данных согласно варианту осуществления настоящего изобретения дополнительно включает в себя контроллер 507 размещения бит. Контроллер 507 размещения бит может управлять информационными битами для того, чтобы быть кодами LDPC, размещенными согласно их степеням важности. Тем не менее, когда передаваемые информационные биты с последовательностью степеней важности, определенной заранее, входят в канальный кодер 501, контроллер 507 размещения бит является необязательным, и коды LDPC могут быть преобразованы согласно заранее определенной последовательности степеней важности.

Далее кодированные биты, которые являются выходными данными канального кодера 501, преобразуются преобразователем 503 сигналов. При этом преобразователь 503 сигналов может преобразовывать символы входных бит различными способами согласно схемам модуляции, используемым в системе связи. Например, когда используется схема двухпозиционной фазовой манипуляции (BPSK) для схемы модуляции, входной бит 0, входящий в преобразователь 503 сигналов, преобразуется в 1, а входной бит 1 преобразуется в -1.

Преобразованный сигнал модулируется в передаваемый сигнал посредством модулятора 505. Модулятор 505 - это устройство, допускающее прием сигналов из преобразователя 503 сигналов и передачу сигнала в линию передачи, т.е. преобразование сигнала в электрический сигнал измененного типа. Схемы модуляции, используемые модулятором 505, включают в себя схему BPSK, схему квадратурной фазовой манипуляции (QPSK), схему восьмипозиционной фазовой манипуляции (8PSK), схему 16-позиционной квадратурной фазовой манипуляции (16QAM) и схему 64QAM. Эти схемы модуляции не имеют прямого отношения к настоящему изобретению, поэтому их подробное описание опущено в данном документе.

Данные, передаваемые устройством передачи, описанным выше со ссылкой на фиг.5, могут приниматься устройством приема, показанным на фиг.6, согласно порядку, который является обратным вышеупомянутому порядку.

Фиг.6 - это блок-схема устройства приема данных согласно варианту осуществления настоящего изобретения.

Ссылаясь на фиг.6, аналогично типичному приемному устройству в системе мобильной связи устройство приема данных согласно варианту осуществления настоящего изобретения включает в себя демодулятор 601, обратный преобразователь 603 сигналов и канальный декодер 605.

Сначала сигнал, принимаемый антенной (не показана) посредством беспроводного канала, входит в демодулятор 601 после радиообработки радиопроцессором (не показан). Демодулятор 601 демодулирует принимаемый сигнал согласно схеме демодуляции модулятора 505 в устройстве передачи данных фиг.5. Например, данные, модулированные согласно схеме BPSK, демодулируются согласно схеме демодуляции, соответствующей схеме BPSK.

Выходной сигнал из демодулятора 601 соответствует элементу преобразованного сигнала перед модуляцией модулятором 505 в устройстве передачи фиг.5. Другими словами, сигнал, модулированный для передачи в устройстве передачи, восстанавливается до сигнала перед модуляцией.

Между тем, выходные данные демодулятора 601 оцениваются и преобразуются в данные до прохождения преобразователя 503 сигналов фиг.5 посредством обратного преобразователя 603 сигналов. Т.е. обратный преобразователь 603 сигналов - это блок, соответствующей преобразователю 503 сигналов фиг.5, и он находит значения оценки для бит перед прохождением преобразователя 503 сигналов для того, чтобы преобразовать выходные данные демодулятора 601 во входные данные канального декодера 605.

Далее выходные данные обратного преобразователя 603 сигналов входят в канальный декодер 605. При этом канальный декодер 605 выполняет процесс, обратный процессу канального кодера 501 фиг.5. При этом канальный декодер 605 оценивает и выводит переданные информационные биты на основе выходных данных обратного преобразователя 603 сигналов.

Между тем, различные типы канальных декодеров согласно структурам канального кодера 501 фиг.5 могут быть использованы в качестве канального декодера 605. Канальный декодер 605, используемый в варианте осуществления настоящего изобретения, - это декодер LDPC, имеющий неравнозначные значения вероятности ошибки.

Т.е. поскольку информационные биты, передаваемые от канального кодера 501 фиг.5, преобразуются в переменные узлы неравнозначного кодера LDPC с учетом приоритетов важности информационных бит, канальный декодер 605 для декодирования принятого сигнала - это предпочтительно неравнозначный декодер LDPC, соответствующий кодеру LDPC, используемому в качестве канального кодера 501.

Между тем, устройство приема данных может включать в себя дополнительный контроллер 607 размещения бит, равный контроллеру 507 размещения бит в устройстве передачи. Контроллер 607 размещения бит контролирует канальный декодер 605 и преобразованием информации относительно способа преобразования неравнозначного кода LDPC согласно приоритету важности информационных бит.

Далее описывается способ передачи данных и способ приема данных со ссылкой на фиг.7 и 8.

Фиг.7 - это блок-схема последовательности операций способа передачи данных согласно варианту осуществления настоящего изобретения.

Ссылаясь на фиг.7, сначала информационные биты, которые должны быть переданы, генерируются на этапе 701. Информационные биты преобразуются к входным узлам кодера согласно приоритетам важности информационных бит (этап 703). Затем выполняется канальное кодирование посредством неравнозначного кодера LDPC, соответствующего схеме преобразования (этап 705). Канально кодированные информационные биты преобразуются по сигналам посредством преобразователя сигналов на этапе 707, и преобразованный по сигналам сигнал входит в модулятор. Сигнал, входящий в модулятор, модулируется согласно схеме модуляции, соответствующей заранее определенному системному условию, на этапе 709, и окончательные данные передаются принимающей стороне на этапе 711.

Данные, передаваемые согласно способу передачи данных, описанному выше со ссылкой на фиг.7, могут быть приняты согласно способу приема данных, описанному со ссылкой на фиг.8. Способ приема данных является обратным способу передачи данных, описанному выше.

Фиг.8 - это блок-схема последовательности операций способа приема данных согласно варианту осуществления настоящего изобретения.

Ссылаясь на фиг.8, сигнал из канала принимается на этапе 801, и принятый сигнал демодулируется в данные, соответствующие ему до модуляции, на этапе 803. При этом демодуляция использует схему демодуляции, соответствующую схеме модуляции стороны передачи. Затем демодулированные данные обратно преобразуются обратным преобразователем сигналов на этапе 805. При этом обратный преобразователь сигналов выполняет оценку данных перед преобразованием сигналов.

Далее выходное значение, обратно преобразованное обратным преобразователем сигналов, входит в декодер, который декодирует значение в данные перед кодированием согласно степени важности на этапе 807. При этом декодирование использует схему декодирования, соответствующую схеме кодирования, описанной выше со ссылкой на фиг.7. Конкретно, декодирование согласно варианту осуществления настоящего изобретения использует коды LDPC, имеющие неравнозначные значения вероятности ошибки. В итоге декодированный сигнал выводится как информационные данные на этапе 809.

Далее со ссылкой на фиг.9 описывается процесс декодирования неравнозначных кодов LDPC согласно варианту осуществления изобретения неравнозначным кодером LDPC, описанным выше.

Фиг.9 - это блок-схема, показывающая внутреннюю структуру декодера для неравнозначных блочных кодов LDPC согласно варианту осуществления настоящего изобретения.

Ссылаясь на фиг.9, декодер неравнозначных блочных кодов LDPC включает в себя часть 900 декодирования переменных узлов, сумматор 915, обращенный перемежитель 917, перемежитель 919, контроллер 921, память 923, сумматор 925, часть 950 декодирования контрольных узлов и блок 929 жесткого декодирования. Дополнительно, часть 900 декодирования переменных узлов включает в себя декодер 911 переменных узлов и переключатель 913, а часть 950 декодирования контрольных включает в себя декодер 927 контрольных узлов.

Сначала сигнал, принимаемый посредством беспроводного канала, входит в декодер 911 переменных узлов части 900 декодирования переменных узлов. Декодер 911 переменных узлов вычисляет значения вероятности входных сигналов и выводит вычисленные значения вероятности переключателю 913 и сумматору 915. При этом декодер 911 переменных узлов соединяет переменные узлы в соответствии с матрицей контроля четности, заданной заранее в декодере для блочных кодов LDPC, и выполняет операцию обновления, имеющую то же число входных значений и выходных значений, что и число значений 1, связанных с каждым из переменных узлов. Число значений 1, связанных с каждым из переменных узлов, равно весу каждого из столбцов матрицы контроля четности. Поэтому декодер 911 переменных узлов выполняет различные внутренние операции согласно весам столбцов матрицы контроля четности.

Сумматор 915 принимает сигнал, выводимый от декодера 911 переменных узлов, и сигнал, выводимый от перемежителя 919 в предыдущем процессе итеративного декодирования. Кроме того, сумматор 915 вычитает выходной сигнал перемежителя 919 в предыдущем процессе итеративного декодирования из выходного сигнала декодера 911 переменных узлов и выводит вычтенный сигнал в обращенный перемежитель 917. При этом, когда декодирование - это первое декодирование, разумеется, предполагается, что выходной сигнал обращенного перемежителя 917 считается 0.

Обращенный перемежитель 917 принимает выходной сигнал сумматора 915, обратно перемежает сигнал согласно схеме, заданной заранее, и выводит его сумматору 925 и декодеру 927 контрольных узлов. При этом обращенный перемежитель 917 имеет внутреннюю структуру, соответствующую матрице контроля четности. Это обусловлено тем, что выходные значения для входных значений перемежителя 919, соответствующего обращенному перемежителю 917, различные согласно позициям элементов, имеющих значение 1 в матрице контроля четности.

Между тем, сумматор 925 принимает сигнал, выводимый из декодера 927 контрольных узлов в предыдущем процессе итеративного декодирования, и сигнал, выводимый из обращенного перемежителя 917. Кроме того, сумматор 925 вычитает выходной сигнал обращенного перемежителя 917 из выходного сигнала декодера 927 контрольных узлов в предыдущем процессе итеративного декодирования и выводит вычтенный сигнал перемежителю 919. При этом декодер 927 контрольных узлов связывает контрольные узлы в соответствии с матрицей контроля четности, заданной заранее в декодере для блочных кодов LDPC, и выполняет операцию обновления, имеющую то же число входных значений и выходных значений, что и число значений 1, связанных с каждым из контрольных узлов. Число значений 1, связанных с каждым из контрольных узлов, равно весу каждой из строк матрицы контроля четности. Поэтому декодер 927 контрольных узлов выполняет различные внутренние операции согласно весам строк матрицы контроля четности.

Далее перемежитель 919 перемежает выходной сигнал сумматора 925 согласно схеме, заданной заранее под управлением контроллера 921, и выводит перемеженный сигнал сумматору 915 и декодеру 911 переменных узлов. При этом контроллер 921 считывает информацию относительно схемы перемежения, сохраненной в памяти 923 согласно матрице контроля четности, созданной согласно настоящему изобретению, и управляет перемежением посредством перемежителя 919. Дополнительно, когда декодирование - это первое декодирование, естественно, что выходной сигнал обращенного перемежителя 917 должен считаться нулем 0.

При этом матрица контроля четности кодов, имеющих неравнозначные значения вероятности ошибки согласно настоящему изобретению, сохранена заранее в памяти, как описано выше, и обращенный перемежитель следует схеме, заданной в контроллере на основе матрицы контроля четности, сохраненной в памяти.

Посредством неоднократного выполнения вышеуказанного процесса может быть достигнуто высоконадежное декодирование без ошибок. После того как периодически повторяющееся декодирование выполняется заранее определенное число раз, переключатель 913 разъединяет соединение между декодером 911 переменных узлов и сумматором 915 и включает соединение между декодером 911 переменных узлов и блоком 929 жесткого декодирования с тем, чтобы сигнал, выводимый из декодера 911 переменных узлов, мог быть выведен блоку 929 жесткого декодирования. Блок 929 жесткого декодирования жестко декодирует сигнал, выводимый из декодера 911 переменных узлов, и выводит результат жесткого декодирования, который является результирующим декодированным значением.

Между тем, неравнозначные коды LDPC согласно варианту осуществления настоящего изобретения сохранены в памяти 923. При этом сохраненные неравнозначные коды LDPC - это коды, заданные для кодирования и декодирования LDPC с учетом степеней важности передаваемых информационных бит. Поэтому, когда последовательность степеней важности передаваемых информационных бит изменяется, столбцы кодов LDPC могут быть заменены, или последовательность преобразования может быть изменена согласно настоящему изобретению.

В вышеописанной системе мобильной связи согласно настоящему изобретению коды, имеющие неравнозначные значения вероятности ошибки, созданы с помощью кодов LDPC, имеющих различные степени, и используются при кодировании информации, имеющей различные степени важности, такой как управляющая информация, тем самым повышая производительность системы.

Несмотря на то что изобретение показано и описано со ссылкой на его конкретные варианты осуществления, специалистам в данной области техники следует понимать, что различные изменения по форме и содержанию могут быть сделаны без отступления от сущности и объема изобретения, определенных прилагаемой формулой изобретения.

Изобретение относится к системе мобильной связи, в частности к устройству и способу передачи и приема кодированных данных посредством кодера, имеющего неравные значения вероятности ошибок. Техническим результатом является собственно создание устройства и способа передачи бит при применении различных значений вероятности ошибки к передаваемым битам посредством использования неравных кодов разреженного контроля четности (LDPC). Предложено устройство передачи информационных бит после кодирования информационных бит с помощью LDPC, имеющих неравные значения вероятности ошибок в системе беспроводной связи, которая канально кодирует и передает информационные биты, включающее: кодер LDPC для преобразования высоких информационных бит к низким переменным узлам и низких информационных бит к высоким переменным узлам, при этом высокие информационные биты имеют высокие приоритеты важности, а низкие информационные биты имеют низкие приоритеты важности из информационных бит, причем низкие переменные узлы - это переменные узлы, имеющие низкие значения вероятности ошибок, а высокие переменные узлы - это переменные узлы, имеющие высокие значения вероятности ошибок на графе коэффициентов кодов LDPC. 4 н. и 32 з.п. ф-лы, 9 ил.

| HYEON WOO LEE | |||

| Enabling technologies in HSDPA | |||

| PANEL DISCUSSION FOR VTC FALL | |||

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

| GUINAND P.S | |||

| et al | |||

| Constraction of UEP codes suitable for iterative decoding | |||

| Proc | |||

| Металлический водоудерживающий щит висячей системы | 1922 |

|

SU1999A1 |

| Canada, June 1999, c.1-4 | |||

| CHINGFU LAN et al | |||

| Scalable Image and Video Transmission Using Irregular | |||

Авторы

Даты

2008-11-27—Публикация

2004-12-20—Подача