Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в операционных усилителях (ОУ)).

Известны схемы так называемых «перегнутых» каскодных дифференциальных усилителей (КДУ) на n-р-n и р-n-р транзисторах [1-40], которые стали основой более чем 20 серийных операционных усилителей, выпускаемых как зарубежными (НА2520, НА5190, AD797, AD8631, AD8632, ОР90 и др.), так и российскими (154УДЗ и др.) микроэлектронными фирмами. В связи с высокой популярностью такой архитектуры ДУ на их модификации выдано более 100 патентов. Предлагаемое изобретение относится к данному подклассу устройств.

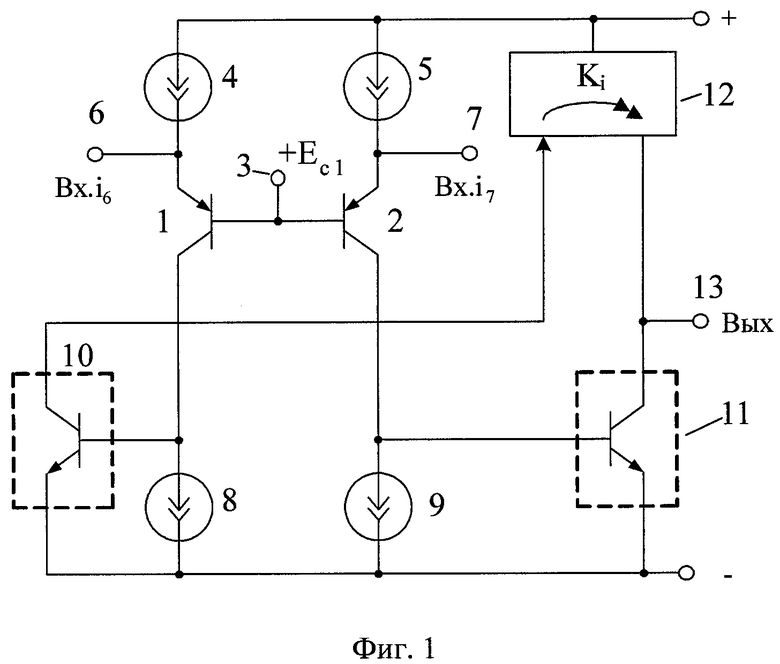

Ближайшим прототипом (фиг.1) заявляемого устройства является каскодный дифференциальный усилитель (КДУ), описанный в патенте Philips Corporation (США) №4723111, содержащий первый 1 и второй 2 входные транзисторы, объединенные базы которых подключены к источнику напряжения смещения 3, первый 4 и второй 5 токостабилизирующие двухполюсники, соединенные с соответствующими эмиттерами входных транзисторов 1 и 2 и токовыми входами 6, 7 каскодного дифференциального усилителя, первый 8 и второй 9 двухполюсники коллекторной нагрузки, соединенные с коллекторами соответствующих первого 1 и второго 2 входных транзисторов и базами первого 10 и второго 11 выходных транзисторов, выходной усилитель тока 12, вход которого подключен к коллектору первого выходного транзистора 10, а выход - связан с коллектором второго выходного транзистора 11 и выходом 13 каскодного дифференциального усилителя.

Существенный недостаток известного КДУ (фиг.1) состоит в том, что он не обеспечивает высокую стабильность статического режима выходного каскада («выходной усилитель тока 12 - второй выходной транзистор 11»), что отрицательно сказывается на его частотных характеристиках, а также работоспособности и токопотреблении при изменениях температуры и разбросе параметров элементов.

Основная цель предлагаемого изобретения состоит в повышении стабильности статического режима КДУ при сохранении главного параметра - относительно высоких значениях максимального выходного тока.

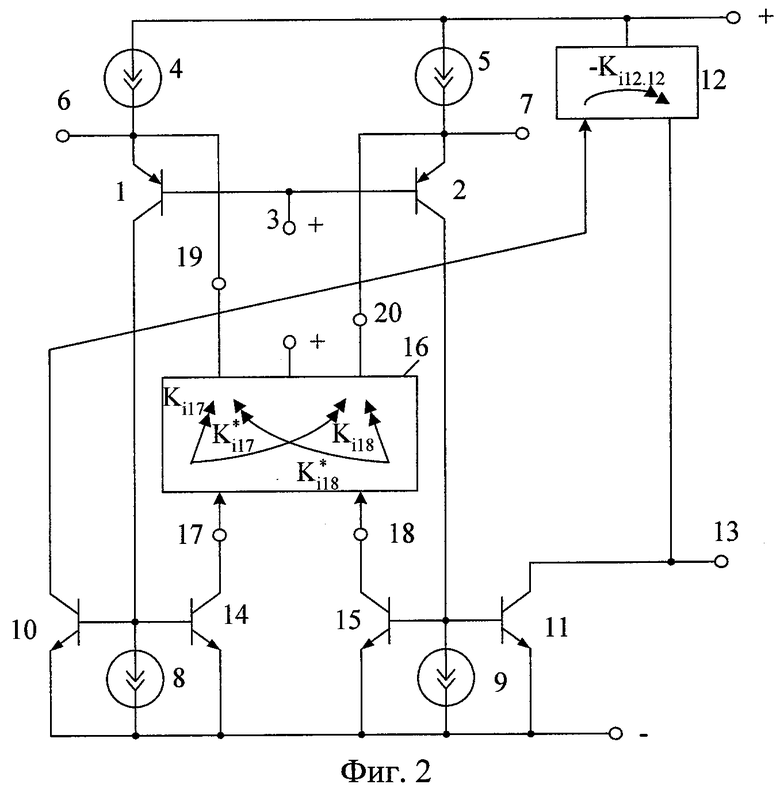

Поставленная цель достигается тем, что в каскодном дифференциальном усилителе фиг.1, содержащем первый 1 и второй 2 входные транзисторы, объединенные базы которых подключены к источнику напряжения смещения 3, первый 4 и второй 5 токостабилизирующие двухполюсники, соединенные с соответствующими эмиттерами входных транзисторов 1 и 2 и токовыми входами 6, 7 каскодного дифференциального усилителя, первый 8 и второй 9 двухполюсники коллекторной нагрузки, соединенные с коллекторами соответствующих первого 1 и второго 2 входных транзисторов и базами первого 10 и второго 11 выходных транзисторов, выходной усилитель тока 12, вход которого подключен к коллектору первого выходного транзистора 10, а выход - связан с коллектором второго выходного транзистора 11 и выходом 13 каскодного дифференциального усилителя, предусмотрены новые элементы и связи - в схему введены первый 14 и второй 15 дополнительные транзисторы, базы которых соединены с коллекторами соответствующих первого 1 и второго 2 входных транзисторов, а также нелинейный делитель тока 16, причем первый 17 вход нелинейного делителя тока 16 соединен с коллектором первого дополнительного транзистора 14, второй 18 вход нелинейного делителя тока 16 соединен с коллектором второго дополнительного транзистора 15, первый выход 19 нелинейного делителя тока 16 подключен к эмиттеру первого входного транзистора 1, второй выход 20 нелинейного делителя тока 16 подключен к эмиттеру второго входного транзистора 2.

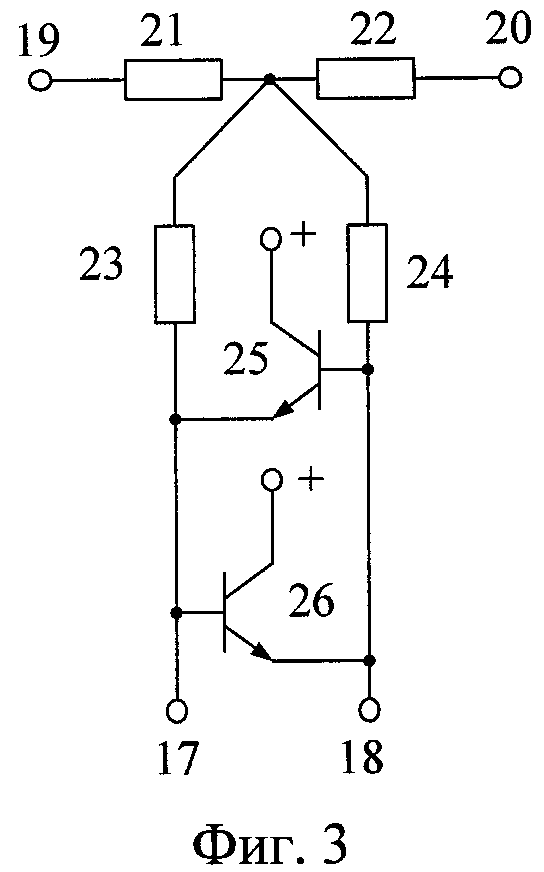

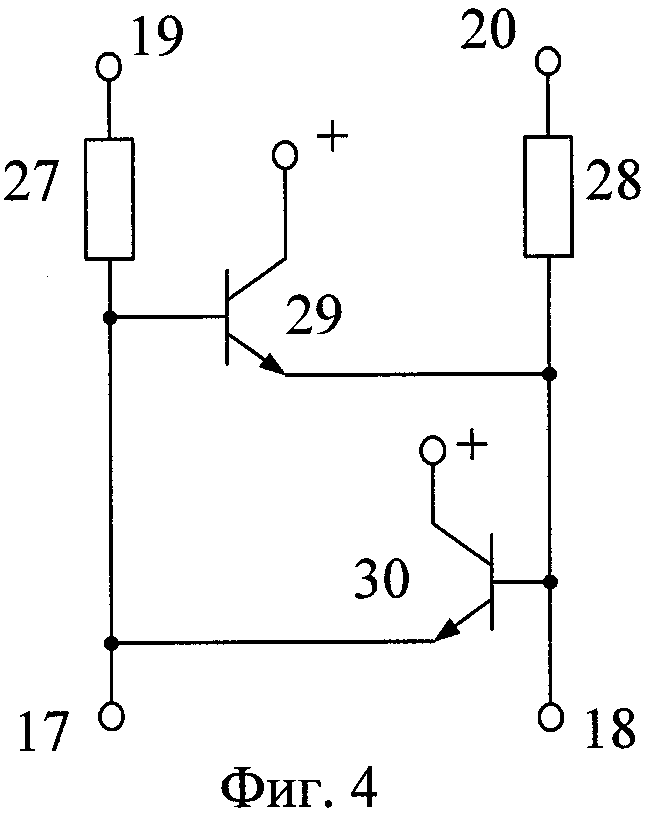

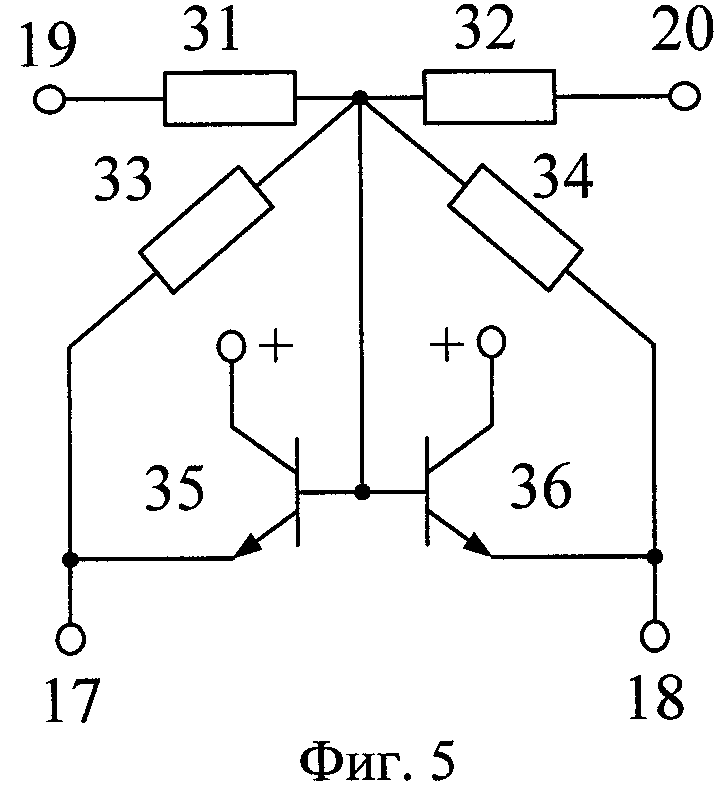

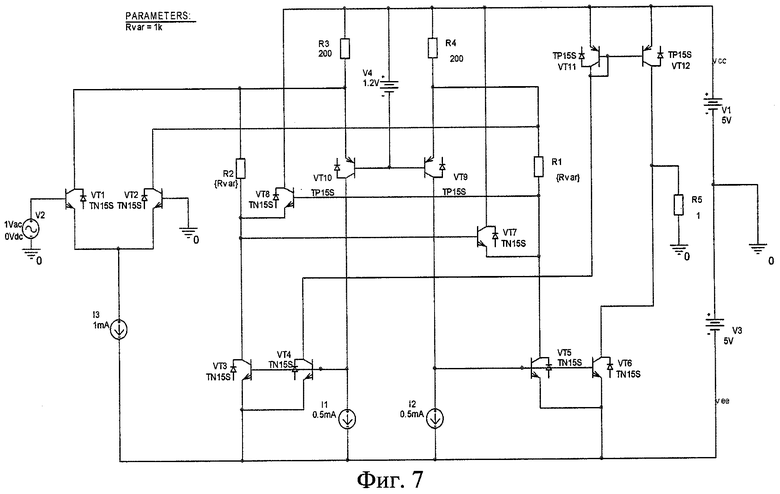

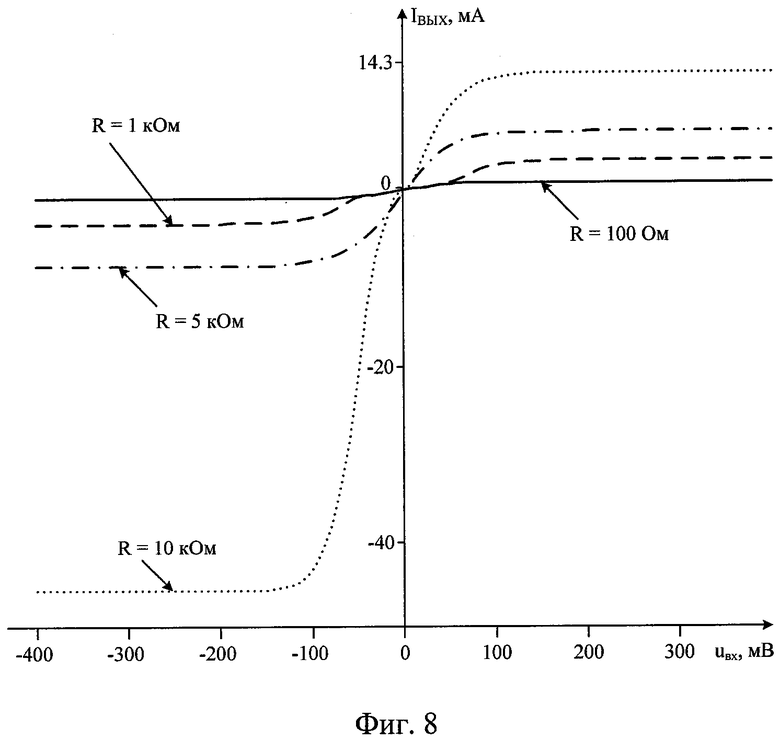

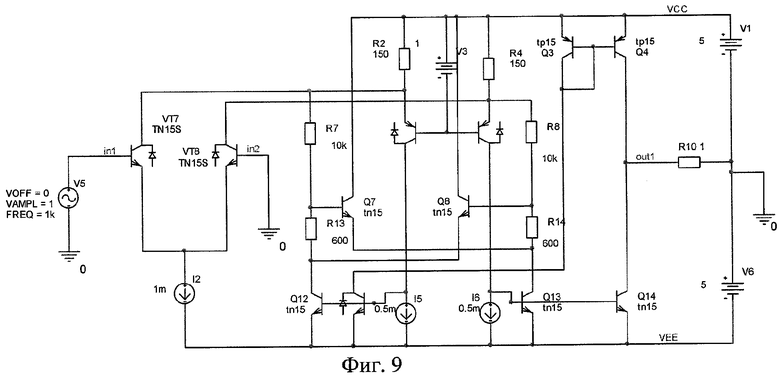

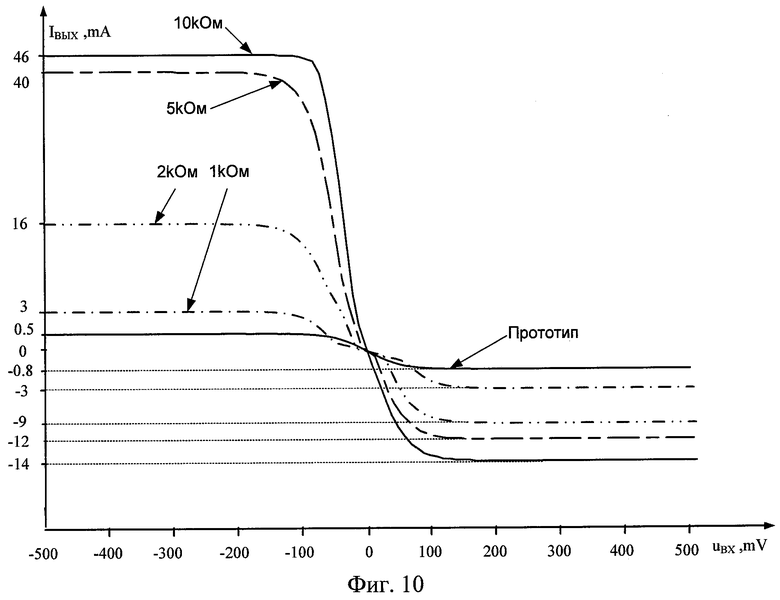

Схема усилителя-прототипа изображена на чертеже фиг.1. На чертеже фиг.2 представлена схема заявляемого устройства в соответствии с п.1 формулы изобретения. На чертежах фиг.3 - фиг.6 показаны частные варианты построения нелинейного делителя тока 16, соответствующие п.2-п.5 формулы изобретения. На чертеже фиг.7 показана схема заявляемого устройства в среде компьютерного моделирования PSpice при выполнении нелинейного делителя тока 16 в соответствии с фиг.4, а на чертеже фиг.8 - результаты компьютерного моделирования данной схемы - зависимость выходного тока от входного напряжения. На чертеже фиг.9 показана модифицированная схема фиг.7, а на чертеже фиг.10 - результаты его компьютерного моделирования.

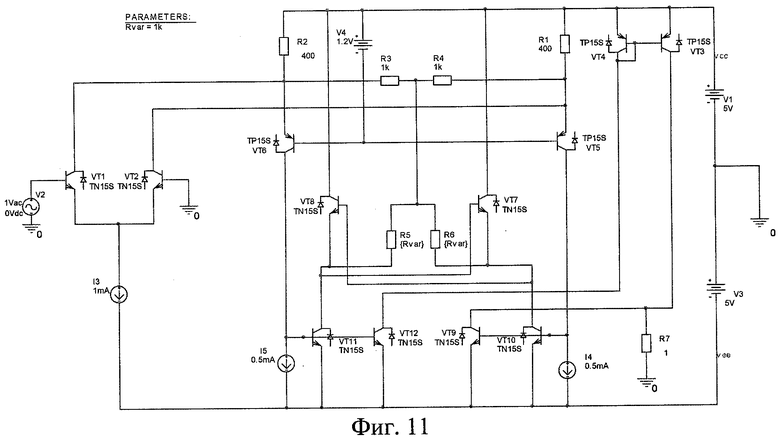

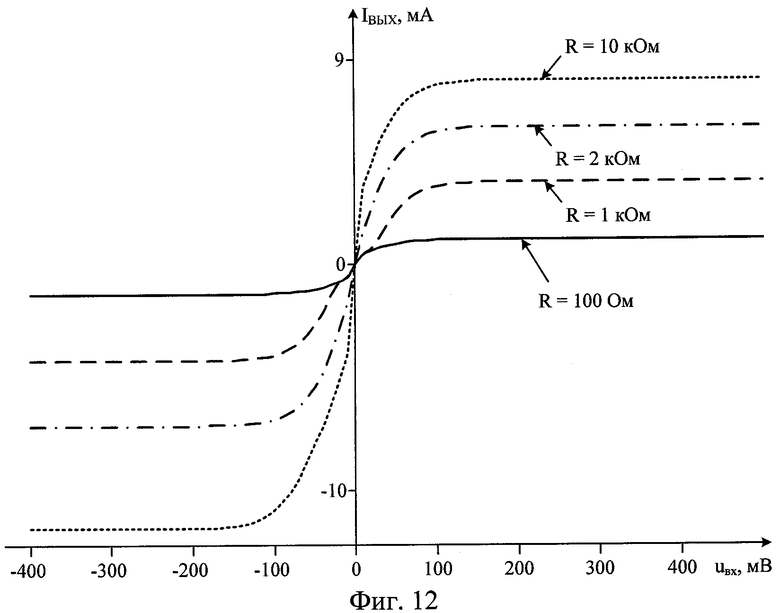

На чертеже фиг.11 изображена схема заявляемого устройства при выполнении нелинейного делителя тока в соответствии с фиг.3, а на чертеже фиг.12 - результаты компьютерного моделирования данной схемы -зависимость выходного тока от входного напряжения.

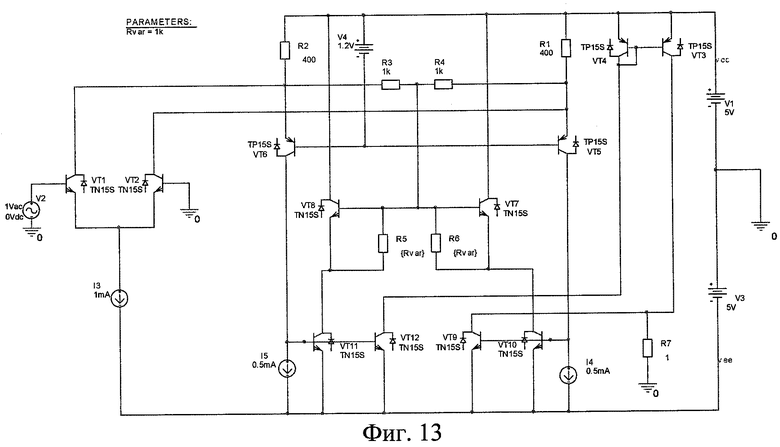

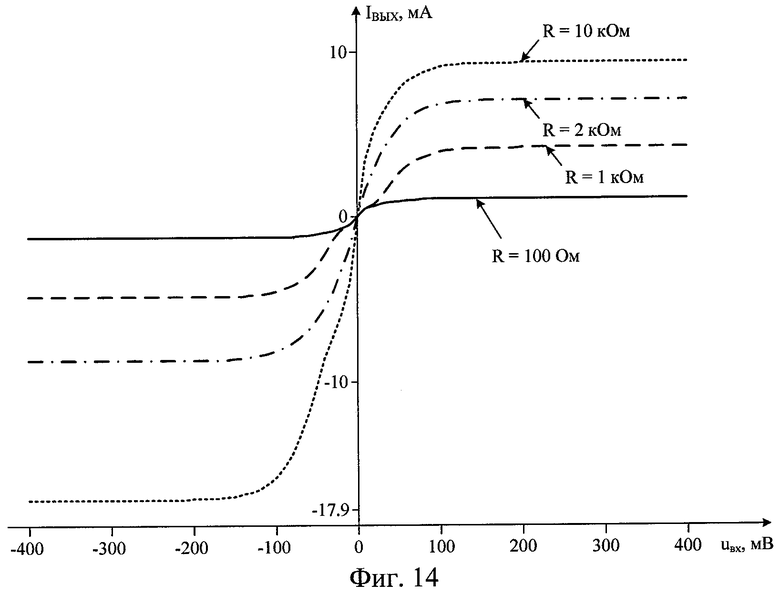

На чертеже фиг.13 приведена схема заявляемого устройства при выполнении нелинейного делителя тока в соответствии с фиг.5, а на чертеже фиг.14 - результаты ее компьютерного моделирования.

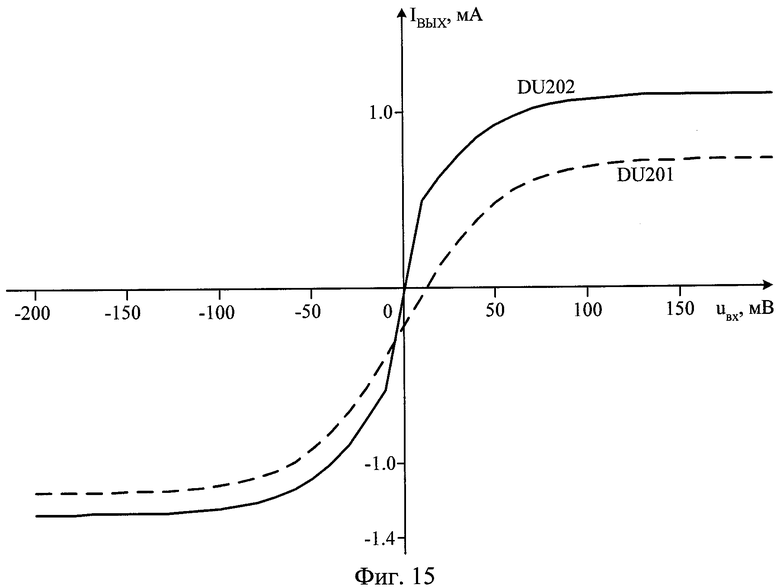

На чертеже фиг.15 дано сравнение проходных характеристик ДУ фиг.13 (DU202) и фиг.7 (DU201) при R=100 Ом, которое показывает, что схема фиг.13 имеет более высокое усиление дифференциального сигнала.

Дифференциальный усилитель фиг.2 содержит первый 1 и второй 2 входные транзисторы, объединенные базы которых подключены к источнику напряжения смещения 3, первый 4 и второй 5 токостабилизирующие двухполюсники, соединенные с соответствующими эмиттерами входных транзисторов 1 и 2 и токовыми входами 6, 7 каскодного дифференциального усилителя, первый 8 и второй 9 двухполюсники коллекторной нагрузки, соединенные с коллекторами соответствующих первого 1 и второго 2 входных транзисторов и базами первого 10 и второго 11 выходных транзисторов, выходной усилитель тока 12, вход которого подключен к коллектору первого выходного транзистора 10, а выход - связан с коллектором второго выходного транзистора 11 и выходом 13 каскодного дифференциального усилителя. В схему введены первый 14 и второй 15 дополнительные транзисторы, базы которых соединены с коллекторами соответствующих первого 1 и второго 2 входных транзисторов, а также нелинейный делитель тока 16, причем первый 17 вход нелинейного делителя тока 16 соединен с коллектором первого дополнительного транзистора 14, второй 18 вход нелинейного делителя тока 16 соединен с коллектором второго дополнительного транзистора 15, первый выход 19 нелинейного делителя тока 16 подключен к эмиттеру первого входного транзистора 1, второй выход 20 нелинейного делителя тока 16 подключен к эмиттеру второго входного транзистора 2.

На чертеже фиг.3 в соответствии с п.2 формулы изобретения нелинейный делитель тока 16 выполнен на основе первого 21, второго 22, третьего 23 и четвертого 24 дополнительных резисторов, первого 25 и второго 26 вспомогательных транзисторов, причем все дополнительные резисторы 21, 22, 23, 24 имеют общую точку, левый вывод первого дополнительного резистора 21 соединен с первым выходом 19 нелинейного делителя тока 16, правый вывод второго дополнительного резистора 22 соединен со вторым выходом 20 нелинейного делителя тока 16, левый вывод третьего дополнительного резистора 23 соединен с первым входом 17 нелинейного делителя тока 16, правый вывод четвертого дополнительного резистора 24 соединен со вторым входом 18 нелинейного делителя тока 16, эмиттер первого 25 вспомогательного транзистора подключен к первому входу 17 нелинейного делителя тока 16 и базе второго 26 вспомогательного транзистора, база первого 25 вспомогательного транзистора соединена с эмиттером второго 26 вспомогательного транзистора и вторым входом 18 нелинейного делителя тока 16.

На чертеже фиг.4 в соответствии с п.3 формулы изобретения нелинейный делитель тока 16 выполнен на основе пятого 27 и шестого 28 дополнительных резисторов, третьего 29 и четвертого 30 вспомогательных транзисторов, причем пятый 27 дополнительный резистор включен между первым входом 17 и первым выходом 19 нелинейного делителя тока 16, шестой 28 дополнительный резистор включен между вторым выходом 20 и вторым входом 18 нелинейного делителя тока 16, база третьего 29 вспомогательного транзистора соединена с эмиттером четвертого 30 вспомогательного транзистора и первым входом 17 нелинейного делителя тока, эмиттер третьего 29 вспомогательного транзистора соединен с базой четвертого 30 вспомогательного транзистора и вторым входом 18) нелинейного делителя тока 16.

На чертеже фиг.5 в соответствии с п.4 формулы изобретения нелинейный делитель тока 16 выполнен на основе седьмого 31, восьмого 32, девятого 33 и десятого 34 дополнительных резисторов, пятого 35 и шестого 36 вспомогательных транзисторов, причем седьмой 31, восьмой 32, девятый 33, десятый 34 дополнительные резисторы имеют общую точку, левый вывод седьмого дополнительного резистора 31 соединен с первым выходом 19 нелинейного делителя тока 16, правый вывод восьмого дополнительного резистора 32 соединен со вторым выходом 20 нелинейного делителя тока 16, левый вывод девятого дополнительного резистора 33 подключен к первому входу 17 нелинейного делителя тока 16 и эмиттеру пятого 35 вспомогательного транзистора, правый вывод десятого дополнительного резистора 34 подключен ко второму входу 18 нелинейного делителя тока 16 и эмиттеру шестого 36 вспомогательного транзистора, базы пятого 35 и шестого 36 вспомогательных транзисторов подключены к общей точке седьмого 31, восьмого 32, девятого 33 и десятого 34 дополнительных резисторов.

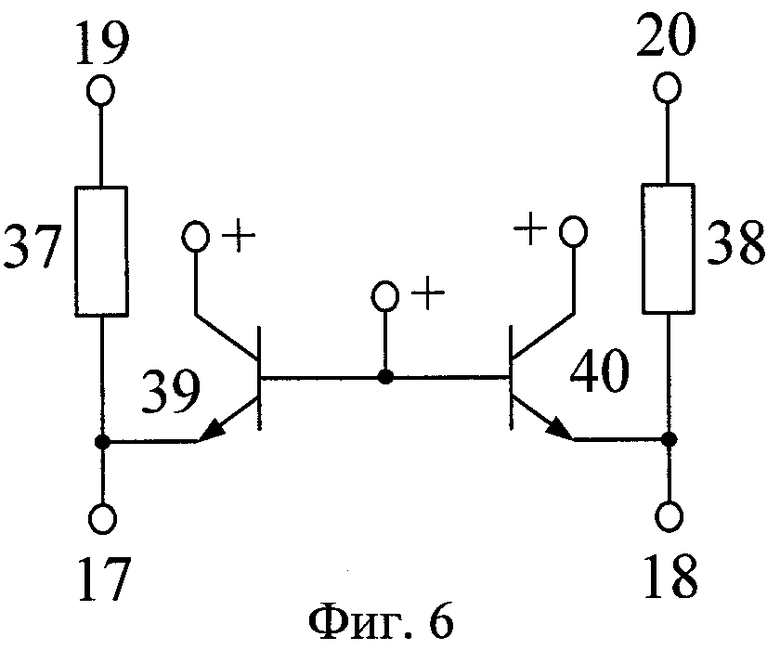

На чертеже фиг.6 в соответствии с п.5 формулы изобретения нелинейный делитель тока 16 выполнен на основе одиннадцатого 37 и двенадцатого 38 дополнительных резисторов, седьмого 39 и восьмого 40 вспомогательных транзисторов, причем одиннадцатый 37 дополнительный резистор включен между первым входом 17 и первым выходом 19 нелинейного делителя тока 16, двенадцатый 38 дополнительный резистор включен между вторым выходом 20 и вторым входом 18 нелинейного делителя тока 16, база седьмого 39 вспомогательного транзистора соединена с базой восьмого 40 вспомогательного транзистора и дополнительным источником питания 41, эмиттер седьмого 39 вспомогательного транзистора соединен с первым входом 17 нелинейного делителя тока 16, а эмиттер восьмого вспомогательного транзистора 40 подключен ко второму входу нелинейного делителя тока 16.

Рассмотрим в начале особенности работы КДУ - прототипа (фиг.1).

На входы 6 и 7 КДУ фиг.1 подается токовый сигнал, например, от входного дифференциального каскада (на схеме не показан). Первый (8) и второй (9) двухполюсники коллекторной нагрузки, а также первый (4) и второй (5) токостабилизирующие двухполюсники определяют статический режим КДУ, который отличается высокой нестабильностью. Например, если ток двухполюсника в 8 (9) меньше, чем статический ток коллектора транзистора 1 (2), зависящий от чистых значений тока двухполюсника 4 (5), то транзистор 10 (11) закрывается (переходит в режим микротоков). В данном состоянии все основные высокочастотные усилительные параметры транзисторов деградируют, что отрицательно сказывается на частотных характеристиках аналоговых микросхем на основе КДУ фиг.1.

С другой стороны небольшое уменьшение тока двухполюсника 8 (9) (под действием температуры или изменения напряжений питания) относительно тока коллектора транзистора 1 (2) вызывает увеличение тока базы транзистора 10 (11). Это приращение тока базы усиливается в β10 (β11) раз транзистором 10 (11) и передается на выход 13 каскада, где β10 (β11) >>1 - коэффициент усиления тока базы транзистора 10 (11). Однако небольшое синфазное уменьшение токов двухполюсников 8 и 9 переводит транзисторы 10 и 11 в открытое состояние, что создает большой сквозной ток между шиной положительного и отрицательного источников питания по цепи «выходной усилитель тока 12 - транзистор 11». Предельная величина этого сквозного тока может достигать десятков - сотен миллиампер, что неприемлемо для большинства применений. Следовательно, схема фиг.1 требует юстировки (обеспечения высокой идентичности) токов двухполюсников 8 и 9 (4 и 5), что также неприемлемо. Таким образом, в рамках известного технического решения (фиг.1) неудовлетворительно решается задача обеспечения высокого диапазона рабочих частот, стабильности статического режима (сквозного тока) и, как следствие, надежности КДУ и аналоговых интерфейсов на его основе.

В заявляемой схеме созданы специальные условия, разделяющие работу КДУ на две режимные области. Первая область - это статический режим и режим малых сигналов (Uвх=5÷20 мВ), когда за счет нелинейного делителя тока 16 в схеме фиг.2 обеспечивается отрицательная обратная связь, стабилизирующая сквозной ток выходного каскада и все статические токи в транзисторах схемы.

Вторая область - это режим усиления больших сигналов Uвх=20÷50 мВ, когда изменения коллекторных токов транзисторов 14 и 15 передаются в эмиттеры транзисторов 1 и 2 с уменьшенным усилением, которое обеспечивается нелинейным делителем тока 6 (Ki18<<l, Кi17<<1), где Кi17, Ki18 - коэффициенты передачи по току подсхемы 6.

В результате отрицательная обратная связь, ранее стабилизировавшая статический режим транзисторов схемы фиг.2 в статическом режиме, а также при малых сигналах, выключается и схема фиг.2 при Uвх=20÷50 мВ приобретает свойства КДУ-прототипа фиг.1, который также не имеет обратной связи. Как следствие в КДУ фиг.2 обеспечивается, как и в КДУ фиг.1, большие уровни выходного тока. Однако это происходит при высокой стабильности статического режима.

Компьютерное моделирование подтверждает преимущества

предлагаемого технического решения.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №6304143.

2. Патент США №5418491.

3. Патент США №4463319.

4. Патент США №6717474.

5. Патент США №6734720.

6. Патент США №4723111.

7. Патент США №4293824.

8. Патент США №5323121.

9. Патент США №5091701.

10. Патент США №4406990.

11. Патент США №5422600.

12. Патент США №6788143.

13. Патент США №4274061.

14. Патент США №5327100.

15. Патент США №5786729.

16. Патент США №3644838.

17. Патент США №4600893.

18. Патент США №4390850.

19. Патент США №6628168.

20. Матавкин В.В. Быстродействующие операционные усилители. - М. Радио и связь, 1989. - с.74, рис.4.15, стр.98, рис.6.7.

21. Патент США №6218900, фиг.1.

22. Патентная заявка US 2002/0196079.

23. Патент США Re 30587.

24. Патент ЕР1.227580.

25. Патент США №6714076.

26. Патентная заявка US 2004/0090268 A1.

27. Патент США №4959622, фиг.1.

28. Патент США №6018268.

29. Патент США №5952882.

30. Патент США №6580325.

31. Патент США №6965266.

32. Патент США №6867643.

33. Патент США №6236270.

34. Патент США №6229394.

35. Патент США №5734296.

36. Патент США №5477190.

37. Патент США №6084475.

38. Патент США №3733559.

39. Патентная заявка US 2005/0001682 А1.

40. Патент США №6300831.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВУХТАКТНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2007 |

|

RU2337469C1 |

| КОМПЛЕМЕНТАРНЫЙ ДВУХТАКТНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2370879C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2469465C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2374757C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2007 |

|

RU2349023C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2468502C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2390912C2 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2439780C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2321159C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2354041C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ)). Технический результат: повышение стабильности статического режима при сохранении высоких значений максимального выходного тока. Каскодный дифференциальный усилитель (КДУ) содержит первый (1) и второй (2) входные транзисторы (Т), объединенные базы которых подключены к источнику напряжения смещения 3, первый 4 и второй 5 токостабилизирующие двухполюсники (ТД), соединенные с соответствующими эмиттерами Т (1) и (2) и токовыми входами (6, 7) КДУ, первый (8) и второй (9) двухполюсники коллекторной нагрузки, соединенные с коллекторами соответствующих первого (1) и второго (2) Т и базами первого (10) и второго (11) выходных Т, выходной усилитель тока (12), вход которого подключен к коллектору первого Т (10), а выход - связан с коллектором второго Т (11) и выходом (13) КДУ. В схему введены первый (14) и второй (15) дополнительные Т, базы которых соединены с коллекторами соответствующих первого (1) и второго (2) Т, а также нелинейный делитель тока (НДТ) (16), причем первый (17) вход НДТ (16) соединен с коллектором первого Т (14), второй (18) вход НДТ (16) соединен с коллектором второго Т (15), первый выход (19) НДТ (16) подключен к эмиттеру первого Т (1), второй выход (20) НДТ (16) подключен к эмиттеру второго Т (2). 4 з.п. ф-лы, 15 ил.

| US 4723111, 02.02.1988 | |||

| Каскодный дифференциальный усилитель | 1980 |

|

SU1164865A1 |

| US 6229394 B1, 08.05.2001 | |||

| US 5748040 A, 05.05.1998 | |||

| US 5455535 A, 03.10.1995. | |||

Авторы

Даты

2009-03-10—Публикация

2007-09-04—Подача