Изобретение относится к бытовой цифровой видеотехнике, может быть использовано для записи и воспроизведения видеоинформации. Аналогом является "Цифровая видеокамера" [1], содержащая объектив, фотоэлектрический преобразователь /ФЭП/, три АЦП видеосигнала, задающий генератор и синтезатор частот, четыре блока элементов И, накопитель цифровой информации, видеоискатель и устройство воспроизведения, включающее три канала обработки кодов R, G, В, блок модуляции излучений, блоки строчной и кадровой развертки, проекционный объектив и матовый экран. Построение кадра выполняется электронно-оптической разверткой двух модулированных по яркости лучей с проецированием их объективом на матовый экран, не обладающий свойством послесвечения. Недостатки аналога: низкая яркость изображения на экране и недостаточное разрешение кадра /800стр×1000отсч/.

Прототипом принята "Цифровая видеокамера" [2], содержащая объектив, ФЭП, включающий два усилителя, два пьезодефлектора, источники опорных напряжений, два дихроичных зеркала, три микрообъектива, три фотоприемника, три предварительных усилителя и блоки строчной и кадровой разверток, содержащая три АЦП видеосигнала, АЦП сигнала звука, четыре блока элементов И, задающий генератор и синтезатор частот, накопитель цифровой информации, видеоискатель и устройство воспроизведения, включающее задающий генетор и синтезатор частот, ключ, три канала обработки кодов сигналов R, G, В, каждый из которых содержит регистр, блок обработки кодов, первый блок задержек, сумматор и первый накопитель кодов кадра, второй блок задержек и второй накопитель кодов кадра, включающее с первого по шестой блоки импульсных усилителей, блок модуляции излучений, блок строчной развертки, проекционный объектив и матовый экран, устройство воспроизведения содержит регистр сигнала звука, блок формирования аналового сигнала /из ЦАП, фильтра низкой частоты и усилителя мощности/ и громкоговоритель. Видеорежим при регистрации видеоинформации 400строк×500отсч×25 Гц, видеорежим при воспроизведении 800строк×1000отсч×25 Гц, разрешение кадра 1000×800=800000 пикселов.

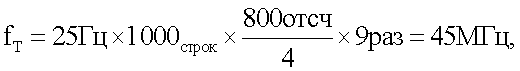

Недостатки прототипа: сложность конструкции фотоэлектрического преобразователя, требующего сохранения прецизионной юстировки при эксплуатации, сложность узла модуляции излучений и электронно-оптической развертки, недостаточное разрешение кадра /1000×800/, запись видеоинформации без ее сжатия ограничивает рабочее время использование видеокамеры. Цель изобретения - упрощение ФЭП, сжатие потока получаемой видеоинформации и увеличение разрешения кадра. Техническими результатами являются упрощение ФЭП исключением из него пьезодефлекторов, усилителей, источников опорных напряжений, блоков строчной и кадровой разверток и введением в него матрицы ПЗИ /прибора с зарядовой инжекцией по технологии ХЗ [3 с.552]/, сжатие видеоинформации с коэффициентом не менее 4 за каждый кадр введением трех кодеров до накопителя цифровой информации и трех декодеров в устройство воспроизведения, увеличение разрешения кадра в два раза 1,6×106 против прототипа. Видеорежим при получении видеоинформации 1000×800×25 Гц, где: 1000 - число кодируемых строк кадра, 800 - число кодируемых отсчетов в строке, 25 Гц - частота кадров. Частота дискретизации при аналого-цифровом преобразовании: fАЦП=1000× 25 Гц×800=20 МГц. Частота отрок 25 кГц /25 Гц×1000/. Наименьший коэффициент сжатия потока кодов кадра принимается 4. Частота дискретизации кодов после сжатия информации составляет 5 МГц /20 МГц:4/. Тактовая частота при следовании кодов в последовательном виде:

где:  - число отсчетов в отроке сжатого потока кодов,

- число отсчетов в отроке сжатого потока кодов,

9раз- число разрядов в коде на выходе кодера. Период следования кодов с АЦП составляет 50 нс. Видеорежим при воспроизведении 1600×1000×25 Гц, где: 1600 - число отсчетов в строке после удвоения, 1000 - число строк в кадре, 25 Гц - частота кадров. Разрешение кадра при воспроизведении 1600×1000, 1,6×106 пикселов.

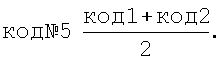

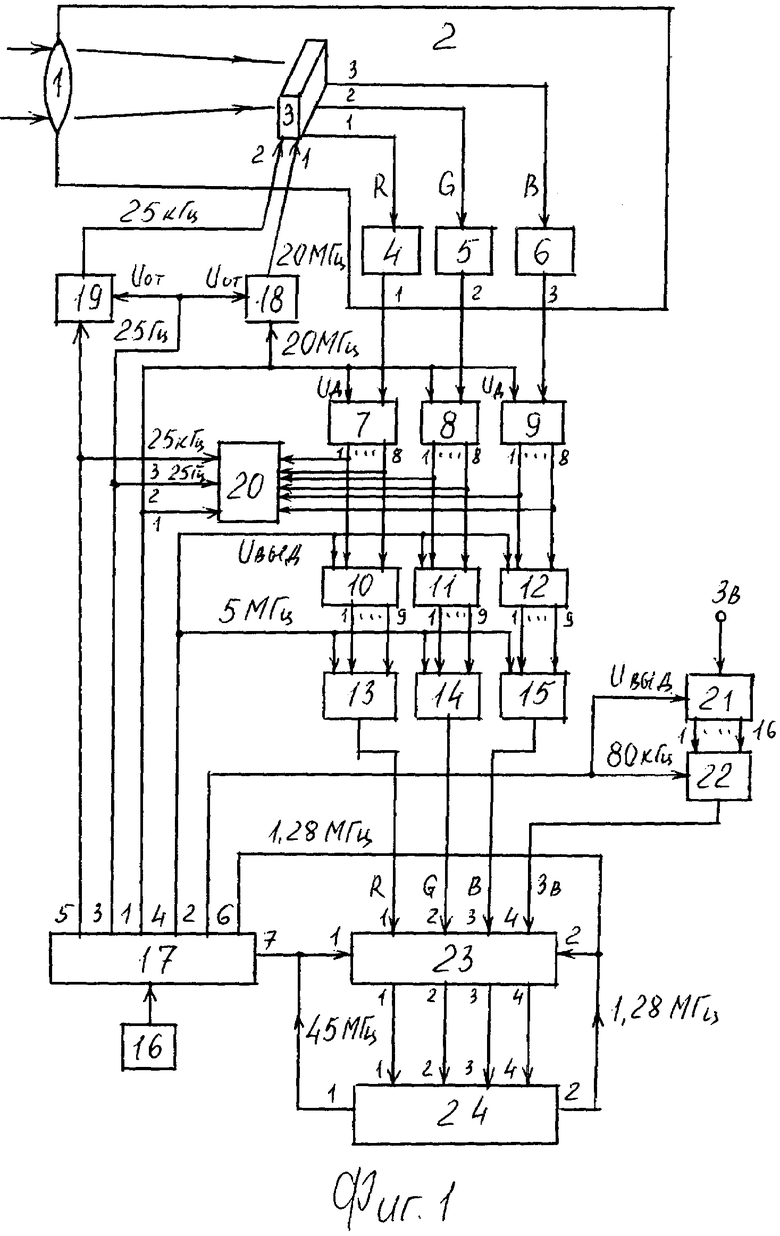

Сущность изобретения в том, что в видеокамеру, содержащую объектив, фотоэлектрический преобразователь, включающий три предварительных усилителя, содержащую три АЦП видеосигнала, АЦП сигнала звука, четыре блока элементов И, накопитель цифровой информации и устройство воспроизведения, включающее три канала обработки кодов R, G, В, вводятся матрица ПЗИ в фотоэлектрический преобразователь, три кодера, ключ, а в каждый канал устройства воспроизведения декодер и формирователь управляющих сигналов, а устройство отображения видеоинформации представляется плоскопанельным светодиодным экраном /СД-экраном/. Структурная схема видеокамеры на фиг.1, устройство воспроизведения на фиг,2, кодер на фиг.3, диаграммы работы кодера на фиг,4, блок элементов И на фиг.5, декодер на фиг.6, блок обработки кодов на фиг.7, накопитель кодов кадра на фиг.8, блок регистров на фиг,9, 10, формирователь управляющих сигналов на фиг.11, CD-ячейка на фиг.12, излучающий элемент на фиг, 13, расположение излучающих элементов в СД-экране на фиг.14. Видеокамера включает /фиг.1/ объектив 1, фотоэлектрический преобразователь /ФЭП/2, являющийся датчиком трех основных цветов R, G, В, включающий матрицу ПЗИ 3 /прибор с зарядовой инжекцией/, выполненную по технологии Foreon X3 из трехслойного КМОП-датчика [3, с.552, 4, с.832-835] о оптическим разрешением 800×1000, обеспечивающую 24-битную глубину цвета [4, c.835], фоточувствительная сторона метрипы ПЗИ 3 расположена в фокальной плоскости объектива 1, с первого по третий выходы матрицы ПЗИ 3 подключены соответственно к входам предварительных усилителей ФЭП 4/R/, 5/G/, 6/В/. Видеокамера включает первый 7, второй 8, третий 9 АЦП видеосигнала R, G, В, которые выполнены идентично АЦП в аналоге [1, с.4 фиг.5], первый 10, второй 11, третий 12 кодеры, первый 13, второй 14, третий 15 блоки элементов И, задающий генератор 16 и синтезатор 17 частот, первый 18 и второй 19 ключи, видеоискатель 20 с ЖК-дисплеем, АЦП 21 сигнала звука, который выполнен идентично АЦП сигнала звука в аналоге [1, с.4 Фиг.6], блок 22 элементов И /четвертый/, накопитель 23 цифровой информации и устройство 24 воспроизведения, содержащее /фиг.2/ задающий генератор 25 и синтезатор 26 частот, ключ 27, и три канала обработки кодов R, G, В, канал обработки кодов R включает последовательно соединенные декодер 28, блок 29 обработки кодов /удвоения/, накопитель 30 кодов кадра и формирователь 31 управляющих сигналов, канал обработки кодов G включает последовательно соединенные декодер 32, блок 33 обработки кодов, накопитель 34 кодов кадра и формирователь 35 управляющих сигналов, канал обработки кодов В включает последовательно соединенные декодер 36, блок 37 обработки кодов, накопитель 38 кодов кадра и формирователь 39 управляющих сигналов. Устройство воспроизведения включает плоскопанельный светодиодный экран 40 /СД-экран/ и последовательно соединенные регистр 41 сигнала звука, блок 42 формирования аналового звукового сигнала из ЦАП, фильтра низкой частоты и усилителя мощности и громкоговоритель 43. Кодеры 10, 11, 12 идентичны, каждый включает /фиг.3/ последовательно соединенные регистр 44, схему сравнения 45 /компаратор/, счетчик 46 импульсов и дешифратор 47, последовательно соединенные блок 48 элементов задержек, блок 49 ключей и буферный накопитель 50 кодов кадра. Информационными входами являются поразрядно объединенные первый-восьмой входы регистра 44, первые входы схемы 45 сравнения и входы блока 48 элементов задержек. Выходами являются с первого по девятый выходы буферного накопителя 50 кодов кадра, объем которого составляет 200×103 девятиразрядных кодов кадра. Управляющим входом является управляющий вход блока 50. Блоки 13, 14, 15 элементов И /Фиг.5/ выполнены соответственно блокам элементов И в аналоге [1, c.5 Фиг.12], выполняют преобразование параллельных кодов в последовательные перед поступлением их в накопитель 23 цифровой информации. Каждый из блоков 10, 11, 12 включает по девять элементов ИI…И9, самоходный распределитель импульсов /СРИ/ и элемент ИЛИ. Импульс пуска Uп 5 МГц поступает с четвертого выхода блока 17. Блок 22 элементов И содержит 16 элементов И /по числу разрядов в коде/, СРИ и элемент ИЛИ. Импульсом пуска Uп являются импульсы 80 кГц со второго выхода блока 17. Декодеры 28, 32, 36 идентичны, каждый включает /фиг.6/ последовательно соединенные первый /девятиразрядный/ регистр 51, накопитель 52 кодов кадра емкостью 200×103 девятиразрядных кодов, второй /девятиразрядный/ регистр 53, первый блок 54 ключей из восьми ключей и третий /восьмиразрядный/ регистр 55, последовательно соединенные второй блок 56 ключей из восьми ключей, восьмиразрядный вычитающий счетчик 57 импульсов и дешифратор 58, первый 59, второй 60, третий 61 и четвертый 62 ключи. Информационным входом является информационный вход первого регистра 51, выходами являются первый-восьмой выходы третьего регистра 55. Управляющими входами являются: первым - первый управляющий вход /Uт 45 МГц/ первого регистра 51, вторым - объединенные второй управляющий вход /5 МГц/ регистра 51 и сигнальный вход третьего ключа 61, третьим - объединенные сигнальные входы /20 МГц/ ключей первого 59, второго 60, четвертого 62. Блоки 29, 33, 37 обработки /удвоения/ кодов идентичны, каждый включает /Фиг.7/ [1 c.5, 9 фиг. 10] триггер 63, первый 64, второй 65 блоки ключей /по В ключей в каждом/, первый 66, второй 67, третий 68, четвертый 69 регистры, сумматор 70, пятый 71 и шестой 72 регистры, выполняющие хранение кодов по 50 нс, и 16 диодов. Информационным входом являются поразрядно объединенные с 1 по 8 входы блоков 64, 65 ключей, на которые в параллельном виде поступают коды цветового сигнала с частотой 20 МГц. Управляющим входом являются объединенные вход триггера 63 и управляющий вход сумматора 70. Выходами являются поразрядно объединенные выходы 0-7 сумматора 70, выходы 1-8 пятого 71 и шестого 72 регистров. С выходов блоков 29, 33, 37 коды в параллельном виде следуют с частотой 40 МГц в накопители кодов кадра соответственно 30, 34, 38. Накопители кодов кадра идентичны /Фиг.8/, каждый включает последовательно соединенные блоки 73 регистров, которых по числу строк в кадре, т.е. 731-1000. Информационным входом накопителя кодов кадра являются поразрядно объединенные /1-8/ входы всех блоков 731-1000 регистров. Выходами являются выходы всех блоков 73 регистров, всего выходов 12,8×106/1600×8×1000/. Управляющими входами являются: первым - первый управляющий вход /25 Гц/ первого блока 73 регистров, вторым - объединенные вторые управляющие входы /Uвыд25 кГц/ блоков 73, третьим - третьи управляющие входы /Uд 40 МГц/ блоков 73 регистров. Управляющий выход каждого предыдущего блока 73 регистров является первым управляющим входом для каждого последующего блока 73. Управляющий выход последнего /1000-ного/ блока 73 регистров подключен параллельно к четвертым управляющим входам всех блоков 73 регистров. Блоки 73 регистров идентичны, каждый включает /Фиг.9, 10/ первый 74 и второй 75 ключи, распределитель 76 импульсов и восемь регистров 771-8, каждый из которых содержит по 1600 разрядов, по числу отсчетов в строке. Информационными входами блока регистров являются поразрядно объединенные с первого по восьмой третьи входы разрядов восьми регистров 77. Выходами являются параллельные выходы всех разрядов восьми регистров 77, всего выходов с блока 73 12800 /1600×8/. Выходы 1000 блоков 73 являются выходами каждого накопителя 30, 34, 38 кодов кадра 12,8×I06 /12800×1000/. Управляющими входами являются: первым - первый управляющий вход /25 Гц/ первого ключа 74, вторым - сигнальный вход /Uвыд 25 кГц/ второго ключа 75, третьим - сигнальный вход /Uд 40 МГц/ первого ключа 74, четвертым - первый управляющий вход второго ключа 75. Выход ключа 74 подключен к входу распределителя 76 импульсов, выходы которого последовательно с первого по 1600-й подключены к первым /тактовым/ входам разрядов параллельно восьми регистров 77. Последний выход блока 76 подключен к второму управляющему входу первого ключа 74 и является управляющим выходом блока 73 и подключен к первому управляющему входу первого ключа 74 в следующем блоке 732 регистров. Выход второго ключа 75 подключен параллельно к вторым входам разрядов восьми регистров 77 и к второму управляющему входу своего ключа 75, прошедшие один импульс Uвыд закрывает ключ 75. Выходы накопителей 30, 34, 38 кодов кадра подключены /фиг.2/ к информационным входам своих формирователей 31, 35, 39 управляющих сигналов, назначение которых выполнять преобразование "код - число импульсов излучений" для получения скважности излучения светодиодов в периоде кадра соответственно величине кода цветового сигнала. Каждый из блоков 31, 35, 39 включает /Фиг.11/ блок 78 Формирователей импульсов, содержащий идентичные схемы формирования импульсов по числу преобразователей 1,6×106 и вход которого является управляющим входом /Uк 25 Гц/ формирователя управляющих сигналов, и содержит преобразователи "код - число импульсов излучений" по числу отсчетов в строке 1600 и числу строк в кадре 1000, т.е. 1,6×106. Преобразователи идентичны, каждый включает /Фиг.11/ последовательно соединенные дешифратор 79, информационные входы 1-8 которого являются информационными входами формирователя 31 управляющих сигналов, блок 80 ключей из 255 ключей и выходной ключ B1, включает также самоходный распределитель 82 импульсов /СРИ/ и источник 83 питания для своего светодиода в СД-экране. Выходы дешифратора 79 подключены к первым управляющим входам UОТ соответствующих ключей в блоке 80 ключей, выходы ключей которого объединены и объединенный выход подключен к управляющему входу Uот выходного ключа 8I, сигнальный вход которого подключен к выходу источника 83 питания. Вход СРИ 82 подключен к своему выходу в блоке 78 формирователей импульсов, СРИ 82 имеет 255 разрядов, выходы которых подключены к сигнальным входам соответствующих 255 ключей в блоке 80 /вход 2/. Информационными входами блока 31 /35, 39/ являются информационные входы всех дешифраторов 79, выходы всех выходных ключей 81 являются выходами блока 31, которые подключены к соответствующим входам СД-экрана 40. Исходное состояние выходных ключей 81 и ключей в блоках 80 закрытое. На управляющий вход блока 31 /35, 39/ поступает сигнал UK 25 Гц, который поступает параллельно на входы всех схем формирователей импульсов, формирующих импульсы соответствующей амплитуды и длительности, являющиеся пусковыми Uп для СРИ 82. Каждый импульс с блока 80 ключей открывает выходной ключ 81 на время 156 мкс tот=40мс:255=156 мкс, 40 мс - длительность кадра, 255 -разрешение 8-разрядного кода, число выходов с блока 82. С приходом кода в дешифратор 79 сигналы с его выходов открывают соответствующие ключи в блоке 80, которые последовательно пропускают на выход блока 80 с соответствующих разрядов СРИ 82 сигналы Uот в выходной ключ 81, и светодиод в экране 40 за период кадра выдает соответствующее число импульсов излучений через равные интервалы за период кадра. Чем больше код, тем больше импульсов излучений выдает светодиод за период кадра. Пример распределения ипульсов излучений соответственно величинам кодов в таблице 1.

Следование излучений в периоде кадра через равные интервалы времени создают наилучшие условия для восприятия зрением человека яркости изображения и достоверности цветопередачи. Инерционность срабатывания светодиодов должна быть до 1 мкс. По окончании накопления кодов кадра блоками 30, 34, 38 все коды сигналов R, G, В синхронно выдаются в формирователи 31, 35, 39 управляющих сигналов, где коды преобразуются в число подач напряжения питания на светодиоды СД-экрана. Современные технологии позволяют выполнить каждый из блоков 30, 31, 34, 35, 38, 39 в одной микросхеме. Плоскопанельный светодиодный экран 40 представляет совокупность излучающих элементов в матрице по числу разрешения кадра 1,6×106, которые выполняются в стекле. СД-экран включает экранное стекло и матрицу из излучающих элементов по числу разрешения кадра. Каждый излучающий элемент включает три светодиодных ячейки /СД-ячейки/, каждая из которых излучает один из основных цветов R, G, B. СД-ячейка содержит /фиг. 12/ светодиод 84 белого свечения и соответствующий цветовой светофильтр 85. Три СД-ячейки составляют излучающий элемент матрицы /фиг.13/, расположение элементов матрицы и СД-ячеек в СД-экране 40 на фиг.14. Уровень яркости излучения СД-ячейки пропорционален числу импульсов светодиода за период кадра, импульсов может быть от 1 до 255, т.е. от 156 мкс до 40000 мкс. Суммарное излучение трех основных цветов тремя СД-ячейками формирует яркость и цветовой тон одного пиксела экрана. В качестве светодиодов могут применяться сверхъяркие светодиоды типа производимых фирмами «Nichia», «Ledtronies», «Kingbright» [5, c.47], но диаметром в 0,5 мм /фиг. 12/ или светодиоды, разрабатываемые по технологии PLED, использующей светодиоды с полимерными органическими молекулами [6, c.43]. Светодиоды исполняются в стекле методом микроэлектронной технологии. Размер одного излучающего элемента 1×1 мм /фиг.13/. Размер СД-экрана составляет: по горизонтали 1600×1 мм=1600мм,

по вертикали 1000×1 мм=1000,

по диагонали 188 см, или 74 дюйма.

Фотоэлектрический преобразователь 2 матрицей ПЗИ 3 формирует три аналоговых сигнала основных цветов R, G, B. Объектив 1 создает изображение в фокальной плоскости, в которой расположена фоточувствительная сторона матрицы ПЗИ 3, оптическое разрешение ее 800отс×1000 строк. Матрица ПЗИ выполнена трехслойной по технологии ХЗ. В периоде /40 мс/ кадра на каждый из трех слоев матрицы ПЗИ вход 1 с ключа 18 поступают импульсы 20 МГц для считывания сигналов R, G, B пикселов по горизонтали [4, c.832], на второй вход матрицы ПЗИ с ключа 19 поступают импульсы 25 кГц частоты строк для считывания сигналов пикселов по вертикали. Аналоговые сигналы с 1-3 выходов матрицы ПЗИ 3 поступают соответственно на входы 4, 5, 6 предварительных усилителей, с выходов которых сигналы поступают на входы 7, 8, 9 АЦП, с выходов которых 8-разрядные коды в параллельном виде с дискретизацией 20 МГц поступают на входы своих кодеров 10, 11, 12. Синхронизация начала считывания с начала периода кадра выполняется импульсом частоты кадра 25 Гц, открывающим синхронно оба ключа 18, 19 для прохода в матрицу управляющих сигналов 20 МГц и 25 кГц. Синтезатор 17 частот выдает: с первого выхода импульсы дискретизации 20 МГц на управляющие входы АЦП 7-9 и сигнальный вход ключа 18, с второго - импульсы дискретизации 80 кГц сигнала звука на управляющие входы АЦП 21 и блока 22 элементов И, с третьего - импульсы частоты кадров 25 Гц на управляющие входы ключей 18, 19 и на второй управляющий вход видеоискателя 20, с четвертого - импульсы 5 МГц на управляющие входы кодеров 10, 11, 12, и на управляющие входы блоков 13, 14, 15 элементов И, с пятого - импульсы 25 кГц частоты строк на сигнальный вход ключа 19 и на третий управляющий вход видеоискателя 20, с шестого - тактовые импульсы 1,28 МГц /80 кГц×16/ сигнала звука на второй управляющий вход накопителя 23 цифровой информации, с седьмого выхода тактовые импульсы 45 МГц на первый управляющий вход накопителя 23 цифровой информации.

Работа кодера, Фиг. 3.

Коды с частотой 20 МГц поступают на 1-8 входы регистра 44, на первые входы схемы 45 сравнения и на входы блока 48 элементов задержек, задерживающих коды на время срабатывания 18 нс схемы 45 сравнения, которая представляется двумя микросхемами 530CD1 с временем срабатывания 18 нс [7, с.279]. Код после задержки в блоке 48 через открытые ключи блока 49 поступает на первый-восьмой входы буферного накопителя 50 кодов кадра, емкостью 200×10 девятиразрядных кодов. Схема 45 выполняет сравнение по величине каждого предыдущего и последующего кодов с целью выявления их равенства или неравенства. При следовании неравных кодов они проходят через блок 48, ключи блока 49 и поступают на первый-восьмой входы буферного накопителя 50 кодов, выдача из которого выполняется сигналом

Uвыд 5 МГц с четвертого выхода блока 17. Поступление кодов в блок 50 при следовании неравных кодов идет с частотой 20 МГц. В общем потоке кодов имеется большое число равных кодов по величине, причем чем выше частота дискретизации, тем больше равных по величие кодов. Кодер выполняет сжатие потока кодов с плавающим коэффициентом от 1 до 255. Общий коэффициент сжатия потока кодов за период каждого кадра принимается не менее 4, что вполне будет выполнено при частоте дискретизации 20 МГц. При неравенстве кодов А>В появляется сигнал на выходе 2 блока 45 /в микросхеме выход 5 [7, с.272 рис.2.190], при равенстве кодов сигнал с выхода 1 блока 45 закрывает ключи в блоке 49, поступает счетным импульсом в счетчик 46 и как сигнал Uвыд на первый управляющий вход регистра 44. Счетчик 46 восьмиразрядный, производит счет импульсов с выхода 1 блока 45 пока идут коды, равные по величине. Счетчик 46 имеет максимальный код 11111111 /255/, отсюда и максимальный коэффициент сжатия 255. С применением счетчика с большей разрядностью, коэффициент сжатия будет больше. Счетчик из микросхем К531ИЕ160 с временем срабатывания 8 нс [7, с.428]. При появлении неравных кодов со схемы 45 следует сигнал с выхода 2 или 3 /при А<В/, которые объединены, сигнал с них используется для выдачи кода числа равных кодов из счетчика 46, который через диоды поступает на первый-восьмой входы блока 50 и заполняет девятый разряд в блоке 50, с этого разряда сигнал используется для опознания по нему кода числа равных кодов при декодировании. Этот же сигнал открывает ключи в блоке 49 /вход 1/ и обнуляет регистр 44 /вход 2/. Выданный перед этим с блока 50 код является первым кодом последовательности, на диаграмме I фиг.4 они помечены крестиками. Коды, равные по величине и подсчитанные счетчиком 46, исключаются из потока кодов /диаграмма III/. Емкость буферного накопителя 50 кодов кадра составляет 200×I03 девятиразрядных кодов для обеспечения коэффициента сжатия 4 за период кадра. При следовании подряд кодов, равных по величине, более 255 в работу вступает дешифратор 47. При коде 11111111 дешифратор 47 выдает сигнал, который одновременно открывает ключи в блоке 49 /вход 1/, обнуляет регистр 44 /вход 2/, выдает код из счетчика 46 /вход 1/ и обнуляет счетчик /вход 2/, а в девятый разряд блока 50 поступает сигнал опознания кода числа равных кодов. Пропускная способность кодера определяется временем срабатывания схемы 45 сравнения /18 нс/ и составляет до 50 Мбайт/c. С выходов кодеров 10, 11, 12 коды в параллельном виде поступают на входы блоков 13, 14, 15 элементов И /фиг.1/, в которых выполняется преобразование параллельных кодов в последовательные перед поступлением их в накопитель 23 цифровой информации. Коды сигналов R, G, В поступают на входы соответственно 1, 2, 3 накопителя 23 цифровой информации. При съемке коды с выходов АЦП 7, 8, 9 поступают и на информационные входы видеоискателя 20, на 1-3 управляющие входы которого поступают импульсы соответственно 20 МГц, 25 Гц и 25 кГц. АЦП 21 сигнала звука преобразует аналоговые сигналы звука в 16-разрядные коды о дискретизацией 80 кГц [l, c.8, Фиг, 6], которые в параллельном виде поступают в блок 22 элементов И, с которого коды звука в последовательном виде поступают на 4 вход накопителя 23 кодов кадра цифровой информации. Устройство 24 воспроизведения предназначено для просмотра снятого материала. Его синтезатор 26 частот выдает: с первого выхода тактовые импульсы UT 45 МГц на сигнальный вход ключа 27 и на первые управляющие входы декодеров 28, 32, 36, со второго выхода - импульсы 1,28 МГц для выдачи с блока 23 кодов сигнала звука и на первый управляющий вход блока 41, с третьего - импульсы дискретизация 80 кГц сигнала звука, с четвертого - импульсы 5 МГц Uвыд с декодеров 28, 32, 36 /вход 2/, пятый - импульсы 25 Гц на управляющий вход ключа 27, на первые управляющие входы накопителей 30, 34, 38 и на управляющий входы формирователей 31, 35, 39 управляющих сигналов, с шестого выхода - импульсы двойной дискретизации 40 МГц на третьи управляющие входы накопителей 30, 34, 38 кодов кадра, с седьмого - импульсы 25 кГц на вторые управляющие входы накопителей кодов кадра 30, 34, 38 /UВыд/, с восьмого - импульсы 20 МГц на третьи управляющие входы декодеров 28, 32, 36 и на управляющие входы блоков 29, 33, 37. Импульсы 25 Гц открывают ключ 27 на длительность кадра, в течение периода которого ключ пропускает пропускает UT 45 МГц на 1, 2, 3 входы накопителя 23 цифровой информации, которые являются сигналами Uвыд последовательных кодов сигналов R, G, В, которые поступают на информационные входы декодеров соответственно 28, 32, 36,

Работа декодеров, Фиг.6.

Коды в последовательном виде поступают c частотой 5 МГц на информационный вход 1 первого регистра 51, на первый /тактовый/ управляющий вход которого поступают тактовые импульсы 45 МГц, на второй управляющий вход поступает сигнал (Uвыд 5 МГц, на третий управляющий вход поступают импульсы 20 МГц с выхода 8 блока 26. Заполняя девять разрядов регистра 51, код приобретает параллельный вид, в котором он далее и используется. С регистра 51 коды выдаются с частотой 5 МГц в накопитель 52 кодов кадра, емкость его 200×10 девятиразрядных кодов. Из накопителя 52 коды выдаются сигналами 5 МГц с ключа 61. При закрытом состоянии ключа 61 коды накапливаются накопителем 52. Исходное состояние ключей в декодере: в блоке 54 открытое, в 56 закрытое, ключей 59, 61, 62 открытое и ключа 60 закрытое. В первый-восьмой разряды второго регистра 53 поступают с первого по восьмой информационные сигналы кода, а при наличии в девятом разряде сигнала опознания числа равных кодов он поступает в девятый разряд регистра 53. С регистра 53 код выдается сигналом Uвыд с ключа 62 уже с частотой 20 МГц. Пока в регистр 53 поступают коды без сигнала в девятом разряде, они далее поступают через открытые ключи блока 54 в третий регистр 55, а с него выдаются сигналом Uвыд1 с ключа 59 на выход декодера. Сигнал Uвыд1 при выдаче кода и обнуляет разряды регистра 55. При поступлении в регистр 53 кода с сигналом в девятом разряде сигнал с девятого разряда закрывает ключи в блоке 54 и открывает ключи в блоке 56, закрывает ключи 59, 61, 62 и открывает ключ 60. Выдача кодов с регистра 53 прерывается, а накопитель 52 кодов производит накопление кодов кадра, так как в него продолжают поступать коды. Код числа равных кодов через открытые ключи блока 56 поступает в вычитающий счетчик 57 импульсов, на счетный вход которого с ключа 60 поступают импульсы 20 МГц. Импульс с ключа 60 поступает и как сигнал

Uввд2 на второй управляющий вход регистра 55 и выдает содержимый в нем код, но при этом не обнуляет его. Поэтому пока идет работа счетчика 57 на вычитание, из регистра 55 выдается один и тот же код. Эти коды являются кодами, изъятыми при сжатии потока кодов в кодере. С выхода регистра 55 идет восстановленный на 100% поток кодов. С регистра 55 идут уже только восьмиразрядные коды с дискретизацией 20 МГц в блок 29 обработки кодов. По окончании вычитания в счетчике 97 в дешифратор 58 поступает код из нулей. С выхода дешифратора 58 сигнал одновременно: закрывает ключи в блоке 56, открывает ключи в блоке 54 /вход 1/, закрывает ключ 60 и открывает ключи 59, 61, 62. С накопителя 52 кодов опять выдаются коды в регистр 53, с него через ключи в блоке 54 в регистр 55, и процессы повторяются. Пропускная способность декодера определяется временем срабатывания /10,5 нс/ счетчика 57, который из микросхем 100ИЕ137 [7, с.428], плюс время 6 нс срабатывания дешифратора 58 из микросхемы 100ИД161 [7, с.433). Скорость восстановления потока кодов до 50 Мбайт/с. Восстановленный поток кодов с частотой 20 МГц /при числе 800 отсчетов в строке/ поступает на вход блока 29 /33, 37/ обработки кодов, выполняющего удвоение числа отсчетов в строке /800×2/. Удвоение выполняется получением промежуточных /средних/ кодов между каждым прошедшим и следующим за ним кодами. Блоки 29, 33, 37 выполняют сложение предыдущего и последующего кодов и деление кода суммы на два. Причем деление выполняется без временных затрат: отбрасыванием младшего разряда в коде суммы /как это делается при делении десятичного числа на десять/ путем соответствующего подключения выходов 0-7 сумматора /фиг.7/ 70 и выходов 1-8 регистров 71, 72:

Разряд 0 означает перенос в старший разряд при сумме кодов.

Удвоение отсчетов в строке сокращает период следования кодов в

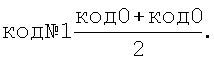

два раза, который становится 25 нс  , т.е. 40 МГц. Процесс сложения двух 8-разрядных кодов должен занимать 25 нс. В качестве сумматора применяется микросхема К555ИМ6 [7, с.258] с временем сложения 25 нс. После включения питания в регистрах 66-69 нули. С приходом первого импульса 20 МГц на вход триггера 63 /фиг.7/ с его первого выхода сигнал Uвыд1 одновременно: выдает "код 0" с регистра 67 на первые входы сумматора 70, из регистра 68 "код 0" в регистр 72 для хранения на 50 нс и через диоды на вторые входы сумматора 70, сигналы выдачи и обнуляют регистры, открывает Uот ключи в блоке 64 на время прохода следующего кода через ключи, и регистры 66, 67 заполняются кодом "код 1". В сумматоре 70 за 25 нс идет сложение "код 0+код 0", и код суммы идет на выход при этом он делится на два:

, т.е. 40 МГц. Процесс сложения двух 8-разрядных кодов должен занимать 25 нс. В качестве сумматора применяется микросхема К555ИМ6 [7, с.258] с временем сложения 25 нс. После включения питания в регистрах 66-69 нули. С приходом первого импульса 20 МГц на вход триггера 63 /фиг.7/ с его первого выхода сигнал Uвыд1 одновременно: выдает "код 0" с регистра 67 на первые входы сумматора 70, из регистра 68 "код 0" в регистр 72 для хранения на 50 нс и через диоды на вторые входы сумматора 70, сигналы выдачи и обнуляют регистры, открывает Uот ключи в блоке 64 на время прохода следующего кода через ключи, и регистры 66, 67 заполняются кодом "код 1". В сумматоре 70 за 25 нс идет сложение "код 0+код 0", и код суммы идет на выход при этом он делится на два:

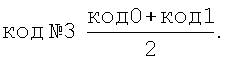

Регистры 71 и 72 хранят код /задерживают/ 50 нс, причем первая половина задержки приходится на процесс выполнения сложения в сумматоре /0-25 нс/. С приходом второго импульса 20 МГц в триггер 63 он обнуляет сумматор 70, а сигнал со второго выхода триггера Uвыд2 одновременно: выдает с регистра 72 код №2 "код 0", с регистра 66 "код 1" в регистр 71 и через диоды в сумматор, с регистра 69 "код 0" в сумматор, открывает ключи в блоке 65, и регистры 68, 69 заполняются кодом "код 2". В сумматоре идет сложение "код 0+код 1", по окончании которого /через 25 нс/ код суммы идет на выход сумматора с делением на два:

Регистры 71 и 72 хранят код /задерживают/ 50 нс, причем первая половина задержки приходится на процесс выполнения сложения в сумматоре /0-25 нс/. С приходом второго импульса 20 МГц в триггер 63 он обнуляет сумматор 70, а сигнал со второго выхода триггера Uвыд2 одновременно: выдает с регистра 72 код №2 "код 0", с регистра 66 "код 1" в регистр 71 и через диоды в сумматор, с регистра 69 "код 0" в сумматор, открывает ключи в блоке 65, и регистры 68, 69 заполняются кодом "код 2". В сумматоре идет сложение "код 0+код 1", по окончании которого /через 25 нс/ код суммы идет на выход сумматора с делением на два:  С приходом третьего импульса 20 МГц в триггер 63 он обнуляет сумматор 70, а сигнал с его первого выхода Uвыд3 одновременно: выдает с регистра 71 код №4 "код 1" на выход блока, из регистра 67 выдает "код 1" в сумматор, из регистра 67 "код 2" в регистр 72 и через диоды в сумматор, открывает ключи в блоке 64, и регистры 66, 67 заполняются кодом "код 3". В сумматоре идет сложение "код1+код 2", код суммы идет на выход и делится на два:

С приходом третьего импульса 20 МГц в триггер 63 он обнуляет сумматор 70, а сигнал с его первого выхода Uвыд3 одновременно: выдает с регистра 71 код №4 "код 1" на выход блока, из регистра 67 выдает "код 1" в сумматор, из регистра 67 "код 2" в регистр 72 и через диоды в сумматор, открывает ключи в блоке 64, и регистры 66, 67 заполняются кодом "код 3". В сумматоре идет сложение "код1+код 2", код суммы идет на выход и делится на два:  С приходом четвертого импульса в триггер 63 он обнуляет сумматор 70, а с сигнал Uвыд одновременно: выдает код №6 "код 2" из регистра 72, с регистра 66 "код 3" в регистр 71 и через диоды в сумматор, с регистра 69 "код 2" в сумматор, открывает ключи в блоке 65, регистры 68, 69 заполняются следующим кодом «код 4». В сумматоре идет сложение "код3+код4", и код суммы идет на выход с делением его на два: код 7

С приходом четвертого импульса в триггер 63 он обнуляет сумматор 70, а с сигнал Uвыд одновременно: выдает код №6 "код 2" из регистра 72, с регистра 66 "код 3" в регистр 71 и через диоды в сумматор, с регистра 69 "код 2" в сумматор, открывает ключи в блоке 65, регистры 68, 69 заполняются следующим кодом «код 4». В сумматоре идет сложение "код3+код4", и код суммы идет на выход с делением его на два: код 7  С приходом пятого импульса в триггер 63 он обнуляет сумматор 70, а сигнал UВЫД5 с первого выхода триггера одновременно: выдает с регистра 72 код №8 "код 3", выдает с регистра 67 "код 3" в сумматор, с регистра 68 "код 4" в регистр 72 на хранение и черев диоды в сумматор, открывает ключи в блоке 64, и регистры 66, 67 заполняются кодом "код 5". Сумматор выполняет сложение "код 3+код 4", код суммы следует на выход с делением на два: код №9

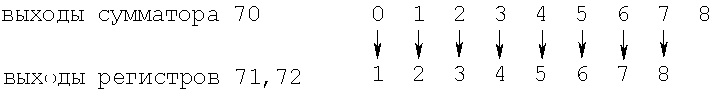

С приходом пятого импульса в триггер 63 он обнуляет сумматор 70, а сигнал UВЫД5 с первого выхода триггера одновременно: выдает с регистра 72 код №8 "код 3", выдает с регистра 67 "код 3" в сумматор, с регистра 68 "код 4" в регистр 72 на хранение и черев диоды в сумматор, открывает ключи в блоке 64, и регистры 66, 67 заполняются кодом "код 5". Сумматор выполняет сложение "код 3+код 4", код суммы следует на выход с делением на два: код №9  С приходом шестого и следующих импульсов в триггер 63 процессы повторяются. Выходы 0-7 сумматора 70 и выходы 1-8 регистров 71, 72 поразрядно объединены и являются выводами блока 29 /33, 37/. Коды с блоков 29, 33, 37 с частотой 40 МГц в параллельном виде поступают на информационные входы накопителей соответственно 30, 34, 38 кодов кадра.

С приходом шестого и следующих импульсов в триггер 63 процессы повторяются. Выходы 0-7 сумматора 70 и выходы 1-8 регистров 71, 72 поразрядно объединены и являются выводами блока 29 /33, 37/. Коды с блоков 29, 33, 37 с частотой 40 МГц в параллельном виде поступают на информационные входы накопителей соответственно 30, 34, 38 кодов кадра.

Работа блоков 73 регистров, фиг.8, 9, 10.

Сигналы кодов поступают на третьи входы разрядов восьми регистров 77 /фиг.9/. Заполнение регистров строки начинается с открытием сигналом кадра Uк 25 Гц первого ключа в первом блоке 731 регистров /фиг.8/. Ключ 74 /фиг.9/ пропускает импульсы 40 МГц на вход распределителя 76 импульсов, тактовые импульсы с которого последовательно поступают на первые входы разрядов параллельно с восьми регистров 77. По заполнению регистров 77 с последнего выхода /1600-го/ блока 76 сигнал Uз закрывает ключ 74 и в качестве управляющего выходного сигнала открывает ключ 74 в следующем блоке 732 регистров, регистры которого заполняются кодами второй строки. За период кадра 40 мс последовательно заполняются кодами регистры 77 всех блоков 731-1000 регистров. С блока 731000 регистров выходной сигнал поступает параллельно на четвертые управляющие входы всех блоков 73 регистров /фиг.8/ и открывает в них вторые ключи 75, которые пропускают по одному сигналу Uвыд, который синхронно выдает из всех блоков 731-1000 регистров коды кадра в свои формирователи 31, 35, 39 управляющих сигналов /фиг.2/, Каждый накопитель 30, 34, 38 кодов кадра имеет 12,8×106 выходов /1600×8×1000/, которые подключены к стольким же входам в каждом из блоков 31, 35, 39, каждый из которых имеет в своем составе 1,6×106 преобразователей /1600×1000/ "код - число импульсов излучений". Выходы от трех блоков 31, 35, 39 4,8×106/3×1,6×106/ подключены к стольким же входам в СД-экране 40. Для надежной и длительной работы устройства воспроизведения лучшим вариантом исполнения его будет исполнение накопителей кодов кадра и формирователей управляющих сигналов на тыльной стороне СД-экрана в единой и неразборной с ним конструкции.

Работа видеокамеры.

ФЭП2 формирует матрицей ПЗИ 3 /фиг.1/ аналоговые цветовые сигналы, которые преобразуются АЦП 7, 8, 9 с частотой 20 МГц в 8-разрядные коды, поступающие в кодеры 10, 11, 12, Кодеры выполняют сжатие потока кодов с коэффициентом 4 за период кадра. Затем параллельные коды преобразуются блоками 13, 14, 15 в последовательные, которые поступают на 1, 2, 3 входы накопителя 23 цифровой информации, на 4-й вход которого поступают коды сигналов звука. При воспроизведении /фиг.2/ сигнал 25 Гц открывает ключ 27, пропускающий тактовые сигналы 45 МГц, являющиеся сигналами выдачи, которые выдают коды R, G, В из накопителя 23 цифровой информации на информационные входы трех декодеров 28, 32, 36, которые восстанавливают сжатые потоки кодов. Блоки 29, 33, 37 выполняют удвоение числа отсчетов в строке, c них коды с частотой 40 МГц поступают на информационные входы накопителей 30, 34, 38 кодов кадра, которые за первый период кадра сосредотачивают все коды кадра в блоках 731-1000 регистров. Выходной управляющий сигнал с последнего блока 731000 регистров синхронно выдает вое коды кадра в формирователи 31, 35, 39 управляющих сигналов, в которых коды преобразуются в сигналы запитывания светодиодов СД-экрана. Видеорежим при воспроизведении на СД-экране 40 1600×1000×25 Гц. Сигналы 1,28 МГц со второго выхода блока 26 выдают из блока 23 коды сигнала звука, которые поступают в блок 41, преобразуются в нем в аналоговые сигналы и воспроизводятся громкоговорителем 43. В устройстве воспроизведения отсутствуют строчная и кадровая развертки. Технические характеристики видеокамеры в таблице 2. В устройстве выполнены заявленные цели: упрощен фотоэлектрический преобразователь, увеличено в 4 раза время работы с видеокамерой и в два раза повышено разрешение кадра.

Использованные источники

1. Патент №220529 C1, кл. H04N 5/225, бюл.5 от 20.02.06, аналог.

2. Патент №2303334 C1, Кл. H04N 5/225, бюл.20 от 20.07.07, прототип.

3. В.И.Мураховский. Устройство компьютера, М., 2003, с.552.

4. Колесниченко О.В., Шишигин И.В. Аппаратные средства PC. 5-е изд, СПб, 2004, с.832, 833, 835.

5. "Радио", №9, 2004, с.47.

6. "Домашний компьютер", №12, 2006, с.43.

7. Цифровые интегральные микросхемы. Минск, 1991, с.258, 279, 272, 428, 433.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2008 |

|

RU2375841C1 |

| СИСТЕМА ТЕЛЕВИДЕНИЯ | 2007 |

|

RU2358411C1 |

| СИСТЕМА ТЕЛЕВИДЕНИЯ | 2008 |

|

RU2368097C1 |

| ВИДЕОКАМЕРА | 2007 |

|

RU2358412C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2008 |

|

RU2369041C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2007 |

|

RU2356179C1 |

| УНИВЕРСАЛЬНАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ | 2009 |

|

RU2410846C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2010 |

|

RU2420025C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2008 |

|

RU2384012C1 |

| ДВУХКАНАЛЬНАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ | 2009 |

|

RU2413387C1 |

Изобретение относится к бытовой цифровой видеотехнике, может использоваться для записи и воспроизведения видеоинформации. Техническими результатами являются упрощение конструкции фотоэлектрического преобразователя /ФЭП/, увеличение длительности непрерывного использования видеокамеры и увеличение разрешения кадра, достигаемые введением в ФЭП матрицы ПЗИ, выполненной по технологии ХЗ, сжатием потока кодов видеоинформации и применением плоскопанельного светодиодного экрана /СД-экрана/. Результат достигается тем, что в ФЭП вводится матрица ПЗИ, в видеокамеру вводятся три кодера, в каждый канал устройства воспроизведения вводятся декодер и формирователь управляющих сигналов, а устройство отображения видеоинформации представляется плоскопанельным светодиодным экраном. 14 ил., 2 табл.

Видеокамера, содержащая объектив, фотоэлектрический преобразователь (ФЭП), последовательно соединенные задающий генератор и синтезатор частот, с первого по третий аналого-цифровые преобразователи (АЦП) видеосигнала, АЦП сигнала звука, на вход которого подан звуковой сигнал и управляющий вход его подключен к второму выходу синтезатора частот, содержащая первый ключ, с первого по четвертый блоки элементов И, накопитель цифровой информации, видоискатель и устройство воспроизведения, соответствующие входы видоискателя подключены к выходам первого-третьего АЦП видеосигнала и третий управляющий вход подключен к пятому выходу синтезатора частот, ФЭП содержит с первого по третий предварительные усилители, выходы которых являются первым, вторым и третьим выходами ФЭП и подключены к информационным входам соответственно первого-третьего АЦП видеосигнала, управляющие входы которых объединены и подключены к первому выходу синтезатора частот, первый-четвертый входы накопителя цифровой информации подключены к выходам соответственно с первого по четвертый блоков элементов И, а первый и второй управляющие входы его подключены к седьмому и шестому выходам синтезатора частот, входы четвертого блока элементов И подключены к выходам АЦП сигнала звука, к управляющему входу которого подключен и управляющий вход четвертого блока элементов И, управляющие входы первого-третьего блоков элементов И объединены и подключены к соответствующему входу синтезатора частот, с первого по четвертый информационные входы устройства воспроизведения подключены соответственно к первому-четвертому выходам накопителя цифровой информации, а первый и второй управляющие выходы его подключены соответственно к первому и второму управляющим входам накопителя кодов цифровой информации, устройство воспроизведения включает последовательно соединенные задающий генератор и синтезатор частот, ключ, сигнальный вход которого подключен к первому выходу синтезатора частот, а управляющий его вход подключен к пятому выходу синтезатора частот, выход ключа является первым управляющим выходом устройства воспроизведения, вторым управляющим выходом которого является второй выход синтезатора частот, содержит три канала обработки кодов R, G, В, каждый из которых включает блок обработки кодов и накопитель кодов кадра, и содержит последовательно соединенные регистр сигнала звука, блок формирования аналогового звукового сигнала и громкоговоритель, информационный вход регистра сигнала звука подключен к четвертому выходу накопителя цифровой информации, первый управляющий вход подключен к второму выходу синтезатора частот, к третьему выходу которого подключен второй управляющий вход регистра звукового сигнала, блоки обработки кодов идентичны, каждый включает триггер, первый и второй блоки ключей, с первого по шестой регистры, сумматор и 16 диодов, информационные входы первого и второго регистров поразрядно объединены и подключены к выходам первого блока ключей, информационные входы третьего и четвертого регистров поразрядно объединены и подключены к выходам второго блока ключей, информационным входом блока являются поразрядно объединенные входы первого и второго блоков ключей, управляющим входом является вход триггера, подключенный к соответствующему выходу синтезатора частот, первый выход триггера подключен к управляющим входам второго, третьего, пятого регистров и первого блока ключей, второй выход триггера подключен к управляющим входам первого, четвертого, шестого регистров и второго блока ключей, первые входы сумматора подключены к выходам второго регистра и через диоды к выходам первого регистра, вторые входы сумматора подключены к выходам четвертого регистра и через диоды к выходам третьего регистра, управляющий вход сумматора подключен к входу триггера, входы пятого регистра подключены к выходам первого регистра, входы шестого регистра подключены к выходам третьего регистра, выходы пятого, шестого регистров и выходы сумматора поразрядно объединены и являются выходами блока обработки кодов, отличающаяся тем, что в фотоэлектрический преобразователь введена матрица ПЗИ, фоточувствительная сторона которой расположена в фокальной плоскости объектива, и первый, второй, третий ее выходы подключены к входам соответственно первого, второго и третьего предварительных усилителей, в видеокамеру введены первый, второй и третий кодеры и второй ключ, сигнальный вход которого подключен к пятому выходу синтезатора частот, третий выход которого подключен к объединенным управляющим входам первого и второго ключей и к второму управляющему входу видоискателя, первый управляющий вход которого и сигнальный вход первого ключа подключены к первому выходу синтезатора частот, информационные первый-восьмой входы первого-третьего кодеров подключены к первому-восьмому выходам первого-третьего АЦП видеосигнала, объединенные управляющие входы первого-третьего блоков элементов И подключены к четвертому выходу синтезатора частот, выход первого ключа подключен к первому входу матрицы ПЗИ, к второму входу которой подключен выход второго ключа, в устройство воспроизведения введен плоскопанельный светодиодный экран (СД-экран), а в каждый из каналов обработки кодов R, G, В введены декодер, выходы которого подключены к информационным входам блока обработки кодов своего канала, выходы которого подключены к информационным входам накопителя кодов кадра, и введен Формирователь управляющих сигналов, информационные входы которого подключены к выходам накопителя кодов кадра своего канала, управляющий вход ключа подключен к пятому выходу синтезатора частот, к которому подключены объединенные первые управляющие входы накопителей кодов кадра трех каналов и объединенные управляющие входы формирователей управляющих сигналов трех каналов, первый, второй и третий выходы накопителя цифровой информации подключены к информационным входам соответственно первого, второго и третьего декодеров трех каналов, одноименные первый, второй и третий управляющие входы декодеров объединены и подключены соответственно к первому, восьмому и четвертому выходам синтезатора частот, объединенные управляющие входы трех блоков обработки кодов подключены к восьмому выходу синтезатора частот, одноименные второй и третий управляющие входы накопителей кодов кадра объединены и подключены соответственно к седьмому и шестому выходам синтезатора частот, соответствующие информационные входы СД-экрана подключены к соответствующим выходам формирователей управляющих сигналов, кодеры идентичны, каждый включает последовательно соединенные регистр, схему сравнения (компаратор), счетчик импульсов и дешифратор, последовательно соединенные блок элементов задержек, блок ключей и буферный накопитель кодов кадра, информационными входами являются поразрядно объединенные первый-восьмой входы регистра, первые входы схемы сравнения и входы блока элементов задержек, выходами являются с первого по девятый выходы буферного накопителя кодов кадра, первый выход схемы сравнения подключен к счетному входу счетчика импульсов, к первому управляющему входу регистра и к второму управляющему входу блока ключей, второй и третий выходы схемы сравнения объединены и подключены к второму управляющему входу регистра, к первому управляющему входу блока ключей, к первому управляющему входу счетчика импульсов и к входу девятого разряда буферного накопителя кодов кадра, первый-восьмой выходы счетчика импульсов подключены к входам дешифратора и через диоды к первому-восьмому входам буферного накопителя кодов кадра, выход дешифратора подключен к второму управляющему входу счетчика импульсов, через диод к первому управляющему входу блока ключей, к второму управляющему входу регистра, к первому управляющему входу счетчика импульсов и к входу девятого разряда буферного накопителя кодов кадра, декодеры идентичны, каждый включает последовательно соединенные первый регистр, накопитель кодов кадра, второй регистр, первый блок ключей и третий регистр, последовательно соединенные второй блок ключей, вычитающий счетчик импульсов и дешифратор, с первого по четвертый ключи, первый-восьмой выходы второго регистра подключены параллельно к первому-восьмому входам первого блока ключей и второго блока ключей, выход девятого разряда второго регистра подключен к второму управляющему входу первого блока ключей, к первому управляющему входу второго блока ключей, к второму управляющему входу первого ключа, к первому управляющему входу второго ключа и к вторым управляющим входам третьего и четвертого ключей, выход дешифратора подключен к первому управляющему входу первого блока ключей, к второму управляющему входу второго блока ключей, к первым управляющим входам первого, третьего и четвертого ключей, к второму управляющему входу второго ключа, выход первого ключа подключен к первому управляющему входу третьего регистра, выход второго ключа подключен к счетному входу вычитающего счетчика импульсов и к второму управляющему входу третьего регистра, выход третьего ключа подключен к управляющему входу накопителя кодов кадра, выход четвертого ключа подключен к управляющему входу второго регистра, информационным входом декодера является информационный вход первого регистра, выходами являются первый-восьмой выходы третьего регистра, управляющими входами являются: первым - первый управляющий (тактовый) вход первого регистра, вторым - объединенные второй управляющий вход первого регистра и сигнальный вход третьего ключа, третьим - объединенные сигнальные входы первого, второго, четвертого ключей, накопители кодов кадра идентичны, каждый включает последовательно соединенные блоки регистров по числу строк (1000) в кадре, информационными входами являются поразрядно объединенные первый-восьмой входы 1000 блоков регистров, управляющими входами являются: первым - первый управляющий вход первого блока регистров, вторым - объединенные вторые управляющие входы блоков регистров, третьим - объединенные третьи управляющие входы блоков регистров, каждый управляющий выход предыдущего блока регистров является первым управляющим входом каждого последующего блока регистров, управляющий выход последнего блока регистров подключен параллельно к четвертым управляющим входам всех блоков регистров, выходами накопителя кодов кадра являются параллельные выходы всех блоков регистров (1600×8×1000), блоки регистров идентичны, каждый включает первый и второй ключи, распределитель импульсов и восемь регистров, информационным входом являются поразрядно объединенные третьи входы разрядов восьми регистров, выходами являются параллельные выходы всех разрядов восьми регистров (1600×8), управляющими входами являются: первым - первый управляющий вход первого ключа, вторым - сигнальный вход второго ключа, третьим -сигнальный вход первого ключа, четвертым - первый управляющий вход второго ключа, выход первого ключа подключен к входу распределителя импульсов, выходы которого последовательно подключены к первым (тактовым) входам разрядов параллельно восьми регистров, последний выход распределителя импульсов подключен к второму управляющему входу первого ключа и является управляющим выходом, подключенным к первому управляющему входу следующего блока регистров, выход второго ключа подключен к вторым входам разрядов параллельно восьми регистров и к второму управляющему входу второго ключа, формирователи управляющих сигналов идентичны, каждый включает блок формирователей импульсов, вход которого является управляющим входом формирователя управляющих сигналов, и преобразователи "код - число импульсов излучений" по числу разрешения кадра (1600×1000), каждый из которых включает последовательно соединенные дешифратор, первый-восьмой входы которого являются входами преобразователя, блок ключей из 255 ключей, и выходной ключ, самоходный распределитель импульсов (СРИ) из 255 разрядов, выходы которых подключены к сигнальным входам соответствующих ключей в блоке ключей и источник питания, соответствующие выходы дешифратора подключены к управляющим входам соответствующих ключей в блоке ключей, выходы ключей в котором объединены и объединенный выход подключен к управляющему входу (Uот) выходного ключа, сигнальный вход которого подключен к выходу источника питания, а выход выходного ключа является выходом преобразователя, блок Формирования импульсов включает схемы формирования импульсов по числу преобразователей "код-число импульсов излучений", выход каждой схемы формирования импульсов подключен к входу СРИ своего преобразователя, информационными входами формирователя управляющих сигналов являются входы дешифраторов всех преобразователей, выходами являются выходы всех преобразователей "код-число импульсов излучений" плоскопанельный светодиодный экран содержит экранное стекло и выполненную в нем матрицу из излучающих элементов по числу разрешения кадра (1600×1000), каждый излучающий элемент включает три светодиодных ячейки (СД-ячейки), каждая из которых излучает один из основных цветов, СД-ячейка включает светодиод белого свечения и соответствующий цветной светофильтр на излучающей стороне, управляющий вход каждого светодиода подключен к соответствующему выходу соответствующего формирователя управляющих сигналов.

| ЦИФРОВАЯ ВИДЕОКАМЕРА | 2006 |

|

RU2303334C1 |

| СИСТЕМА ПОЛНОЦВЕТНОГО СВЕТОДИОДНОГО ДИСПЛЕЯ | 2000 |

|

RU2249858C2 |

| JP 2007043279 A, 15.02.2007 | |||

| JP 2007184786 A, 19.07.2007. | |||

Авторы

Даты

2009-06-20—Публикация

2007-11-06—Подача